E-1158

ERASABLE STORE MOD 3C contro

by

David Shansky

July 1962

Inst.

contro

tion of

rized w

M.I.T.

by the

and

CAMBRIDGE 39, MASSACHUSETTS LABORATORY

| S        | Approved Ellen C Hall Date 7/17/62                                  |

|----------|---------------------------------------------------------------------|

|          | ELDON C. HALL, ASSISTANT DIRECTOR INSTRUMENTATION LABORATORY        |

| HUS      | Approved 716 B Lagest Date 7/18/62 MILTON B. TRAGESER, DIRECTOR     |

| AC       | MILTON B. TRAGESEK, DIRECTOR APOLLO GUIDANCE AND NAVIGATION PROGRAM |

| 25       | Approved Date 7/19/62 ROGER B. WOODBURY, ASSOCIATE DIRECTOR         |

| <b>S</b> | ROGER B. WOODBURY, ASSOCIATE DIRECTOR INSTRUMENTATION LABORATORY    |

E-1158

by

David Shansky

July 1962

### FOR OFFICIAL USE ONLY

This document has been prepared for Instrumentation Laboratory use and for ERASABLE STORE MOD 3C controlled external distribution. Reproduction or further dissemination is not authorized without express written approval of M.I.T. This document has not been reviewed by the Security Classifications Office, NASA, and therefore, is not for public release.

# INSTRUMENTATION RATORY

CAMBRIDGE 39, MASSACHUSETTS

COPY#\_\_\_

#### ACKNOWLEDGEMENT

The advice and active assistance of Dr. Albert Hopkins and Dr. Ramon Alonso during the design, construction and debugging of the memory is gratefully acknowledged. Mr. Samuel T. Scott is to be credited for much of the Sense Amplifier thermal design and for that section of the report dealing with the effect of temperature on amplifier response.

This report was prepared under the auspices of DSR Project 55-191, sponsored by the Manned Spacecraft Center of the National Aeronautics and Space Administration through contract NAS9-153.

The publication of this report does not constitute approval by the National Aeronautics and Space Administration of the findings or the conclusions contained therein. It is published only for the exchange and stimulation of ideas.

## E-1158 ERASABLE STORE MOD 3C

#### ABSTRACT

An erasable ferrite memory consisting of 512 - 16 bit words has been assembled and is being tested in the Mod 3C computer. The memory has been designed for operation from  $0^{\circ}$  to  $100^{\circ}$ C. Characteristics of the cores selected and the circuits designed to fulfill this objective are discussed.

by David Shansky July 1962

# TABLE OF CONTENTS

|      |            |                                    |         |         |        |        |        |    | Page |

|------|------------|------------------------------------|---------|---------|--------|--------|--------|----|------|

| Era  | sable      | Store Mod 3C                       |         |         |        |        |        |    | 7    |

|      | Intr       | oduction .                         |         |         |        |        | •      |    | 7    |

|      | Add        | lress Selection                    |         |         |        |        |        | ,  | 8    |

|      | Dri        | ver Circuits .                     |         |         |        |        | •      |    | 9    |

|      | Sen        | se Amplifiers                      |         | •       |        |        |        | ,  | 11   |

|      | Ter<br>Sen | nperature Effects<br>se Amplifiers | on 3C   | Erasa   | able M | emor   | У .    |    | 12   |

|      |            | Experimental R                     | esults  |         |        |        |        |    | 12   |

|      |            | Conclusions                        |         |         | ě.     |        |        |    | 13   |

|      |            | Further Work                       |         |         |        |        |        |    | 13   |

| Appe | endix      | I High Density Sta                 | ck      |         |        |        |        |    | 31   |

|      |            |                                    |         |         |        |        |        |    |      |

|      |            | LIST OF I                          | LLJIST  | rr A Ti | IONS   |        |        |    |      |

|      |            |                                    |         |         | CIVID  |        |        |    |      |

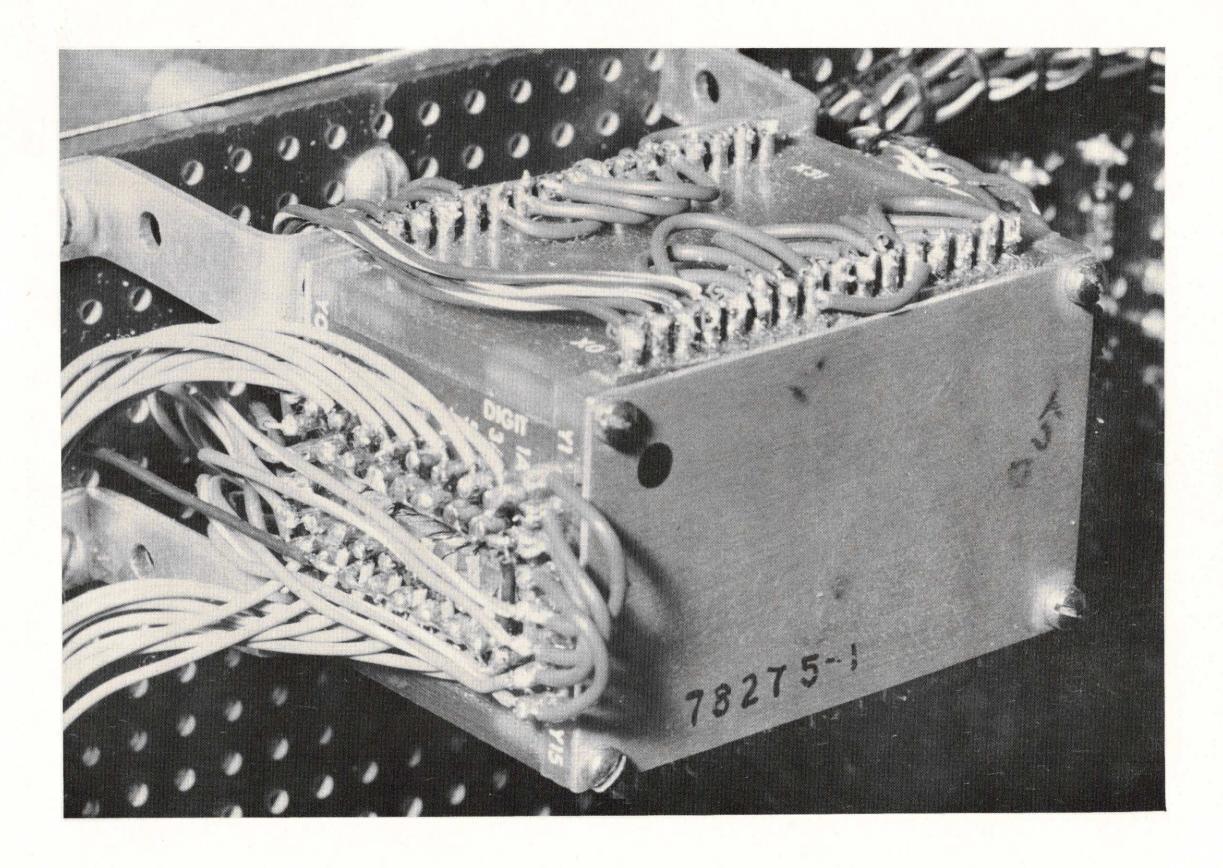

| Fig. | 1          | The 512 word fer                   | rite m  | emory   | У      |        |        |    | 16   |

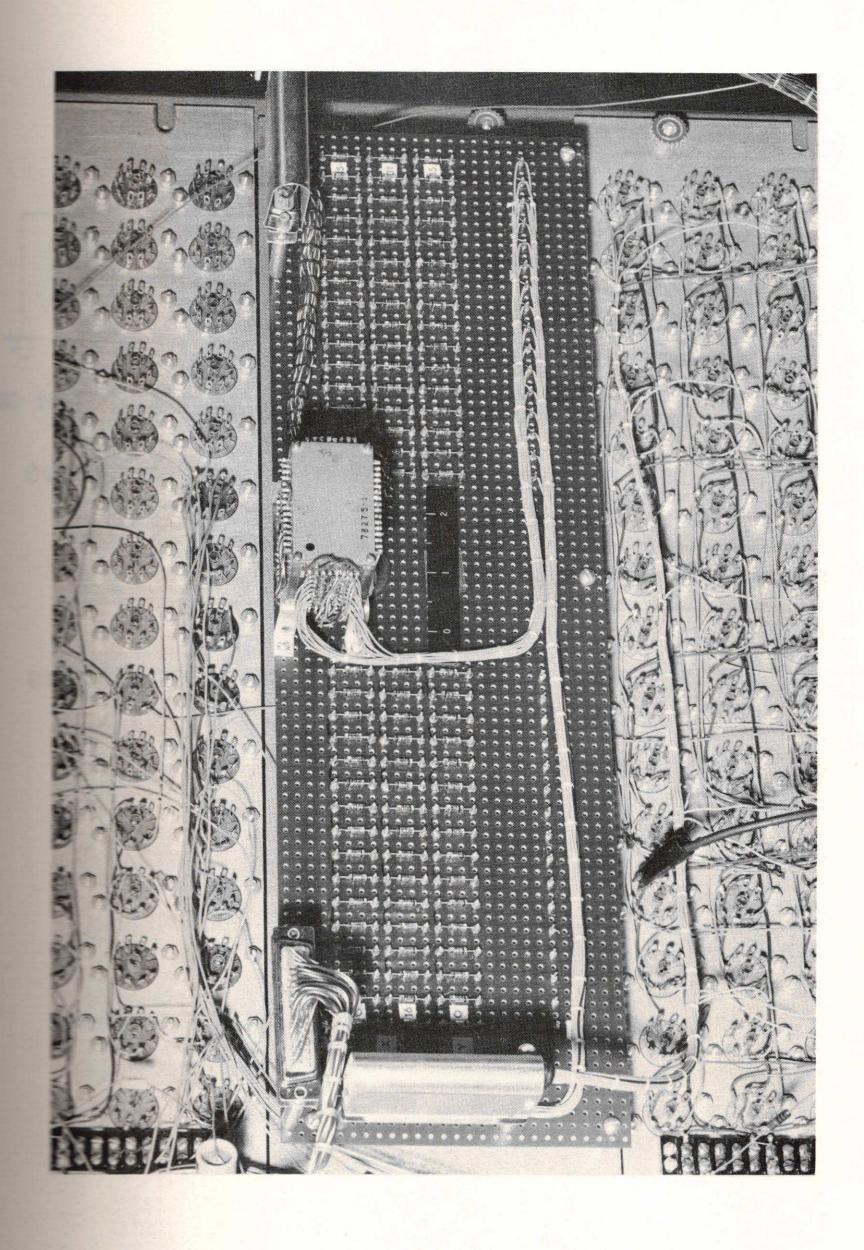

| Fig. | 2          | The 512 word me                    | mory a  | and se  | lectio | n elec | tronic | es | 17   |

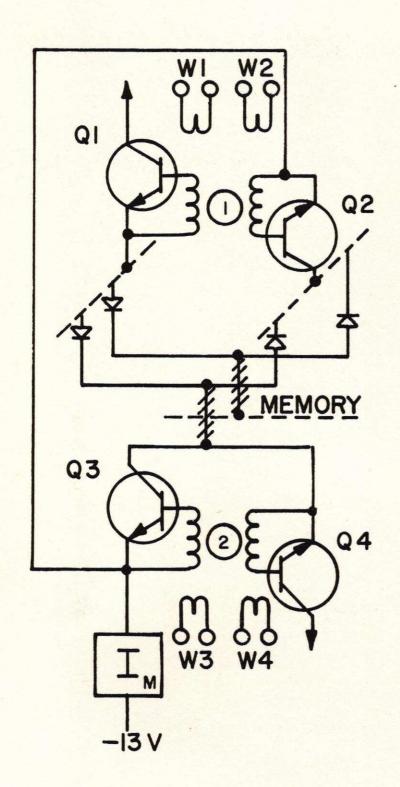

| Fig. | 3          | Memory current                     |         |         |        |        |        |    | 18   |

| Fig. | 4          | The Y address se                   | lection | n       |        |        |        | •  | 19   |

| Fig. | 5          | The X address se                   |         |         |        |        |        |    | 20   |

| Fig. | 6          | Current regulator                  | (X an   | d Y a   | xes)   |        | •      |    | 21   |

| Fig. | 7          | Inhibit driver (Z                  | plane)  |         | •      |        |        |    | 22   |

| Fig. | 8          | I = f(t), current r                | regulat | or      | •      |        |        |    | 23   |

| Fig. | 9          | Combination of fe                  | rrite o | core a  | nd dri | ver.   |        |    |      |

| This | 10         | illustrating consta                |         |         |        |        |        |    | 24   |

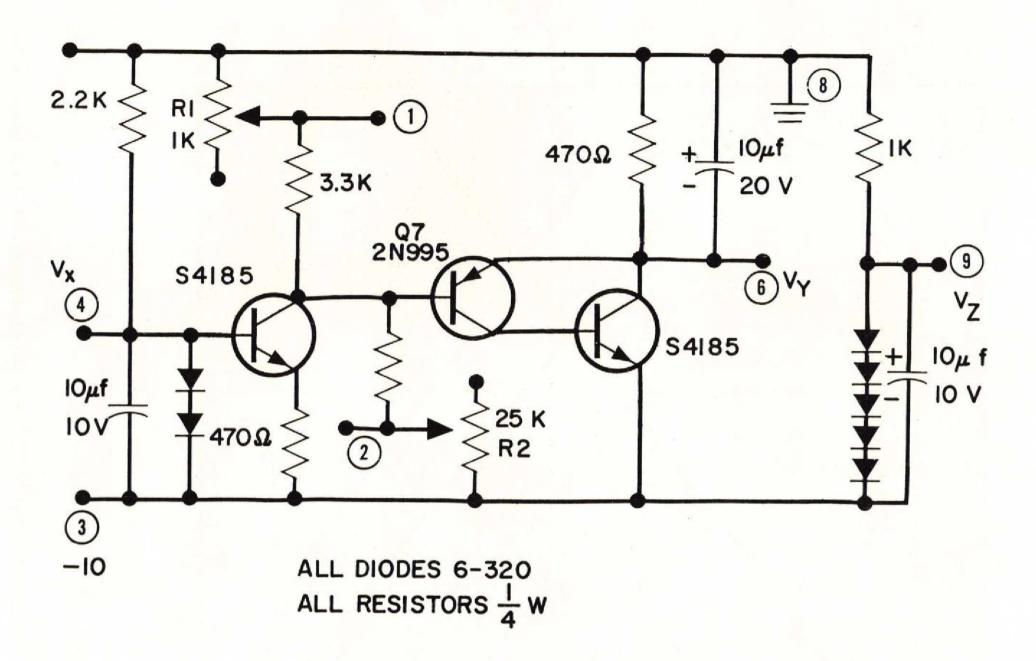

| Fig. |            | Sense amplifier e                  |         |         |        |        | •      | •  | 25   |

| Fig. | 11         | Voltage source (perasable memory   | art of  | sense   | ampl   | ifier  | •      |    | 26   |

| Fig. | 12         | Initial data with w                |         |         |        |        |        |    | 27   |

| Fig. | 13         | Variation of sense temperature     |         |         |        |        |        |    | 28   |

| Fig. | 14  | Performance of temperature compensated |       |         |        |       |   |      |

|------|-----|----------------------------------------|-------|---------|--------|-------|---|------|

|      |     | sense amplifier                        | •     |         | •      |       | • | . 28 |

| Fig. | 15  | Circuit for $V_Y$ with coefficient     | posit | tive te | empera | ature |   |      |

|      |     | coefficient .                          | ٠     |         |        |       |   | . 29 |

| Fig. | A-1 | (a), (b), (c), (d)                     | ٥     | ۰       |        |       |   | . 33 |

| Fig. | A-1 | (e), (f), (g), (h)                     | •     | •       |        |       | • | . 34 |

#### ERASABLE STORE MOD 3C

#### Introduction

A Ferrite coincident current memory, consisting of 512 - 16 bit words has been assembled for Mod 3C and is presently being tested.

The ferrite core array itself has been assembled using RCA 233 M1 ferrite cores. These cores produce a nominal 1 output of 50 mv when driven at 800 MAT at 25°C. Wiring in the array itself was specified to minimize the physical size of the memory and the number of permissible joints. The wiring of the X and Y selection axes is continuous, breaks being allowed only for the purpose of replacing cores which were found defective in test. The total size of the experiment array is approximately 1.25" x 2.25" x 1.25" exclusive of solder lugs. The memory itself has been operated over the temperature range -55°C to + 300°C with variable drive currents. The coefficient of coercive force vs. temperature, in the range 0°C to + 100°C is approximately -0.3%/°C. Figures 1 and 2 are photographs of the memory. Photographs of the output waveforms for a worst word pattern and a numerical summary of the entire stack are included in Appendix I. These waveforms were obtained by cycling the memory through all addresses with the memory storing a pattern which produces the worst disturb noises on the sense winding. The drive currents were held constant at  $I_X = I_Y = I_Z = 400$  ma. The temperature was allowed to vary over a 100°C temperature interval.

One of the basic objectives of this design was to render the performance of the memory insensitive to temperature. This

has involved the design of current drivers whose temperature characteristic matched the particular core (memory cell) characteristic, and the design of sense amplifiers whose sensing threshold is a defined function of temperature, program and supply voltage. The characteristics of these building blocks will be discussed in more detail later in this report.

#### Address Selection

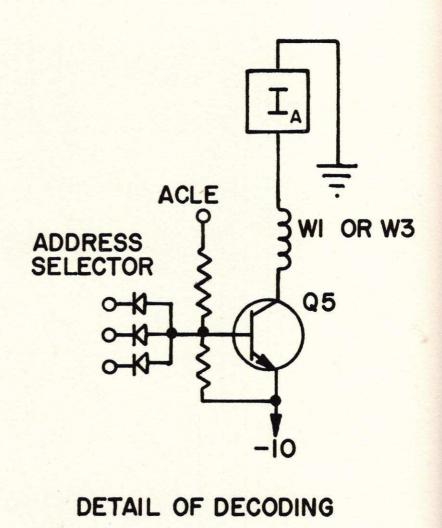

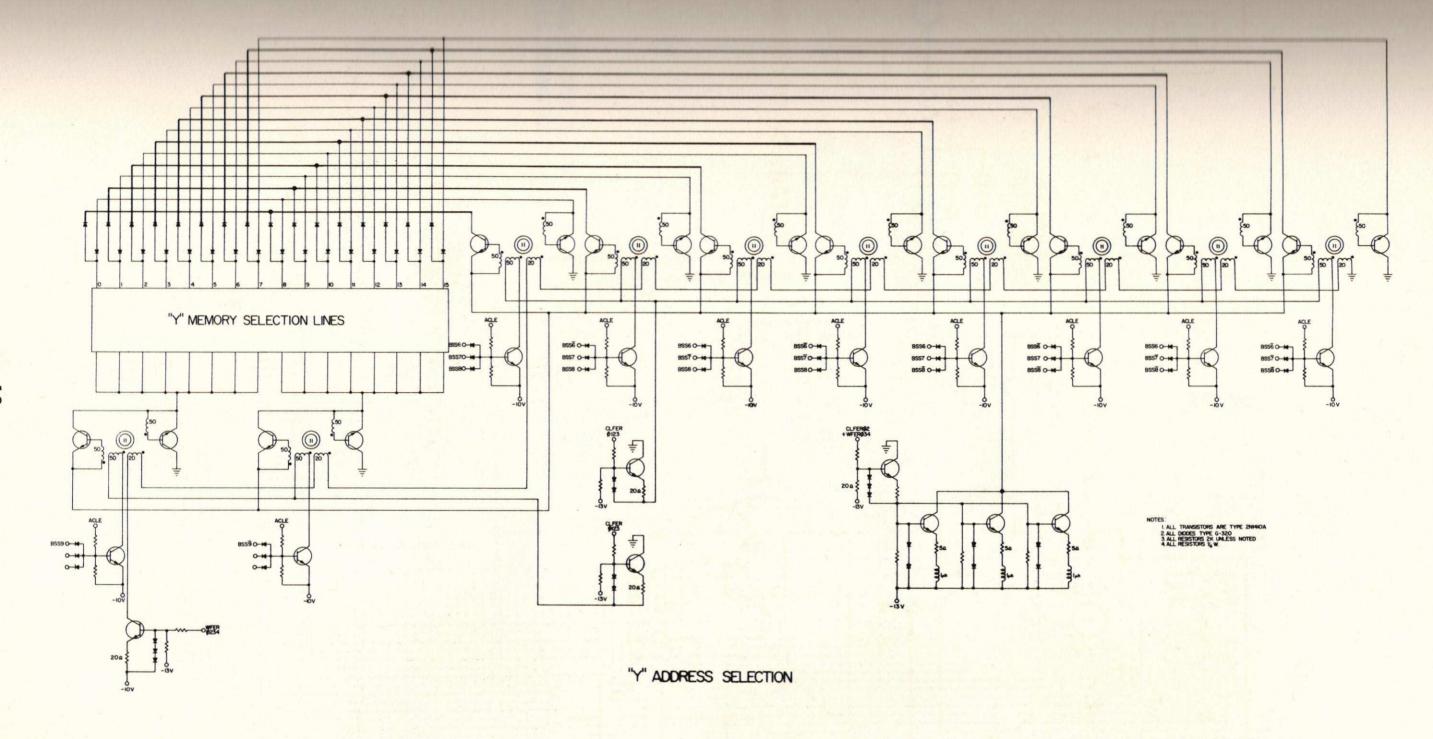

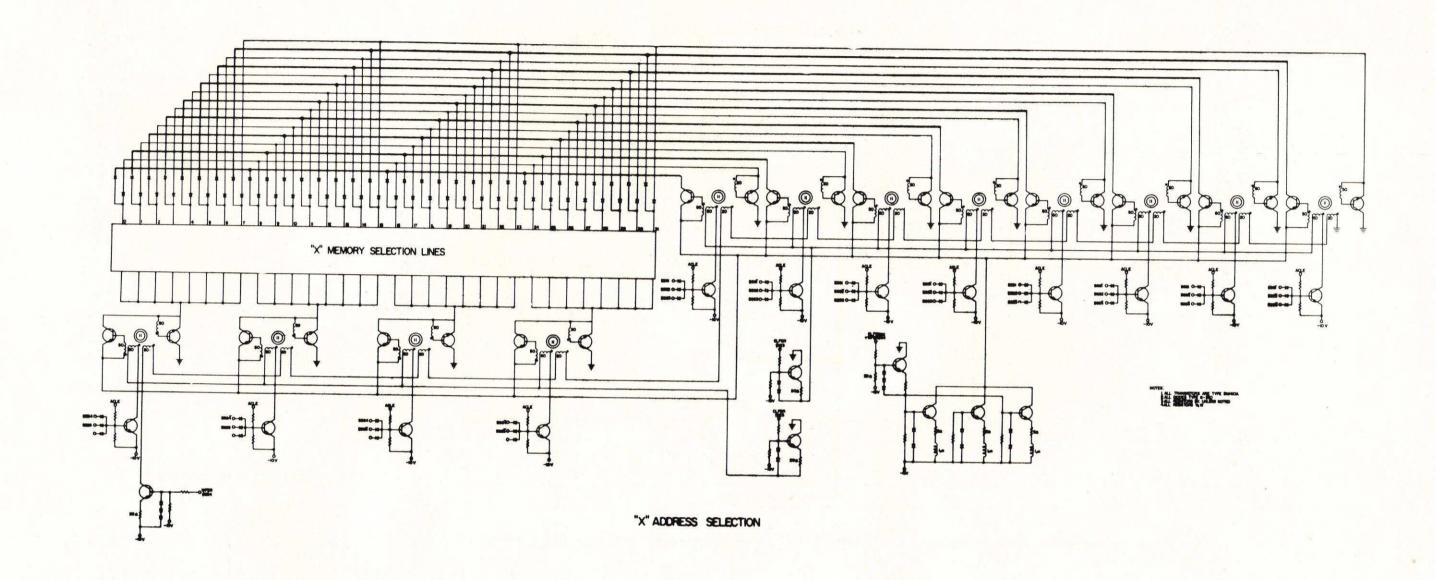

The address selection system discussed in MIT Instrumentation Laboratory Reports E-1074 (Erasable Ferrite Memory -Mod 3C Computer) was breadboarded and subsequently abandoned because of poor performance at the low-voltage operating margin (6 v). A transistor diode line selector, which performs well within the power supply excursion that the remainder of the computer must tolerate, is the present choice. In reference to Fig. 3, a simplified schematic of one element of the address selection system, it will be noted that line selection in the memory is performed in two steps. The output of the Erasable Memory Address Register (SS) is decoded to select two out of ten transistors represented in the Y dimension of memory Fig. 4, or two out of twelve transistors in the X dimension of memory Fig. 5. These four transistors are saturated by ACLE. CL FER  $m{\phi}_{123}$  is activated causing a current  $I_A$  to flow through winding  $W_1$ , switching core #1 to the 1 state. Transistor Q1 is saturated for a time determined by t =  $\frac{n\Delta I}{V_{\rm EB(SAT)}} \cong 3 \,\mu{\rm sec.}$  In a similar fashion, an

additional current source  $I_A$  which is activated by CL FER  $_{123}$  drives current through  $W_3$  of switch core #2 saturating Q3 for the same length of time. Current source  $I_M$  is activated at Q2 and the current produced here is steered through only one memory line in the proper direction via Q1 and Q3. It should be noted that the address of the word that has been interrogated has effectively been stored in the cores which are a part of the steering mechanism, thus permitting a change in the state of the Memory Address

Register (SS), after the Read portion of the cycle has been completed.

During the Write portion of the cycle; another current source WFER  $\phi_{234}$  is activated clearing all of the cores in the selection system to the 0 state. The cores switch in a time determined again by  $t = \frac{n \cancel{\phi}_1}{V_{EB}}$ , saturating Q2 and Q4. Current (SAT)

source I<sub>M</sub> is again activated and current is now steered in a direction opposite to the Read direction through the previously selected memory line.

Appropriate delays are provided between the selection of a steering core and the activation of the memory current source  $I_M$  to insure proper current steering in the presence of spurious coupling (noise) in the address selection cores. The Clear pulses supplied to these cores during Write time are adjusted in length so that the cores which have been addressed during Read time are completely switched during the Write portion of the cycle.

#### Driver Circuits

All of the various current sources used in the memory are characterized by their insensitivity to most of the transistor parameters and to power supply environment. They all have the same temperature coefficient, namely approximately 0.3%/°C of the nominal room temperature value of current.

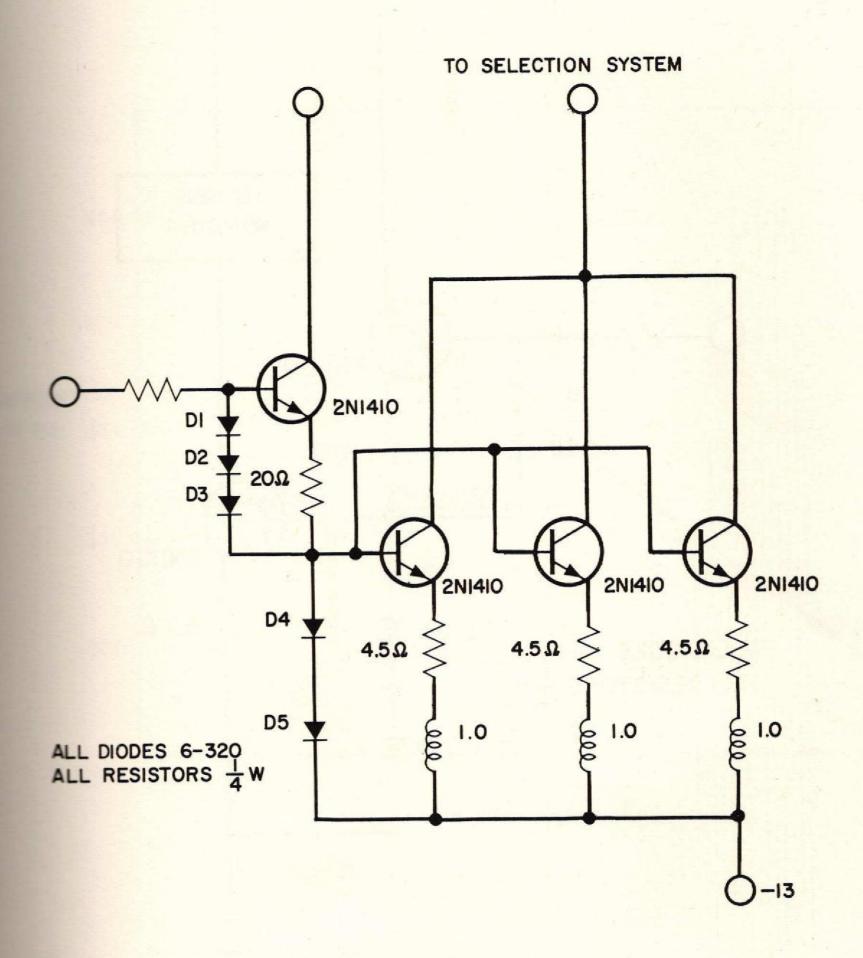

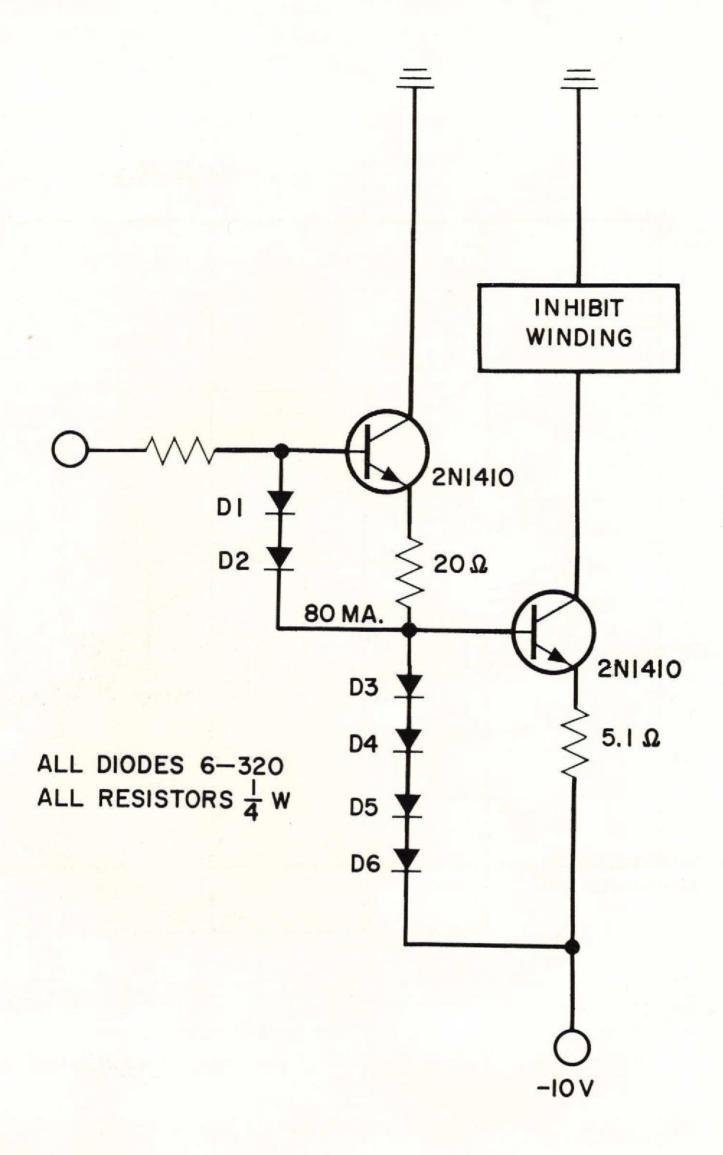

Referring to either the drawing of the Current Regulator, Fig. 6, or the Inhibit Driver, Fig. 7, one may observe that both of these consist of two similar circuits, one of which drives the other. Both of these circuits are current sources and each current source may be analysed in the following fashion. Consider the current source consisting of Diode D1, D2, D3, the 2N1410 and the  $20\Omega$  resistor. For a given collector current, the base-emitter voltage drop ( $V_{be}$ ) may be assumed constant. Hence a constant voltage will appear across the  $20\Omega$  resistor, producing a constant emitter current. The collector will be equal to  $\alpha$  I or approx-

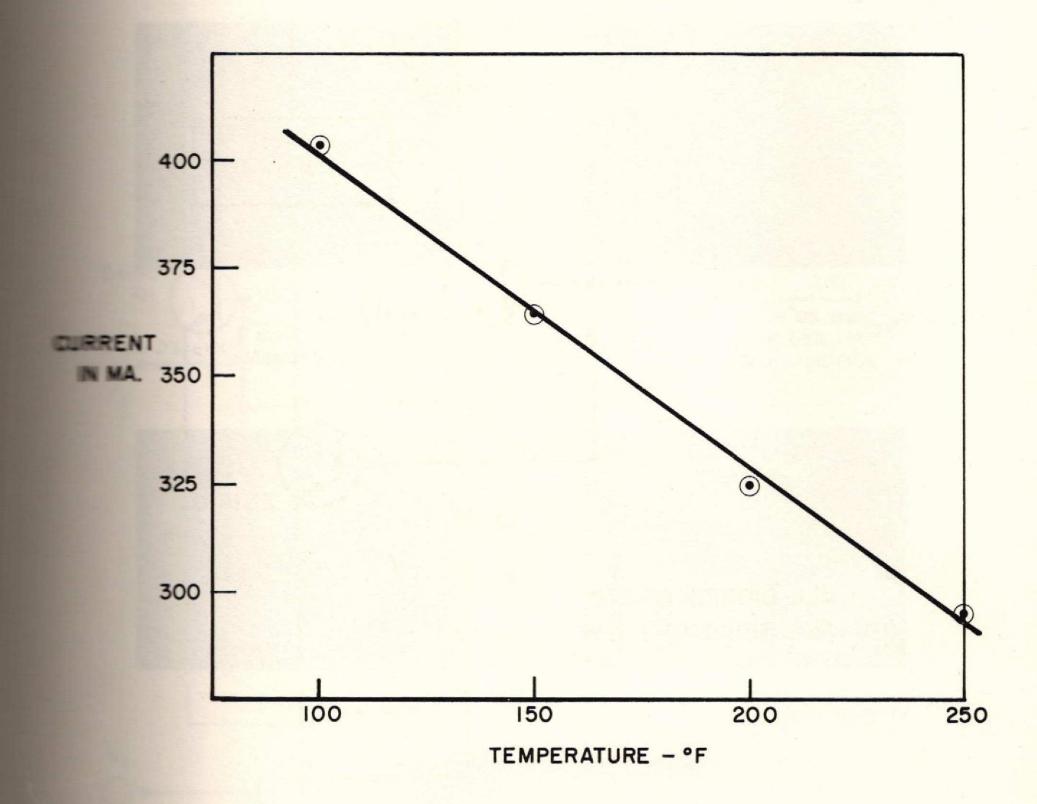

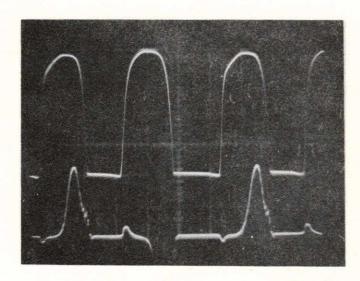

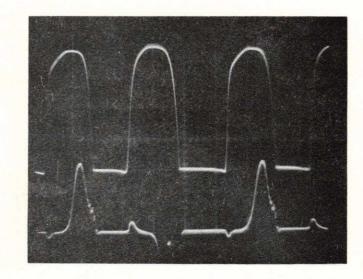

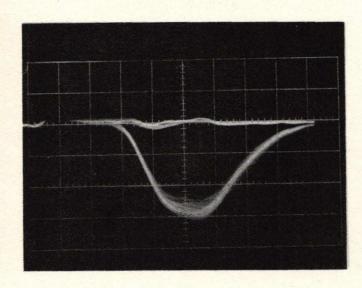

imately 98% of the emitter current. The various semiconductor voltage drops will vary as a function of temperature giving rise to a change in current as a function of temperature. A curve of  $I_{\rm C}$  = f(t) may be seen by referring to Fig. 8. The switching performance of the combination of the memory core and the driver over a  $100^{\rm O}{\rm F}$  temperature interval is shown in Fig. 9. It can be seen from this figure that there is no appreciable change in switching time, but there is an appreciable change in flux. The ceramicists at RCA are presently investigating the modification of the ferrite material to cure this condition. However, it should be noted that the material in its present condition is usable. (This will become obvious when the sense amplifier is discussed.)

Cascading two current sources, as is done in both the X and Y Regulator and the Inhibit Driver, has the effect of improving the performance of the current source by virtue of the diode current being held more constant. Rise time of the collector current is controlled by the addition of an inductance. The following equation describes the behavior of the emitter current.

$$I_e = \frac{V_{diode} - V_{be} + SL}{R}$$

The collector current is simply

$$I_c = \alpha I_e$$

This current will be independent of collector supply voltage as long as the transistor (s) is unsaturated. In saturation, the current will be determined by the supply voltage, the emitter resistance, and the saturation resistance of the transistor.

It will be noted from an inspection of the current source schematics that a number of silicon diodes are apparently redundant. These diodes were furnished to simplify packaging in Mod 3C, and coincidently enhance reliability.

#### Sense Amplifiers

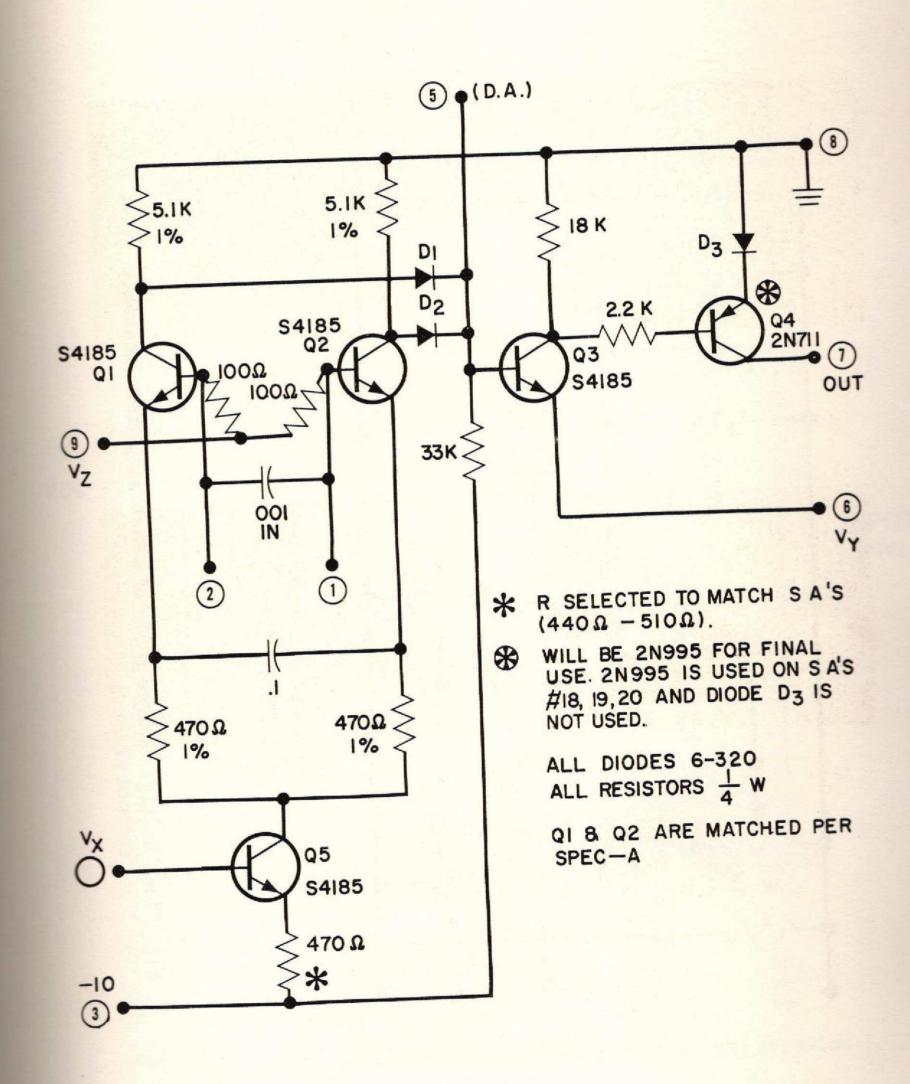

The sense amplifiers for the Mod 3C memory accept signals from either the fixed (Rope) memory or the erasable (Ferrite) memory. It must be able to reject large amplitude (~ 1 v ) common mode noise and amplify and rectify a core output signal of the order of 50 mv nominal in the presense of 10 mv of difference mode noise. The amplifier chosen for this application may be seen in Fig. 10. A differential amplifier Q1 and Q2, whose input is terminated by a network equal to the sense winding characteristic impedance, is the first stage of this amplifier. A current source, similar to the type previously described in the section dealing with the driver circuits, takes the place of the usual emitter resistor. This current establishes a constant woltage drop across the collector load resistors. The resistors used for emitter degeneration guarantee equal voltage drops at the collectors. Positive signals are OR'D together into the base of Q3 via diodes D1 and D2. The emitter of Q3 is held at a constant reference voltage (V<sub>V</sub>) with respect to ground. This voltage is adjusted to provide a threshold for noise rejection and signal acceptance. When the base-emitter junction of Q3 is forward blased, the transistor saturates, causing base current to flow in The collector of Q4 drives a standard Latch input equipped with an inhibiting gate. This gate is normally inhibited except during Read time to prevent spurious setting of the latches which constitute the Memory Output Register.

A special voltage source, Fig. 11, is furnished to drive the  $\mathbf{V}_{\mathbf{X}}$  and  $\mathbf{V}_{\mathbf{Y}}$  inputs. This voltage source has been designed to insure proper temperature tracking of the Difference Amplifier Collector rest potential and the threshold of conduction of Q3 in addition to compensating for the changes in voltage across the diodes and transistors as a function of temperature.

## Temperature Effects On 3C Erasable Memory Sense Amplifiers

The temperature compensation scheme used for the 3C Erasable Memory Sense Amplifier depends on the similarity and linearity of forward biased semiconductor junction voltage variations with temperature. It has been established elsewhere that such junction voltage drops are matched and vary linearity to within about 10% for similarly produced units. The temperature compensation to be described is valid only for the case where all critical junctions are operating in the same temperature environment.

An experimental analysis and some conclusions that may be drawn which tend to demonstrate the applicability of the sense amplifier to a wide temperature environment are as follows.

#### Experimental Results

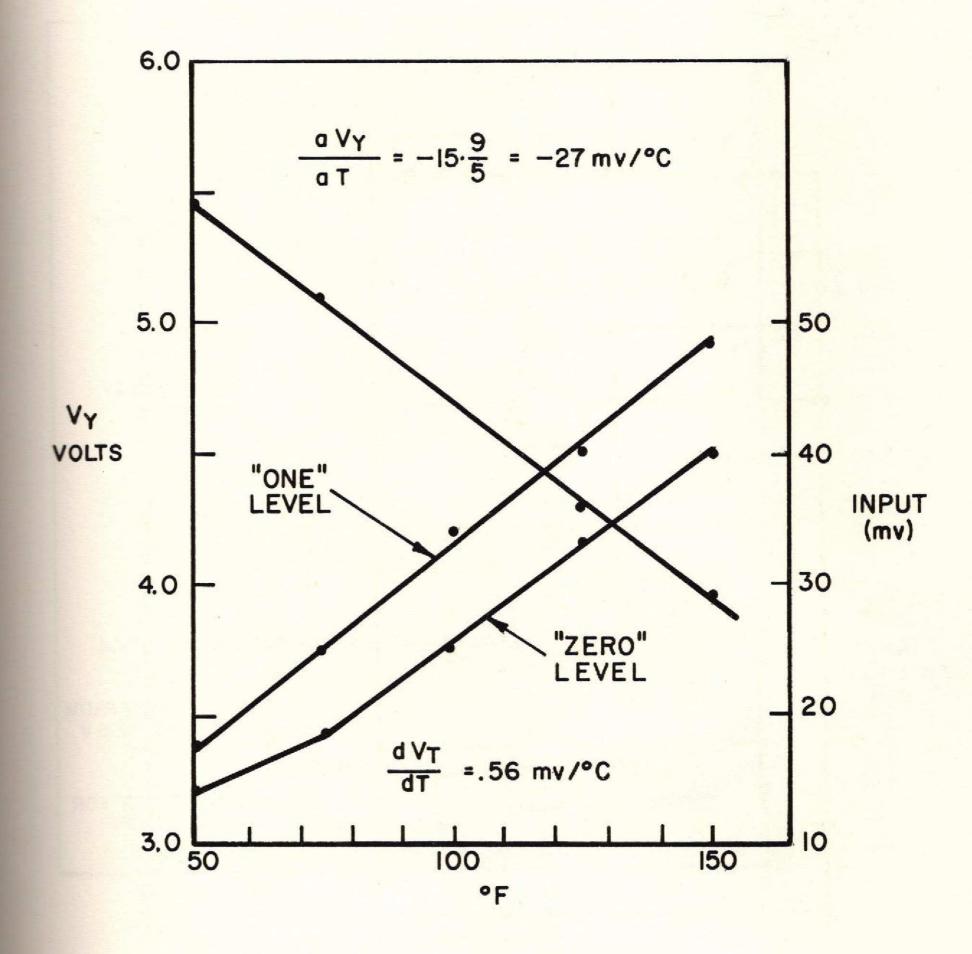

Figure 12 is a graph showing the temperature dependence required of  $\rm V_Y$  to maintain a temperature independent voltage threshold (1's signal). The linearity of this graph demonstrates the feasability of using a temperature varying voltage source to control the sensing threshold. The voltage source shown in Fig. 11 has two controls.  $\rm R_1$  sets the voltage  $\rm V_Y$  and thus the sensing threshold.  $\rm R_2$  sets the change in  $\rm V_Y$  with power supply voltage and thus adjusts sensing threshold for variations in power supply voltage. The incremental output impedance is about 3-50 and thus the voltage source can be common to all the sense amplifiers.

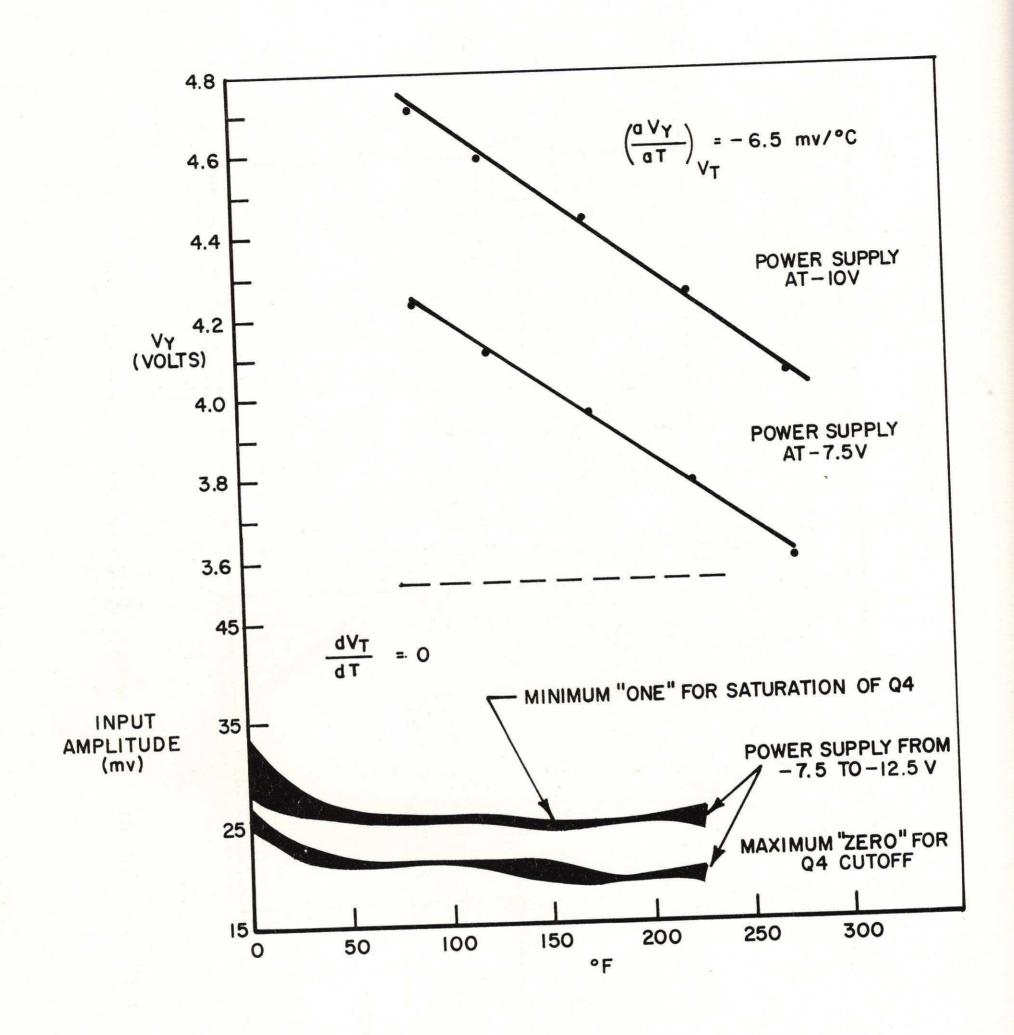

Figure 13 is a graph showing variation of sense threshold and  $V_{\Upsilon}$  with temperature. Figure 14 shows the temperature dependence of the temperature compensated sense amplifier. For estimating worst cases and also for designing temperature dependent thresholds, it is useful to compute two parameters from the data.

Let  $V_T$  = voltage input threshold. Then  $V_T = V_T (V_Y, T)$

$$\frac{dV_{T}}{dT} = \frac{\partial V_{T}}{\partial T} \bigg|_{V_{Y} = \text{const.}} \left( + \frac{\partial V_{Y}}{\partial T} \right) \left( \frac{\partial V_{T}}{\partial V_{Y}} \right)_{T = \text{const.}}$$

Since the graphs are linear,  $\left(\frac{\partial V_T}{\partial T}\right)_{V_Y}$  and  $\left(\frac{\partial V_T}{\partial V_Y}\right)_{T}$  are constants and may be evaluated at any  $V_Y$  and T from the graphs. From Fig. 2, we have:

$$\frac{dV_T}{dT} = 0.31 \frac{9}{5} = \left(\frac{\partial V_T}{\partial T}\right)_{V_Y} - 15 \times \frac{9}{5} \left(\frac{\partial V_T}{\partial V_Y}\right)_T$$

From Fig. 3:

$$\frac{dV_{T}}{dT} = 0 = \left(\frac{\partial V_{T}}{\partial T}\right)_{V_{Y}} - 7 \left(\frac{\partial V_{T}}{\partial V_{Y}}\right)_{T}$$

Solving, we have

$$\left(\frac{\partial V_T}{\partial T}\right)_{V_Y} = -0.196 \text{ mv/}^{\circ}\text{C}$$

$$\left(\frac{\partial V_{T}}{\partial V_{Y}}\right)_{T} = -0.028 \approx \frac{1}{G_{D}}$$

Where  $G_D$  is the voltage gain of the differential amplifier.

#### Conclusions

When the differential voltage gains of all the sense amplifiers are matched at the operating point, it can be expected that a worst case mismatch in temperature coefficients of the sense amplifiers will be about 10% of

$$\left(\frac{\partial V_T}{\partial T}\right)_{V_Y}$$

or about 0.02 mv/ $^{\rm O}$ C. Thus, temperature variations in sensing thresholds can be held to about 2 mv over a range of  $100^{\rm O}$ C. Other effects, such as variation of threshold with power supply voltage, mismatch in  $G_{\rm D}$ , etc. give an estimated maximum combined mismatch of perhaps 8 to 10 mv over the total range of power supply voltage and temperature. Since all of these effects are independent of the threshold selected, we can operate at a threshold 1 of 50 mv with a signal to noise ratio as low as 2:1 and a variability of 20% in the sizes of ones and zeros. For smaller ampitude inputs these margins would be reduced.

#### Further Work

Roger Lamson has recently shown that the total flux switched by a ferrite core has a large negative temperature dependence. Since in a coincident current memory it is necessary to have the drive currents track with  ${\rm H_{c}}$ , this means that the voltage input to the sense amplifier will decrease with temperature. Preliminary data for the ferrite cores used in 3C show a linear temperature dependence that is

$$E_{out} = 72 - 0.45T \text{ mv}$$

T measured in  ${}^{O}C$

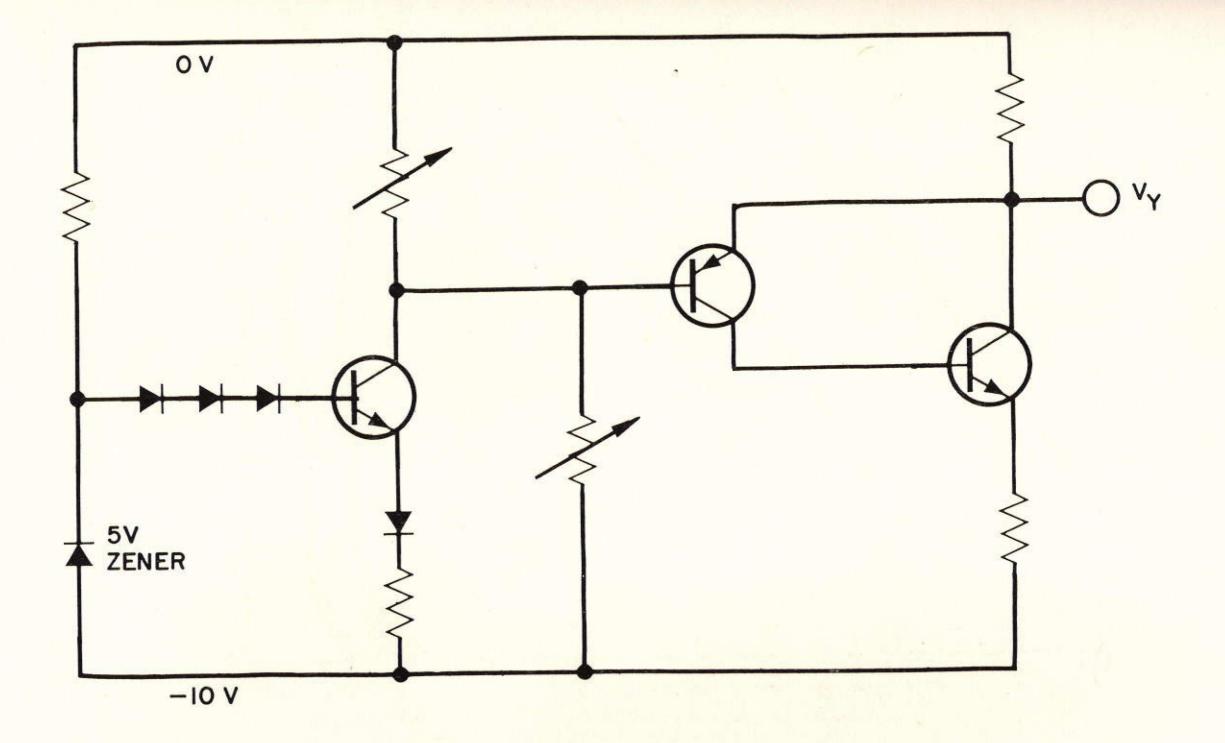

This data is over the range from  $27^{\circ}C$  to  $90^{\circ}C$ . Compensation for this effect would have to be done in the sense amplifier since drive current tracks with  $H_c$ . A linear temperature compensation with  $V_Y$  would require that

$$\frac{dV_{T}}{dT}$$

= - 0. 45 = - 0. 196 - 0. 028  $\frac{\partial V_{Y}}{\partial T}$

or

$$\frac{\partial V_Y}{\partial T} = +9 \text{ mv/}^{\circ}C$$

The circuit shown in Fig. 11 is incapable of producing a  $V_Y$  with a positive temperature coefficient, therefore a different type of circuit would have to be used. Since a 5 v zener diode has a very small temperature coefficient, a circuit like that in Fig. 15 could be used. Actual design will be done after the ferrite characteristics are more certainly established.

At present the sense amplifiers in computer 3C are being used for both the rope memory and the erasable memory with transformers being used to match and isolate inputs. The rope cores produce outputs which are nominally about 2  $\mu$ sec wide vs. 0.6  $\mu$ sec for the ferrite memory. For the same probability of sensing a 1, it is necessary to apply a smaller nominal input from the rope cores, because of the sense amplifier's frequency response characteristic. Since the rope drivers have a linear negative temperature coefficient and since  $\frac{\partial E}{\partial I} = \frac{\phi}{S}$  (where  $\phi$  and S are characteristics of the tape wound cores) it is possible to achieve a temperature varying output from the rope cores which matches the temperature tracking of the sense amplifier. This will be done for the 3C computer.

Fig. 1 The 512 word ferrite memory

Fig. 2 The 512 word memory and selection electronics

Fig. 3 Memory current steering simplified schematic

Fig. 4 The Y address selection

Fig. 5 The X address selection

Fig. 6 Current regulator (X and Y axes)

Fig. 7 Inhibit driver (Z plane)

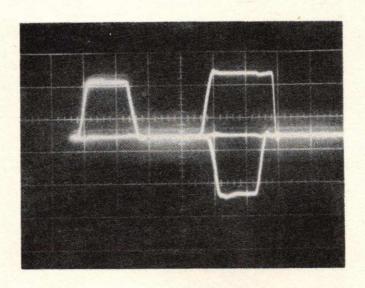

Fig. 8 I=f(t), current regulator

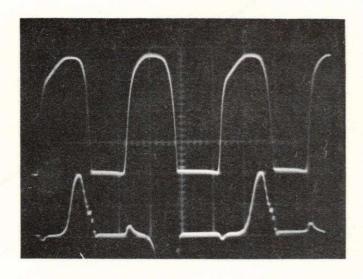

a) TEMP. 80°F

TOP: ,050 VOLTS/CM

BOTTOM: 100 MA/CM

X 1μ SEC/CM

b) TEMP. 100°F

TOP: .050 VOLT/CM

BOTTOM: 100 MA/CM

X I µ SEC/CM

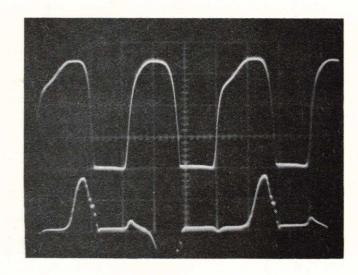

c) TEMP. 150°F

d) TEMP. 200°F.

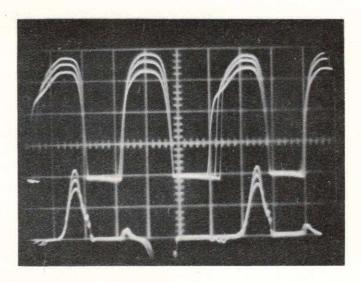

e) 200°F, 150°F, 100°F

Fig. 9 Combination of ferrite core and driver, illustrating constant T<sub>S</sub>

Fig. 10 Sense amplifier erasable memory

Fig. 11 Voltage source (part of sense amplifier erasable memory)

Fig. 12 Initial data with wrong temperature compensation

Fig. 13 Variation of sense threshold and  $V_Y$  with temperature

Fig. 15 Circuit for V<sub>Y</sub> with positive temperature coefficient

Appendix I

# HIGH DENSITY STACK 32 $\times$ 16 $\times$ 16

#### 233M 1

$$I_r/_2 = I_w/_2 = I_{mhibit} = 400 \text{ ma}$$

$T_r = 0.5 \mu \text{secs}$

$T_d = 3 \mu \text{sec} (50-50)$

$$Temperature = 100^{\circ}\text{C}$$

| Plane # | uV <sub>1</sub> (mv)             | Plane<br>Noise (mv) | T <sub>p</sub> (µsec)      | T <sub>s</sub> (µsec)          |

|---------|----------------------------------|---------------------|----------------------------|--------------------------------|

| 1       | 60 - 90<br>60 - 90               | . 8<br>8            | 0.92 - 1.00<br>0.94 - 1.00 | 1.42 - 1.58<br>1.44 - 1.56     |

| 2       | 60 - 88<br>60 - 88               | 7<br>9              | 0.94 - 1.00<br>0.88 - 1.00 | 1.46 - 1.56<br>1.46 - 1.60     |

| 3       | 60 <b>-</b> 92<br>64 <b>-</b> 90 | 8                   | 0.92 - 0.98<br>0.92 - 0.98 | 1.44 - 1.56<br>1.44 - 1.56     |

| 4       | 60 <b>-</b> 90<br>60 <b>-</b> 88 | 8 7                 | 0.92 - 0.98<br>0.92 - 0.98 | 1.46 - 1.58<br>1.44 - 1.56     |

| 5       | 56 - 88<br>56 - 88               | 8                   | 0.94 - 1.00<br>0.94 - 1.00 | 1.44 - 1.60<br>1.44 - 1.56     |

| 6       | 60 - 92<br>58 - 90               | 8                   | 0.92 - 0.98<br>0.92 - 0.98 | 1.46 - 1.58<br>1.44 - 1.56     |

| 7       | 56 <b>-</b> 94<br>62 <b>-</b> 96 | 7<br>8              | 0.92 - 1.00<br>0.94 - 1.00 | 1.44 - 1.56<br>1.44 - 1.56     |

| 8       | 64 <b>-</b> 94<br>58 <b>-</b> 90 | 8                   | 0.90 - 0.98<br>0.94 - 1.00 | 1.44 - 1.58<br>1.46 - 1.60     |

| 9       | 56 <b>-</b> 90<br>52 <b>-</b> 88 | 8<br>7              | 0.94 - 1.00<br>0.92 - 1.00 | 1.46 - 1.58<br>1.44 - 1.60     |

| 10      | 62 <b>-</b> 90<br>60 <b>-</b> 88 | 8<br>8              | 0.94 - 0.98<br>0.92 - 1.00 | 1. 46 - 1. 56<br>1. 46 - 1. 56 |

| 11      | 60 <b>-</b> 88<br>56 <b>-</b> 90 | 8                   | 0.92 - 1.00<br>0.92 - 1.00 | 1. 44 - 1. 56<br>1. 46 - 1. 58 |

| 12      | 60 - 88<br>58 - 88               | 8<br>8              | 0.88 - 1.00<br>0.90 - 1.00 | 1.50 - 1.66<br>1.44 - 1.62     |

| 13      | 60 <b>-</b> 80<br>58 <b>-</b> 80 | 9<br>9              | 0.94 - 1.00<br>0.92 - 1.00 | 1.48 - 1.64<br>1.48 - 1.60     |

| 14      | 60 <b>-</b> 88<br>56 <b>-</b> 88 | 8<br>8              | 0.92 - 0.98<br>0.92 - 1.00 | 1.44 - 1.56<br>1.44 - 1.56     |

| 15      | 58 <b>-</b> 80<br>60 <b>-</b> 80 | 9                   | 0.92 - 1.00<br>0.92 - 1.00 | 1. 48 - 1. 62<br>1. 48 - 1. 64 |

| 16      | 60 - 84<br>60 - 80               | 9                   | 0.92 - 0.98<br>0.92 - 1.00 | 1. 48 - 1. 64<br>1. 44 - 1. 62 |

# HIGH DENSITY STACK 32 $\times$ 16 $\times$ 16

# 233M1 Cores

$$I_r/_2 = I_w/_2 = I_{\text{mhibit}} = 400 \text{ ma}$$

$$T_r = 0.5 \mu sec$$

$T_d = 3 \mu sec (50 - 50)$

Temperature = 0°C

|         |                                  | Temp                |                                           |                                                 |  |

|---------|----------------------------------|---------------------|-------------------------------------------|-------------------------------------------------|--|

| Plane # | uV <sub>1</sub> (mv)             | Plane<br>Noise (mv) | T <sub>p</sub> (μsec)                     | T <sub>s</sub> (µsec)                           |  |

| 1       | 56 - 80<br>56 - 80               | 6 6                 | 0.92 - 0.98<br>0.92 - 0.98<br>0.94 - 1.00 | 1. 38 - 1. 48<br>1. 40 - 1. 48<br>1. 36 - 1. 50 |  |

| 2       | 56 - 80<br>54 - 80               | 6<br>6              | 0.94 - 0.98<br>0.94 - 0.98                | 1.36 - 1.48<br>1.36 - 1.48                      |  |

| 3       | 52 <b>-</b> 82<br>56 <b>-</b> 80 | 6<br>6              | 0.94 - 0.98                               | 1.36 - 1.48<br>1.36 - 1.48                      |  |

| 4       | 52 - 88<br>54 - 80               | 6                   | 0.96 - 0.98<br>0.94 - 0.98                | 1.36 - 1.50<br>1.36 - 1.48                      |  |

| 5       | 52 - 80<br>52 - 80               | 9<br>6              | 0.94 - 0.98<br>0.92 - 0.98                | 1.38 - 1.50<br>1.36 - 1.48                      |  |

| 6       | 56 <b>-</b> 80<br>52 <b>-</b> 80 | 9<br>6              | 0.94 - 0.98<br>0.96 - 0.98                | 1. 36 - 1. 50<br>1. 36 - 1. 48                  |  |

| 7       | 52 - 84<br>52 - 84               | 8 6                 | 0.94 - 0.98<br>0.94 - 0.98                | 1.36 - 1.50<br>1.36 - 1.48                      |  |

| 8       | 52 <b>-</b> 84<br>56 <b>-</b> 84 | 8                   | 0.94 - 0.98<br>0.94 - 0.98                | 1. 36 - 1. 48<br>1. 36 - 1. 48                  |  |

| 9       | 54 - 82<br>50 - 80               | 7<br>6              | 0.94 - 0.98<br>0.94 - 0.98                | 1.36 - 1.48<br>1.36 - 1.48                      |  |

| 10      | 56 - 80<br>52 - 76               | 6<br>6              | 0.94 - 0.98<br>0.94 - 0.98                | 1.36 - 1.50<br>1.36 - 1.48                      |  |

| 11      | 54 - 80<br>50 - 78               | 6<br>6              | 0.96 - 0.98<br>0.94 - 0.98                | 1.36 - 1.50<br>1.36 - 1.48                      |  |

| 12      | 48 - 72<br>48 - 80               | 6                   | 0.94 - 0.98<br>0.90 - 0.98                | 1. 36 - 1. 50<br>1. 36 - 1. 48                  |  |

| 13      | 48 - 72<br>48 - 72               | 6<br>6              | 0.90 - 0.98<br>0.94 - 0.98                | 1.36 - 1.50<br>1.36 - 1.50                      |  |

| 14      | 56 - 80                          | 6<br>6              | 0.94 - 0.98<br>0.96 - 0.98                | 1. 36 - 1. 50<br>1. 36 - 1. 48                  |  |

| 15      | 50 - 80<br>46 - 78               | 6<br>6              | 0.92 - 0.98<br>0.88 - 0.96                | 1.36 - 1.50<br>1.36 - 1.50                      |  |

| 16      | 46 - 78<br>48 - 78<br>48 - 64    | 6<br>6              | 0.90 - 0.96<br>0.92 - 0.96                | 1.36 - 1.50                                     |  |

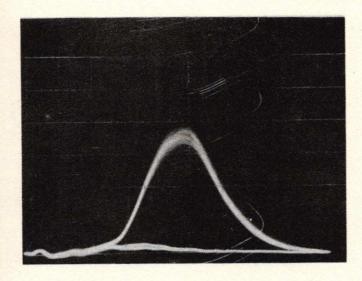

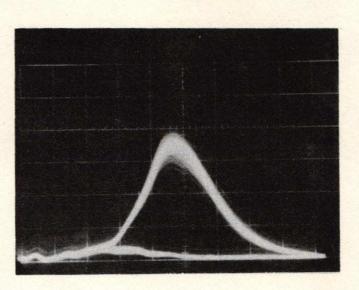

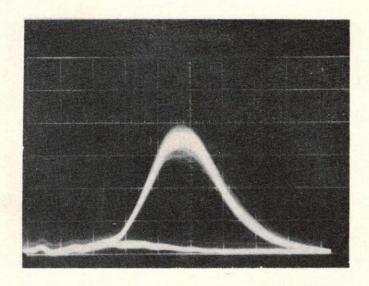

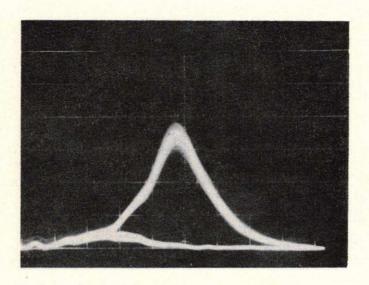

a) TEMP. 100°C SW TIME 0.2 μSEC/CM CAL 20 MV/CM

b)

c) TEMP. 97°C SW TIME 0.2 µSEC/CM CAL 20 MV/CM

d) TEMP. 60°C SW TIME 0.2 µSEC/CM CAL 20 MV/CM

Fig. A-1

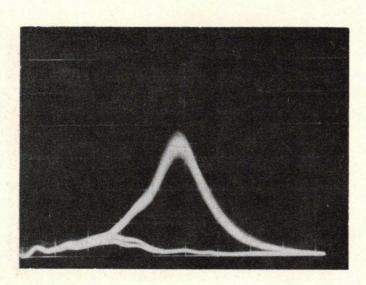

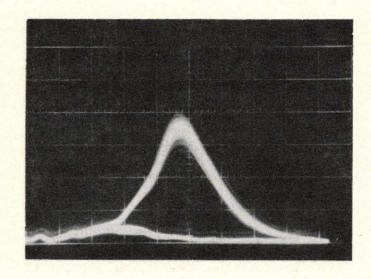

e' TEMP. 80° C SUN TIME .2 μ SEC/CM CAL 20 MV/CM

f) TEMP. 20°C SUN TIME . 2 μSEC/CM CAL 20 MV/CM

g) TEMP. O°C SW TIME .2 μ SEC/CM CAL 20 MV/CM

h) TEMP. 40°C SW TIME .2 µSEC/CM CAL 20 MV/CM

Fig. A-1 (cont.)