Volume I Final Report Contract NAS-9-11778

ADVANCED SOFTWARE TECHNIQUES

FOR

DATA MANAGEMENT SYSTEMS

February 1972

STUDY OF SOFTWARE ASPECTS OF THE PHASE B SPACE SHUTTLE AVIONICS SYSTEM

Intermetrics Technical Report #12-72

#### Foreword

This document is the final report of a study entitled "Advanced Software Techniques for Data Management Systems". The study was focused on an evaluation of key aspects of software for the Phase B Space Shuttle avionics system including the executive system, software verification, programming languages and computer features. This work was sponsored by the NASA Manned Spacecraft Center in Houston, Texas, under Contract NAS-9-11778. It was performed by Intermetrics, Inc., Cambridge, Mass. over the period of 16 June 1971 to 1 February 1972, under the technical direction of Mr. Joseph A. Saponaro. The technical monitor for the Manned Spacecraft Center was Mr. Donald Barron, EB5.

This final report is presented in three volumes:

Volume I: Software Aspects of the Phase B Space Shuttle Avionics System

Volume II: Space Shuttle Flight Executive System: Functional Design

Volume III: Programming Language Characteristics and Comparison Reference

The publication of this report does not constitute approval by NASA of the findings or conclusions contained therein.

### ACKNOWLEDGEMENT

Several Intermetrics personnel contributed to the preparation of material and the publication of this report:

Dr. Fred H. Martin

Mr. Alex L. Kosmala

Mr. Daniel J. Lickly

Mr. Thomas A. James Dr. James T. Pepe

Mr. Woodrow H. Vandever

Mr. James H. Flanders

# Table of Contents

| CHAP' | rer l c | Objectives and Summary                          | . 1  |

|-------|---------|-------------------------------------------------|------|

| 1.1   | Introdu | action                                          | 1    |

| 1.2   |         | Objectives and Scope                            | 1    |

| 1.3   |         | ound and Approach to the Study                  | 3    |

|       | -       | Background                                      | 3    |

|       | 1.3.2   | Approach                                        | 4    |

| 1.4   |         | ummary and Review                               | 5    |

|       | 1.4.1   | Executive System Design Task                    | 5    |

|       | 1.4.2   | Software Verification Task                      | 6    |

|       | 1.4.3   | Space Shuttle Phase B Review Task               | 8    |

|       |         | Higher Order Programming Language Task          | 9    |

|       | 1.4.5   |                                                 | 10   |

|       | ,       |                                                 |      |

| CHAP  | TER 2   | Software Verification                           | 15   |

|       | Introd  |                                                 | 15   |

| 2.1   |         | ements and Specifications                       | 18   |

| 2.2   | -       | The Formulation of Software Specifications      | 19   |

|       |         | Necessary Detail Within Software Specifications | 21   |

|       |         |                                                 | 22   |

|       | 2.2.3   |                                                 | 27   |

| 2.3   |         | m Design  Program Structure                     | 27   |

|       | 2.3.1   |                                                 | 30   |

|       |         | Program Modularity                              | 32   |

|       | 2.3.3   |                                                 | 37   |

|       | 2.3.4   |                                                 | 41   |

| 2.4   |         | mentation: Code and Test                        | 41   |

|       | 2.4.1   | Implementation of System Programs               | 41   |

|       | 2.4.2   | -                                               | . 51 |

|       | 2.4.3   | Program Confidence: Test Philosophy             | J.   |

| 2.5  | Verifi | cation                                                                            | 56   |

|------|--------|-----------------------------------------------------------------------------------|------|

|      | 2.5.1  | "Feedback" and "Feed-forward"                                                     | 57   |

|      | 2.5.2  |                                                                                   | 59   |

|      | 2.5.3  | Phase 4: Verification through Hardware                                            | 60   |

|      | 2.5.4  | Independent Verification                                                          | 62   |

|      | 2.5.5  | Special Testing                                                                   | 64   |

|      |        | •                                                                                 |      |

| СНАР | TER 3  | Software Verification Facilities                                                  | 67   |

| 3.1  | Introd | uction                                                                            | 67   |

| 3.2  |        | ties Versus Levels of Development                                                 | 68   |

|      | 3.2.1  |                                                                                   | 68   |

|      | 3.2.2  | Phase 2: Implementation Code and Test                                             | 69   |

|      | 3.2.3  | Phase 3: Verification through Software                                            | 69   |

|      |        | Phase 4: Verification through Hardware                                            | 71   |

| 3.3  |        | re Development Facility                                                           | 73   |

|      | 3.3.1  |                                                                                   | 73   |

|      | 3.3.2  | Advantages of Interpretive Simulation                                             | 74   |

|      | 3.3.3  |                                                                                   | 75   |

|      | 3.3.4  | Experience                                                                        | 77   |

|      | 3.3.5  | Avionics Environment Simulator                                                    | 78   |

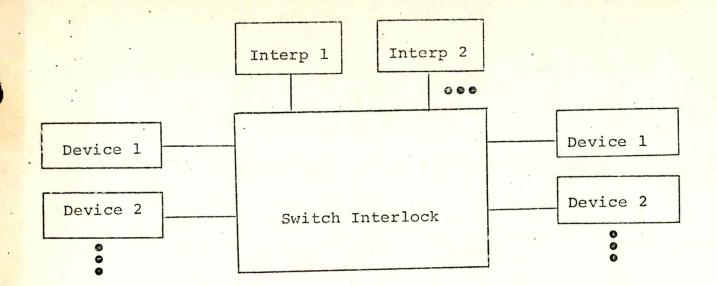

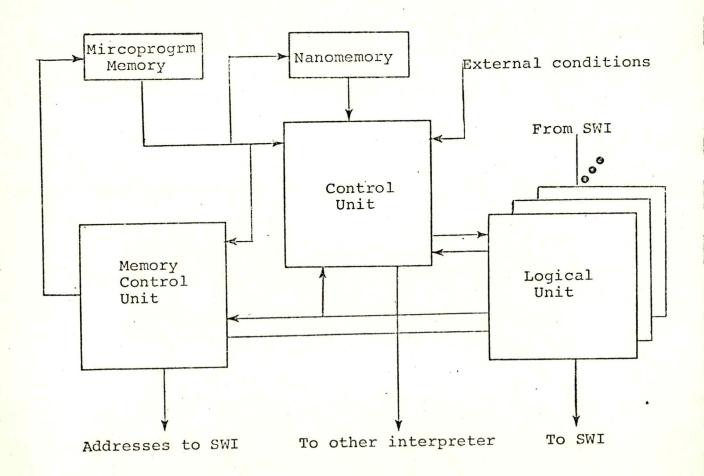

|      | 3.3.6  | Redundancy Simulation .                                                           | 80   |

|      | 3.3.7  | Space Shuttle Simulation Speed Improvements                                       | 81   |

| 3.4  | Direct | Use of Higher Order Language on the Host Machine                                  | 81   |

| 3.5  |        | rison of Interactive and Batch Computer Facilities<br>nuttle Software Development | 82   |

| CHAE | TER 4  | Space Shuttle Phase B Design Review                                               | 85   |

| 4.1  | Introd | luction and Scope                                                                 | 85   |

| 4.2  | Summar | ry of Phase B Designs                                                             | 8.6  |

| 4.3  |        | al Software Implications of Phase B Designs                                       | 91   |

|      |        | Centralized Computer Software Management Problem                                  | . 91 |

|      |        | I/O Timing Difficulties                                                           | 94   |

|      | 4.3.3  | Failure Identification, Isolation, and Reconfiguration                            | 95   |

| 4.4  |                                                           | re Implications of Differences Between ase B Contractor System Baselines | 95   |

|------|-----------------------------------------------------------|--------------------------------------------------------------------------|------|

|      | 4.4.1                                                     | General                                                                  | 95   |

|      | 4.4.2                                                     | Computer Organization in Redundant Operation                             | 96   |

|      | 4.4.3                                                     | Operating Memory                                                         | 98   |

|      | 4.4.4                                                     | Secondary Storage and Utilization                                        | 99   |

|      | 4.4.5                                                     | Management of Redundant Subsystems by the Central Computer               | 100  |

|      | 4.4.6                                                     | Display Subsystem Interface to Computer                                  | 100  |

| 4.5  | Onboar                                                    | d Checkout Software                                                      | 102  |

|      | 4.5.1                                                     | Overview                                                                 | 102  |

|      | 4.5.2                                                     | Subsystem Monitoring                                                     | 104  |

|      | 4.5.3                                                     | Fault Detection                                                          | 105  |

|      |                                                           |                                                                          |      |

| CHAP | TER 5                                                     | Higher Order Programming Languages                                       | 109  |

| 5.1  | Introd                                                    | uction                                                                   | 109  |

| 5.2  | "Languages" on the Space Shuttle                          |                                                                          | 110  |

|      | 5.2.1                                                     | Role of the Crew Language                                                | 110  |

|      | 5.2.2                                                     | Crew Language Requirements                                               | 112  |

| 5.3  | Justif<br>Langua                                          | ication for Using a Higher Order Programming                             | 113  |

|      | 5.3.1                                                     | Higher Order Programming Language Experience                             | 115  |

| 5.4  | Single Compiler Approach                                  |                                                                          | 116  |

|      | 5.4.1                                                     | Systems Programming                                                      | 117  |

| 5.5  | Advantages of the HOL and Compiler to Software Modularity |                                                                          | 120  |

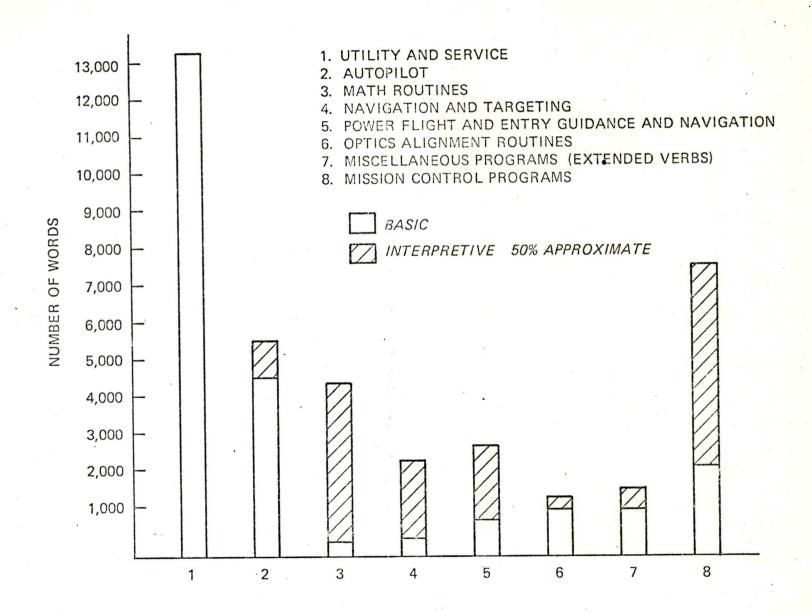

|      | 5.5.1                                                     | Apollo Experience                                                        | 120  |

|      | 5.5.2                                                     | Software Modularity                                                      | 121  |

|      | 5.5.3                                                     | Additional Advantages of the HOL Approach                                | 129  |

|      | 5.5.4                                                     | Summary                                                                  | 130  |

| 5.6  | Checko                                                    | out Languages                                                            | 131  |

| 5.7  | HOL Co                                                    | mpiler Implementation                                                    | .131 |

|      | 5.7.1                                                     | Compiler Problem                                                         | 131  |

|      | 5.7.2                                                     | Approaches to Efficient Code Generation                                  | 132  |

|      | 573                                                       | Implementation Factors                                                   | 134  |

| CHAP' | rer 6 F             | light Computer Features                                          | 139        |

|-------|---------------------|------------------------------------------------------------------|------------|

| 6.1   | Introduction        |                                                                  | 139<br>140 |

| 6.2   | Scope and Objective |                                                                  |            |

| 6.3   |                     | ound to Computer Features                                        | 140        |

|       |                     | Flight Computer Generation                                       | 140        |

|       | 6.3.2               | Aerospace Software Characteristics                               | 143        |

| 6.4   |                     | ed Computer Features .                                           | 143        |

|       | 6.4.1               | Higher Order Language Processing                                 | 144        |

|       | 6.4.2               | Stacks                                                           | 146        |

|       | 6.4.3               | Microprogramming                                                 | 146        |

|       | 6.4.4               | Descriptors                                                      | 149        |

|       | 6.4.5               | Run Time Diagnostic Aids                                         | 150        |

| 6.5   | Genera:             | l Computer Features                                              | 152        |

|       | 6.5.1               | •                                                                | 152        |

|       | 6.5.2               | Static Versus Dynamic Addressing                                 | 156        |

|       |                     | Subroutine Linkage                                               | 159        |

|       |                     | Floating Point                                                   | 161        |

|       | 6.5.5               | Unimplemented Instructions                                       | 164        |

|       | 6.5.6               | Short Form Instructions                                          | 165        |

|       | 6.5.7               | Differing Memory Speeds                                          | 165        |

|       | 6.5.8               | 1 Change to mighting                                             | 166        |

|       | 6.5.9               |                                                                  | 166        |

|       | 6.5.10              | Selection Criteria                                               | 168        |

| 6.6   | Benchm              | ark Programs as an Aid in Computer Selection                     | 169        |

|       | 6.6.1               | Background                                                       | 169        |

|       | 6.6.2               | Hand Compiled HOL Benchmarks                                     | 170        |

|       | 6.6.3               | Statistical Approach                                             | 171        |

|       | 6.6.4               | _                                                                | 173        |

|       | 6.6.5               | 1 2 2                                                            | 174        |

|       |                     |                                                                  |            |

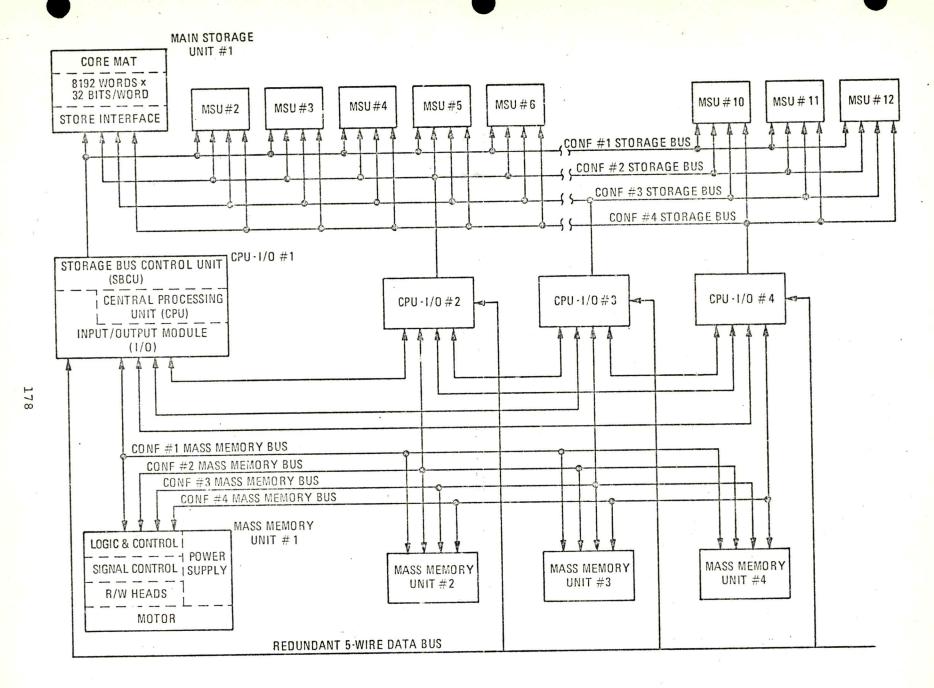

| App   | endix A             | Phase B North American Rockwell (NAR)<br>Baseline System Summary | 177        |

| 1.    | Introdu             | action                                                           | 177        |

|       |                     | And the second second                                            | 7 77       |

General System Summary

| 3.  | Hardware Configuration (IBM-Generated)                                            | 177 |  |

|-----|-----------------------------------------------------------------------------------|-----|--|

| 4.  | Software Requirements                                                             | 183 |  |

| 5.  | Size and Speed Estimates                                                          | 187 |  |

| 6.  | Equipment Interfacing with DMS and Data Requirements                              | 189 |  |

|     |                                                                                   |     |  |

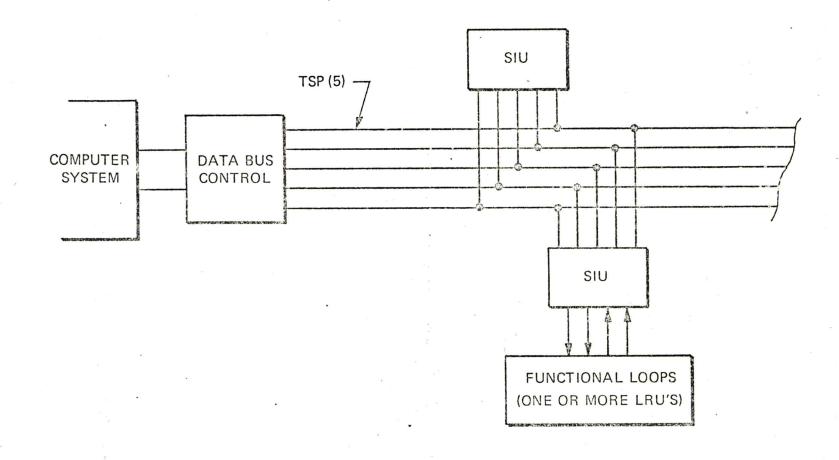

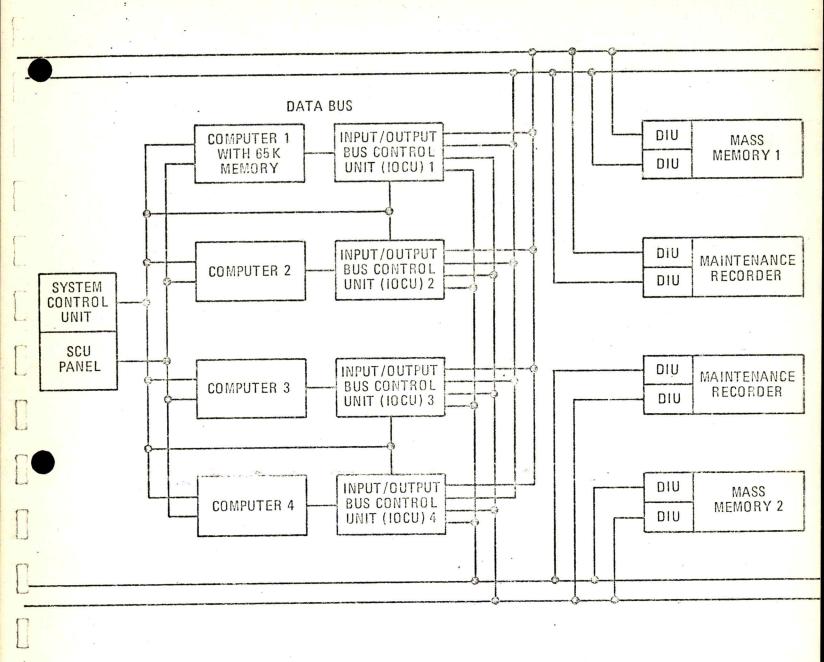

| App | endix B McDonnell-Douglas Aircraft Corp. (MDAC) Phase B Baseline Avionics Systems | 193 |  |

| 1.  | Introduction                                                                      | 193 |  |

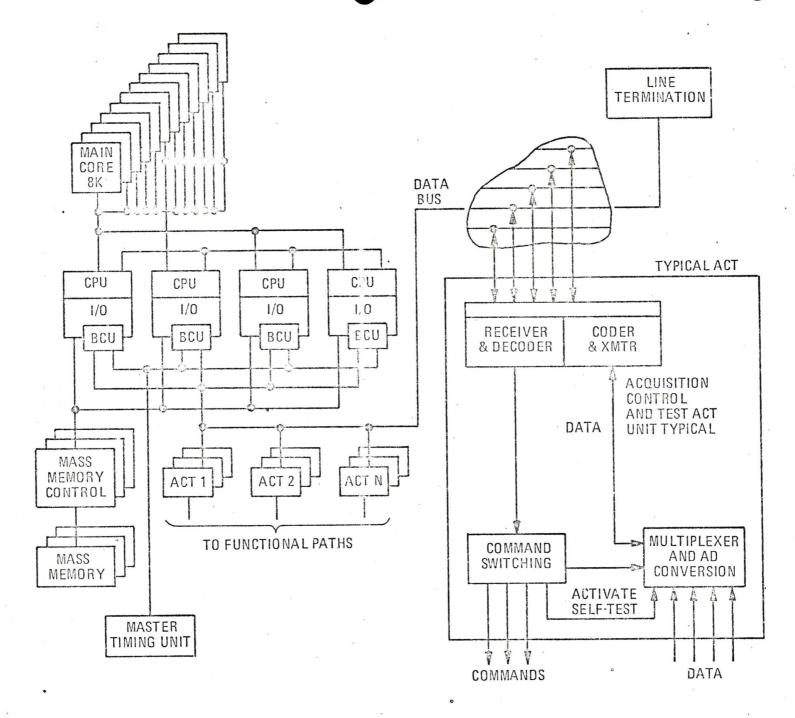

| 2.  | General System Architecture                                                       | 193 |  |

| 3.  | Data Management Computer System                                                   | 194 |  |

| 4.  | Software in MDAC Baseline                                                         | 197 |  |

| 5.  | Size and Speed Estimates                                                          | 199 |  |

| 6.  | Avionics Subsystems and Computer Traffic                                          | 202 |  |

|     |                                                                                   |     |  |

| App | endix C Inflight Checkout of Avionics Equipment (Orbiter)                         | 205 |  |

| 1.  | Introduction                                                                      | 205 |  |

| 2.  | Subsystem Inflight Checkout Requirements (Orbiter)                                | 206 |  |

|     |                                                                                   |     |  |

| App | endix D Fixed Point Versus Floating Point Arithmetic                              | 219 |  |

| 1.  | Introduction                                                                      | 219 |  |

| 2.  | Fixed Point Arithmetic                                                            | 219 |  |

| 3.  | Fixed Point Problems                                                              | 220 |  |

| 4.  | Analysis of the Apollo Guidance Computer                                          | 223 |  |

| 5.  | Advantages of Floating Point                                                      | 228 |  |

|     |                                                                                   |     |  |

| App | endix E Floating Point Wordlength for Shuttle                                     | 229 |  |

| 1.  | Introduction                                                                      | 229 |  |

| 2.  | Numerical Range                                                                   | 229 |  |

| 3.  | Roundoff Errors                                                                   | 230 |  |

| 4.  | Growth of Roundoff Errors                                                         |     |  |

| 5.  | In-Orbit Navigation Computations                                                  | 235 |  |

| 6.  | Approach and Landing Navigation                                                   | 247 |  |

| 7.  | Summary                                                                           | 248 |  |

| App | pendix F General Description of Burroughs D-Machine | 251 |

|-----|-----------------------------------------------------|-----|

| 7   | Architectural Highlights                            | 251 |

|     | State of Development                                | 252 |

|     | Software                                            | 252 |

#### Chapter 1

#### Objectives and Summary

#### 1.1 Introduction

Past experience has shown that software is a significant factor in the costs associated with development of manned space-craft systems. Since software is an integral and important part of the total system it is essential that it be given consideration during the system definition.

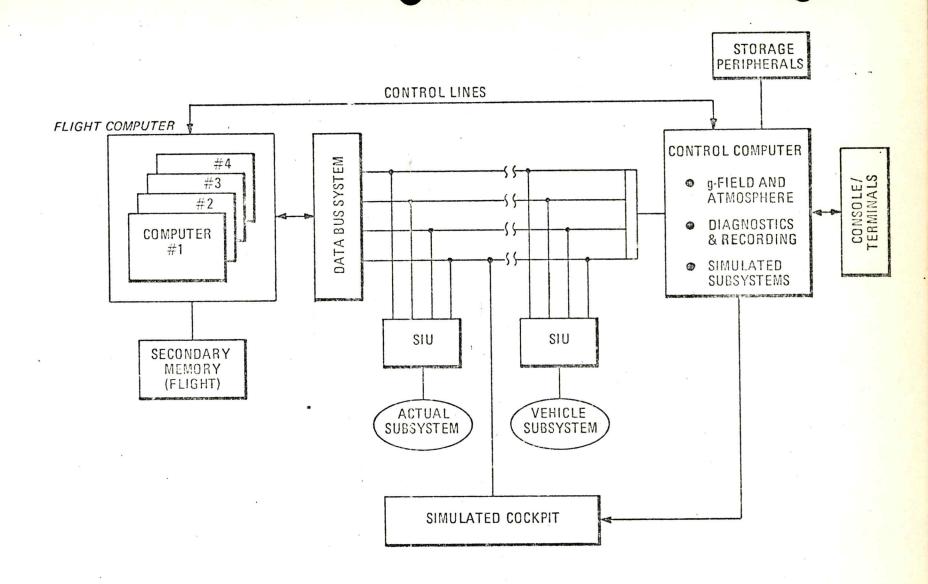

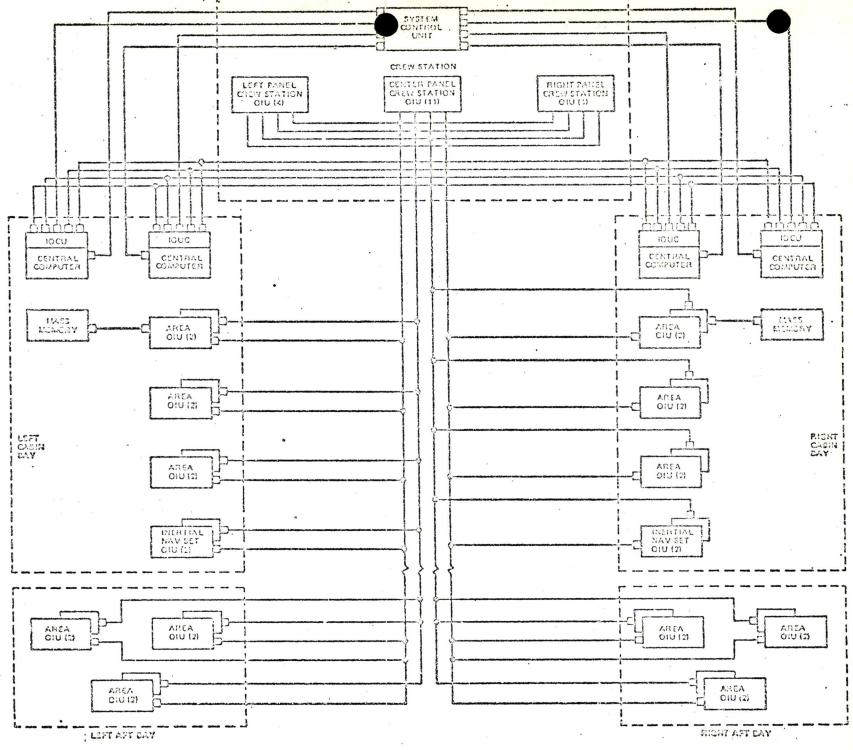

Design concepts for the reusable Space Shuttle vehicle recommended during Phase B include a centralized integrated avionics system approach. The baseline avionics system designs incorporate a quad redundant central computer system which performs all primary processing functions for the entire Shuttle mission. Various levels of redundant avionics equipment, required to achieve multiple failure tolerance requirements, are interfaced to the computer system via a high speed, time multiplexed data bus system.

# 1.2 Study Objectives and Scope

This study is concerned with the evaluation of several key software aspects of the Space Shuttle Phase B avionics system design. Five primary software areas were addressed:

Flight software executive system. The primary objective of this study was to perform a top level functional design of the flight software executive system. Executive functions of task management, scheduling and control, I/O management and configuration management were emphasized in the design. Several key aspects of the overall executive

structure were analyzed, such as: synchronous versus asynchronous control structure, memory allocation and sharing schemes, central I/O control, interrupt handling and high speed data bus I/O. The design is based on the application software requirements of the Phase B avionics system. This task was given major emphasis during the study.

- b) Software verification. Since the major cost of developing aerospace software be attributed to verification, a secondary study objective was to devise a comprehensive approach to software verification, including a definition of verification levels and the roles of facilities to support them. The emphasis was directed at defining an overall approach toward more reliable Shuttle software development in order to lower the high costs of testing and validating flight software. This task was given secondary importance during the study.

- c) Phase B baseline avionics system review. The objective of this task was to review the Phase B baseline avionics systems design and identify the major software implications. The scope was limited to a general review of the designs with emphasis on the architecture of the computer configuration, redundancy management, onboard checkout functions. The purpose was to evaluate their impact on the organization of flight software and its verification. In addition, a summary of the major characteristics of the application software was obtained for use during the course of the study in terms of size, speed and general processing functions.

- d) Higher order languages and compilers. The objective of this task was to investigate the role that a higher order language compiler should have in the development of flight software for the Space Shuttle. This task was limited in scope and was primarily directed at:

- evaluating software areas for which a higher order language approach is difficult, and

- 2) evaluating the role of other languages such as crew language and checkout languages.

In addition, methods of improving compiler efficiency were examined.

e) Computer hardware features. Since the architecture and hardware design of the computer system have a direct impact on the software, the objective of this task was to identify those computer features which are desirable from a software point of view.

# 1.3 Background and Approach to the Study

### 1.3.1 Background

Heavy penalties in cost and time have been paid for underestimating the manpower and time necessary to produce effective qualified and documented flight software. The production of Shuttle flight software will be a complicated and lengthy process and will involve at least the following activities:

- a) generation of mission requirements;

- b) generation of functional software requirements;

- c) generation of software design specifications for: executive and operating system, pilot display processing, telemetry, autopilots, guidance, navigation, subsystem monitoring and control (radar, power, etc.), onboard checkout, data management, configuration and sequencing control, utility and support programs (compilers, simulators, diagnostics) and operational mission programs such as targeting, rendezvous, entry and landing;

- d) preparation of code;

- e) debugging and testing of code;

- f) modification of design;

- g) verification and demonstration of software;

- h) maintenance of software.

Superimposed on the software development cycle above are the requirements for adequate documentation, and management visibility and control. These procedures are necessary to measure program progress, cope with design changes and change controls, insure high quality output, and respond to the pressures of developmental and operational schedules.

In the development of flight software for Apollo, the magnitude of this task caused many problems and delays, primarily in software debugging, verification, and change control. The difficulties experienced can be related directly to the fact that the software design exhibited little overall structure and the programmers themselves had few flight computer hardware aids and little programming language help. Software verification became the single most time consuming and laborious activity because neither the avionics configuration, the computer, nor the programming techniques were designed with checkout in mind.

The MIT Draper Laboratory has reported that fully 80% of the total Apollo software effort was expended on verifying and qualifying flight software. A recent Rand Report [1] corroborates the significant cost of verification by estimating that approximately 50% of the software dollars for SAGE and GEMINI went toward verification. In addition, these factors contributed to the set of "traditional" software difficulties, namely: unpredictable schedules, poor visibility of program status, undefinable software quality, residual unreliability, and spiraling cost.

#### 1.3.2 Approach

Accordingly the approach to this study has emphasized the selection of features, tools, and techniques which aid in software verification. The philosophy proposed is one of improving software quality through careful design and structured software rather than through an iterative search for errors during verification (i.e., "an ounce of design is worth a pound of testing").

In this final report, the Shuttle software development process, the necessary programming language(s), computer hardware features, avionics configuration and executive design are examined in great detail. All are considered with a view toward creating reliable Shuttle software at reasonable cost. Techniques such as top down structured programming, use of a higher order programming language, comprehensive computer hardware and diagnostic facilities are analyzed. Furthermore, an effort has been made to eliminate software problems which in the past imposed difficulties during verification by designing them out. The proposals concerning the structure of the executive system, the handling of interrupts, and the allocation of memory are aimed toward this goal.

Finally, the inclusion of software from the start as an integral part of the total system design will be of immeasurable help. The interrelationships of hardware and software and their effects on overall reliability, demand an integrated design effort.

### 1.4 Task Summary and Review

### 1.4.1 Executive System Design Task

The executive system design is presented in Volume II of this report. The design was based on the application software requirements derived for the Space Shuttle Phase B avionics system and is specified for implementation on the IBM 4 Pi EP computer system within the NASA breadboard data management system. Although a detailed summary is provided in Volume II, an overview of its main features is provided here.

- a) Structure. The executive system structure is based on a high priority synchronous "foreground" for execution of cyclic tasks and an asynchronous priority controlled background for other applications software. The synchronous foreground is initiated by a timer interrupt at a fixed frequency, with the scheduling and sequencing of each computation in a cycle predetermined and specified via control sequencing tables. After completing execution of the computations each minor cycle, the executive dispatches the processor to one of the "ready" tasks in the executive ready queue on the basis of priority. A total of three priority levels has been established for application programs.

- b) Interrupt and task dispatching. Interrupts are immediately serviced by the executive and entries are made in appropriate queues. The interrupted task then resumes and continues until it either ends or until it reaches a segment dispatch point. Only then is a higher priority background task activated by the executive dispatcher. Long duration tasks can be organized into reasonable execution segments with task swapping or interruption points being more predictable. The dispatching of the cyclic task controller each minor cycle is, however, an exception and is executed immediately at the occurrence of the minor cycle clock interrupt. This exception is made as a reasonable tradeoff to provide the timing and response characteristics needed for cyclic computations.

- the executive to schedule another task on the occurrence of an event or a specified time. Events are system defined in scope and may be posted or deposted by applications tasks via the executive.

- Memory organization and allocation. Programs are defined as either total mission resident or mission phase resident. Phase resident programs are loaded from the secondary storage device into their assigned portion of the operating memory by the phase initiation function of the executive. Dynamic memory is allocated to each task by the executive, when it is made ready for execution, out of a subpool of working memory established for each priority level.

A portion of the memory is dedicated to shared data. It is organized into mission dependent resident data and an overlaid area for phase dependent data. All access to the common data is controlled through and by the executive.

- e) I/O control. Control and execution of all input and output operations are performed by the executive system. Input/output services are performed in two modes: on demand via request by an executing task, or table driven as in the case of cyclic computations in the synchronous mode. Secondary memory management is under the control of the executive.

- f) Configuration management error recovery. The executive responds to all system hardware and software detected error conditions and supervises reconfiguration of the system. A standard system error recovery action is defined for each error class. During execution, application tasks may invoke local recovery for a class via specification of a task reentry point.

#### 1.4.2 Software Verification Task

An approach to the development of more reliable software is presented in detail in Chapter 2 of Volume I. The thesis put forward is that definitive statements of software quality can only be made by careful examination of the basic program structure. This structure must be carefully and explicitly created during a thorough initial software design phase.

The traditional role of software testing is shown to be one of demonstrating that the software can meet a finite set of requirements rather than verification of an error-free program. Verification, on the other hand, must be performed from the beginning as an integral part of the implementation,

and consists of a combination of visual examination ("eye-balling")

and selected testing based on program structure and subroutine

interfaces.

It is suggested that the verification procedure is enhanced through the discipline of structured programming. The technique proposed is best described as "top down" programming. all control structure of a program is implemented first, and run, calling upon dummy subroutines. After its operation is verified the subroutines are "filled-in, as you go" with actual code, always keeping the total program in operating order. Programming proceeds in this top-down fashion until all model subroutines ("dummies") are replaced by intended code. The objectives of this technique are to provide "at a glance" understanding of the functions of the program and an ability to achieve an operating status at a very early stage of development. down" assembly of structured programs can be continuously exercised throughout development, providing continuous integration and thereby confidence and visibility of status. The use of a higher order programming language is promoted as an important tool in facilitating this structured approach to Shuttle software.

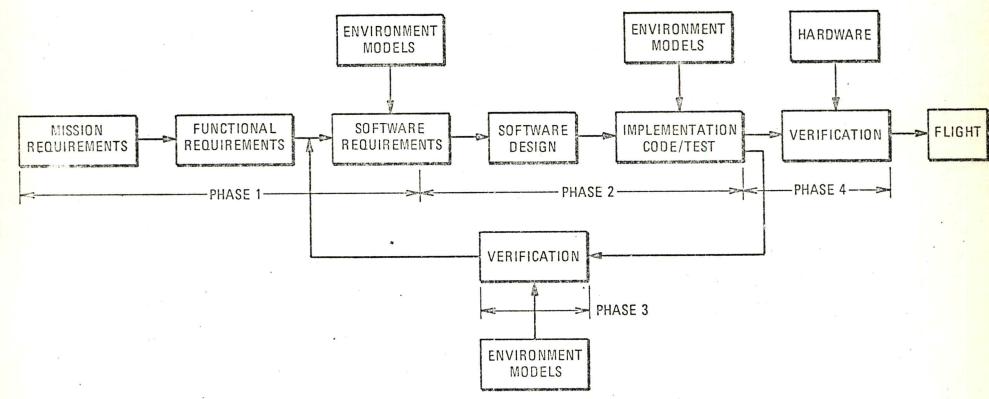

The facilities required to support the phases of software development are presented in Chapter 3. Four phases of software development are identified: Phase 1, software requirements, Phase 2, implementation code and test, Phase 3, verification through software, and Phase 4, verification through hardware. An all-digital software development facility is recommended to support Phases 1, 2, and 3. A hybrid test bed avionics integration facility is used for Phase 4.

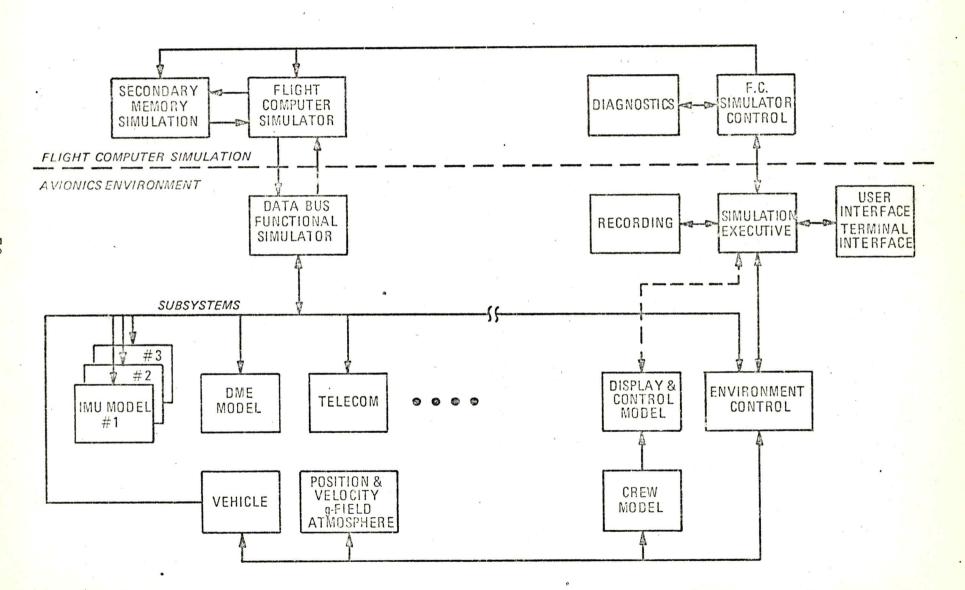

The software development facility (SDF) consists of a large scale commercially available computer system augmented with disk type storage drives, printers and other data processing peripheral equipment. A higher order programming language and compiler for both the host and flight computer are presumed in support of Phases 1 and 2. The use of an interpretive instruction level digital simulator is recommended during Phases 2 and 3. Methods are suggested for improving simulation speed including an efficiently tailored simulator, simulation advance through periods of idle computer activity, and maximum use of HOL programs by direct testing on the SDF host computer.

An all digital avionics environment simulation is recommended for use during the requirements phase (Phase 1). During Phase 3, it will be augmented and interfaced to the interpretive computer

simulator providing "feedback" to the software requirements. The SDF will provide both interactive and batch operation, with limited user interaction during simulations. The avionics integration facility will consist of actual flight hardware supported and controlled by an environment computer.

# 1.4.3 Space Shuttle Phase B Review Task

The Phase B avionics system designs defined by North American Rockwell and McDonnell-Douglas Aircraft Corporation were reviewed. The software implications and features are summarized in Chapter 4 and Appendices A and B. Both Phase B designs have many similarities. Both employ centralized integrated avionics systems with multiple levels of redundant avionics equipment. The central software of both systems is organized around a synchronous structured executive system which includes functions of guidance, navigation, flight control, displays, checkout and configuration management. It is estimated in size to be approximately 50K of 32 bit words with maximum processing speed of up to 275K adds per second. The synchronous versus asynchronous method of control is analyzed in Volume II with a recommendation for a combined synchronous and asynchronous structure.

The multiple failure tolerance requirement of "fail operational" after failure of two critical components and "fail safe" after the third failure is identified as introducing the greatest complexity in the Phase B designs. The control and management of the various levels of redundancy in the system have significant impact on the software, particularly in the executive system. Several general implications of the centralized Phase B designs are discussed: central computer software management problems and I/O timing difficulties with a shared multiplex data bus.

Those differences in the baseline avionics configuration features, which effect software, are identified as:

- a) computer organization and redundant operation,

- b) operating memory and reconfiguration,

- c) secondary storage and utilization,

- d) subsystems redundancy management and interfacing,

- e) operation of display systems.

A discussion of these features in each configuration and its influence on software is provided in Chapter 4.

A review of onboard checkout software was conducted during this task to determine its requirements and interfaces with the executive system. It was determined that checkout software has similar requirements to other flight software and can be implemented within the framework of the executive system described in Volume 2. That is, functions such as subsystem status monitoring, displays and other cyclic processing can be accommodated by the synchronous foreground structure and event driven processing such as diagnostics, recovery and crew requests, can be controlled by the asynchronous background.

## 1.4.4 Higher Order Programming Language Task

The role and types of languages for the Space Shuttle onboard software are presented in Chapter 5. A general purpose higher order programming language (HOL) is recommended for use in developing flight software. It is proposed as a significant step towards a more orderly and controlled production effort. It is also recommended as an essential ingredient of the structured programming approach. Supporting justification and rationale for the HOL recommendation are reviewed in Chapter 5.

A crew language is identified for use by pilots and other crew members to communicate with and command the computer. The crew language must be designed to enable insertion of data, control over program module and processing flow, and general support of crew interaction. This language is not used for software development or on-line compiling.

The features and characteristics of eight programming languages have been tabulated and are presented in Volume III including PL/1, HAL, SPL, CLASP, FORTRAN, ALGOL, MAC and JOVIAL. SPL Mark IV and HAL contain many general purpose features applicable to a wide variety of aerospace software applications, including the Shuttle.

Although it appears reasonable that most flight programming can be done with a general purpose HOL, the difficult areas of machine dependent coding such as system programming are discussed. The use of direct machine language intermixed with HOL statements is not recommended. It is recommended that if special machine dependent features are required, then they should be provided through a special subset of the general purpose development language and be restricted in use.

It is also recommended that if higher level, problem oriented type languages (such as checkout) are required, that they be linked to the general purpose HOL compiler. As discussed in Chapter 5, statements in all languages are ultimately directed into a single compiler system to facilitate standardization and automatic checking performed during compilation. It is recognized that a "single compiler" approach for both lower level system programming and problem oriented languages is not the most flexible. However, it is motivated by a goal of producing quality flight software of high integrity and reliability which may only be achieved through conformance to a highly structured and controlled environment.

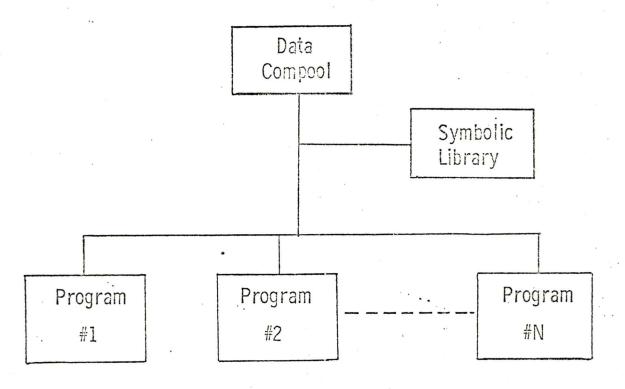

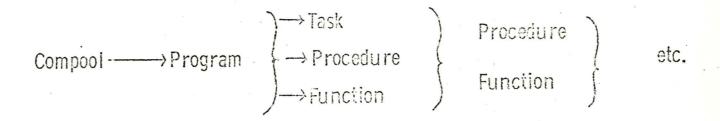

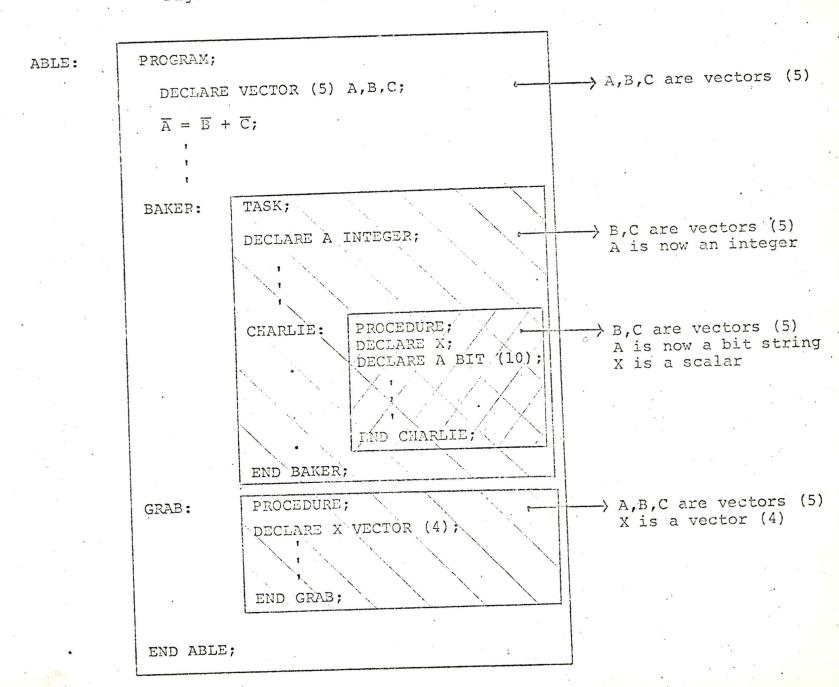

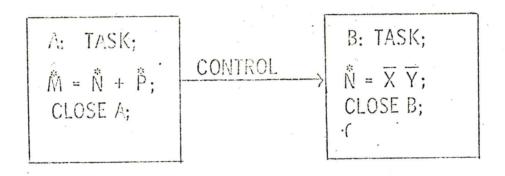

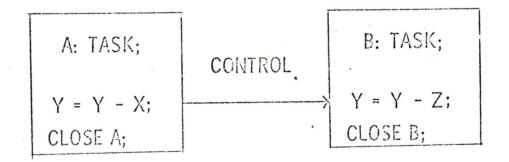

In a subsequent section, the advantages provided by a procedure oriented higher order language and compiler for structure and modularity are discussed: independent compilation, compool control of shared data, block structure, access rights to shared data, and automatic checking features.

The final section of Chapter 5 discusses compiler implementation. The chief complaint regarding use of HOL compilers has been inefficient generation of machine code. The use of a "software interpreter" executing and intermediate language is discussed as an approach to conservation of memory. Microprogram implementation of the interpreter is suggested as a possible approach.

# 1.4.5 Computer Features Task

Several computer features and architectural characteristics are identified as desirable from a software viewpoint in Chapter 6. While it is recognized that these features have tradeoffs associated with hardware complexity, cost, and availability within off-the-shelf hardware, they are presented as valuable to the software production effort as well as a trend for future flight hardware. A summary of the major computer features discussed in the chapter is provided below.

a) It is recommended that the flight computer selected for the Shuttle should possess features to enable efficient execution in a higher order language environment. Ideally, it would be designed as a higher order language machine. The design of a machine which matches the language will not only improve processing efficiencies but will improve performance and reduce memory requirements.

- b) Hardware stacks are identified as desirable for the management of nested procedures and efficient execution of arithmetic statements.

- word length and particular processing aspects of Shuttle software. It provides significant flexibility which is desirable over the long life of the Shuttle through its ability to modify and change microprograms. Specialized spacecraft functions such as data bus servicing can be absorbed into the high speed microprogram and improve performance significantly.

- d) Descriptors are desirable features to provide hardware checks of proper use of data.

- e) Hardware implemented run time diagnostics features are desirable for direct execution and debugging of software, thereby reducing digital simulation requirements. These features can be provided as options in a ground based version of the flight hardware.

- f) The addressing scheme is identified as one of the most important characteristics of the computer. General addressing schemes are reviewed. The "zero address" or stack machine is shown to be most efficient. Most current aerospace computers shown to be "two address" machines containing general registers.

The need for both static and dynamic addressing is recognized for the Shuttle. Indirect addressing, indexing, and base registers are all recommended as desirable for this environment.

- g) Three methods of subroutine linkage are reviewed: return address in a memory, register or stack. The stack is identified most desirable to software.

- h) Floating point data representation is strongly recommended for use on the Shuttle. Appendix D provides a detailed discussion of this recommendation. Appendix E provides an analysis of 32 bit single precision floating point word size as to its adequacy in navigation computations.

- i) In lieu of microprogramming, unimplemented op-codes are identified as a technique of obtaining specially tailored system instructions or routines.

A summary of major flight computer features identified for Phase B is presented in Chapter 6 including: physical characteristics, processor, memory, and production availability.

Finally, higher order language benchmark programs tailored to the Shuttle application software are suggested as an additional measure of the relative performance of candidate Shuttle computers.

# Reference for Chapter 1

1. Boehm, B.W., "Some Information Processing Implications of Air Force Space Missions: 1970-1980", Memorandum RM-6213-PR, Rand Corporation, Santa Monica, California, January 1970.

#### Chapter 2

#### Software Verification

#### 2.1 Introduction

The question of how to develop reliable flight software in a cost effective manner is of overriding concern to the Shuttle Program. Although methods employed during the Apollo development were successful in that Command Module and Lunar Module computer software did the job and suffered few significant anomalies, the effort expended in manpower and program testing time, and the residual uncertainty in product reliability leads one to search for surer, more efficient ways to achieve program quality.

The production of man-rated real-time operating software for the Shuttle will be a complex process of interrelated activities: generation of requirements and specifications, design of algorithms and methods of implementation, coding and testing, verification, management, change control, operations, and field support. Each activity can bear a direct responsibility for contributing to software reliability. In an effort to better organize, expedite, track and smooth the process, a number of improvements might be suggested; thus

- a) more detailed specifications

- b) initial design documents

- c) detailed design documents

- d) detailed test plans

- e) automatic decoding aids

- f) automatic flow charts

- g) multiple levels of testing

- h) automatic diagnostic aids

- i) automatic test aids

- j) automatic evaluation aids

- k) management review of milestones at all significant points of development

- 1) strict configuration control of coding and testing

- m) strict procedures for change control

- n) control and timely production of all necessary documenta-

No one can doubt that many of the items listed above will enhance the production of Shuttle software, but still one might ask "will they insure bug-free programming?". It certainly will be more convenient and less error prone to set up test runs and conduct them using automatic aids for initialization, edits, evaluation, etc., but will these features find, or help to locate, software errors? And, further, how can it be determined that no more errors exist and the testing phase is completed?

For any large, non-trivial programming effort these questions have remained largely unanswerable. The approaches taken, for the most part, include establishing the closest control over the coding and changes to the coding, demanding comprehensive documentation and conducting elaborate and usually exhaustive test programs. While recognizing the value of these approaches, this report contends, nevertheless, that the reliability of software is best improved by proper design, structure, methods of implementation, and through the use of software and hardware techniques which can prevent errors in the first place. For example, Apollo flight software anomalies were caused mostly by errors due to erasable conflicts, scaling difficulties and imperfect restart logic [1].

Prodigious amounts of engineering and computer time were spent in diagnosis and testing for this kind of error. If the Shuttle software utilizes floating point, automatic data sharing through hardware and/or software locks, and a single instruction restart machine, then the most prevalent Apollotype errors would be eliminated, not by controls, test plans, test facilities, etc., but by design.

In the sections that follow, it is design responsibility, design methods and careful implementation procedures that are stressed. The hope, and objective, is that both quality and cost efficiency will be gained by entering the verification phase with an inherently more reliable software product. Verification can then proceed, quickly and smoothly, to demonstrate compliance with requirements instead of having to bear a major responsibility for debugging an imperfect program.

Three principal ideas are espoused:

- 1) Coding must be preceded by a thorough software design effort in which the methods and procedures of implementation are carefully formulated and specified.

- The application programmer's machine interface is built upon layers of virtual machines where each layer only uses the facilities provided by the "machine" (layer) directly below it. Access to internal layers from above is disallowed.

- The programs are implemented in a "top-down" manner beginning with the overall control and concepts, and are gradually refined by filling in the detailed code. Programs are kept in operating condition while still under development (using models) so that problems of integration are faced and solved along the way, rather than being postponed until all coding is submitted.

In summary, more emphasis is placed on building in software quality by design, and less on the relentless search for errors after the fact.

### 2.2 Requirements and Specifications

The production of Shuttle software is a process which begins when the broad objectives of the Mission Requirements are formulated. Its primary objective is to produce a concrete set of correctly functioning programs for the on-board computer(s). It is an activity spanning a wide spectrum of management and engineering disciplines, during which the statement of the overall requirements undergoes successive refinement and redefinition on the way to the final product. The ultimate form of this statement is the computer program itself.

The need for commonly accepted definitions of the software requirements, at levels in between the statement of mission objectives and the computer program, has been recognized in the past by the establishment of software functional specifications, software engineering specifications, program design specifications, etc. It is Intermetrics' view that the formulation of these specifications is an important part of the software production process itself, and must be integrated with it.

A specification must describe accurately and fully the functions it defines. No questions which require recourse to an authority outside of the specification for answers must be raised in the minds of those interpreting that specification. On the other hand, the specification writer must not impose constraints on the subsequent design activity by specifying details of implementation more properly deferred to that activity. Perhaps the most insidious software error is that due to the misinterpretation of a specification requirement by the implementer. It is impossible to devise rigorous verification procedures to detect failures of human understanding. Ambiguities and omissions in the specification must be eliminated in order to achieve "correct" programs.

The assurance of this kind of quality in a software specification implies that the development of such a specification is a design task in its own right, and must be considered a part of the overall software production effort. The objective of this section is to define the number, purpose, and the characteristics of a minimal set of specifications considered to be necessary for the implementation of Shuttle software, and to indicate how the design of such a set is to be approached.

# 2.2.1 The Formulation of Software Specifications

A four level hierarchy of Shuttle software specifications is envisaged. Four specification documents need to be identified, to define and describe the following:

- a) Mission Requirements

- b) Functional Requirements

- c) Software Requirements

- d) Program Design

The term "specification", where used in the remainder of this section, will refer to one of these documents.

Each level constitutes a refinement of the requirements of the previous one; each specification in the sequence yields a definition of the software in increasingly concrete terms. Each set of requirements is assumed to be organized in the form of a document, which is treated as the specification and reference manual for the next activity. Each of the above specifications will now be described in greater detail.

- 2.2.1.1 Mission Requirements. At the highest level are the Mission Requirements. These set forth the activities and objectives of the Shuttle concept. All intended mission phases are indicated from launch to landing, with definitions of all nominal, off-nominal, contingency, backup and abort situations. The Mission Requirements indicate broadly the operational functions of the Shuttle, the range of capabilities, the expected levels of performance, and the accuracies that must be achieved. The Mission Requirements are the specification for a detailed functional design of an operational system to accomplish the mission objectives. The result of this stage of design is a set of Functional Requirements which specify the manner in which the Shuttle will accomplish the objectives.

- 2.2.1.2 Functional Requirements. This specification will define the various operational phases, identify the functions to be performed, determine the sequence of operations, establish the interrelationships of the functions, and provide mission time-lines. The Functional Requirements Specification will identify and determine the scope and capabilities of the various on-board subsystems, and will

indicate the nature and degree of cooperation with ground based operations. It is during the design of the Functional Requirements that definitions about the number and types of the various subsystems, their functions, and the configuration of the system begin to be made.

The next stage of software design takes the form of a detailed analysis of the Functional Requirements, with the objective of establishing techniques for their realization. The end result of this very important phase is a set of Software Requirements.

2.2.1.3 Software Requirements. This Specification contains definitions of all the appropriate equations and algorithms to be implemented, details of critical timing and sequencing as demanded by the Functional Requirements, operational procedures, and definitions of operational interfaces between the computer/software and the rest of the Shuttle system (i.e., crew, subsystems, ground). The Software Requirements Specification contains all information that is required to embark upon a detailed structural design for the Shuttle computer programs. This includes, particularly, all appropriate data that is to be used, both fixed and variable. Dynamic ranges of all specified mission variables will be established and defined. The Software Requirements will constitute a specification for the design of the actual program.

An essential part of the Software Requirements Specification is a definition of the set of tests to which the completed program must be subjected in order to demonstrate its correct operation. The task of defining these tests requires knowledge of the design concepts for the whole system, and is not one to be left to the programmer. The test requirements will include prescribed test cases with initial conditions, mission parameters such as state vectors, weights, inertias, etc., and the specified levels of performance to be achieved, together with evaluation criteria to enable a judgement to be made.

2.2.1.4 Program Design. This final stage of software specification is perhaps one that has not, in the past received the attention it demands. Too often a basic structural software design has not been possible, perhaps because there is no time for it, because the job was not completely specified at the time programming began, or because already existing segments of software had to be

pressed into use. It is our contention that the establishment of a Program Design Specification is necessary to ensure that an overall program structure and operating philosophy be established at the outset. There must be a conscious effort to design this Specification. It must be based on a comprehensive set of Software Requirements, and it must precede the start of operational program coding. Because it is followed by implementation, the final stage of refinement, the Program Design Specification must address the set of problems associated with programming, checkout and integration. Section 2.3 will review in greater detail the approach to be taken in establishing this Specification.

# 2.2.2 Necessary Detail Within Software Specifications

The generation of definitive software specifications is a process of successive refinement, during which the scope of Shuttle functions being considered narrows to only those associated with the details of software operation, as those details become increasingly more apparent. The primary purpose of the specification documents is to provide tangible interfaces and control mechanisms between the groups of people, of varying disciplines and working styles, who will be involved in the process. The hierarchy of specifications (i.e. the several Requirements) can also be seen as stepping stones on the route to a program design, forcing an evaluation of the design at intermediate points. One purpose of this hierarchy is to prevent selected aspects of the total system design from being taken prematurely from conception through implementation, or, conversely, from falling behind. An uneven rate of development creates inflexibility and discourages the across-the-board compromises which are always necessary as a design solidifies. This principle will be invoked again in the discussion of program implementation (Section 2.4).

In order to maintain the desirable flexibility it must be emphasized that each specification is only the starting point for the next stage of design. A set of requirements should avoid dictating, or even implying, the use of specific techniques of organization or design that might appear to be necessary to achieve these requirements. It is important to preserve the choice of design policies, so that overall compromises can be made. The tendency to become too specific is a common fault in specification design. It is difficult to resist as the system becomes progressively more clearly defined and seemingly obvious techniques of implementation begin to present themselves. For example, although the Software Requirements Specification should present all the

information required by a program designer to create and deliver the software, it often specifies, as well, how it is to be structured. Functions are presented as software modules with the interfaces among modules already defined. A specification that goes to these lengths not only absorbs unnecessary effort during its design, but creates further waste because it may have to be unravelled before a real program design can begin. If such over-specification is not recognized, but is promulgated in the design of the program, basic options of organization and design may no longer be available. Furthermore, the application of the principles of structured programs (to be discussed in Section 2.3) is impeded, lessening the possibility that reliable software can be produced and making modification and change procedures more difficult to apply.

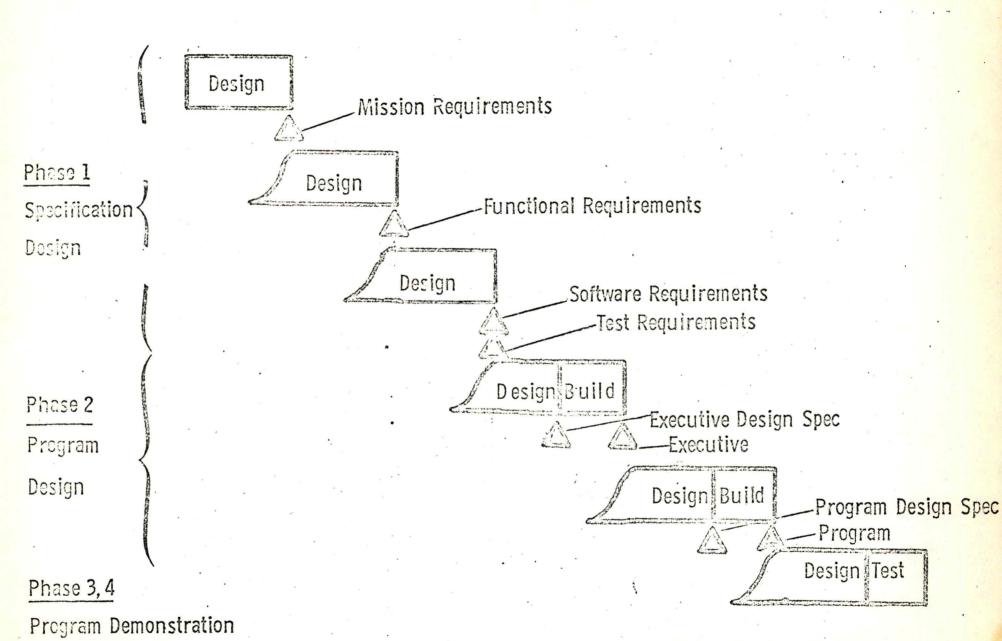

# 2.2.3 The Phases of Software Development

Shuttle software production must be considered as a continuous process, which is initiated by the formulation of the mission requirements, and does not end until after the delivery of a validated set of flight-ready programs. The nature of the activities involved in this process naturally undergoes significant transformation as the software evolves through specification, design, implementation, testing, integration and, eventually, to operation. These activities can be grouped into three phases, characterized broadly as specification, implementation and verification activities. The disciplines of the personnel, and the techniques and facilities that are involved in these phases differ sufficiently to suggest these categories. The remainder of this section will be devoted to a brief description of each phase and its product.

2.2.3.1 Phase I: Specification. The basic characteristics and content of the Mission, Functional and Software Requirements documents generated during this phase have already been discussed in Section 2.2.2. Although shown as separate activities in Figure 2-1, the work leading to the publication of these three specifications cannot be conducted independently. Each specification must acknowledge fully the capabilities and limitations of the activities it seeks to direct. The Functional Requirements designer must be aware of equipment limitations. In generating the Software Requirements, the basic problems associated with program design and checkout must be appreciated. This may seem obvious, but in practice

Figure 2-1 The Software Process

these principles have often been violated. As a consequence a subsequent activity experiences problems that should have been anticipated earlier (e.g. inadequately defined hardware interfaces, or failures to specify the dynamic ranges of intermediate results). To minimize these occurrences, specifications must be formulated, reviewed and iterated with participation from all phases of software design.

As the definition of the software progresses towards its embodiment in the actual program, the specification becomes successively more quantitative and requires an increasing degree of analysis and computation. especially true in the case of the Software Requirements. Specification which contains the necessary equations, algorithms, loop gains, coefficients, sampling frequencies, etc., so that no aspect of the performance of the system need be established during the program implementation phase. This implies that a thorough analytical investigation is necessary to devise the techniques by which the performance specified in the Functional Requirements may be attained. The development of this specification is therefore a major undertaking. It is our contention that specification design should rank in importance and emphasis with the design and development of the computer program itself. Too often it is left to the flight program personnel, already hampered by an unproven program and by a simulation environment ill-suited to the purpose, to fill the gaps of an inadequate specification.

An analytical specification design effort requires the support of adequate tools and facilities. The evaluation of the closed loop performance of the Shuttle thrust and attitude control systems, for example, requires an accurately modeled simulation of the vehicle's dynamics, its stabilization and thrusting subsystem, and other appropriate guidance and control functions. If such a simulation is a requirement for this stage of software design, then it is natural to ask whether it can also be used in the later stages of verifica-It will be suggested in Section 2.5 that a modular simulation organized with this objective is feasible. modular elements can be utilized, either individually or in smaller subsets, to support the needs of Phase 1 analysis In its integrated configuration it can provide the comprehensive all-digital simulation environment postulated for the demonstration testing of Phase 3. A modular environment simulation offers two significant advantages:

a) only one simulation design effort need be undertaken to satisfy the needs of two distinct activities.

b) the simulation models that are used in Phase 1 to formulate software concepts, are themselves verified at a later stage, by comparing their performance against that of the more real equipment in the system integration facility. This concept will be developed more fully in Section 2.5.

An important aspect of software production is testing. Although it will be shown in Sections 2.3 and 2.4 that there are good reasons to change the customary view that testing is the basis of verification, software testing will always be necessary. As a consequence the task of specifying and defining all the test cases, and the problem of establishing the test criteria will have to be faced. The responsibility for test case design belongs properly to those charged with developing the Software Requirements. During this stage the basic concepts of system and software design are formulated, and the software performance characteristics are established. The design of tests that demonstrate the correct implementation of these concepts requires considerable effort from personnel who have knowledge of the overall system operation.

Special care must be taken to eliminate uncertainty in the mind of the tester when he is asked the question "was the test successful?". The performance of closed loop control system always falls short of that established by the ideal, weightless, inertia-less systems upon which concepts are based. The degree of acceptable mismatch must be established in the Software Requirements Specification so that the software tester will have to exercise an absolute minimum of judgement in evaluating program performance. This is especially true for tests conducted by the Phase 2 personnel, the programmers. Their primary objective is to deliver correct code, not to evaluate say, the performance of a minimum fuel thrusting maneuver. Test case design cannot be performed by those already overburdened with the demanding task of designing and verifying the details of program implementation. The test requirements, therefore, will form an essential ingredient of the software requirements document, to be delivered at the conclusion of Phase 1.

2.2.3.2 Phase 2: Program Design. This phase accomplishes the design, implementation and testing of the actual flight program to the Software Requirements established in the previous phase. The details of how this is to be done will be described in Sections 2.3 and 2.4. At this point only a brief summary will be given. Figure 2-1 illustrates the two major activities of this phase; the executive design, and

the design of the operational programs. Both consist of a pure design phase followed by an implementation phase. the end of the executive design phase, which will apply the principles of "layered" structure to be described in Section 2.3, an Executive Interface Specification document will be published. To the applications programmer this becomes the definition of his interface with a "virtual" machine. It will specify how he will schedule tasks, handle I/O, control timing, etc. It will obviate any necessity for him to become familiar with the real details of machine hardware structure, and will prevent him from interfering with such basic operations as scheduling, memory allocation I/O, interrupts, etc. The publication of the Executive Interface Specification signals the start of executive program coding and test, and the start of the design phase for the applications programs.

Applications program design is perhaps the most important activity in the whole software development process. Its purpose is to establish an overall structure for the computer program before the coding and testing begins. main objective is to create a framework that logically and sequentially interrelates the various program modules which are also identified during this phase. This represents the first opportunity to apply in an initial layout of the actual program itself some of the principles of structured programming and top-down implementation. This subject is explored fully in Section 2.3. The applications program design phase is complete when the Program Design Specification document is published. This is the last in the series of specifications that together define the software design process. From this point on program coding, integration and testing can proceed, with the confidence that no major design hurdles have still to be overcome. Effort can be concentrated on the creation of a well defined, visible, program whose dynamic characteristics can be more easily assessed from its static structure, than has been the experience of the past. This subject is analysed further in Section 2.4.

- 2.2.3.3 Phase 3 and 4: Verification. At the end of Phase 2 the flight program is complete and "internally" verified. It now enters the final phase of testing before being exposed to the actual flight environment. The principle objectives of this phase, which will be described fully in Section 2.5 are:

- to demonstrate correct software operation according to the Software Requirements Specification;

- b) to confirm that the concepts formulated during Phase 1 are still effective in an environment which more closely resembles that of the real world;

- c) to confirm the adequacy and validity of the modeled environment used during Phase 1 and 2 to provide quantitative test and performance data.

The rationale for dividing the verification activity into two distinct phases will be presented later, together with a description of the techniques and facilities to be used.

### 2.3 Program Design

It is proposed to build reliability into the Shuttle software, by design, through the technique of "structuring" the flight programs. The essence of this approach is "modularity with structure". This section will explore its application under the principal headings of

- a) Program structure,

- b) Program modularity,

- c) Influence of language,

- d) Program design process.

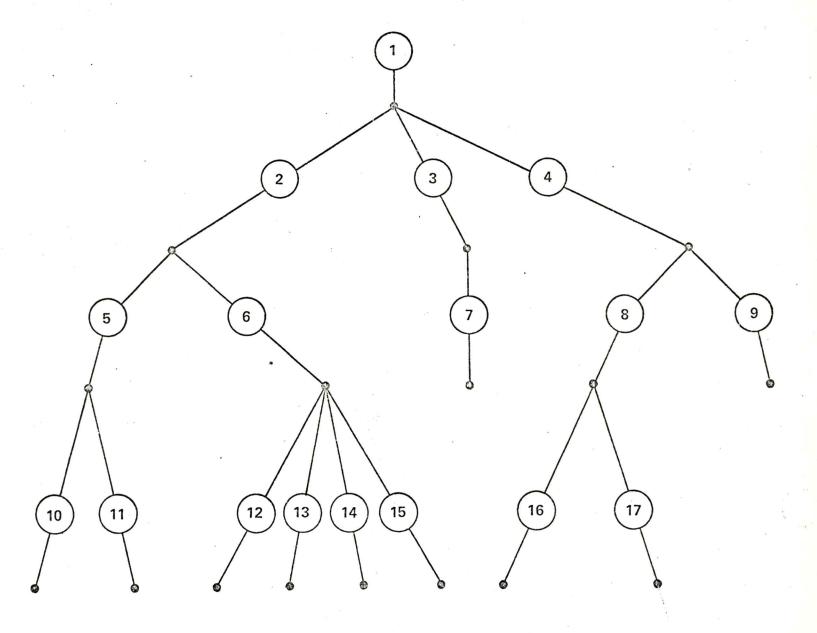

# 2.3.1 Program Structure

A large, complex program must be visualized as an hierarchical organization of functions, rather than as a collection of somewhat arbitrarily defined program modules. The overall objective of a computer program is to execute a translation from the highly sophisticated requirements of the mission and environment into the relatively simple logical statements required to control the computer hardware. This translation can be conceived in a series of steps, in which each step performs a translation between intermediately defined procedural and logical interfaces. In this way the interaction between functions in the software can be limited, defined, and more easily controlled. Such a structured approach has been successfully applied to the design of operating systems for large general purpose facilities [2,3,4]. It is proposed to apply the principle to the whole of the program in the Shuttle computer, including the applications program. Because of the strong influence of the real-time

requirements, structure becomes even more desirable, in order to achieve effective separation and modularization of functions.

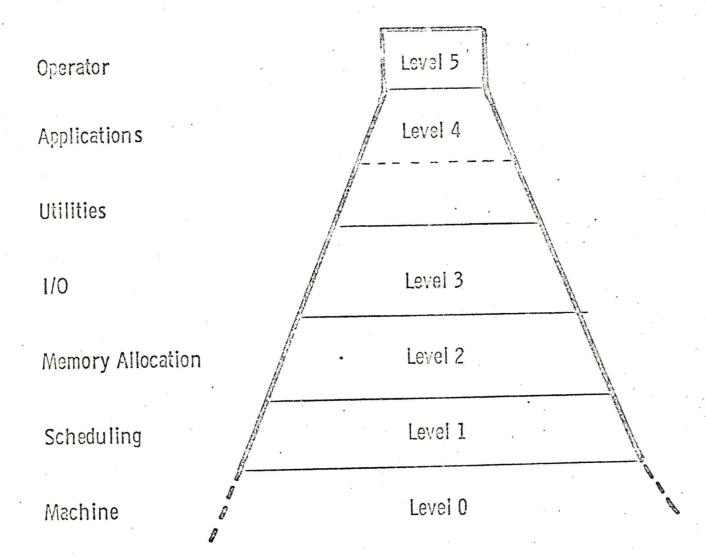

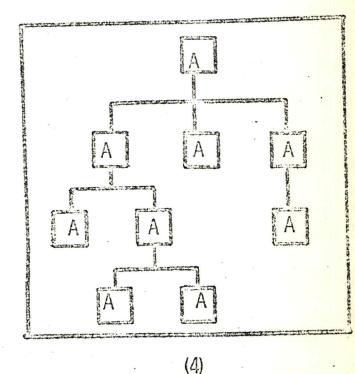

The hierarchical, or layered, organization can be represented as in Figure 2-2. The machine itself is depicted as the lowest or zero level. The actual hardware/software interface is therefore between Level 0 and Level 1. "tiered cake" appearance of the figure is due to the choice of coordinates. The horizontal scale represents interface complexity, defined as the number of system variables controlled by that interface. The vertical scale indicates the level of sophistication or abstraction of the function from the interface. The higher the level the more sophisticated the "virtual machine" becomes. The highest level is ultimately the crew member, who uses the computer to accomplish the appropriate mission phases. He may have only a few options of control; for example, he may be able to select major mission modes such as "ascent", "insertion", "rendezvous", with perhaps a few variations, as specified by the Mission Requirements. Although limited in number, these are very sophisticated functions indeed.

The layers are so organized that each level interfaces only with those levels immediately above and below it. A given level is unaware of any detailed structure within the "level" below it. The functions performed by the software within that level may, in fact, regard the lower interface as a "virtual machine" [2], whose properties are defined by the requirements of that interface.

The decomposition of the Shuttle software functions into a succession of layers can be illustrated as in Figure 2-2. The function of each of these levels is as follows:

- Level 0: The machine

- Level 1: The control of processes. The allocation of the processor(s) to active jobs, i.e., scheduling and dispatching. Also the control of response to interrupts, and the resolution of priorities.

- Level 2: The responsibility for allocating space in operating memory, and if it is provided, the control of secondary storage.

- Level 3: The management of I/O operations. This might include the interfaces to the displays, manual inputs, and the Shuttle data bus.

Level 4: The application program functions. A sublevel of Level 4 might be a collection of program utilities which provides standard higher mathematical functions, coordinate transformations, integration algorithms, etc., not already available within the programming language.

Level 5: The crew member.

These are only broad suggestions, offered in illustration of the principle. Other categorizations have been made [2,3]. Levels 1 through 3 fall into a category normally referred to as the operating system. From a structured viewpoint, an operating system has, in the past, been somewhat arbitrarily defined. It is normally considered as an entity, rather than a subset of hierarchical levels, because the collection of executive functions is usually considered to be invariant, a part of the machine. The applications programs, and their requirements, are often quite unknown until late in the development of the system. In the Shuttle environment, the totality of functions is known and well-defined, and the layers of program functions may be optimally organized.

The first stage of program design is to identify the various levels, and to define their functions. The interfaces of the levels with each other are then determined, and will form the basis for the implementational techniques to be described in Section 2.4. The constraints to be observed in organizing the software into a hierarchy of functions will obviously be, at the highest level, the requirements defined in the Software Requirements Specification, and at the lowest, the characteristics of the computer.

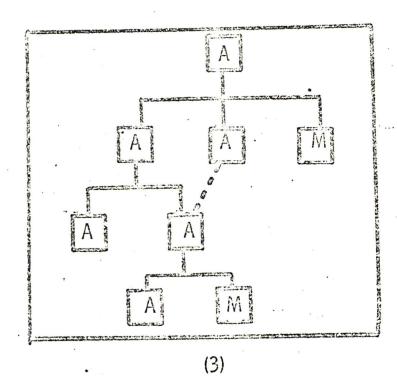

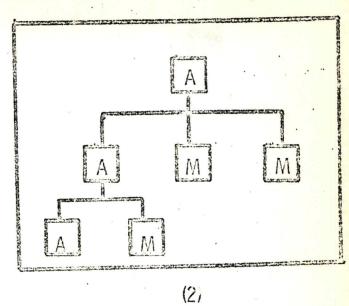

#### 2.3.2 Program Modularity

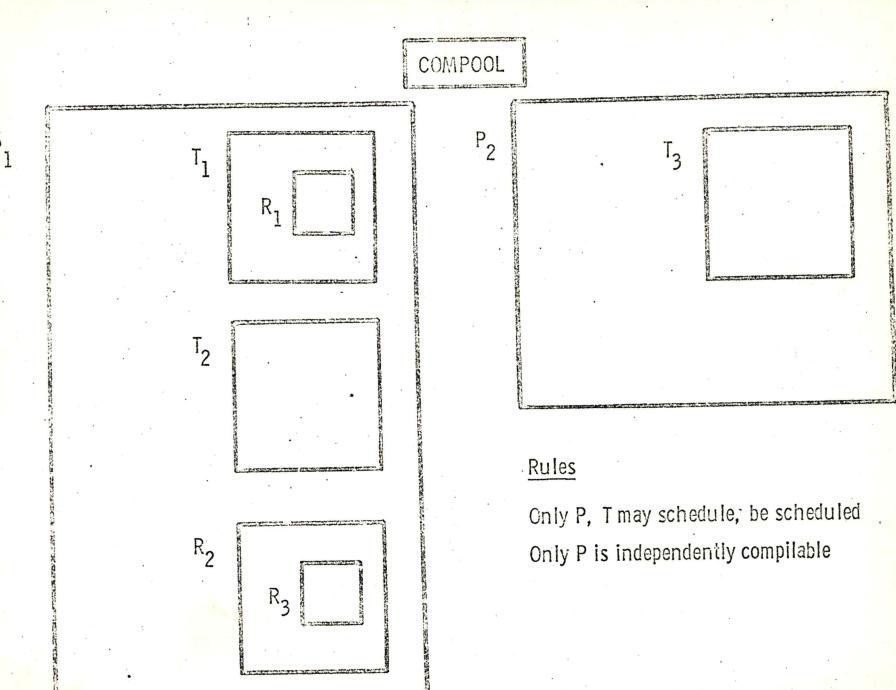

To be containable and manageable, program code must be capable of being organized into sizable modules, containing groups of logically related statements, or instructions. It is advantageous if the number of different types of such modules is kept to a minimum, so that simple rules can be devised to enforce their control. Past experience with software for real-time aerospace control applications indicates that perhaps only two types of module need be defined, and that their desirable characteristics should be as follows:

#### a) Data Modules

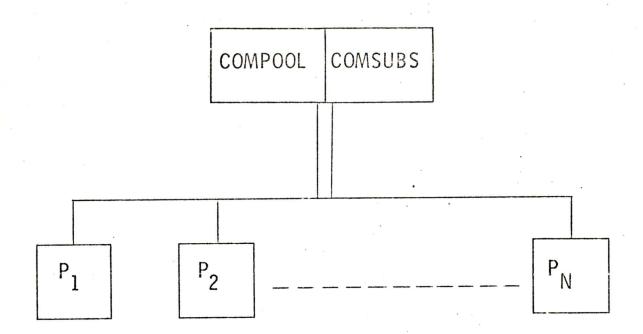

Prescribed inputs are processed in a logical or computational fashion and outputs are delivered back to the caller. Access to common data is allowed only through the rigid supervision of a common data pool (COMPOOL) control mechanism.

#### b) Control Modules

This module is scheduled by the executive and may call Data Modules as necessary to perform the basic processing tasks. A Control Module may schedule, via the executive, other Control Modules. An objective in defining this type of module is to bound the program control functions so that the number of executive interfaces is minimized. A well defined control module is thus independently operable, without being unmanageably complicated or large. The purpose behind this concept is to create software entities that are visible, comprehensible and testable; i.e., easy to conceive, construct and verify, to set up and run, with well-defined, limited modes of operation. Their functions are obvious by examination, and their performance under test can be readily observed and evaluated.

The software modules created by application of these definitions do not necessarily bear relationship to the functional elements of former, typical software requirements specifications. It is on this point that a departure from previously established procedure is suggested. Formerly, the software specification was organized into convenient functional portions, each of which played a visible role in the operation of the avionics system. These elements were formerly implemented with little reorganization for optimal implementation, verification, and execution, so that they became intimately and often randomly entwined with each other and with the system programs. The result was a complex structure that became very difficult to debug, verify, or modify.

During Phase 2, the program will be broken down into an assembly of Data and Control Modules. The performance and interface specifications for these Modules will be established as part of the Program Design Specification. The Module specifications will include

a) definition of all input and output parameters and their characteristics (e.g., dynamic range, scaling, precision, formats, etc.);

- b) all timing details, both internal and external;

- c) all priority and other scheduling information;

- d) definition of interfaces that the module shares with other modules;

- e) definition of all logical and computational operations to be performed within the module.

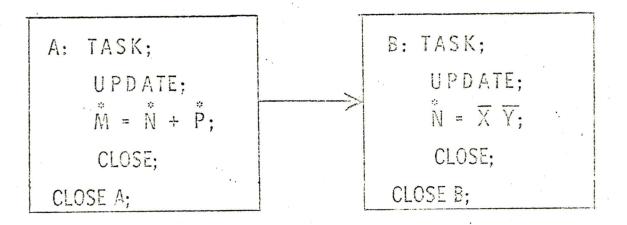

A higher order compiler language can be instrumental in achieving the first objective. A language which provides for the definition and manipulation of program blocks will allow Data Modules to be more easily defined, maintained, and their intended use to be enforced. A real-time control capability can assist the definition of the Control Modules and enforce their proper use. A specific language, HAL, will be discussed in the next section, and the relevance of its structure to the attainment of program modularity will be indicated.

### 2.3.3 The Role of the Programming Language

The advantages and disadvantages of the use of a higher order language for the programming of the Shuttle computer is discussed in a broad context in Chapter 5. In this section only those aspects which have relevance to the structuring of programs will be considered.