#### R-358

## A DIGITAL CONTROL COMPUTER DEVELOPMENTAL MODEL 1B

by

R. L. Alonso, A. I. Green, H. E. Maurer, and R. E. Oleksiak

April 1962

## INSTRUMENTATION LABORATORY MASSACHUSETTS INSTITUTE OF TECHNOLOGY CAMBRIDGE 39, MASSACHUSETTS

CLASSIFIED by AF 04/647 Subject to General Declassification Schedule of Executive Order 11652 Automatically Downgraded at Two Year Intervals. DECLASSIFIED on 31 Dec 1973

Approved: Elelan C Hall

Assistant Director

Approved: ()

#### **ACKNOWLEDGMENT**

.

This report was prepared under the auspices of DSR Project 52-156, sponsored 'by the Ballistic Systems Division of the Air Force Systems Command through USAF contract AF 04(647)-303.

This notional contains information affects the national conse of the United states within the meaning of the Disage Laws, Title 18, U.S.C., Section 23 and 794. Its transmission or a certain with contents in any matter to an unauthorized person is problem by law.

The publication of this report does not constitute approval by the Air Force of the findings or the conclusions contained therein. It is published only for the exchange and stimulation of ideas.

## G

#### R-358

## A DIGITAL CONTROL COMPUTER DEVELOPMENTAL MODEL 1B

#### ABSTRACT

This report describes in detail a pilot model of a parallel, programable digital control computer. Magnetic cores are used as storage devices and extensively in the logic, thus reducing power consumption. Transistors are the active elements.

The computer has capabilities for automatic incrementing of counters and automatic program interruption, or mode changing. These are used to advantage in the control of a steppingmotor.

by Ramon L. Alonso Alan I. Green Harold E. Maurer Robert E. Oleksiak April 1962

CONFIDENTI

## TABLE OF CONTENTS

|              | ]                                                  | Page  |

|--------------|----------------------------------------------------|-------|

| Introduction | by R. L. Alonso                                    | 1     |

| Chapter E    | Computer Structure by R. L. Alonso                 | 11    |

| Chapter 2    | Mod 1B Control of Stepper-Motor by A. I, Green     | 35    |

| Chapter 3    | Electrical Design by R. E. Oleksiak                | 65    |

| Chapter 4    | Controlled Devices by H. E. Maurer                 | 139   |

| Bibliography |                                                    | 165   |

| Appendix A   | Register Assignments by A. I, Green                | 167   |

| Appendix B   | Bit Assignment of Special Registers by A. I. Green | 169   |

| Appendix C   | Core Packages Used in Mod 1B by R. E. Oleksiak     | .17 1 |

| Appendix D   | Power Amplifiers by R. E. Oleksiak                 | 173   |

## LIST OF ILLUSTRATIONS

|      |               |                                                                       |   | F | age! |

|------|---------------|-----------------------------------------------------------------------|---|---|------|

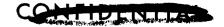

| Fig. | I - 1         | Mod 1A Computer and Control Panel, .                                  | , | , | :5   |

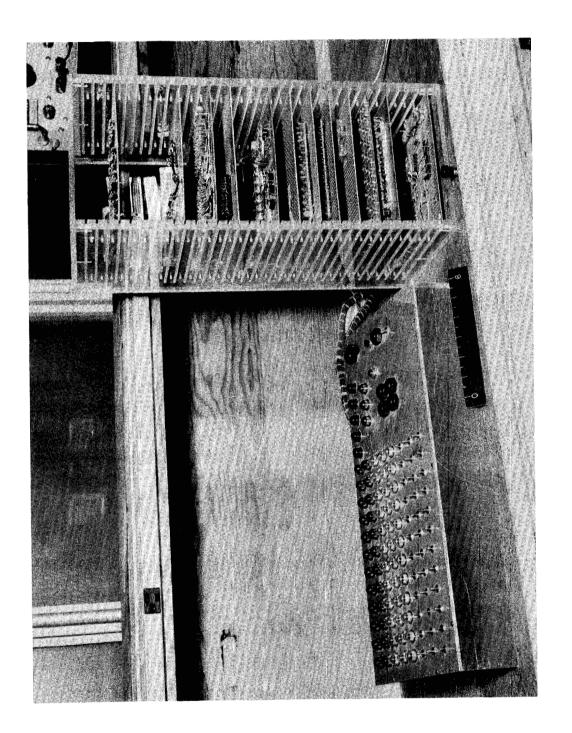

| Fig. | I - 2         | Mod 1B Computer , . , . , , ,                                         | , |   | 6    |

| Fig. | I - 3         | Mod 1B Control Panel , , ,                                            | , | • | 7    |

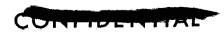

| Fig. | I - 4         | Tray 5 from Mod 1B , ,                                                | , |   | 8    |

| Fig. | 1-1           | Organization of the 1A Part of 1B from the Programers Viewpoint . , , | • | , | 2 1  |

| Fig. | 1 - 2         | Detailed Structure of Mod 1B                                          | , | • | 22   |

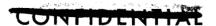

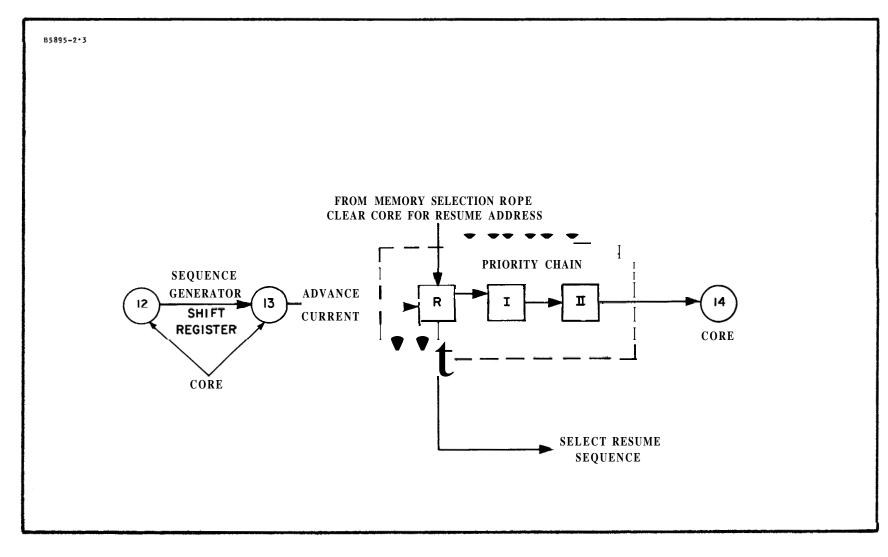

| Fig. | 2 - 1         | Automatic Increment Priority Chain . ,                                | , | • | 52   |

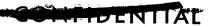

| Fig. | 2 <b>- 2</b>  | Automatic Interrupt Priority Chain , ,                                | , | • | 53   |

| Fig. | 2 - 3         | Automatic Interrupt Priority Chain Showing RESUME Core , , ,          | , |   | 54   |

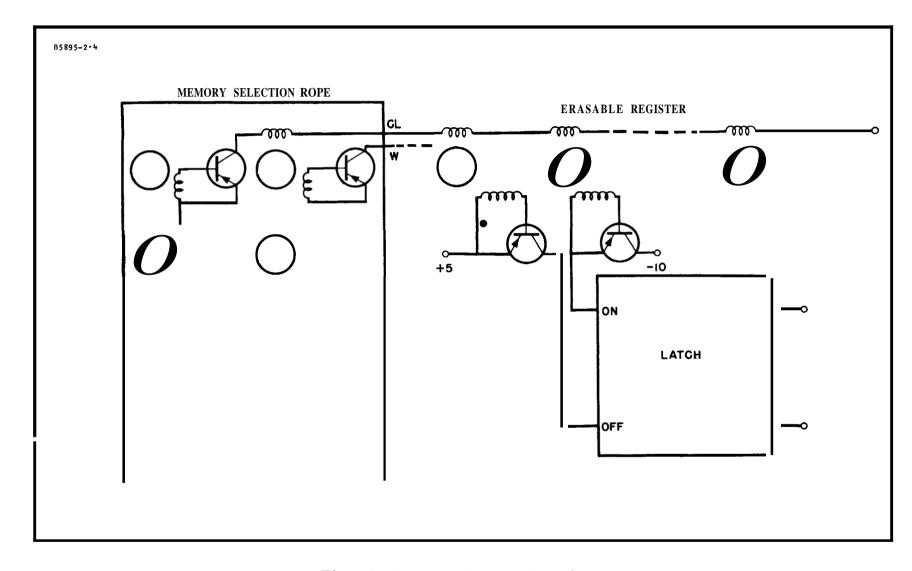

| Fig. | 2 - <b>4</b>  | Latch Control Register , ,                                            |   |   | 55   |

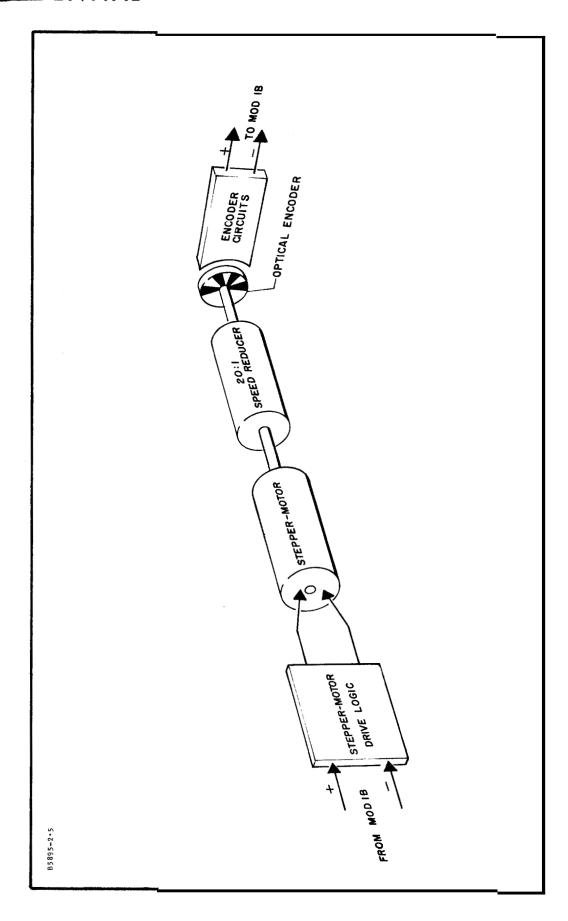

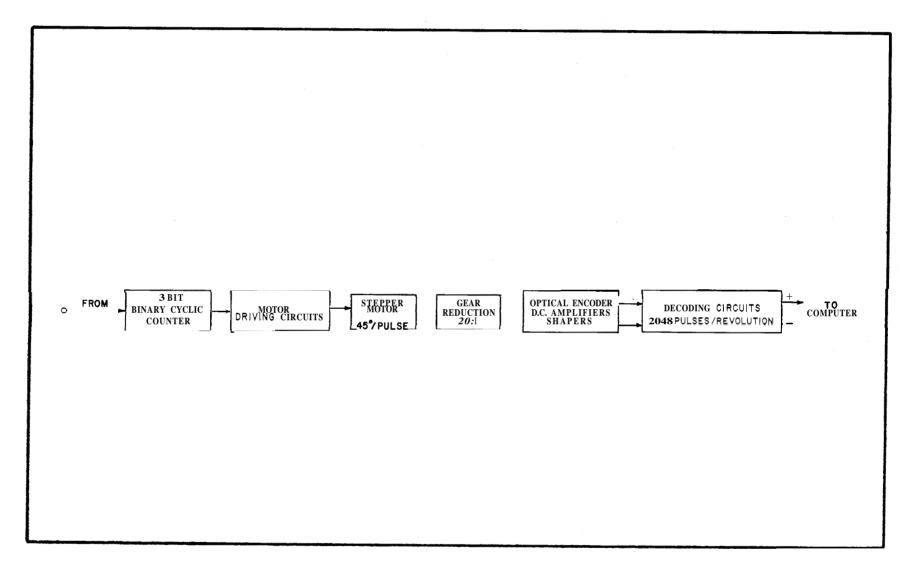

| Fig. | <b>2 -</b> 5  | Stepper-motor Drive and Encoder ,                                     | , | , | 56   |

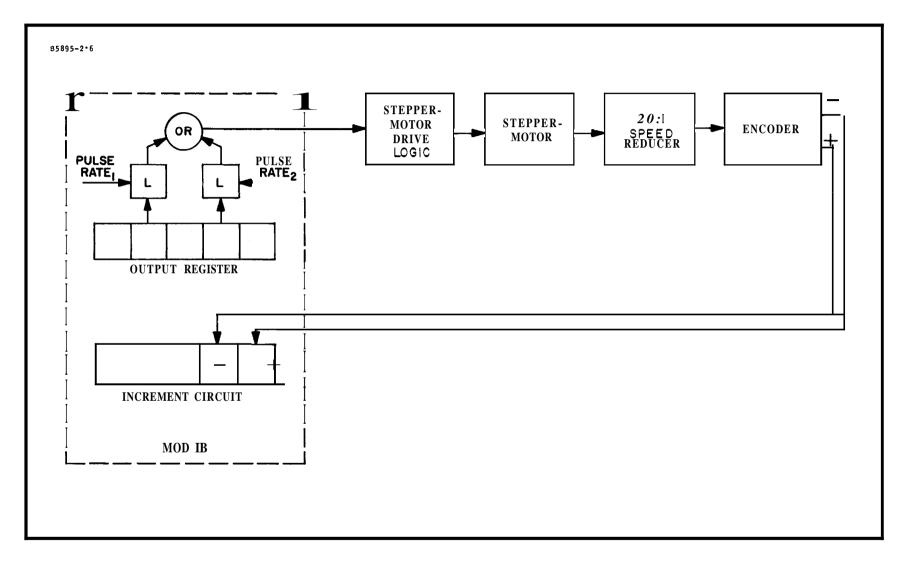

| Fig. | 2 - 6         | Stepper-motor Control System . , , .                                  | , | ı | 57   |

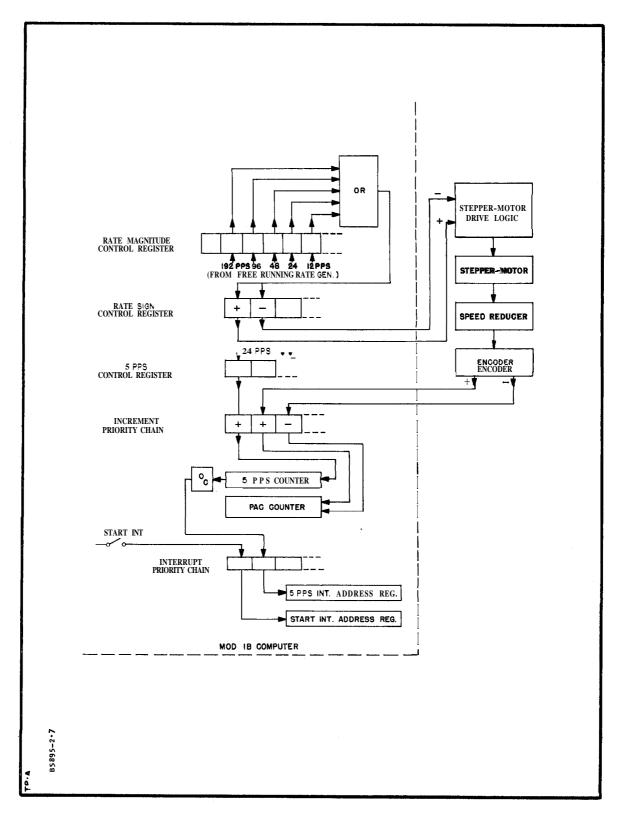

| Fig. | 2 - 7         | Detail of Rate Control , ,                                            | , |   | 58   |

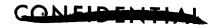

| Fig. | 2 - 8         | Detail of Position Control , ,                                        |   |   | 59   |

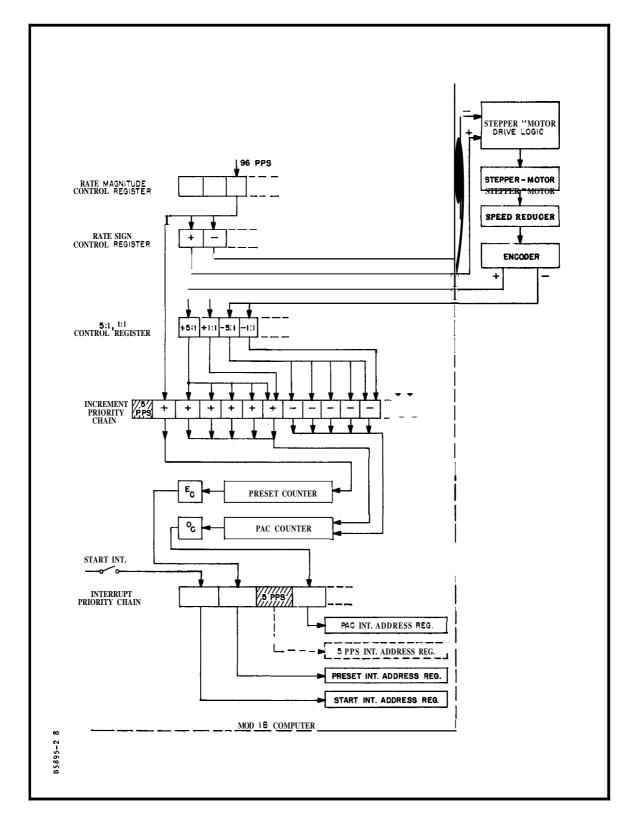

| Fig. | <b>2 -</b> 9  | Flow Diagram of Control Program                                       |   |   | 60   |

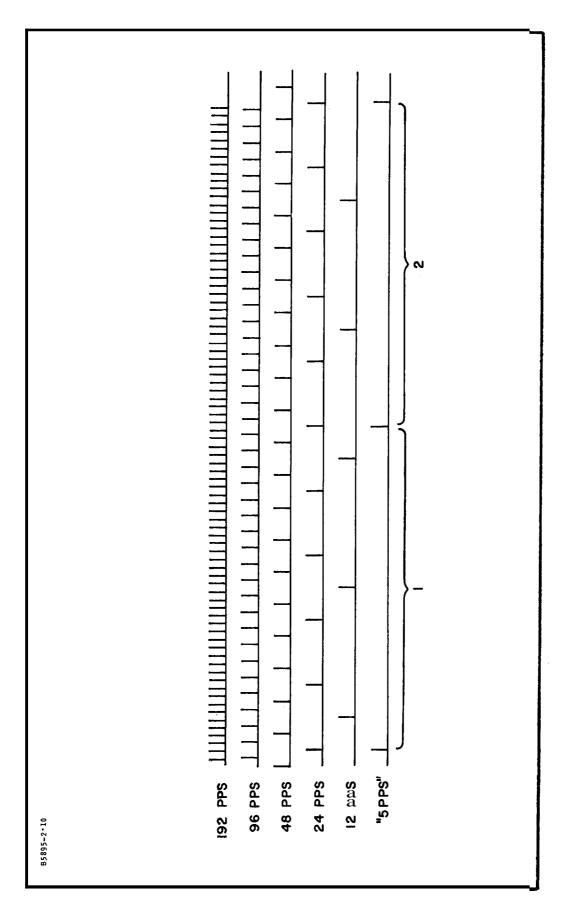

| Fig. | <b>2</b> - 10 | Applied Pulse Rates                                                   |   |   | 61   |

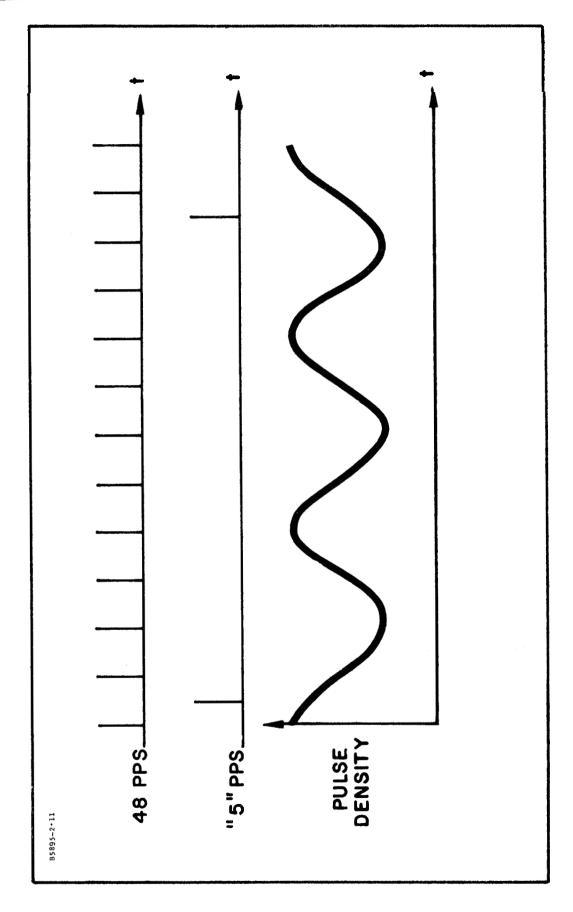

| Fig. | 2 - 11        | Pulse Density of Encoder Output ,                                     |   |   | 62   |

| Fig. | 3 - 1         | Basic Circuit Configuration                                           |   |   | 93   |

| Fig. | 3 - 2         | Clock Block Diagram ,                                                 |   |   | 94   |

| Fig, | 3 - 3         | One Stage of Clock Shift Register                                     |   |   | 95   |

| Fig, | 3 - 4         | Sequence Generator ,                                                  |   |   | 96   |

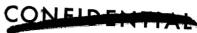

| Fig, | 3 - 5         | Increment Priority Chain. , , . , .                                   |   |   | 97   |

## CONFIDENTIAL

|                    | Pag                                                       | ,e |

|--------------------|-----------------------------------------------------------|----|

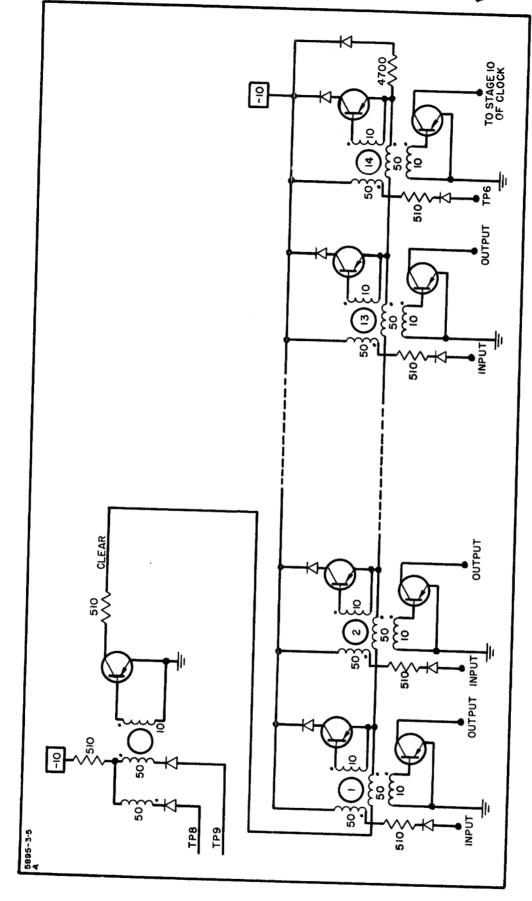

| Fig. 3-6           | Sneak Current Paths in Priority Chain 98                  | 3  |

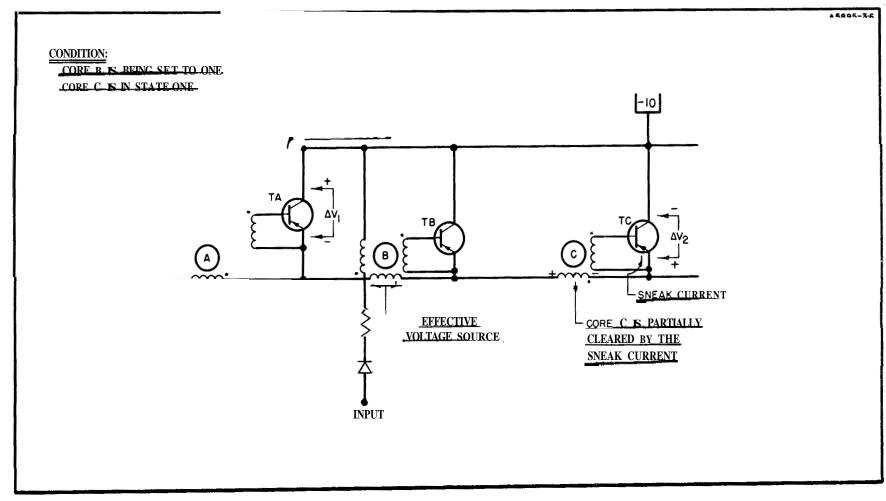

| Fig. 3 - 7         | Interrupt Priority Chain                                  | 9  |

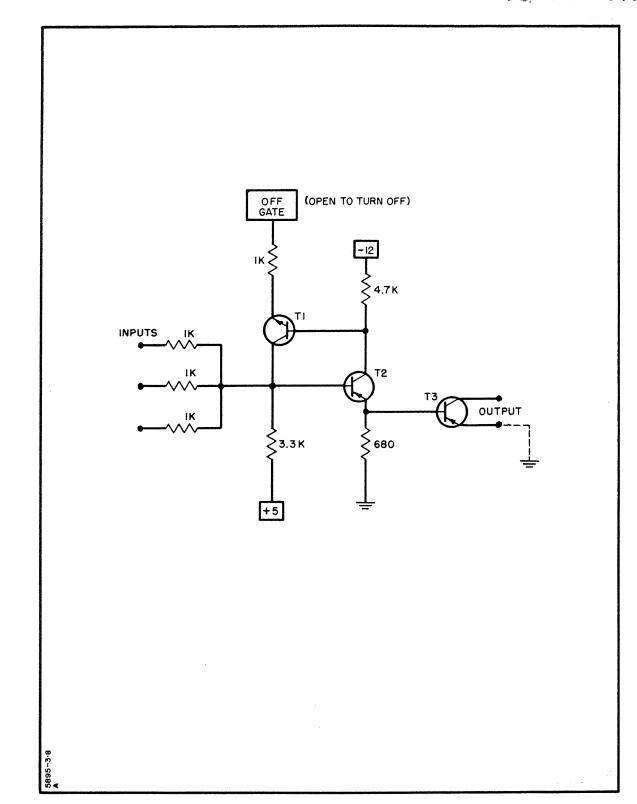

| Fig. 3 - 8         | Latch 1 ,                                                 | 1  |

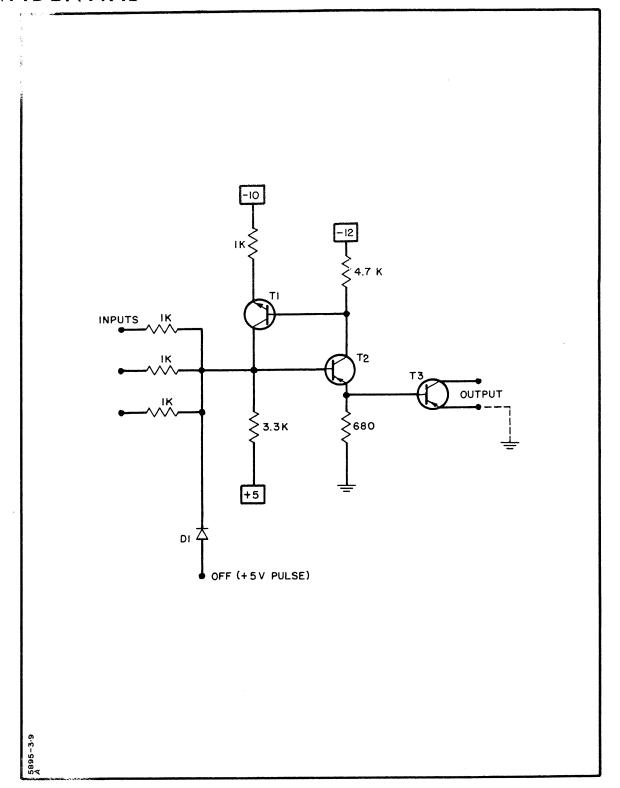

| Fig. 3 - 9         | Latch2 , ,                                                | 2  |

| Fig. 3 - 10        | Latch 3                                                   | 3  |

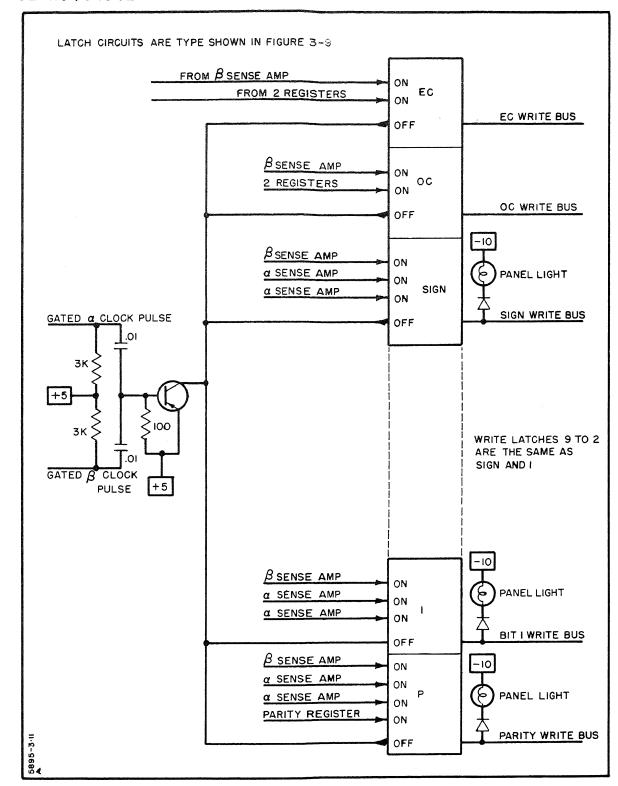

| Fig. 3-11          | Write Latches (latch circuits are type shown in Fig. 3-9) | 4  |

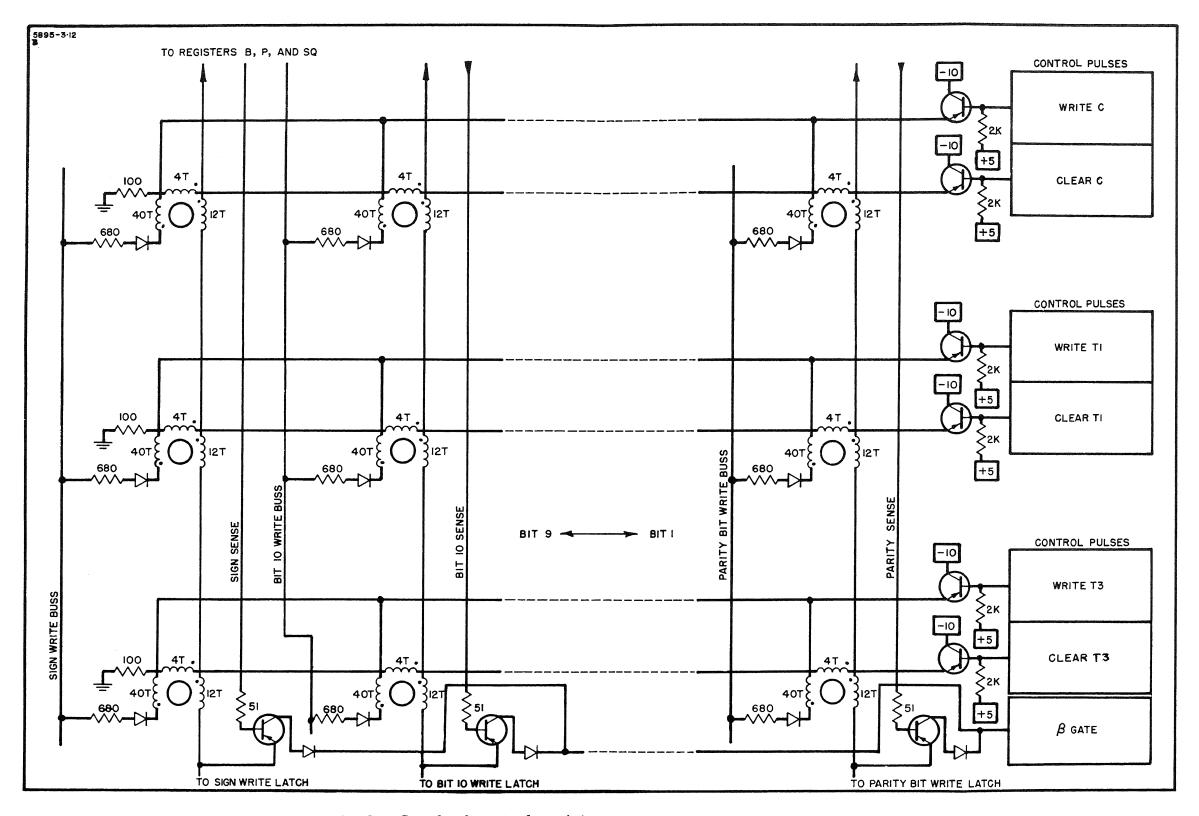

| Fig. 3-12          | Standard Central Registers                                | 5  |

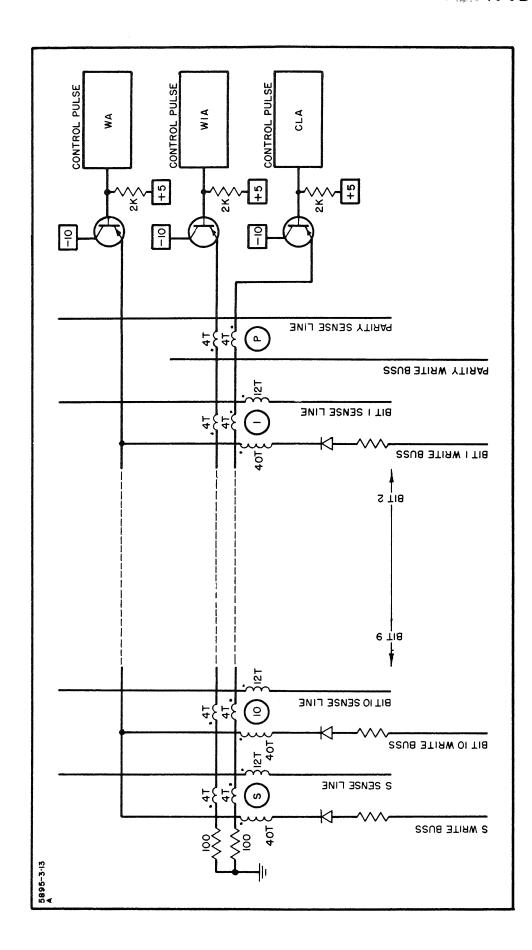

| Fig. <b>3 -</b> 13 | A Register                                                | 7  |

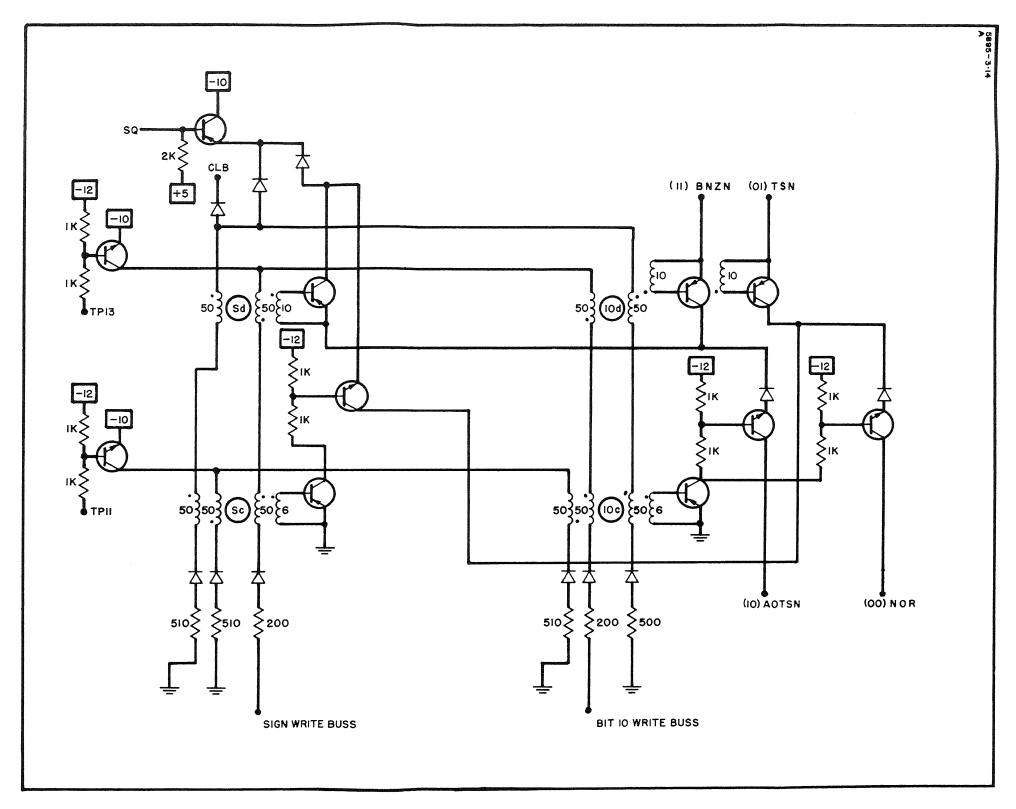

| Fig. 3 - 14        | SQ Register                                               | 9  |

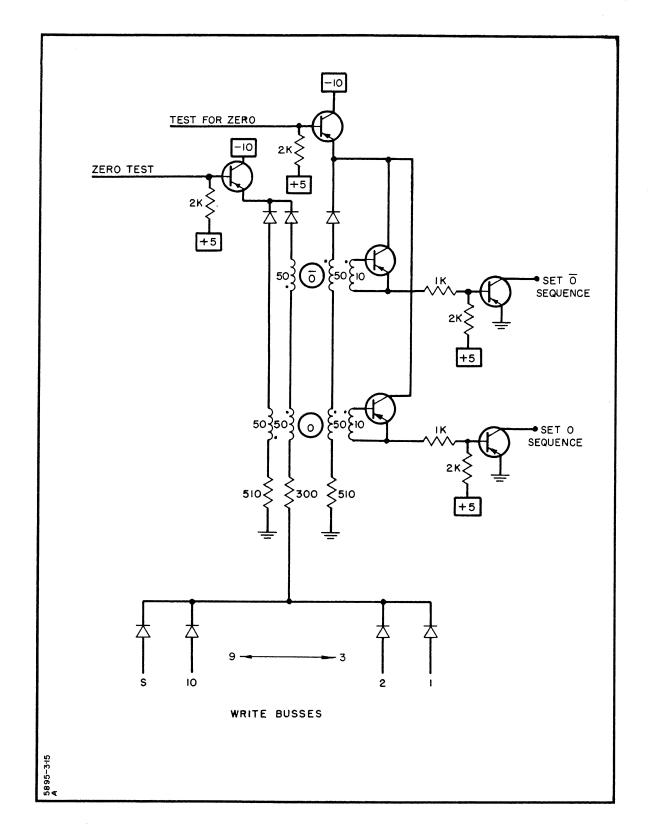

| Fig. 3 - 15        | Zero Test                                                 | 1  |

| Fig. 3-16          | "Exclusive Or" Circuit . , . ,                            | 2  |

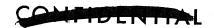

| Fig. <b>3-</b> 17  | Parity Tree                                               | 3  |

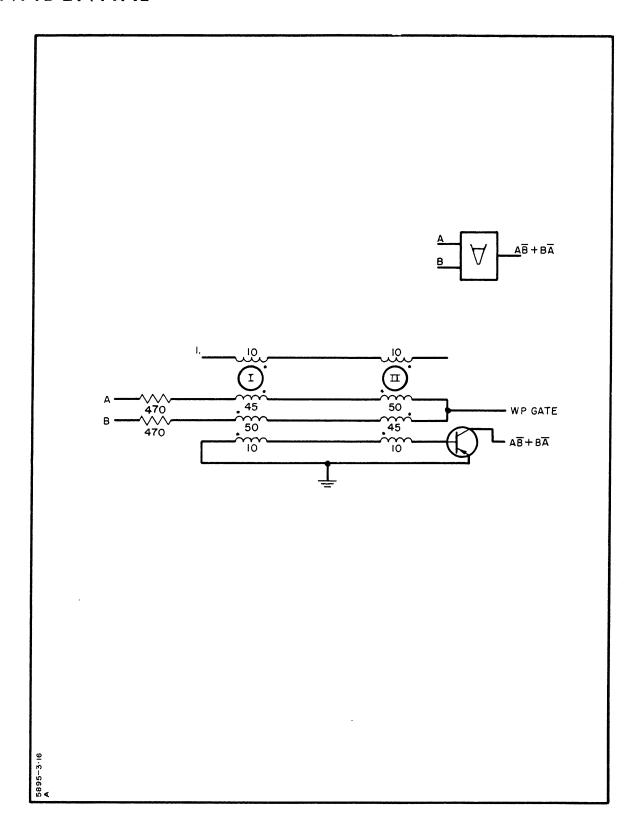

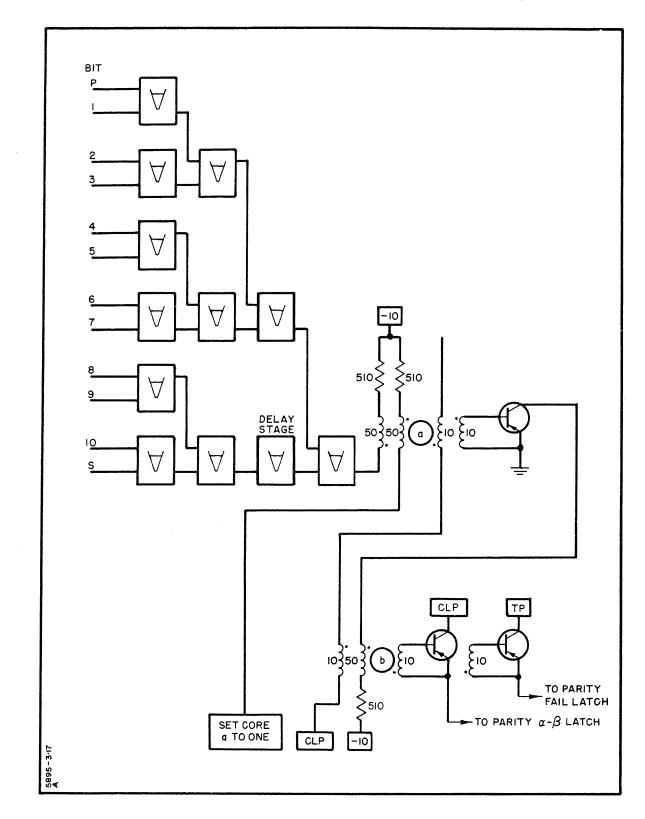

| Fig. 3 - 18        | Delayed WP                                                | 4  |

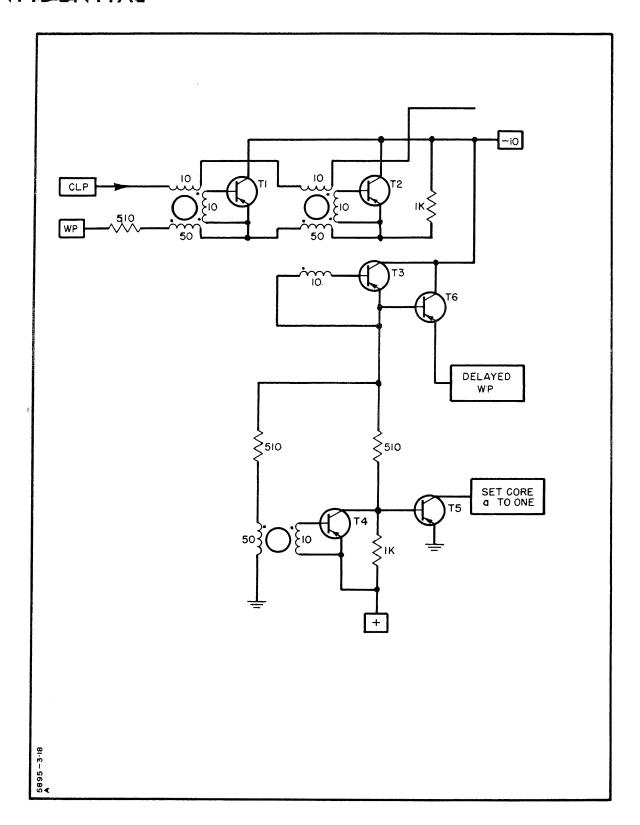

| Fig. 3-19          | Block Diagram of Z Register , ,                           | 5  |

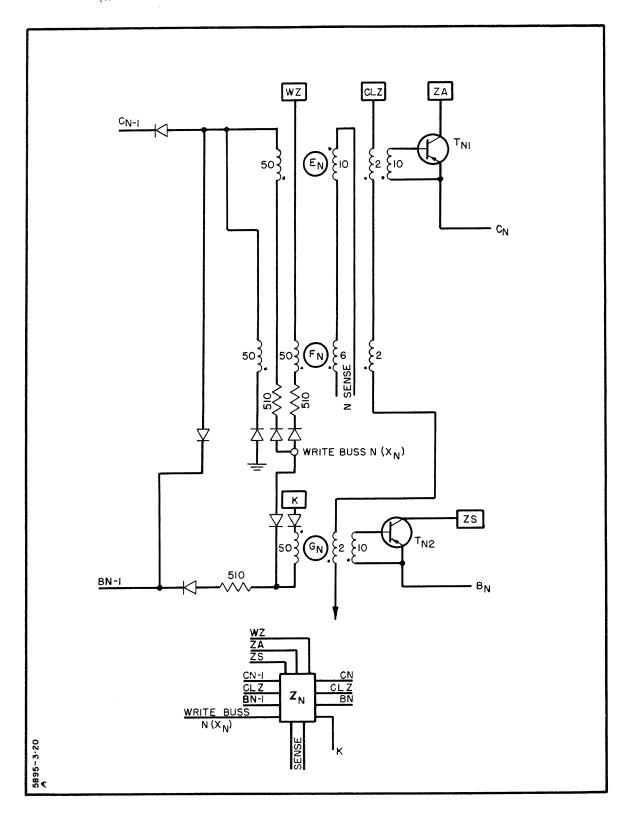

| Fig. 3 - 20        | Z INC + or                                                | 6  |

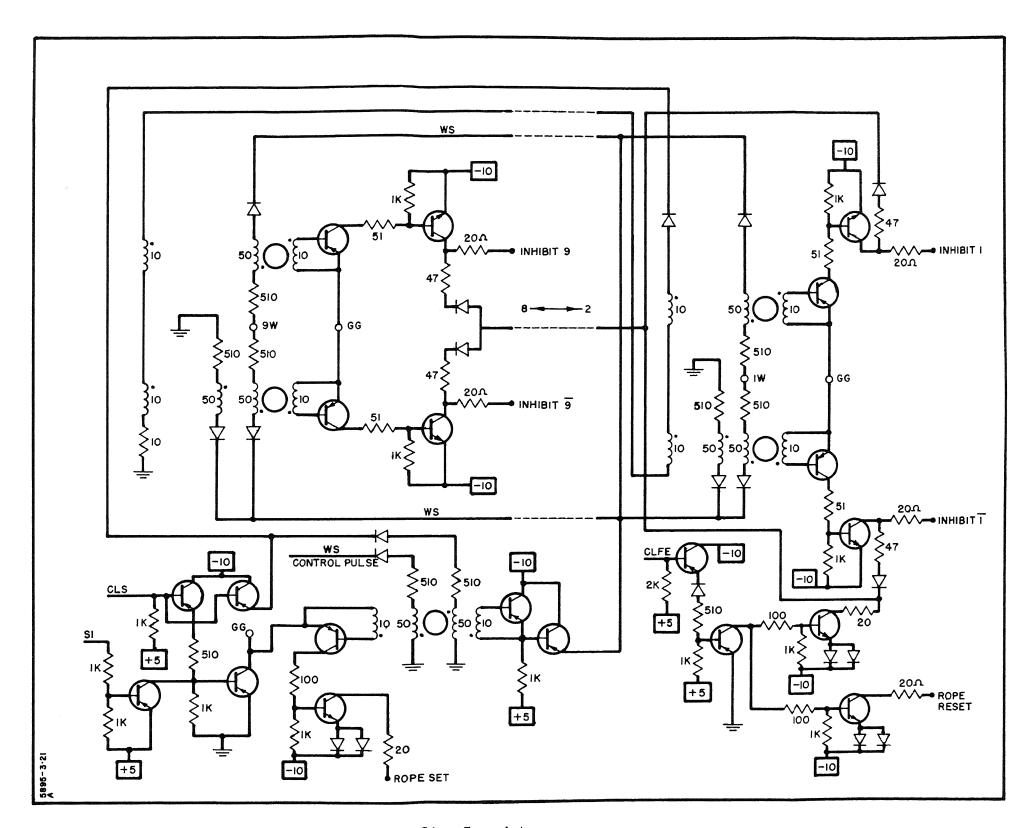

| Fig. 3 - 21        | S Register                                                | 7  |

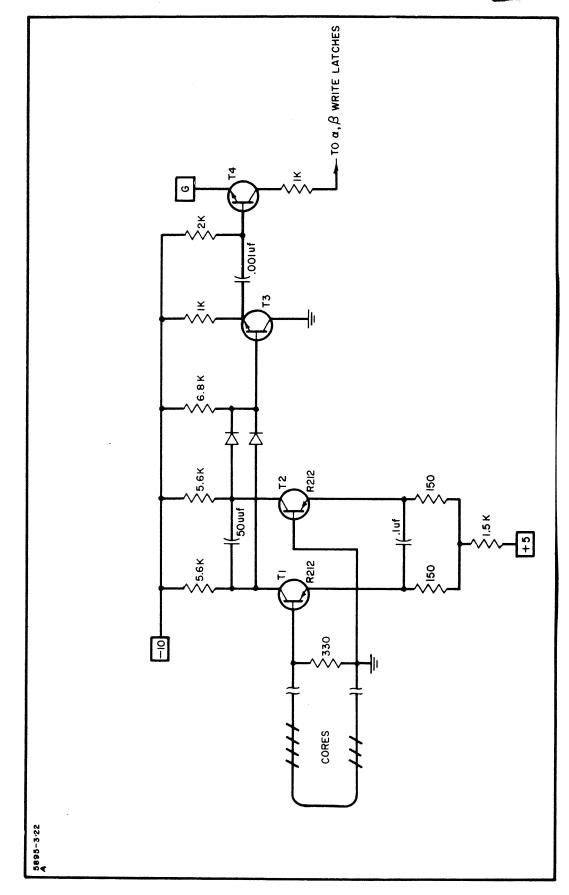

| Fig. <b>3 -</b> 22 | Rope Sense Amplifier (1 of 12)                            | 9  |

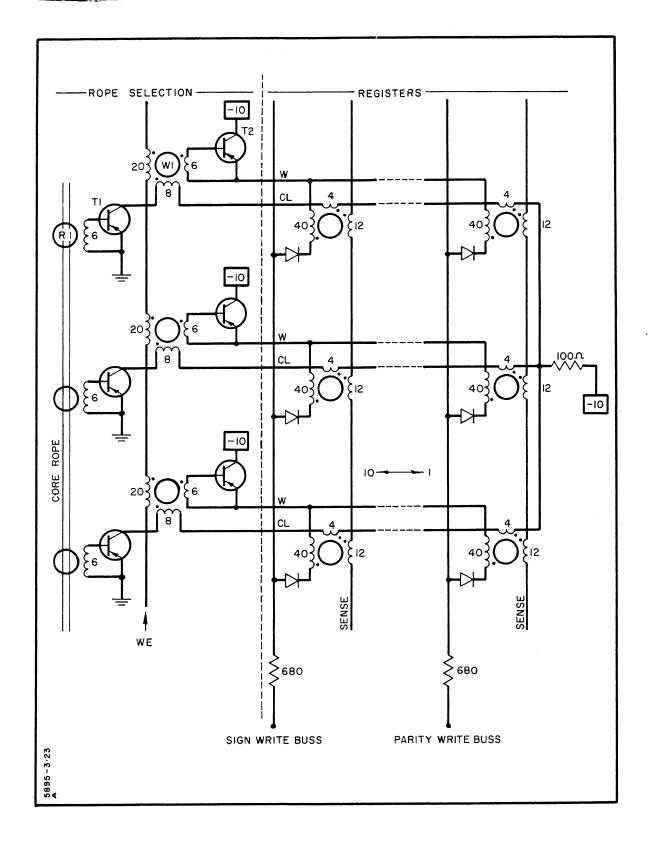

| Fig. 3 - 23        | Standard Erasable Register , , 12                         | 0  |

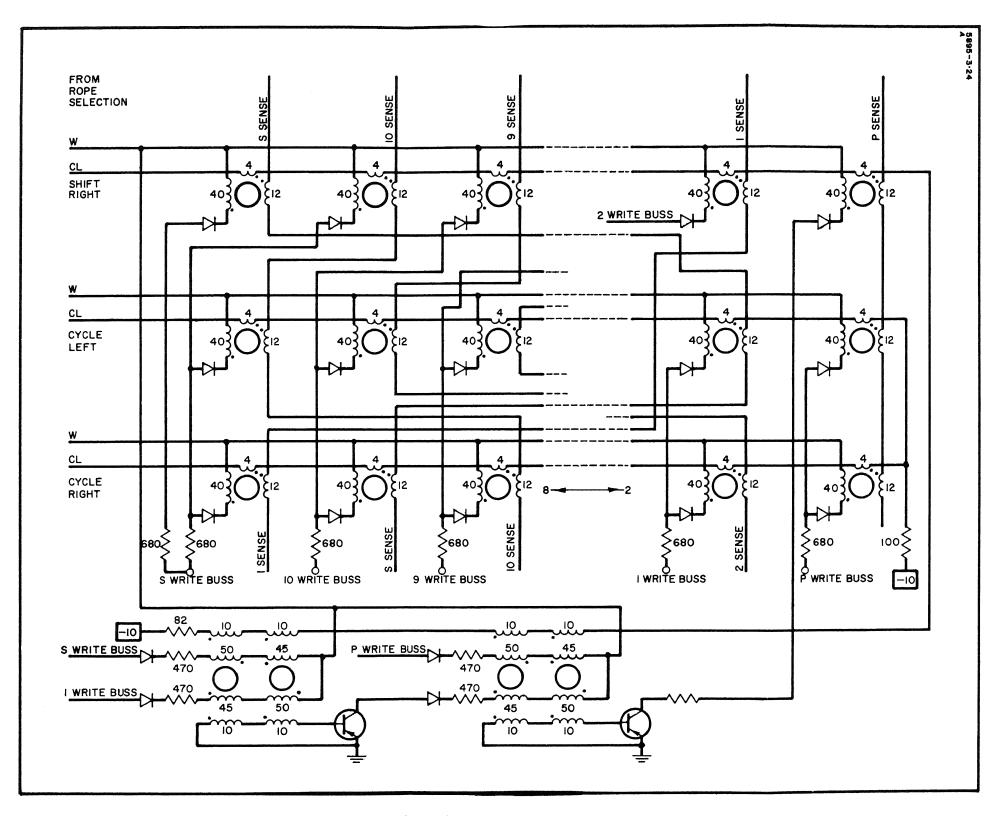

| Fig. 3 - 24        | Cycle and Shift Registers , ,                             | 1  |

| Fig. 3 - 25        | Switch Registers (2 of 4)                                 | 3  |

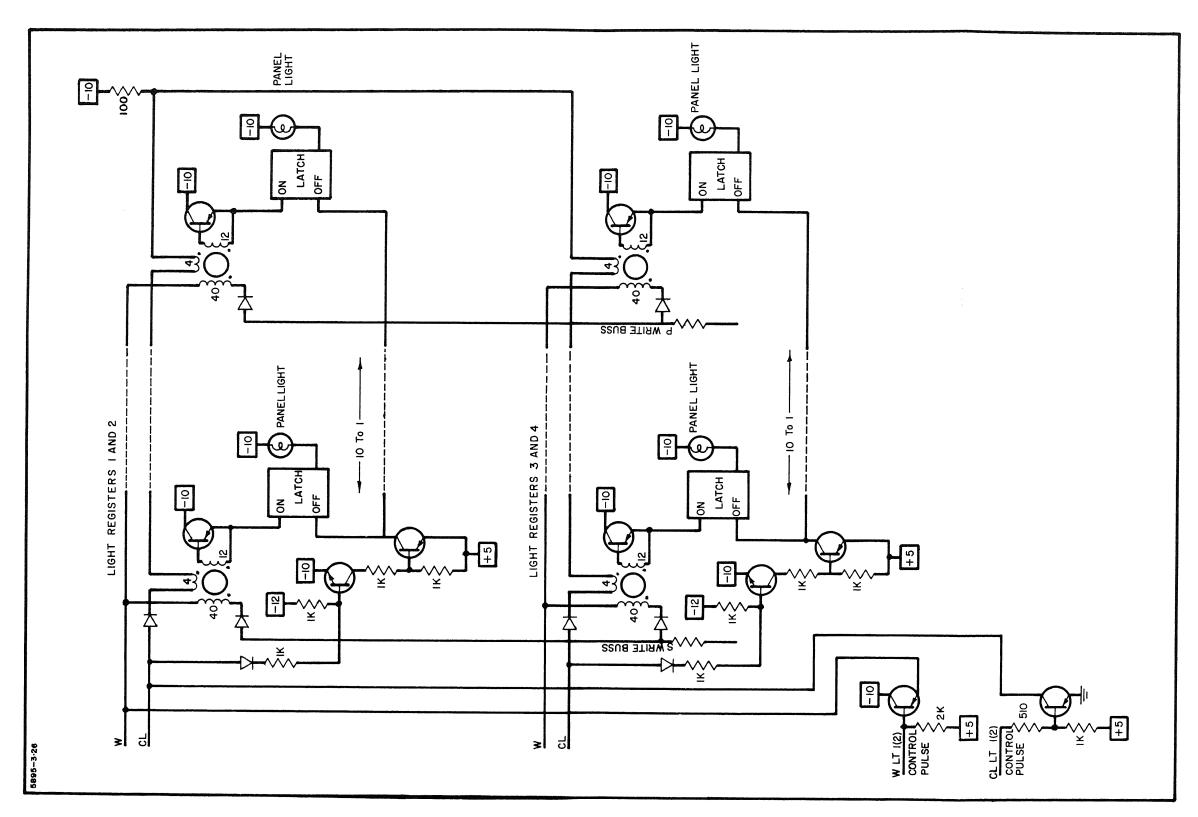

| Fig. 3 - 26        | Light Registers                                           | 5  |

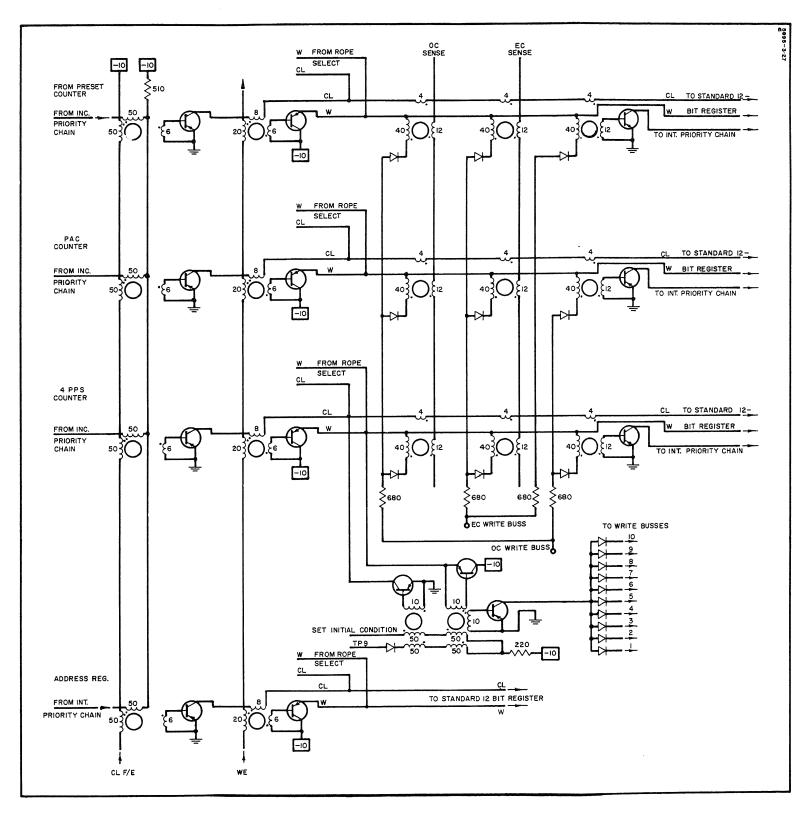

| Fig. 3 - 27        | Counter and Address Registers . , 12                      | 7  |

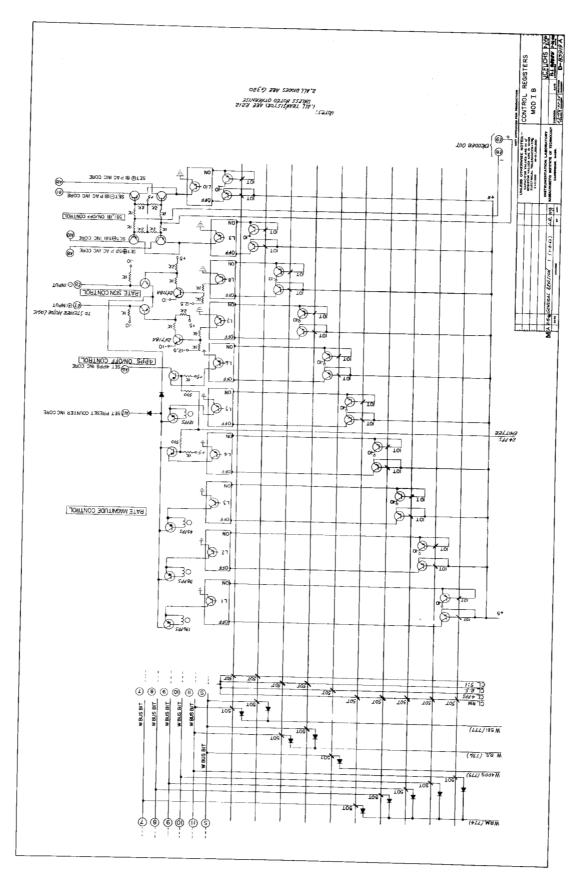

| Fig. 3 - 28        | Control Registers                                         | 9  |

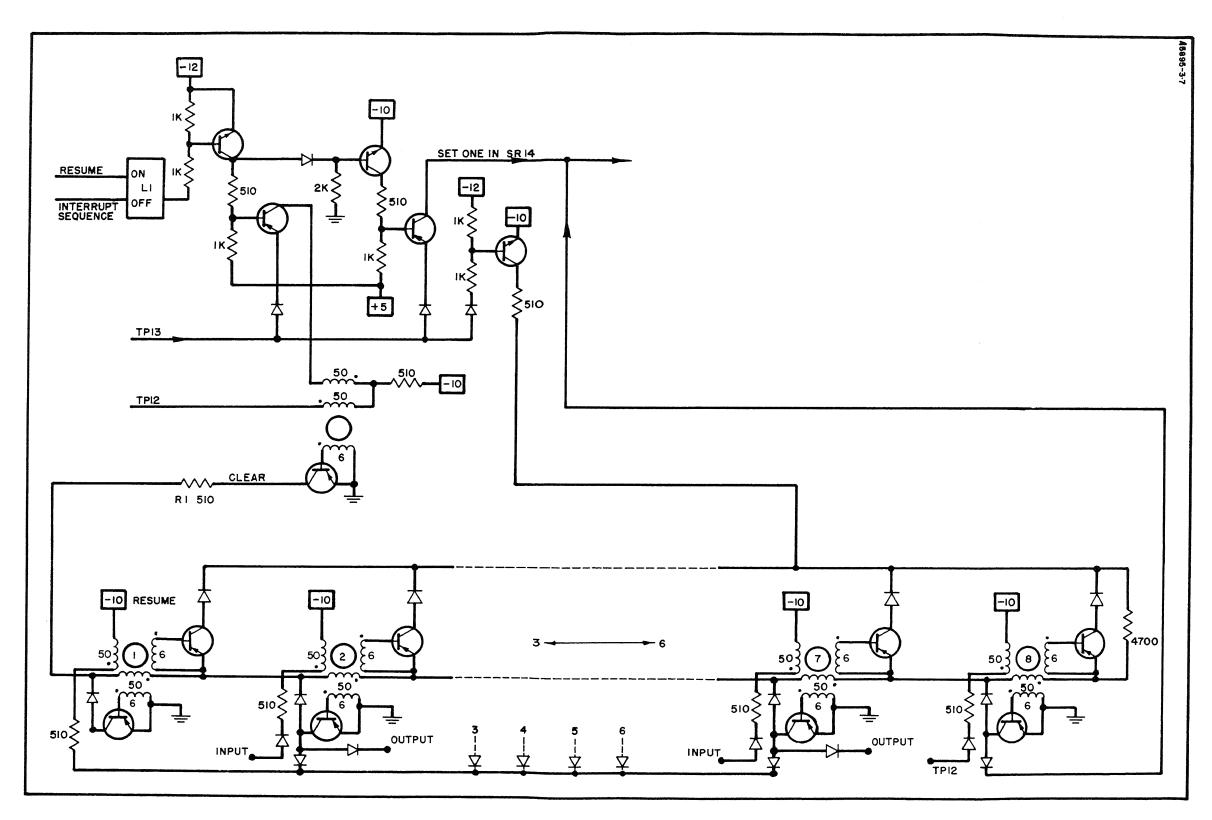

| Fig. <b>3 -</b> 29 | RESUME and Normal Stop                                    | 1  |

GONFIDENTIAL

|      |                |                                                                                                                                                                          | Pag  | ge |

|------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----|

| Fig. | 3 <b>- 3</b> 0 | Pulse Rate Source                                                                                                                                                        | . 13 | 32 |

| Fig. | 3 - 31         | Counter Section                                                                                                                                                          | . 1  | 33 |

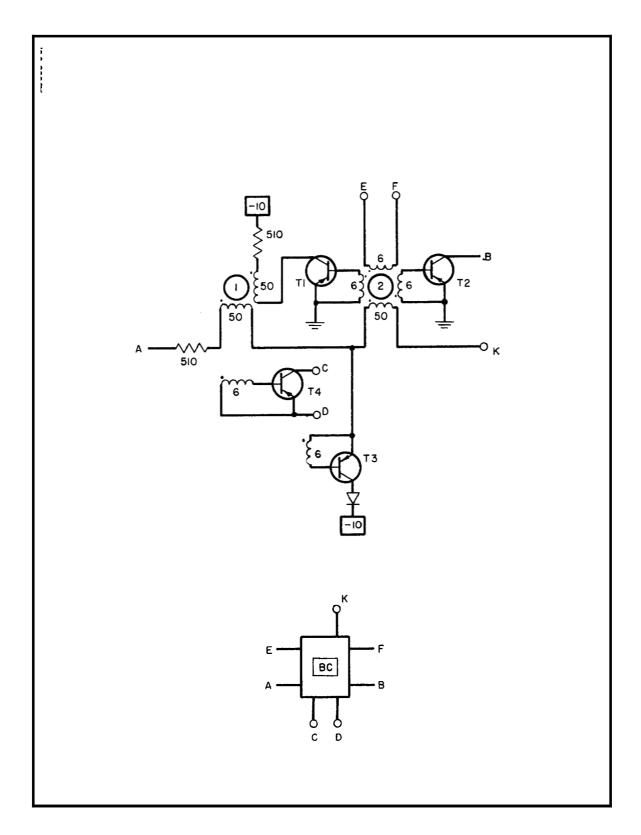

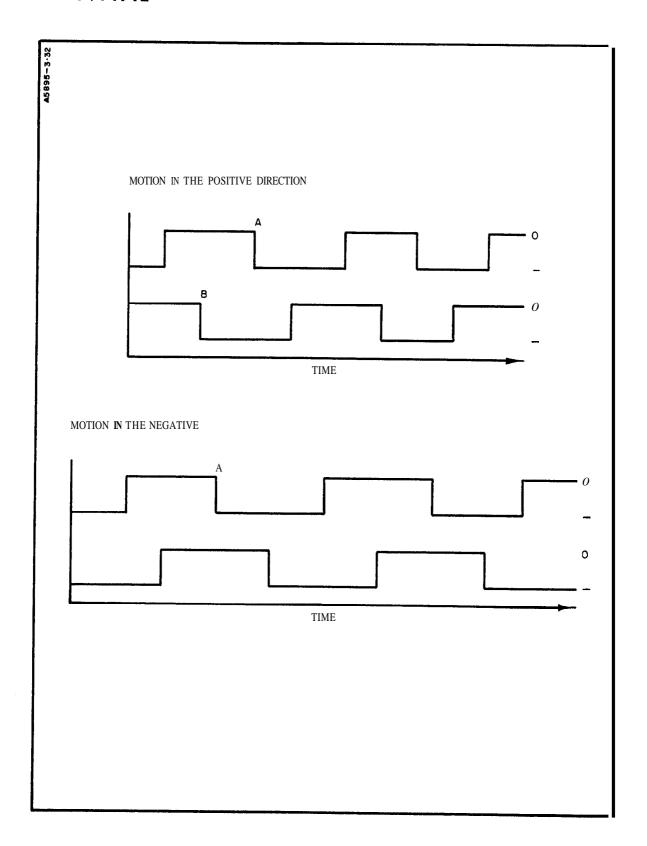

| Fig. | 3 - 32         | Photoelectric Encoder Output , , .                                                                                                                                       | . 13 | 34 |

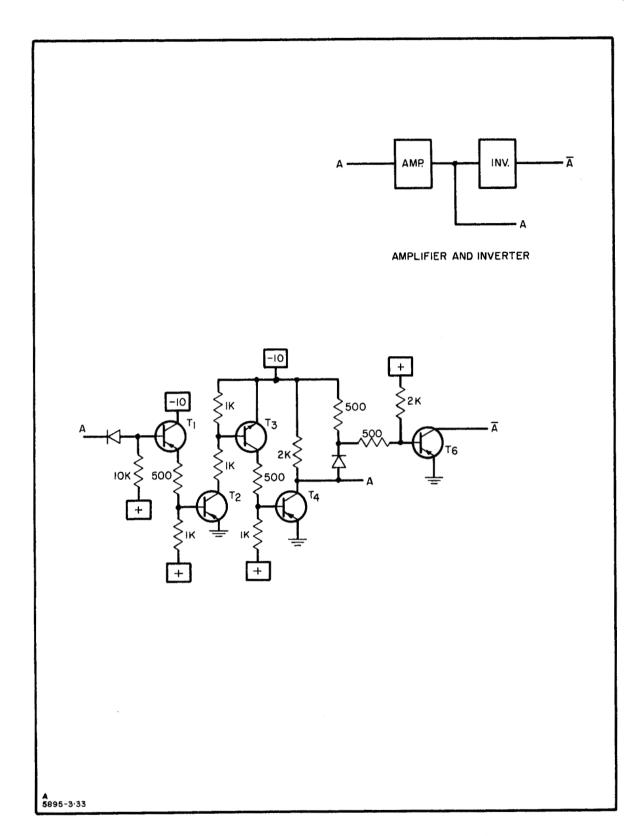

| Fig. | 3 - 33         | Amplifier and Inverter                                                                                                                                                   | . 1  | 35 |

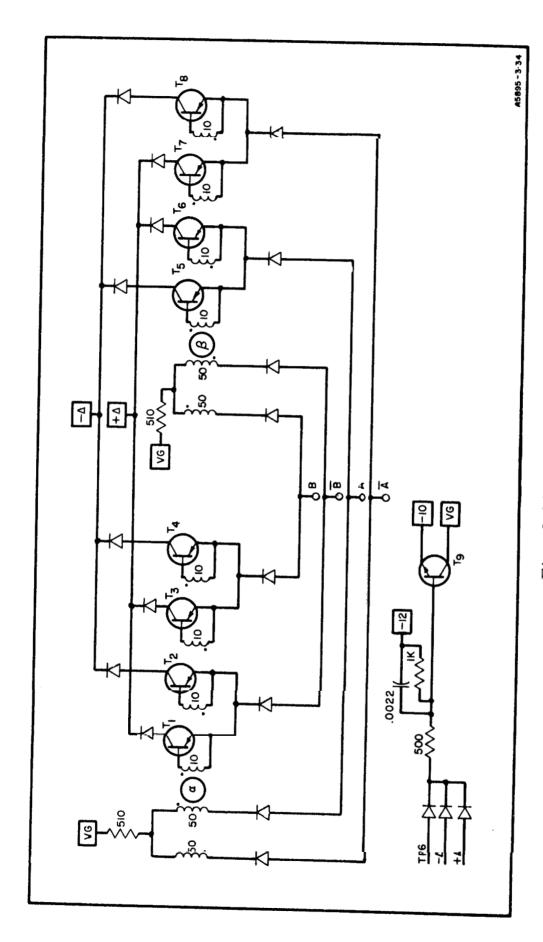

| Fig. | 3 - 34         | Decoder                                                                                                                                                                  | , 1  | 36 |

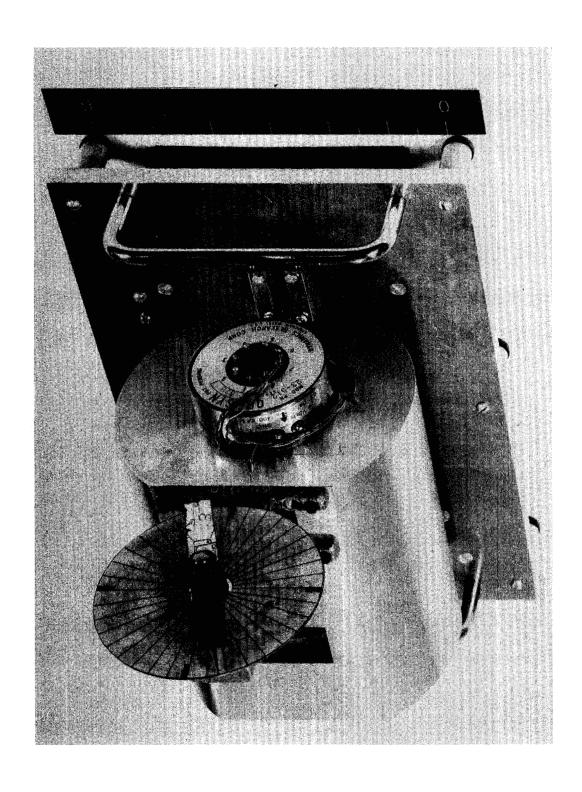

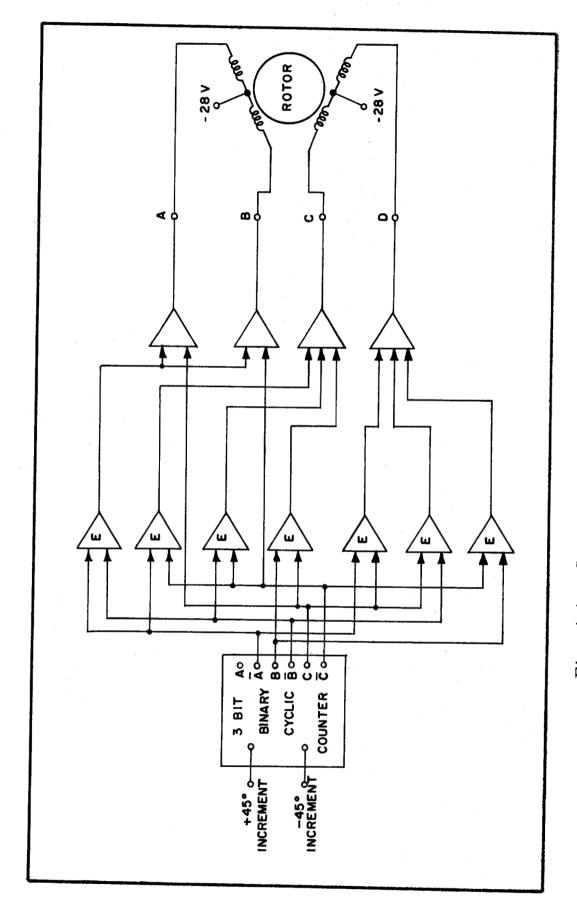

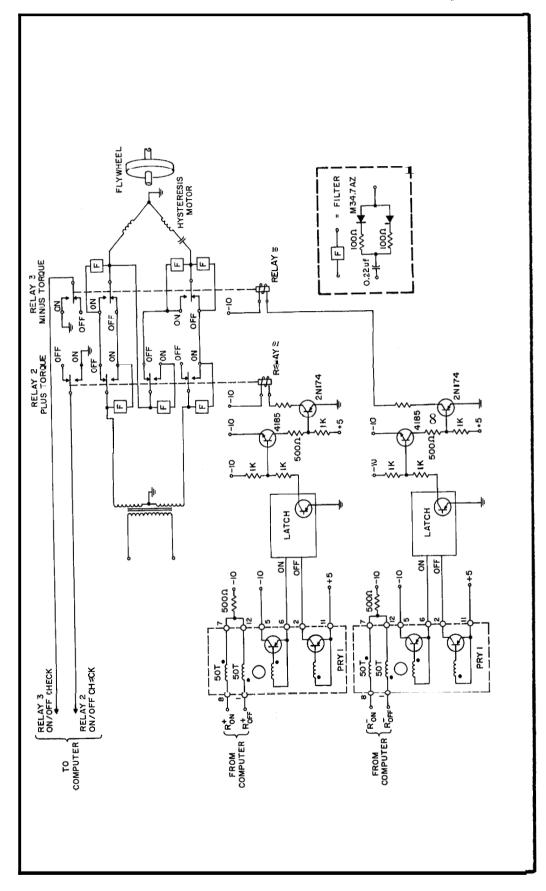

| Fig. | 4 - 1          | Stepper-motor Control ,                                                                                                                                                  | , 1  | 40 |

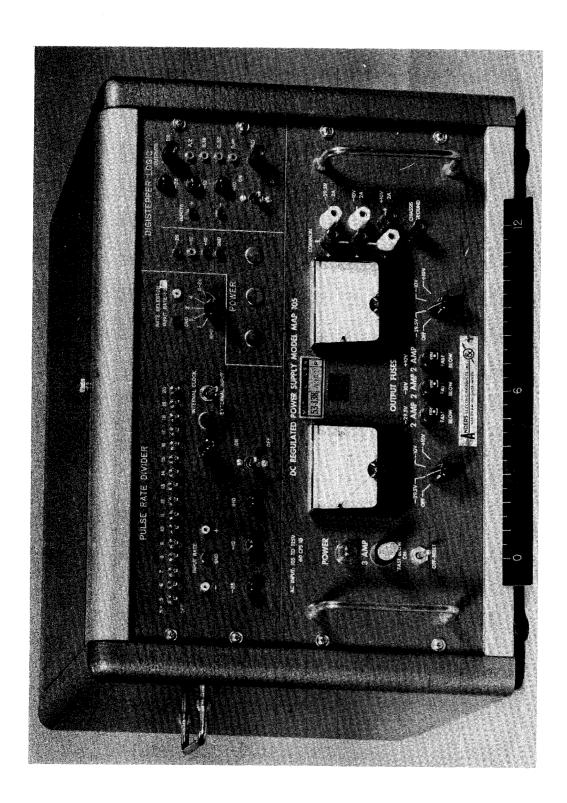

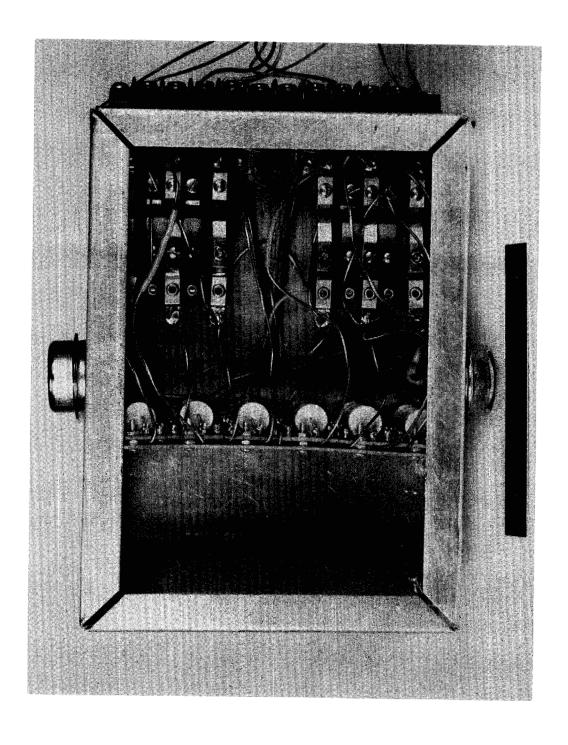

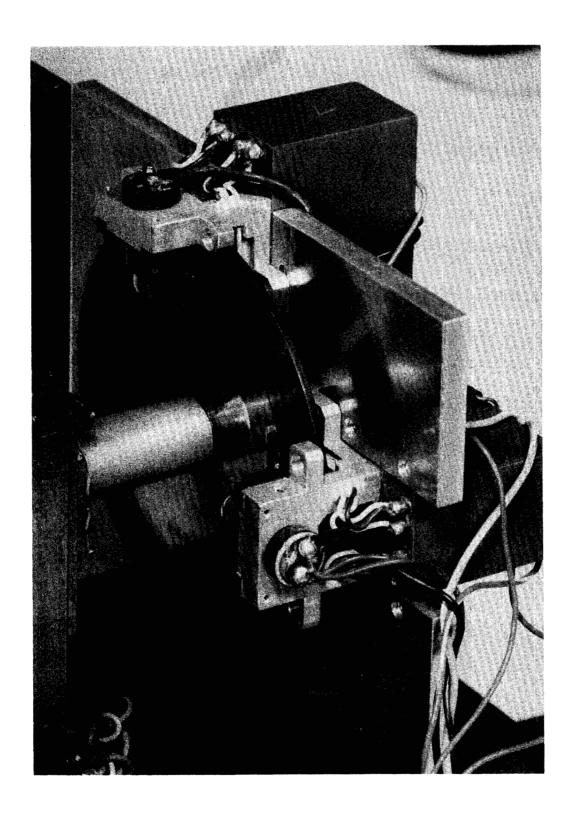

| Fig. | 4 - 2          | Stepper-motor Control Assembly                                                                                                                                           | , 1  | 41 |

| Fig. | 4 - 3          | Stepper-motor Logic Assembly                                                                                                                                             | , 1  | 42 |

| Fig. | 4 - 4          | Stepper-motor with Driving Logic Circuits                                                                                                                                | , 1  | 44 |

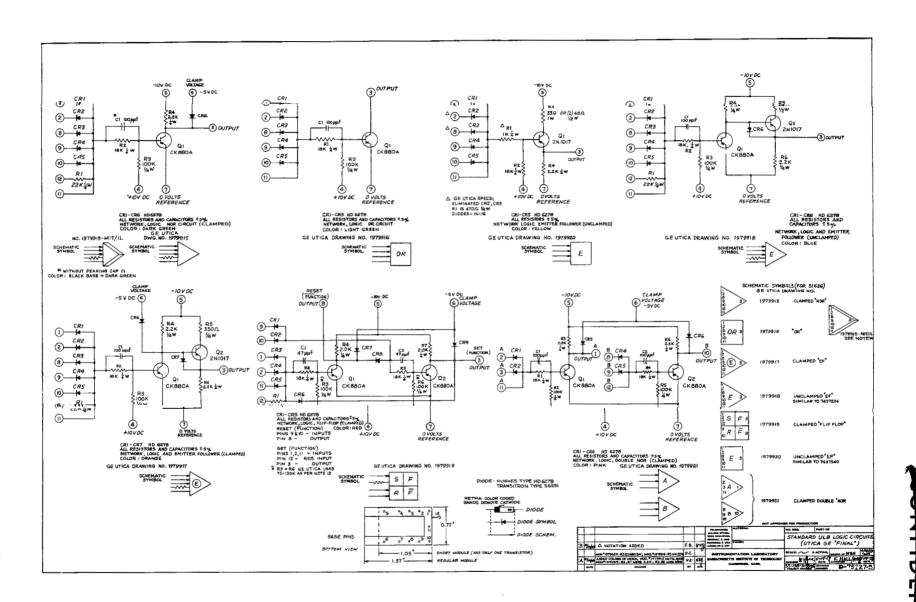

| Fig. | 4 - 5          | Standard ULB Logic Circuits (UTICA GE "FINAL")                                                                                                                           | . 1  | 45 |

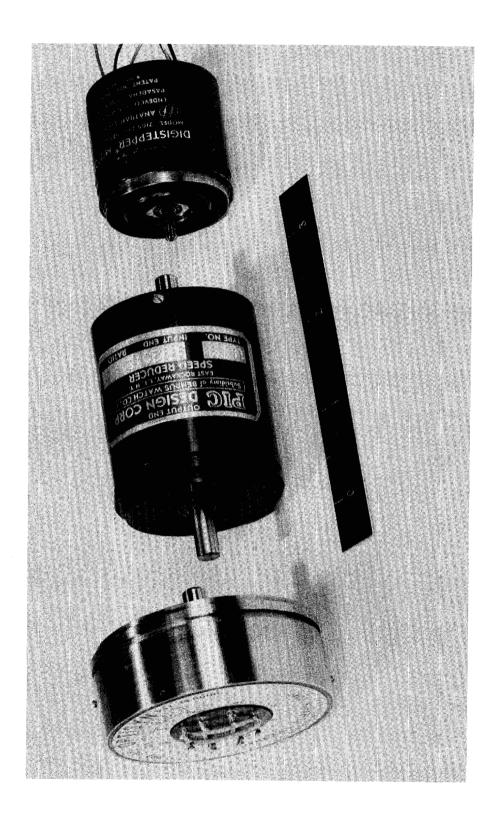

| Fig. | 4 - 6          | Stepper-motor, Speed Reducer, and Optical Encoder.                                                                                                                       | . 1  | 46 |

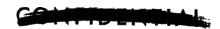

| Fig. | 4 - 7          | Step Servo Motor Size 15                                                                                                                                                 | . 1  | 48 |

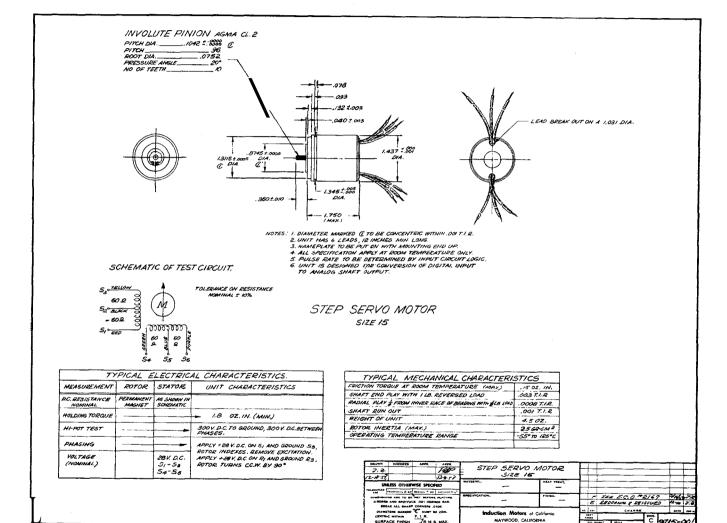

| Fig. | 4 - 8          | Optical Encoder and Decoder                                                                                                                                              | . 1  | 49 |

| Fig. | 4 - 9          | Shaper or Schmitt Trigger ,                                                                                                                                              | , 1  | 50 |

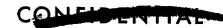

| Fig. | 4 - 10         | Block Diagram of Programed Hysteresis Motor Control , ,                                                                                                                  | . 1  | 54 |

| Fig. | 4 - 11         | Flywheel, Switching Circuit and Encoder Assemblies                                                                                                                       | . 1  | 55 |

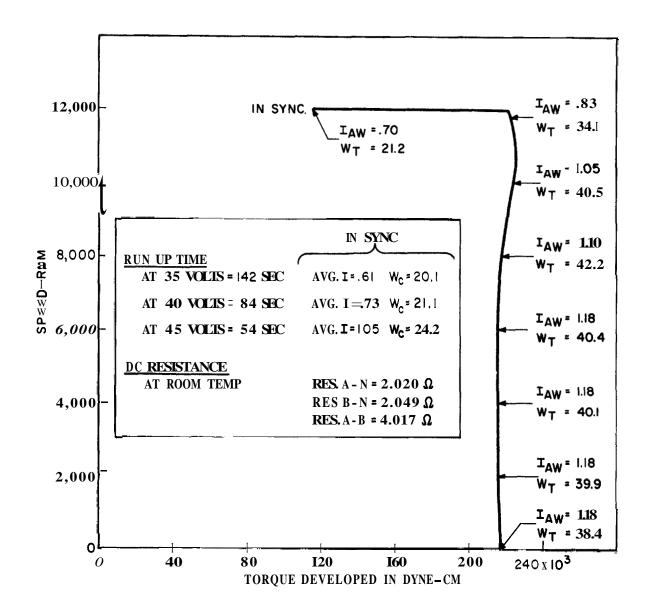

| Fig. | 4 - 12         | Speed-Torque Characteristic for the MT 27-198 Motor Tested in the IL #2 Fixture with an inertia of 9850 gm cm <sup>2</sup> 40 volts/phase, $2 \phi$ - 400 cps Excitation | . 1  | 56 |

| Fig. | 4 - 13         | Hysteresis Motor Control Circuit Diagram                                                                                                                                 | . 1  | 57 |

| Fig. | 4 - 14         | Switching Circuit Assembly                                                                                                                                               | . 1  | 58 |

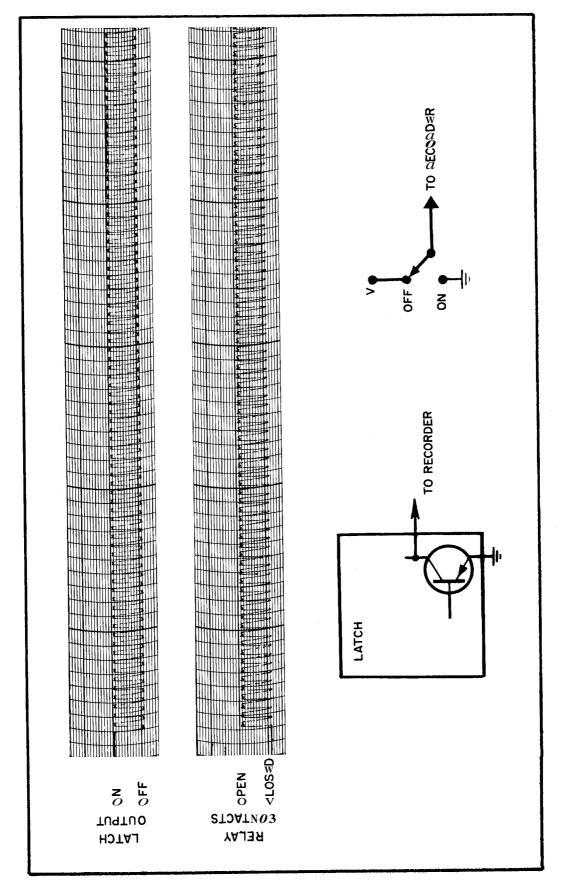

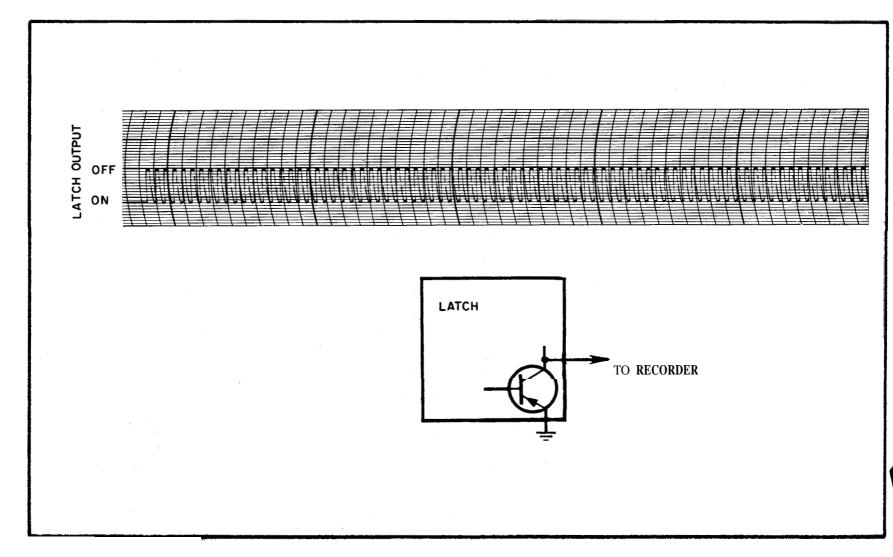

| Fig. | 4 - 15         | Latch and Relay Contact Outputs of Hysteresis Motor Control Circuit, No Filters, No Motor                                                                                | 1    | 50 |

## COMPIDENTIAL

|             |                                                             | Page_ |

|-------------|-------------------------------------------------------------|-------|

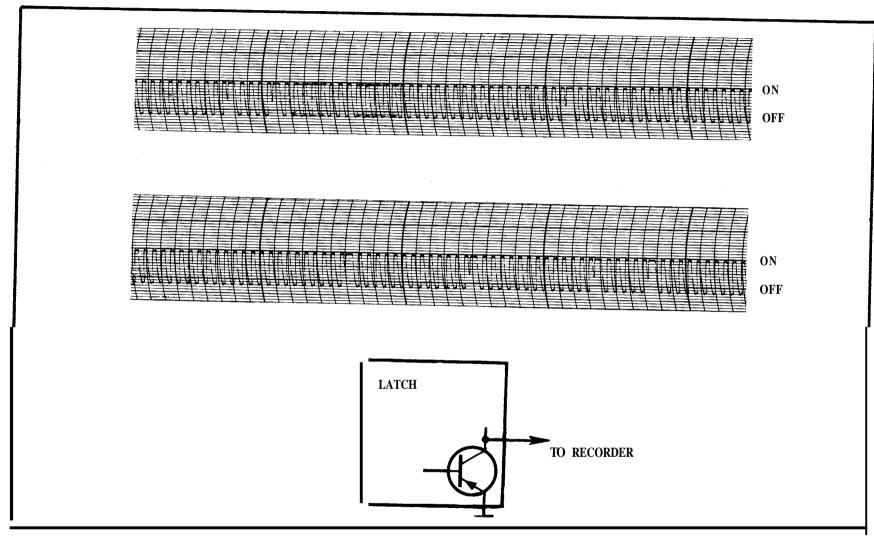

| Fig. 4-16   | A Latch Output of Hysteresis<br>Motor Control, No Filters   | . 160 |

| Fig. 4 - 17 | A Latch Output of Hysteresis<br>Motor Control Circuit , , , | , 161 |

| Fig. 4-18   | Encoder Assembly                                            | , 163 |

| Fig. 4 - 19 | Encoder Disk with Zero Slit. , , , , ,                      | , 164 |

| Fig. B-1    | Control Registers                                           | , 170 |

## LIST OF TABLES

|             |                                            | Page         |

|-------------|--------------------------------------------|--------------|

| Table I - 1 | Approximate Dates of Events.               | '9           |

| Table 1 1   | Mod 1B Order Code , .                      | 23           |

| Table 1-2   | Special Function Registers .               | 24           |

| Table 1-3   | Input Registers,                           | 24           |

| Table 1-4   | Output Registers .                         | 25           |

| Table 1- 5  | Mod 1B Storage Assignments.                | 26           |

| Table 1-6   | Sequences Involved ,                       | 30           |

| Table 1 - 7 | Test Sequences.                            | 31           |

| Table 1 - 8 | List of Control Pulses .                   | 32           |

| Table 1 - 9 | Mod 1B Tray Contents .                     | 34           |

| Table 2 • 1 | Rate Problem Results ,                     | <b>63</b>    |

| Table 2 - 2 | Position Problem Results .                 | 64           |

| Table 3 - 1 | Formation of Positive and Negative Pulses. | <b>137</b> . |

INTRODUCTION

by R. L. Alonso

#### INTRODUCTION

Report R-276<sup>(1)</sup> proposed a computer which the authors believed to have several advantages over others available at that time. The design arose from the exploitation of certain circuit techniques, namely the wired-in "core rope" memory and various core-transistor circuits such as the Priority Circuit, and was primarily logical in character.

Some months prior to the publication of R-276 it was thought desirable Go build a small demonstration computer based on those principles, as opposed to continuing to build isolated circuits and subsystems. The resulting program list called for the construction of Mod 1A and later of Mod 1B.

Mod 1A (Fig. I-1) was to be small, as simple as possible, and devoid of any sophisticated input and output. At the same time it had to demonstrate the essential features of the R-276 design. The programs written for Mod 1A, although not trivial, were of a "make work" kind, The most ambitious of these programs was a set of interpretive subroutines by means of which programs could be written in pseudo-instructions more powerful than the basic four Mod 1A instructions. Various programs were then written in pseudo instructions; these programs were essentially memory checks, including sum checks, displays and score keeping sf the number of successful executions of a basic loop.

The Mod 1A design called for 256 words'of storage, each word consisting of eleven bits plus a parity bit. Of these words, 208 were wired in programs of constants; of the remaining 48 words, 42 were erasable storage, 3 were input registers (connected to manual switches), and 3 were output registers, connected to lights. The order code set was composed of four instructions. Algebraic addition was a subroutine.

The specific goals €or Mod 1A were: to perform the functions expected of it; to show that the design in which power consumption is proportional to speed is both sound and possible; to show that a 256 core rope is practical; to show that the sequence generator is a practical subsystem. Furthermore, Mod 1A was meant to bring forth any hidden problems, and to serve as a test for the many different circuits necessary for such a computer.

Mod 1B (Fig. I-2, I-3, 1-4) was based on Mod 1A, but with a much more complicated sequence generator capable of Automatic Counter Incrementing and Automatic Program Interruption. The basis for these features was the Priority Circuit, which was not used in Mod 1A. The Mod 1B memory was expanded to include 32 more erasable registers, and 224 more fixed ones. The additional tasks set for Mod 1B were the control of a stepping motor and shaft encoder system. Either angular rate or angular position were to be controlled while concurrently executing any one of the original Mod 1A programs,

The goals for Mod 1B were the same as those for Mod 1A, plus the additional one of demonstrating the Priority Circuit and the sequence generator system based on it. Moreover, Mod 1B was to be in a real time loop and in actual control of a steppermotor, while receiving inputs from a shaft encoder. This fact made the whole system much more complicated than was the case for Mod 1A. Furthermore, at the time of conception of the construction program it was hoped that Mod 1B would also serve as a vehicle for testing various packaging schemes.

The preceding paragraphs describe the planned program. Table I-1 shows the approximate dates on which several events actually took place. Mod 1A was abandoned before completion for a number of reasons having to do primarily with difficulties of construction and the inexperience of the constructors. The point at which Mod 1A was abandoned was just short of being able to execute programs. Construction had been essentially completed

and the major task of debugging had begun. Unfortunately, the assembly methods chosen were such that attempts to modify a circuit often resulted in more troubles than were present originally. Cold solder joints were a particularly frequent and frustrating source of troubles. At the time of abandonment, all of the various major subsystems had worked individually but not together. Mod 1A was abandoned because of a gradual shift in interest towards Mod 1B. This replacement was no doubt accelerated by the desire of the builders to start with a clean slate.

Mod 1B was a more successful enterprise, attaining all goals except the packaging one. Mod 1B was able to do everthing Mod 1A was meant to do some six months after construction was started; the construction and debugging of the additional parts of Mod 1B required an additional 6 months. The peripheral equipment, i.e., the stepper-motor, encoder, and auxiliary driving electronics had been designed and built some time prior to January 1961.

Mod 1B is composed of eight trays, two and a half of which contain circuitry additional to what was needed for Mod 1A. The entire computer required about one thousand transistors, and consumed about 25w when operating at full speed. This latter figure includes about 10w used for input, output, and display purposes.

Those registers which are common to both Mod 1A and Mod 1B are marked by the letter A following their octal address, which in this case is from 000 to 377. All addresses from 400 to 777 have the letter B following them, and represent registers added to Mod 1A to form Mod 1B.

The rest of this report contains a detailed description of Mod 1B, the various programs, and the peripheral equipment. Some effort has been made to evaluate as well as describe the points which might have been done differently.

The labor of doing and building various tasks and devices described here was shared approximately as follows: the original

Mod 1A and Mod 1B concepts were proposed by J. H. Laning Jr. and R.L. Alonso\*. These programs were later modified by H, Blair-Smith. Electrical design and construction of Mod 1A was done by R. E. Oleksiak and R. L. Alonso. The detailed planning of the Mod 1B system of computer and motor was done primarily by A. I. Green and H. E. Maurer. A. I. Green wrote the sequences and the detailed control program; both he and H. E. Maurer designed a first version of the Automatic Interrupt and Automatic Increment circuitry and shared the system analysis. The stepper-motor, encoder and auxiliary circuitry were the responsibility of H. E. Maurer. The exacting task of, writing the listings for the harness wiring was done by A. I. Green and T. E. Burke. As was the case for Mod 1A, the electrical design, construction, and debugging of Mod 1B was carried out by R. E. Oleksiak and R. L. Alonso. R. E. Oleksiak designed the Parity, Z, and S registers.

H. Blair-Smith wrote the IBM 650 programs which generated the rope wiring lists, and also wrote some further programs for Mod 1B.

<sup>\*</sup>The first Mod 1A instruction sequences and test programs, including the interpretive program, were written by J.H. Laning Jr.

Fig. I-1

Mod 1B computer

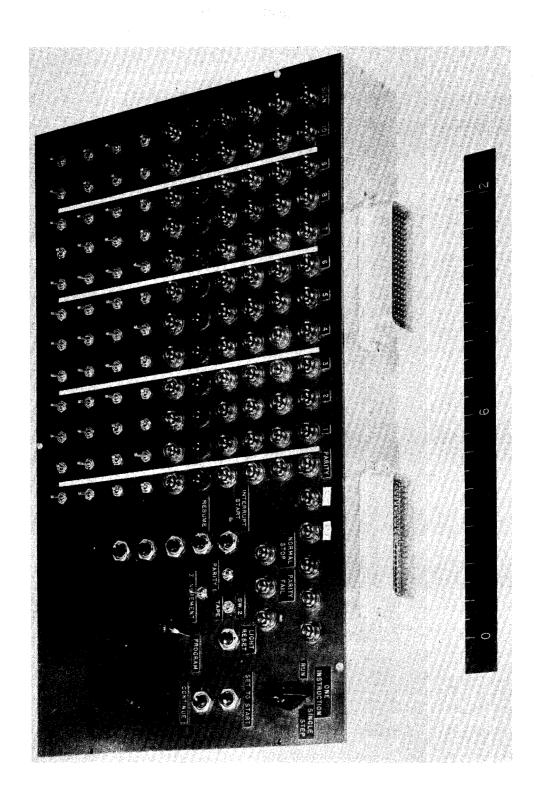

Fig. I-3 Mod 1B control panel

## ONEIDENTIAL

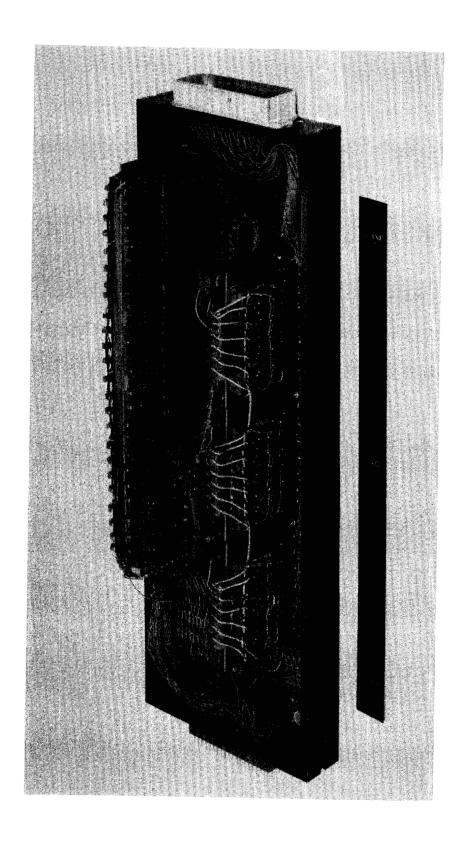

Tray 5 from Mod 1B

Table I-1 Approximate Dates of Events

| Approximate<br>Date | Event                                                                                                                                                            |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| July 1959           | Mod 1A construction started.                                                                                                                                     |

| December 1959       | Planning for Mod 1B started.                                                                                                                                     |

| July 1960           | Construction of Mod 1B started.                                                                                                                                  |

| August 1960         | Major portion of Mod 1B planning completed.                                                                                                                      |

| September 1960      | Mod 1A abandoned,                                                                                                                                                |

| November 1960       | Stepper auxiliary equipment complete.                                                                                                                            |

| February 1961       | Part of Mod 1B common to Mod 1A completed and debugged (Mod 1B able to do everything Mod 1A was supposed to do).                                                 |

| July 1961           | Construction of Mod 1B completed.                                                                                                                                |

| August 1961         | Debugging of Mod 1B completed, Mod 1B performs all intended functions of Program Interruption, Automatic Counter Incrementing, and control of the stepper-motor. |

# CHAPTER 1 COMPUTER STRUCTURE by R. L. Alonso

GOTTAL TIAL

#### CHAPTER 1

#### COMPUTER STRUCTURE

#### 1. 1 Order Code

A convenient way to start is to consider the organization of the computer from the point of view of the programer (Fig. 1-1). All transactions are parallel word transfers to addressable storage from register A, or to register A from addressable storage. The four instructions which comprise the 1B order code are listed, and their net effects described, in Table 1-1.

The instruction NOR derives its name from the following: if address x contains X and address y contains Y (ie, c(x) = X,, and c(y) = Y) then assuming A contains all 1's, the execution of the two instructions

NOR x

NOR y

results in

$$c(A_i) = \overline{X_i} \cdot \overline{Y_i}$$

,

where the subscript refers to the ith bit position or the ith bit. That is, register A now contains the bit by bit NOR of X and Y. The names of the other instructions are self explanatory.

The Table 1-1 order code is about as small and as weak as a useful order code can be. In the present case, the order code does not reveal certain special properties of some of the erasable registers (e.g., cycling right or left), which normally would be achieved by special instructions.

#### 1.2 Word Structure

The word size of Mod 1B is 12 bits, named

Bit P is the parity bit for both data and instruction words, and it is ONE if all other bits are ZERO, or if there is an even number of ONEs among the other eleven bits. Bit S is the sign bit in the case of numerical data. The number system is "ONE's complement", in which  $-x = \overline{x}$ .

The instruction word format is:

Bits S, 10: Order code.

Bits 9-1: Data address.

Bit P: Parity,

#### 1,3 Special Function Registers

There are four special function registers which are listed in Table 1-2. The cycling registers are so wired that a word written into them (e.g., by TSN CYCL) is shifted, with end-around-carry, by the act of writing into that register. A subsequent instruction NOR CYCL will read the cycled word out of CYCL. Thus the pair of instructions

TSN CYCL,

NOR CYCL,

has the net effect of causing the contents of A to be cycled left by one bit position as well as complemented.

The Shift R Register operates in much the same way, but with an important exception. The sign bit is written not only into bit position 10, as in the case of CYCR, but into the sign position as well; and bit 1, which in CYCR is written into the sign position, is lost. The shifting operation is equivalent to multiplication by  $2^{-1}$ , whereas the cycling operation is not.

The parity bit is not disturbed in the case of cycling, and parity is preserved. This is not the case in the shifting operation, and special provisions must be made for this.

## 1.4 Input Registers

The input registers are listed in Table 1-3. The Switch

Registers are ordinary erasable registers which have the core windings, normally connected to the Write Busses, connected to external toggle switches, The electrical details are shown elsewhere in this report.

The toggle switches take the place of the A register in the execution of  $TSN\ x$ , if x is a Switch Register. Hence the pair of instructions

TSN SW1,

NOR SW1,

results in

$$c(A) = -c(SW1) = c\overline{(SW1)}.$$

The three Counter Registers are again ordinary erasable registers which have additional means for being addressed by external circuitry. These registers act as accumulators of trains of pulses where the incrementing is done in such a way that there is no logical interference with the normal execution of instructions, even if these involve the active counter register. Each pulse counted requires 30 psec, so that counting at a rate of 1 kc slows down the normal program execution by  $\frac{30 \times 10^3}{10^6}$  = .03 of full speed. The details of operation of these Counter registers are given in other sections of this report. As far as the programer is concerned, counters are erasable registers which may be interrogated or written into as any other registers, and which have the further property of accumulating pulses from an external source. Writing into a counter is a way of presetting it so that it will overflow after so many pulses. The overflows, underflows, or endaround carries of these counters can be considered to be outputs.

## 1,5 Output Registers

Output registers are listed in Table 1-4, Each bit of an output register has associated with it a latch, which is a bistable device analogous to a flip-flop. The instruction TSN LT1 for example, turns to ON all those latches of register LT1 which correspond to positions in which A had a ONE. If c(A) = 0,

then all the latches of LT1 will be left in the OFF state, regardless of their previous states.

Latch outputs are d-c levels, suitable for lighting small incandescent bulbs or turning on relays. This is true for all output registers except the STOP and RESUME registers. In these two cases the output is not a level but a short pulse, lasting about  $3\mu sec$ . The functions of these registers will be described later.

It is not possible to interrogate an output register. The result of NOR x, where x is an output register, is to read a word of all ZEROs from storage, where the parity bit is also ZERO. This will fail to pass the parity check.

### 1.6 Central Registers

Figure 1-2 shows the Central Registers of Mod 1B. The computer is divided into two halves, an  $\alpha$  side and  $\beta$  side, "a Time" is defined as the time of clearing information out of the  $\alpha$  side, sensing it, turning ON the appropriate Write Busses, and writing it somewhere in the  $\beta$  side; " $\beta$ Time" is the converse. Times  $\alpha$  and  $\beta$  alternate.

The various registers are operated by means of Control Pulses. These pulses are generated by a subsystem called 'Sequence Generator', which is discussed later. Listed below are all the central registers, together with their pertinent control pulses and a pulses which clear the named (Z or S here) register to all ZEROs. Pulses WZ, WS are such that they cause writing into the named register. What is written into a register is whatever is present in the Write Busses.

The following is a list of central registers and their properties. The parenthesized ( $\alpha$ ) or ( $\beta$ ) refers to which side of the machine they belong.

Z(α) Capable of adding 0, ± 1 to whatever is written into it.

Control Pulses CLZ; WZ; ZA (for Z Add); ZS (for Z subtract).

WZ alone causes the number on the Write Busses to be written into Z unchanged, i.e., cores of Z are driven to ONE if they correspond to Write Busses at ONE, and left at ZERO otherwise. WZ and ZA together cause the number to be incremented by one. WZ and ZS together cause the number to be decremented by one. The Z register has circuits for detection of overflow, underflow and, end around carry and borrow. Of these, only overflow and end around carry are used in 1B.

A(α) Complementing register. Control pulses CLA, WA, W1A.

Pulse W1A sets A to all ONEs. WA results in cores of A being driven to ZERO if they correspond to Write Busses which are at ONE, and left undisturbed otherwise; This is the opposite action from the normal, in that WA results in clearing cores to ZERO rather than setting them to ONE.

- S(α) Address register. Control Pulses CLS, WS.

WS results in writing into cores of S the information present on the first nine Write Busses. CLS clears the cores of S, and in so doing a single core of the 512 cores Rope is driven from ZERO to ONE. Every core in the Rope corresponds to a unique word cleared out of S. Both Fixed and Erasable are addressed by means of the cores in the core Rope.

- T2(α) Storage for interrupt. Control Pulses CLT2, WT2.

When a program interruption is called for, the contents of Central Register C are preserved in T2. As will be repeated below, c(Z) and c(A) are preserved in T1 and T3 respectively. When the Resume Sequence

COMPLEXITAL

is called for, i.e., when the interrupted program is resumed, (c(T1), c(T2)), and c(T3) are returned to Z, C, and A, and the interrupted program is resumed.

- Buffer register. Control Pulses CLB, WB.

Used for temporary storage of information coming from Erasable and Fixed Storage.

- C(β) Auxiliary Buffer. Control Pulses CLC, WC

- Parity Register. Control Pulses CLP, WP, TP (Test Parity).

P is a one bit register. WP results in writing ONE into P if the number of ONEs in the incoming word, which includes any previous parity bit, is even; ZERO otherwise. CLP clears the P register. If Control Pulse TP is also present, the computer will stop if the bit in P was not ZERO. An 11 bit word with its correct parity added to it always has an odd number of ONEs; e.g. the number zero is represented by a word of 11ZEROs, with the parity bit being ONE.

- O. C. (β) Overflow register. Control Pulses CLOC.

O. C. is a one bit register. It is written into if and only if Z overflows as result' of adding one to a number, a fact which is electrically detected at CLZ time. If

O. C. has a ONE in it, then CLOC results in turning ON the Overflow Buss. This Buss is analogous to a Write Buss.

- E. C. (β) End around carry register. Control Pulse CL E. C.

Identical to O.C., except that a ONE is written into

E. C. if there is end around carry instead of overflow in Z.

- T1(β) Storage for interrupt. Control Pulses CLT1, WT1.

Stores C(Z) during an interrupt.

- T3(β) Storage for interrupt. Control Pulses CLT3, WT3.

Stores c(A) during an interrupt.

- SQ(β) Sequence Decoder. Control Pulses WSQ, CLSQ.

WSQ results in writing into SQ the two highest order bits (bits S and 10) of the Write Busses. CLSQ select:; one of four sequences, in this case one of the four possible instructions. This action is similar to the selection of one out of 512 cores in a rope.

#### I. 7 Sequence Generator

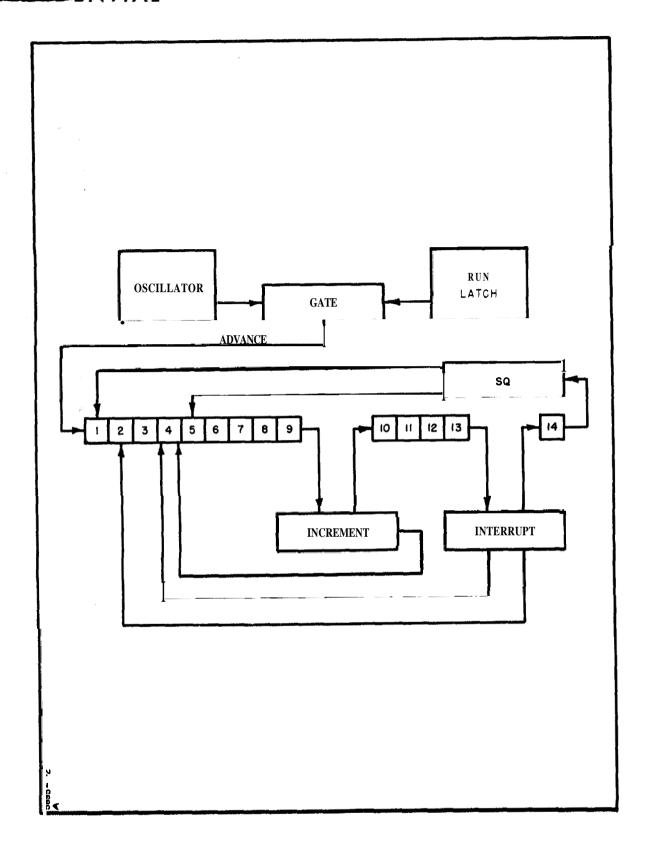

The device for generating the various necessary sequences of control pulses is the Sequence Generator. A general description of this device and how it operates is given in R-276.

Mod 1B has a total of 10 sequences. Of these, two are called Engineering Sequences E1 and E2, and play no part in the normal machine operation. 'The other 8 are listed in Table 1-6. The leftmost column lists the 14 Time Pulses, TP1 through TP14. These time pulses are generated by a shift register (abbreviated SR) in which a single ONE circulates. The columns of Table 1-6 list the various sequences by showing which control pulses occur at which times.

Each of the four instructions has a sequence associated with it. The instruction BNZN actually has two subsequences within it, as will be explained later. Sequences INT and RES refer to program interruption and resumption of interrupted program respectively. Sequences INC + and INC - refer to counter incrementing and decrementing. These last four sequences will be discussed in detail in Chapter 2.

To understand the instruction sequences it is necessary to know the initial conditions of several registers. Actually, it is easiest to start with the events of TP13 and TP14, which are the same for all instructions. At TP13 the Control Pulse CLE results in reading out of memory (Fixed or Erasable) the next instruction to be

executed. The next instruction to be executed is defined as being the word OPx, located at address L, The symbol OP refers to the two highest order bits of the word, and denotes any of the instruction codes; the symbol x refers to the address part of the instruction, The word OPx is written into registers B, C,, and P, and the OP part of the word is written into SQ. At the same time register T2 is cleared to all ZEROs. Since T2 is on the  $\beta$  side its contents are not sensed. Clearing T2 is done for reasons having to do with a possible program interruption, and not for reasons having to do with normal program operation.

At TP14, pulses CLB, WE write back into memory the word read out at TP13, if it came from Erasable. If the word came from Fixed, the WE pulse has no effect.' Pulses CLP, TP test the parity of the word, and the computer will be stopped with an alarm if the parity check fails. Pulse WS results in writing the lower order 9 bits, i.e., the address x, of the word present on the Write Busses into the S register (the address register), The pulse CLSQ clears the SQ register, and in so doing generates an output pulse which selects the next sequence to be executed. This selection is accomplished by setting to a ONE a subset of cores in the Sequence Generator, where upon they are cleared to ZERO one by one by the TP's. As these cores are cleared to ZERO they generate outputs which are sensed and amplified, forming Control Pulses.

Simultaneously with the selection of the next sequence to be executed, a ONE is placed somewhere in the Shift Register, as shown in the bottom row of Table 1-6. Sequences are not all of the same length; in selecting OP=NOR or OP=TSN a ONE is placed in position 5 of the Shift Register, whereby the first Time Pulse of those sequences is TP5. Notice that all sequences end at TP14, but because of different lengths, begin at different Time Pulses.

After TP14, the initial conditions are: the next instruction: has been selected and its sequence set up. The address part x of

the instruction is in S, and the entire instruction OPx in C. The address L+1 of the next instruction following the one about to be executed is in register Z.

Suppose now that the selected instruction is NOR, where x is the address part already in S. At TP5 S is cleared, thereby switching a selected rope core from ZERO to ONE. At TP6 register C is cleared. The instruction was originally placed in C in case an interrupt occurred, At TP7 the Control Pulse CLE resets the selected rope core to ZERO. If this core was part of Fixed Storage, then the information wired into it is sensed by the Rope sense amplifiers, and the proper Write Busses turned on, If the selected core was part of Erasable, then a transistor amplifier (one per register) generates a current which clears the selected Erasable register, The information being cleared out is likewise used for turning on the appropriate Write Busses. There is no possibility of conflict between the two kinds of storage because only one core in the selection rope will switch at this time. The information corning from storage is written into C and P. At TP8, C is cleared and the word written back into Erasable, if it came from there, and the previous transfer is checked by the pulses CLP and TP, which check parity, The word being cleared out of C is also written into register A, where each Write Buss at ONE drives to ZERO the appropriate core of A, If A had all ONEs In it, then c(A) will be the complement of what was read out of storage. The action of writing into A in this special way results in the desired operation  $c(A) = c(X) \cdot b(A)$ , where b(A) is the "before" contents of A, and c(A) the contents of A after TP8.

The next six time pulses, starting from TP9, are concerned with fetching the next instruction to be executed. Just before this time c(Z) = L + 1 = address of the next instruction. TP9 results in clearing Z, and writing L + 1 into C. At TP10 the address L + 1 is written into address register S, and into the Z register. Since control pulse ZA is present at TP10, the net result of this

pulse time is to cause L+2 to be written into Z, and L+1 into S. After TPIO follows TP11, in which S is cleared, and which results in setting to ONE the core in the rope which corresponds to L+1; the contents of L+1 are the next instruction to be executed, and they are sensed at TP13. This, it will be recalled, is the Time Pulse with which this exposition was started; the cycle of operations has been completed.

The point at which an instruction starts or stops is a matter of somewhat arbitrary definition. In the present case the dividing time is defined by the time at which the next sequence is selected.

The sequences for instructions TSN and AOTSN follow the same pattern as the one for NOR. The sequence for BNZN, the branch instruction, has certain characteristics worth mentioning. As is shown in Table 1-6, there are really three sequences involved in this instruction. The first of these generates the control pulses for TPI and TP2. During these times the contents of A are examined to see if they are identically positive zero or not. Then, depending on the outcome of this examination, one of two further sequences is selected. If  $c(A) \neq +0$ , the next instruction is taken from L+1, where c(Z) = L+1 at the start of the Branch instruction. If  $c(A) \equiv +0$ , the next instruction is taken from x, where x is the address part of BNZN x. Both subsequences generate the same control pulses for TP11, TP12, TP13, and TP14.

There are two additional sequences, shown in Table 1-7, which are not used in normal computer operation. These are "Engineering Sequences" the main purpose of which is to provide some meaningful repetitive activity of various parts of the computer. Sequence El allows the interrogation of any addresss, as specified by switch register (input register) SW1. After interrogation, c(SW2) is written into the selected register. The selected address is displayed in light register 1 (LT1, an output register), and the word read from memory is displayed in LT2.

Addressable

Storage

Erasable

Output

Input

A Register

Fig. 1-1 Organization of the 1A part of 1B from the programer's view point.

|     | F    | (fixed storage)              |

|-----|------|------------------------------|

|     | Е    | ('erasable storage)          |

| (A) | Z    | (adds or subtracts 1)        |

| (A) | A    | (complements)                |

| (A) | S    | (sets memory selection rope) |

| (B) | T2   | (storage for interrupt)      |

|     |      | Write Busses β Sense         |

| (A) | В    | (buffer register)            |

| (A) | SQ   | (instruction decoder)        |

| (A) | C    | (auxiliary buffer register)  |

| (A) | P    | (parity - E bit)             |

| (B) | O.C. | (overflow - 1 bit)           |

| (B) | E.C. | (end-around-carry-1bit)      |

| (B) | Т1   | (storage for interrupt)      |

| (B) | Т3   | (storage for interrupt)      |

|     |      |                              |

Note: (A's refer to register of Mod 1A, and B's to those additional registers necessary to make up Mod 1B)

Fig. 1-2 Detailed structure of Mod 1B

Table 1-1 Mod 1B Order Code

| c(x) are preserved. |

|---------------------|

|                     |

$\overline{c(x)}$  n  $c(A) \rightarrow A...$

10. AOTSN x: (Add ONE to c(A), transfer to storage; normalize A)

$$c(A) \subset 1-x$$

;  $1-A$ .

11. BNZN x: (Branch non-zero to x; normalize A) if

$$c(A) \neq +0$$

, take next instruction from x;  $1 - A$ . if  $c(A) \equiv +0$ , go to next instruction;  $1 - A$ .

#### NOTES:

00. NOR x:

- a. Symbol \( \bigcap \) means the bit by bit AND of the two quantities.

- b. The number representation is ONE's complement; hence it is necessary to distinguish between ÷ 0 and -0.

- c. The instruction word structure is:

Order code, bits S, 10;

Data Address, bits, 9, 8, 7, 6, 5, 4, 3, 2, 1;

Parity, bit 0.

Table 1-2 Special Function Registers

#### SPECIAL FUNCTION REGISTERS

| Octal<br>Address | Name    | Function                 | Bits |

|------------------|---------|--------------------------|------|

| 006 A            | CYCL    | Cycle word left one bit  | ALL  |

| 007 A            | CYCR    | Cycle word right one bit | ALL  |

| 761 B            | CYCLB   | Same as CYCL             | ALL  |

| 762 B            | SHIFT R | Shift Right by one bit   | ALL  |

Table 1-3 Input Registers

#### INPUT REGISTERS

| Octal<br>Address | Name   | Function          | Bits |

|------------------|--------|-------------------|------|

| 000 A            | SW 1   | Switch register 1 | ALL  |

| 001 A            | SW 2   | Tape input        | ALL  |

| 010 A            | SW 3   | Switch register   | ALL  |

| 760 B            | SW 4   | Switch register   | ALL  |

| 765 B            | PRESET | Counter           | ALL  |

| 766 B            | 4PPS   | Counter           | ALL  |

| 767 B            | PAC    | Counter           | ALL  |

Table 1-4 Output Registers

#### **OUTPUT REGISTERS**

| Octal<br>Address | Name              | <u>Function</u>                  | Bits |

|------------------|-------------------|----------------------------------|------|

| 003 A            | LT 1              | Light register                   | ALL  |

| 004 A            | LT 2              | Light register                   | ALL  |

| 005 A            | LT 3              | Light register                   | ALL  |

| 377 A            | STOP              | Stops computer                   | 1    |

| 763 B            | LT 4              |                                  | ALL  |

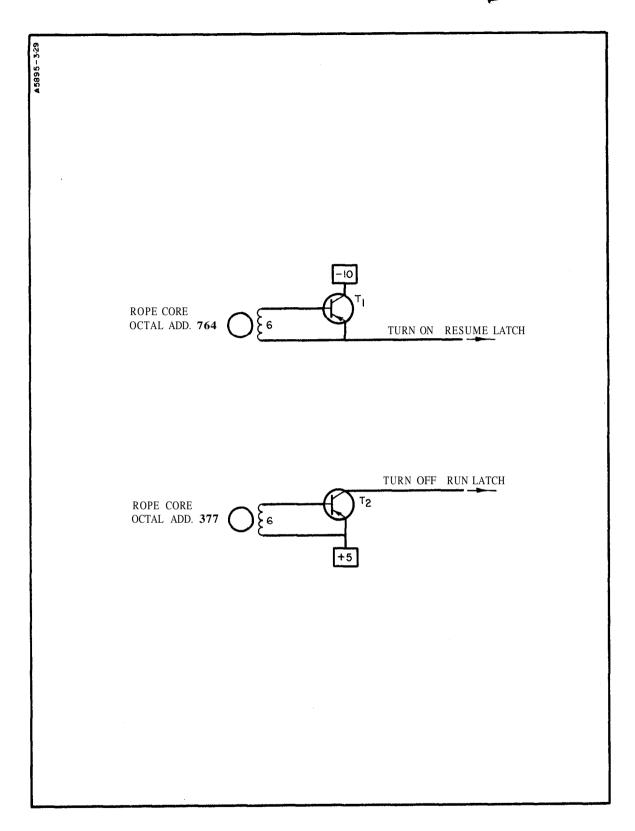

| 764 B            | RESUME            | Note (a)                         | 1    |

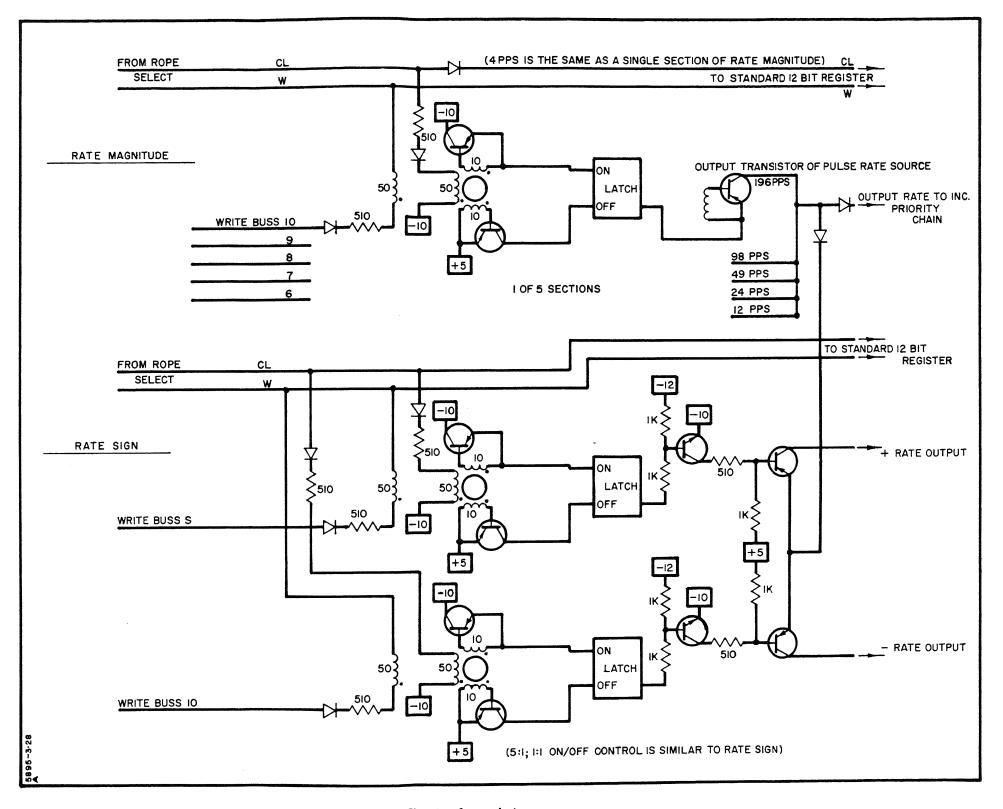

| 774 B            | RATE<br>MAGNITUDE | Sums outputs from rate generator |      |

| 775 B            | 4PPS<br>ON/OFF    |                                  | 1    |

| 776 B            | RATESIGN          |                                  | 2    |

| 777 B            | 5:1/1:1           |                                  | 2    |

|                  |                   |                                  |      |

Note (a) Addressing RESUME selects the Resume sequence, which resumes the interrupted program.

Table 1-5 Mod 1B Storage Assignments

| Octal Address | <u>Function</u>                |

|---------------|--------------------------------|

| 000 A         | IN Switch #1                   |

| 001 A         | IN Switch #2 or Tape Reader IN |

| 002 A         | IN Switch '#3                  |

| 003 A         | OUT Light #1                   |

| 004 A         | OUT Light #2                   |

| 005 A         | OUT Light #3                   |

| 006 A         | Cycle left                     |

| 007 A         | Cycle right                    |

| 010 A         | Normal erasable                |

| 011 A         | Normal erasable                |

| 012 A         | Normal erasable                |

| 013 A         | Normal erasable                |

| 014 A         | Normal erasable                |

| 015 A         | Normal erasable                |

| 016 A         | Normal erasable                |

| 017 A         | Normal erasable                |

| 020 A         | Fixed                          |

| to            |                                |

| 037 A         | Fixed                          |

| 040 A         | Normal erasable                |

| to            |                                |

| 077 A         | Normal erasable                |

Table 1-5 (cont'd)

| Octal Address | <u>Function</u>                                          |

|---------------|----------------------------------------------------------|

| 100 A         | Fixed                                                    |

| to            |                                                          |

| 367 A         | Fixed                                                    |

| 370 A         | No registers (i.e., No sense lines through these cores.) |

| 376 A         | No registers (i.e., No sense lines through these cores.) |

| 377 A         | OUT Normal stop                                          |

| 400 B         | Fixed                                                    |

| 624 B         | Fixed                                                    |

| 625 B         | Not used (fixed)                                         |

| 655 13        | Not used (fixed)                                         |

| 656 B         | Fixed                                                    |

| 726 B         | Fixed                                                    |

| 727 B         | Not used (fixed)                                         |

| 737 B         | Not used (fixed)                                         |

| 740 B         | Normal erasable                                          |

| 741. B        | Normal erasable                                          |

| 742 B         | Normal erasable                                          |

| 743 B         | Normal erasable                                          |

| 744 B         | Normal erasable                                          |

| 745 B         | Normal erasable                                          |

| 746 B         | Normal erasable                                          |

| 747 B         | Normal erasable                                          |

Table 1-5 (cont'd)

| Octal Address | Function                                 |

|---------------|------------------------------------------|

| 750 B         | Normal erasable                          |

| 751 B         | Normal erasable                          |

| 752 B         | Normal erasable                          |

| 753 B         | Normal erasable                          |

| 754 B         | Normal erasable                          |

| ·             |                                          |

| 755 B         | Normal erasable                          |

| 756 B         | Normal erasable                          |

| 757 B         | Normal erasable                          |

| 760 B         | IN Switch #4                             |

| 761 B         | Cycle left                               |

| 762 B         | Shift Right                              |

| 763 B         | OUT Light #4                             |

| 764 B         | OUT Resume                               |

| 765 B         | CTR IN (Preset) Counter                  |

| 766 B         | CTR IN (4 PPS) Counter                   |

| 767 B         | CTR IN (PAC) Counter                     |

| 770 B         | Automatic Interrupt Address<br>Registers |

| 771 B         | Automatic Interrupt Address<br>Registers |

| 772 B         | Automatic Interrupt Address<br>Registers |

| 773 B         | Automatic Interrupt Address<br>Registers |

Table 1-5 (cont'd)

| Octal Address | _ Function_                 |                    |

|---------------|-----------------------------|--------------------|

| 774 B         | OUT Output Latch Bits 6-10  | RATE MAG Control   |

| 775 B         | OUT Output Latch Bits S     | 4PPS ON/OFF Contol |

| 776 B         | OUT Output Latch Bits S, 10 | RATE SIGN Control  |

| 777 B         | OUT Output Latch Bits S, 10 | 5:1/1:I. Control   |

|               |                             | 1                  |

CONTIDENTIAL

Table 1-6 Sequences Involved

| TIME<br>PULSES | NOR                              | TSN                          | AOTSN                        | BNZN                         | INT                          | RES                         | INC+                           | INC -                          |      |

|----------------|----------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|-----------------------------|--------------------------------|--------------------------------|------|

| TP1 $\alpha$   |                                  |                              | CLA, WB, WP                  | CLA, WB, ZT                  |                              |                             |                                |                                | 1 α  |

| TP2 β          |                                  |                              | CLC                          | CLB, Test for<br>ZERO        | CLT1, CLT3,<br>BI            |                             |                                |                                | 2β   |

| TP3 α          |                                  |                              | CLZ, WC                      |                              | CLT2                         |                             |                                |                                | 3α   |

| TP4β           |                                  |                              | CLB, CLP<br>WZ, ZA           |                              | CLB, CLP, TP<br>WE           | CLB, CLP,<br>TP, WE         | CLOC, CLEC                     | CLOC, CLEC                     | 4β   |

| TP5α           |                                  |                              |                              | Zero Non-Zero                |                              |                             |                                |                                | 5α   |

|                | CLS                              | CLA, CLS,<br>WB, WP          | CL <b>Z</b> , WB, WP,<br>CLS | CLS CLZ                      | CLZ, WT1                     | CLZ                         | CLF/E, WB,<br>WP               | CLF/E, WB,<br>WP               |      |

| ΤΡ6 β          | CLC                              | CLC                          |                              | CLC                          | CLC, WT2                     | CLC                         | CLB, WZ, ZA,<br>CLP            | CLB, WZ, ZS,<br>CLP            | 6β   |

| TP7 α          | CLF, WC<br>WP                    | CLE                          | CLE                          | CLE<br>WC, WP                | CLF, WC<br>WP, WB            |                             | CLZ, WB, WP                    | CLZ, WB, WP                    | 7α   |

| ТР8 β          | CLC, CLP, TP,<br>WE, WA          | CLB, CLP, WE                 | CLB, CLP, WE                 | CLC, CLP,<br>TP, WE          | CLB, CLP, TP,<br>WE          | CLT3, WA                    | CLB, CLP,<br>WE, CLEC,<br>CLOC | CLB, CLP,<br>WE, CLEC,<br>CLOC | 8β   |

| ΤΡ9 α          | CLZ, WC                          | CLZ, WC                      | CLZ                          | CLZ, WCCLZ                   | CLA, WT3, CLZ                | CLA, WT3,CLZ                | CLZ                            | CLZ                            | 9α   |

|                |                                  |                              | INC                          | REMENT, if any, (So          | et Core 4 of Shift Re        | egister)                    |                                |                                |      |

| ΤΡ10β          | CLC, WS, WZ,<br>ZA               | CLC, WS, WZ,<br>ZA           | CLC, WS, WZ,<br>ZA           | CLC, WS CLC, WZ<br>WZ, ZA ZA | CLC, WS, WZ,<br>ZA           | CLT1, WZ,<br>W1A            |                                |                                | 10β  |

| TP11α          | CLS                              | CLS                          | CLS                          | CLS                          | CLS                          |                             |                                |                                | 11α  |

| ΤΡ12β          |                                  | W1A                          | W1A                          | W1A                          | W1A                          | CLT3, WA                    |                                |                                | 12 β |

| TP 13α         | CLE, CLT2,<br>WB, WC, WP,<br>WSQ | SAME                         | SAME                         | SAME                         | CLE, WB,<br>WC, WP           | SAME                        |                                |                                | 13 α |

|                |                                  |                              | INT                          | ERRUPT, if any, (Se          | t Core 2 of Shift Re         | gister)                     |                                |                                |      |

| ΤΡ14β          | CLB, CLP, TP,<br>WS, WE, CLSQ    | SAME                         | SAME                         | SAME                         | SAME                         | SAME                        |                                |                                | 14β  |

| TO<br>Enter:   | Set ShiftRegister<br>Core 5      | Set Shift Register<br>Core 5 | Set Shift Register<br>Core 1 | Set Shift Register<br>Core 1 | Set Shift Register<br>Core 2 | Set Shift Registe<br>Core 4 | Set Shift Registe<br>Core 4    | r SetShift Register<br>Core 4  |      |

Table 1-7 Test Sequences

|             | E <sub>1</sub>                             | $^{ m E}_2$                                |

|-------------|--------------------------------------------|--------------------------------------------|

| 1 α         | CL LT 1, LT2                               | CL LT1, LT2                                |

| <b>2</b> β  | w sw1, sw2                                 | CLC, WZ, ZA                                |

| 3cY         | CL SW1, WB                                 | CLZ, wc, WB                                |

| 4 P         | CLB, WS, WLT1                              | CLB, WS, WLT1                              |

| 5cY         | CLS, CLSW2, WC                             | CLS                                        |

| 6 β         | -                                          | -                                          |

| 7 α         | CLF/E, WB, WP                              | CLF/E, WB, WP                              |

| 8 β         | CLC, WE                                    | -                                          |

| 9 α         | -                                          | -                                          |

| 10 P        | CLB, WE, CLP, TP, WLT2                     | CLB, WE, CLP, TP<br>WLT2                   |

| 11 <b>a</b> | -                                          | -                                          |

| 12 P        | Test Recycle. Set Shift<br>Register Core 1 | Test Recycle. Set Shift<br>Register Core 1 |

Table 1-8 List of Control Pulses

(Those Control Pulses not mentioned previously have a note number next to their names.)

BI (Note 1)

CLZ

CLA

SI (Note 4)

CLB

Test for ZERO (Note 5)

CLC

WLT1 (Note 2)

**CLEC**

WLT2 (Note 2)

CLE

CL LT1, LT2 (Note 2)

WSW1 (Note 3)

**CLOC**

WSW1, SW2 (Note 2)

CLP

CLS

CLSW1 (Note 3)

CLSW2 (Note 3)

CLT1

CLT2

CLT3

- Note 1 BI is used to inhi'bit further interrupts until the RESUME sequence is actuated.

- Note 2. LT1 and LT2 are two output registers (octal addresses 003 and 004) with lights attached to the output latches. The single control pulse CLLT1, LT2 clears both these registers, turing off all lights. WLT1 allows whatever is on the Write Busses to be written into LT1, and similarly for LT2.

- Note 3. SW1 and SW2 are two input registers (octal addresser; 000 and 001), with toggle switch connected to each core. The single control pulse WSW1, SW2 allows the information

## Table 1-8 (continued)

| Medica o America de La Companyamento del Companyamento de la Companyamento de la Companyamento del Companyamento de la Company | of the toggle switches to be written into SW1 and SW2. CLSW1 and CLSW2 are control pulses for clearing these registers.                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SI inhibits the flow of setting and inhibiting currents for the core rope, so that register S may be cleared without altering the state of the rope. |

| Note 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Test for Zero and ZT. These control pulses are used for determining whether c(A) = 0 or not.                                                         |

Table 1-9 Mod 1B Tray Contents

| Tray 1                                             | Tray 2                     | Tray 3                             | Tray 4                      | Tray 5                        | Tray 6                                              | Tray 7                   | Tray 8               |

|----------------------------------------------------|----------------------------|------------------------------------|-----------------------------|-------------------------------|-----------------------------------------------------|--------------------------|----------------------|

| Clock                                              | Main Sequence<br>Generator | β to α<br>Amplifiers               | α to β<br>Amplifiers        | 1A<br>Erasable<br>Registers   | 1B Erasable Registers (Control Registers, Counters) | 1A Fixed<br>Storage      | Interrupt<br>Circuit |

| Main Shift<br>Register<br>Time Pulse<br>Amplifiers |                            | Sequence<br>Selection<br>Logic     | A Register<br>Z<br>T2<br>DA | 1A<br>Switch<br>Registers (3) | Rate Generator                                      | 1B Fixed<br>Storage      | Encoder<br>Logic     |

| Increment<br>Circuit                               | Test Sequence<br>Generator | B Register OC EC C T1 T3 DB Parity | Parity<br>Timing<br>Circuit | 1A<br>Light<br>Registers (3)  | 1B Light Register                                   | Rope Sense<br>Amplifiers |                      |

|                                                    |                            | Latches                            |                             | Memory<br>Selection<br>Rope   | 1B Switch<br>Register                               | S Register               |                      |

| Engineering<br>Sequence<br>Electronics             |                            |                                    |                             |                               | Memory Selection<br>Rope                            |                          | <u>,</u>             |

| Panel Mode<br>Electronics                          |                            |                                    |                             |                               | 1B Erasable<br>Amplifiers                           |                          |                      |

# CHAPTER 2 MOD 1B CONTROL OF STEPPER-MOTOR by A.I. Green

CONTIDENTIAL

CONTIDENTIAL

#### CHAPTER 2

#### MOD 1B CONTROL OF STEPPER-MOTOR

#### 2. 1 General Discussion of Systems Application of Mod 1B

The systems application of Mod 1B computer was devised to demonstrate the ability to solve several problems simultaneously by time-sharing the central computing equipment of a general purpose machine rather than by permanently committing specific physical sections of a special purpose computer to each problem. The computer was given the task of controlling a rotating device (a common requirement in space vehicles) while, at the same time, performing the details of a main program, such as the solution of guidance equations.

The rotating device, in this case, was a commercially available stepper-motor, a device which rotates a fixed, finite number of degrees for each input pulse, The choice was based upon considerations of availability, familiarity, and the existence of already proven input and output circuitry. Experiments with a continuously rotating, higher inertia motor are planned for a later stage in development.

Mod 1B has several versatile and efficient facilities available which make it particularly well suited for performing several different tasks simultaneously. There is an "Automatic Increment" facility which can be used to accumulate input data increments without interfering with the main problem the computer is solving. This equipment can also be used internally whenever counting techniques are required,

An important capability of Mod 1B is that of mode changing at the program level, This "Automatic Interrupt" accomplishes a transfer of control to a specified sub-routine upon the occur-

rence of a pre-specified signal, When this Interrupt Sub-routine is completed, control is returned to the point in the main program at which the interruption took place and the solution of the main program continues, These Automatic Interrupt capabilities furnish the ability to solve several different classes of problems at essentially the same time, without consuming large amounts of time in the usual scanning procedures, Different problem modes may be assigned a predetermined priority of solution; thus, less pressing solutions may be deferred until the computer is relatively idle and can easily perform them.

The output equipment required for a task such as controlling a stepper-motor consists of a pulse rate source and several gating switches for applying the required rates to the proper equipment. These gating switches are operated by regular erasable registers.

In order to furnish the Increment and Interrupt capabilities, it was necessary to make certain modifications and additions to the Sequence Generator. An INTERRUPT and a RESUME Sequence are provided, The INTERRUPT Sequence stores the location of the instruction being performed when the Interrupt occurred; and performs the steps necessary to transfer control to the desired Interrupt Sub-routine. The RESUME Sequence uses the information stored during the INTERRUPT Sequence to return control to the point in the main program where the interruption occurred.

In order to perform the increment function, an INCREMENT Sequence is included in the Sequence Generator. This sequence selects the contents of a predetermined erasable register, adds one to it (or subtracts one from it), and returns the new result to that same erasable register.

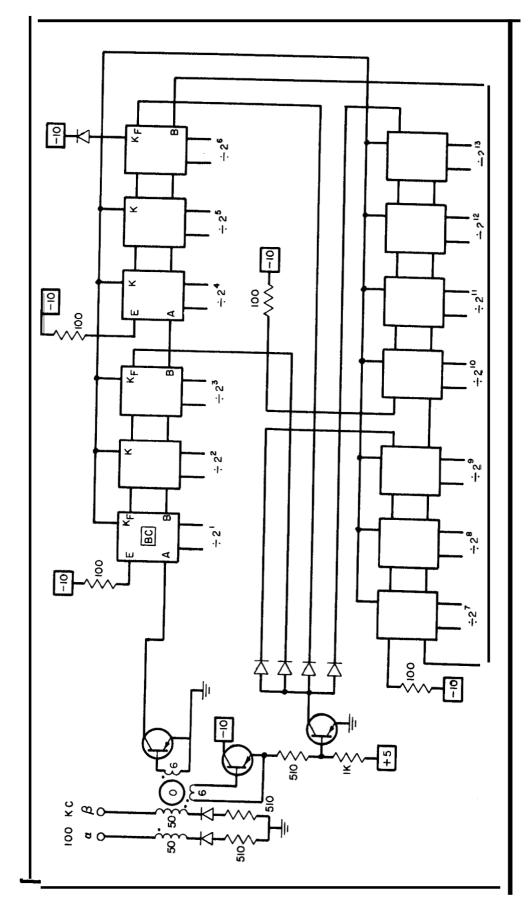

#### 2.2 The Automatic Increment Circuit

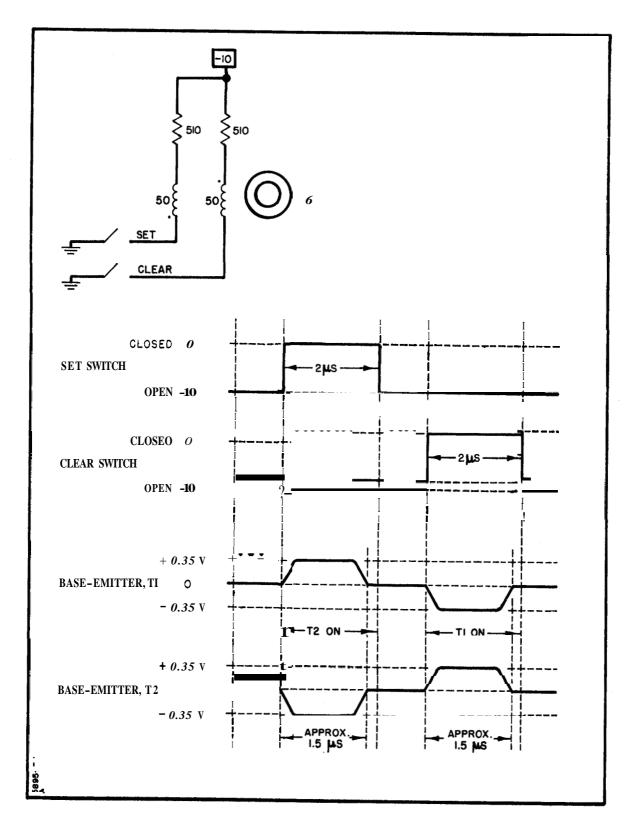

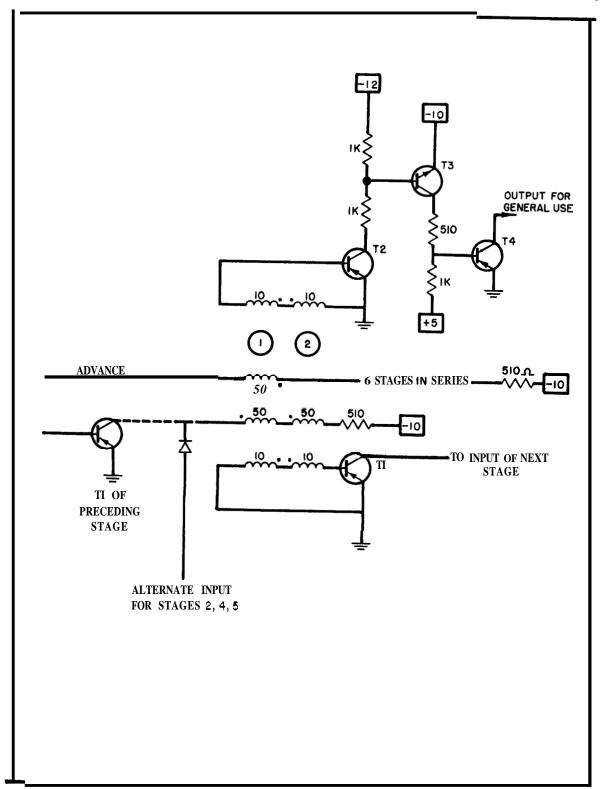

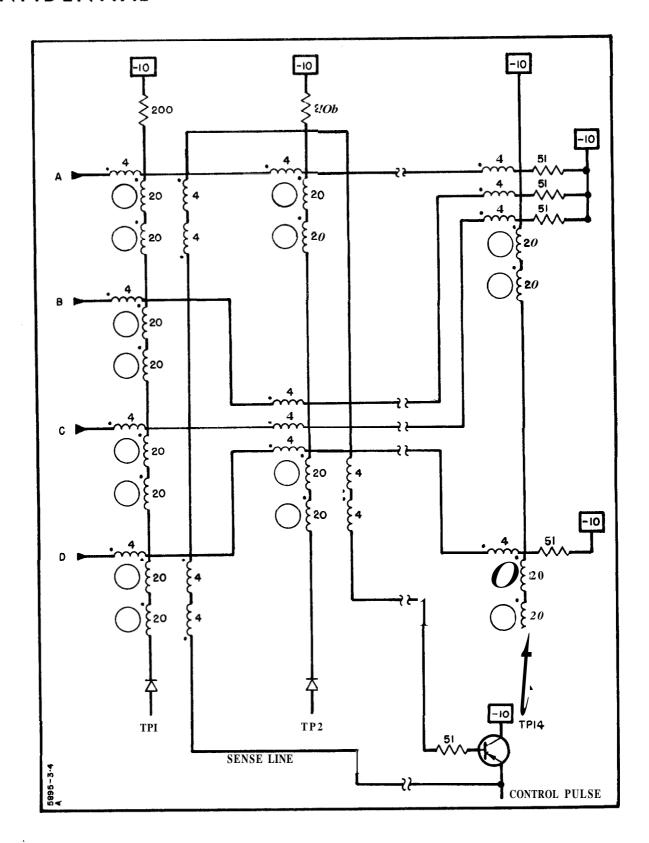

The heart of the Automatic Increment mechanism is the Priority Circuit. See Fig, 2-1. This is a chain of cores and transistors inserted between two successive cores of the Shift

Register in the Sequence Generator, In our case, it is placed between cores 9 and 10. (Core 9 furnishes Time Pulse 9; core 10, Time Pulse 10). If no cores in the Priority Chain are set to ONE, the Priority Chain acts like a short-circuit, and Time Pulse 10 simply follows Time Pulse 9, as if there were no Priority Chain present, However, if any of the Priority Chain cores is set to ONE, the advance current is diverted away from core 10 and Time Pulse P0 does not follow Time Pulse 9. Instead we perform an INCREMENT Sequence between Time Pulses 9 and 10 of the instruction that was being performed. In particular, the advance current is diverted in such a way that it selects the INCREMENT Sequence; sets to ONE the fourth core of the Sequence Generator shift register; sets to ONE the clear core of the memory selection rope corresponding to a predetermined counter, (The Priority Chain core is also cleared to ZERO.) Thus a Time Pulse 4 follows a Time Pulse 9, and the INCREMENT Sequence is performed on Time Pulses 4 through 9. If there are no further Increments to be performed, the Sequence Generator next performs Time Pulse 10 of the original instruction, and continues until the instruction is completed, The counter is merely an erasable storage register the contents of which will be incremented (or decremented) by one whenever its particular core in the Increment Circuit Priority Chain is set to ONE.

The physical sequence of the cores in the Priority Chain determines the order in which the Increments are processed. The Priority Chain core closest to Shift Register Core 10 has the lowest priority; it will be processed only after all higher priority cores have been processed. By processing a core in the Increment Priority Chain, we mean incrementing (or decrementing) by one the counter register which is associated with that core in the Priority Chain, Notice that a Priority Chain core can not be set to ONE at Time Pulse 9, when the advance current passes through the Increment Priority Chain. Also, that the order in

which the Priority Chain cores were set to ONE does not determine the order in which they are processed. That is determined by the priority position of the core. When counters are used as internal timing devices, the timing pulse that is to be counted down is applied to the input set line of the Increment Priority core.

The counter registers have associated with them two special bits in addition to the regular 12 bits. These are called EC and OC and are used to indicate the fact that the last time the given counter was incremented, either an end-around carry or an overflow occurred. Very often these EC or OC signals are used to initiate an Automatic Interrupt, or change of program mode.

Since an Automatic Increment may be performed during any instruction, it is necessary to arrange the sequences for all instructions so that at the Time Pulse when an Increment may occur, all sequences leave certain pertinent central equipment in the same state. In particular, the Z register must be cleared to ZERO since it will be used to perform the increment; the B register must be cleared to ZERO since it will be used in transferring the counter contents to the Z register; both the clear and write cores of the memory selection rope must be cleared to ZERO since the counter register contents will be fetched and later returned to memory.

The INCREMENT Sequence is selected upon the action of the Increment Priority Chain. It is not decoded from the highest order two bits of an instruction word, as are normal programable sequences. It fetches the contents of the counter associated with the Priority Chain core which set up the INCREMENT Sequence and reads this into the Z register, which performs the addition (or subtraction) of one and sets to ONE either the EC core or the OC core, if appropriate. It then reads the new result back into the counter register along with the EC and OC bits. The In-

crement Priority Chain cores for negative increments select a Negative Increment Sequence, which differs from the Positive Increment Sequence only in that it causes the Z register to subtract one from the number read into it. In this case, the EC records the fact that an end-around borrow has occurred; the OC, that an underflow has occurred.

#### 2. 3 The Automatic Interrupt Circuit

Many of the ideas developed in the section on the Automatic Increment Circuit are pertinent to the Automatic Interrupt Circuit. Once again, a Priority Chain is inserted between two cores of the shift register in the Sequence Generator. The performance of the Interrupt Circuit is slightly more complex than the Increment,

The Interrupt Priority Chain is inserted between cores 13 and 14 of the Sequence Generator Shift Register. See Fig. 2-2. If no cores in the Priority Chain are set to ONE, Time Pulse 14 follows Time Pulse 13. However, if any of the Priority Chain cores are set to ONE, the advance current is diverted away from core 14 in such a way that it selects the INTERRUPT Sequence; sets to ONE the first core of the Sequence Generator shift register; sets to ONE the clear core of the memory selection rope corresponding to a predetermined Interrupt Address Register. (The Priority Chain core is also cleared to ZERO,) Thus a Time Pulse 1 follows a Time Pulse 13, and the INTERRUPT Sequence is performed on Time Pulses 1 through 14. An interlock is also activated so that no further Interrupts are processed until a RESUME indication is received. (This is described below,) The Interrupt Address Register is simply an erasable register the contents of which will be interpreted as the location of the first instruction of a sub-routine which we wish to enter when the Interrupt is processed.

The Priority Chain cores cannot be set to ONE at Time Pulse 13, when the advance current passes through the Interrupt Priority Chain. The order in which the Interrupts are processed is determined by the priority position of the cores, not by the order

in which they are set.