# OF TECHNOLOGY MASSACHUSETTS INSTITUTE

## GUIDANCE, NAVIGATION

AND CONTROL

R-700 MIT's ROLE IN PROJECT APOLLO FINAL REPORT ON CONTRACTS NAS 9-153 AND NAS 9-4065

VOLUME III

COMPUTER SUBSYSTEM

ELDON C. HALL

AUGUST 1972

### CHARLES STARK DRAPER LABORATORY

CAMBRIDGE MASSACHUSETTS 02139

# 500 T 0

### 0

### **GUIDANCE, NAVIGATION** AND CONTROL

AND NAVIGATION PROGRAM APOLLO GUIDANCE

Date

di Approved R. R. RAGAN, DEPUTY DIRECTOR THE CHARLES STARK DRAPER LABORATORY

Date 25 72

R-700 MIT's ROLE IN PROJECT APOLLO FINAL REPORT ON CONTRACTS NAS 9-153 AND NAS 9-4065

VOLUME III

COMPUTER SUBSYSTEM by ELDON C. HALL

AUGUST 1972

### **CHARLES STARK DRAPER** LABORATORY CAMBRIDGE, MASSACHUSETTS, 02139

### ACKNOWLEDGMENTS

This report was prepared under DSR Project 55-23890, sponsored by the Manned Spacecraft Center of the National Aeronautics and Space Administration through Contract NAS9-4065.

The author expresses appreciation to many individuals within Draper Laboratory who contributed to the following sections of the report. In particular:

| A. Hopkins              | Section 1, 2 |

|-------------------------|--------------|

| A. Green, R. Filene     | Section 4    |

| A. Harano               | Section 5    |

| D. Bowler               | Section 6    |

| D. Hanley, J. Partridge | Section 7.   |

The publication of this document does not constitute approval by the National Aeronautics and Space Administration of the findings or conclusions contained herein. It is published for the exchange and stimulation of ideas.

> © Copyright by the Massachusetts Institute of Technology Published by the Charles Stark Draper Laboratory of the Massachusetts Institute of Technology Printed in Cambridge, Massachusetts, U.S.A., 1972

### FOREWORD

The title of these volumes, "MIT's Role in Project Apollo", provides but a modest hint of the enormous range of accomplishments by the staff of this Laboratory on behalf of the Apollo program. Man's rush into spaceflight during the 1960s demanded fertile imagination, bold pragmatism, and creative extensions of existing technologies in a myriad of fields. The achievements in guidance and control for space navigation, however, are second to none for their critical importance in the success of this nation's manned lunar-landing program, for while powerful space vehicles and rockets provide the environment and thrust necessary for space flight, they are intrinsically incapable of controlling or guiding themselves on a mission as complicated and sophisticated as Apollo. The great achievement of this Laboratory was to supply the design for the primary hardware and software necessary to solve the Apollo guidance, navigation and control problem. It is to the credit of the entire team that this hardware and software have performed so dependably throughout the Apollo program.

The quantum leap in technology nurtured by the Apollo program has been and should continue to be of immensely significant benefit to this country-socially, economically and in terms of its national esteem. It is the responsibility of all those who contributed to the proud achievements of Apollo to convince their countrymen of the directions this nation ought to follow in implementing these newly gained-and hard fought for-advances.

> C. Stark Draper, President Charles Stark Draper Laboratory

### R-700

### MIT'S ROLE IN PROJECT APOLLO

Final Report on Contracts NAS9-153 and NAS9-4065

### VOLUME III

### COMPUTER SUBSYSTEM

### ABSTRACT

The Apollo guidance computer (AGC) is a real-time digital-control computer whose conception and development took place in the early part of 1960. The computer may be classified as a parallel, general-purpose or whole number binary computer. This class of computer is representative of most of the ground-based digital computers in existence in the late 1950s, when the precursers of the AGC were being designed. However, at that time few computers of this class had been designed for the aerospace environment, and those few embodied substantial compromises in performance for the sake of conserving space, weight, and power. The design of the AGC capitalized on advancements in digital computer technology in order to provide significant improvements in computational performance and still conserve space, weight and power.

The AGC is the control and processing center of the Apollo Guidance, Navigation and Control system. It processes data and issues discrete output and control pulses to the guidance system and other spacecraft systems. An operational Apollo spacecraft contains two guidance computers and three DSKYs (keyboard and display unit for operator interface), with one computer and two DSKYs in the command module, and one of each in the lunar module. The computers are electrically identical, but differ in the use of computer software and interface control functions. As a control computer, some of the major functions are: alignment of the inertial measurement unit, processing of radar data, management of astronaut display and controls and generation of commands for spacecraft engine control. As a general purpose computer, the AGC solves the guidance and navigation equations required for the lunar mission.

The operational experience<sup>\*</sup> in the Apollo guidance systems includes 20 computers which flew missions and another 25 flight type computers which are still in various phases of prelaunch activity including storage, system checkout, prelaunch spacecraft checkout, etc. These computers were manufactured and maintained under very strict quality control procedures with requirements for reporting and analyzing all indications of failure. Probably no other computer or electronic equipment with equivalent complexity has been as well monitored and documented. Since it has demonstrated a unique reliability history, it is important to record the technique and methods which have contributed to this history.

by Eldon C. Hall August 1972

The operational experience includes missions through Apollo 15 which flew in August of 1971. Three Bl I and one Bl II computers flew in unmanned missions. Sixteen Bl II computers flew manned missions.

### CONTENTS

| Section         |           |       |       |       |      |      |      |      |      |     |    |    |     |    |     |    |     |   |    |    | Page |

|-----------------|-----------|-------|-------|-------|------|------|------|------|------|-----|----|----|-----|----|-----|----|-----|---|----|----|------|

| Acknowledgm     | ents      |       |       |       |      |      |      |      |      |     |    |    |     |    |     |    |     |   |    |    | ii   |

| Foreword .      |           |       |       |       |      |      |      |      |      |     |    |    |     |    |     |    |     |   |    |    | iii  |

| Abstract        |           |       |       |       |      |      |      |      |      |     |    |    |     |    |     |    |     |   |    |    | v    |

| List of Illustr | ations .  |       |       |       |      |      |      |      |      |     |    |    |     |    |     |    |     |   |    |    | xv   |

|                 |           |       |       |       |      |      |      |      |      |     |    |    |     |    |     |    |     |   |    |    |      |

| Preface         | • • • •   | • •   | • •   | • •   | •    | • •  | •    | •    | • •  | •   | •  | ł  | •   | •  | •   | •  | •   |   | •  | •  | 1    |

| 1.0 SUBSY       | STEM D    | EVEI  | LOP   | MEI   | T    |      |      |      |      |     |    |    |     |    | Ļ   |    |     |   |    |    | 3    |

| 1.1             | Evolutio  |       |       |       |      |      |      |      |      |     |    |    |     |    |     |    |     |   |    |    | 3    |

| 1.2             | Initial I |       |       |       |      |      |      |      |      |     |    |    |     |    |     |    |     |   |    |    | 15   |

| 1.3             | Expand    |       |       |       |      |      |      |      |      |     |    |    |     |    |     |    |     |   |    |    | 19   |

|                 | 1.3.1     |       | nory  |       |      |      |      |      |      |     |    |    |     |    |     |    |     |   |    |    | 19   |

|                 | 1.3.2     | Imp   | lem   | enta  | tior | n M  | eeti | ings | 3 -  | 19  | 64 |    |     |    |     |    |     |   |    |    | 20   |

|                 | 1.3.3     | Wei   | ght   | Savi  | ngs  | (15  | 962  | to   | 196  | (5) |    |    |     |    |     |    |     |   |    |    | 20   |

|                 | 1.3.4     | Ele   | ctro  | mag   | net  | ic I | nter | rfei | ren  | ce  | Sp | ec | ifi | ca | tic | ns | - 1 | 1 | 96 | 3. | 21   |

|                 | 1.3.5     | Fir   | e Pr  | oofi  | ng   | - 19 | 967  |      |      |     |    |    |     | ÷  |     |    |     |   |    |    | 21   |

| 2.0 COMP        | UTER SY   | TSTE  | M D   | ESC   | RIF  | TIC  | ON   |      |      |     |    |    |     |    |     |    |     |   |    |    | 23   |

| 2.1             | Introdu   | ction |       |       |      |      |      |      |      |     |    |    |     |    |     |    |     |   |    |    | 23   |

| 2.2             | General   | Fun   | ction | nal ] | Des  | criț | otio | n    |      |     |    |    |     |    |     |    |     |   |    |    | 29   |

|                 | 2.2.1     | Con   | nput  | er .  |      |      |      |      |      |     |    |    |     |    |     |    |     |   |    |    | 29   |

|                 | 2.2.2     | Dis   | play  | and   | Ke   | ybo  | ard  | ۱.   |      |     |    |    |     |    |     |    |     |   |    |    | 29   |

| 2.3             | Subsyst   | em C  | hara  | acte  | rist | ic . |      |      |      |     |    |    |     |    |     |    |     |   |    |    | 32   |

|                 | 2.3.1     | Wor   | rd L  | engt  | h.   |      |      |      |      |     |    |    |     |    |     |    |     |   |    |    | 32   |

|                 | 2.3.2     | Nur   | nber  | Re    | pre  | sent | tati | on   |      |     |    |    |     |    |     |    |     |   |    |    | 35   |

|                 | 2.3.3     | Mul   | tiple | e - 1 | Pre  | cisi | on   | Ari  | ithr | net | ic |    |     |    |     |    |     |   |    |    | 37   |

|                 | 2.3.4     | Inst  | ruct  | ion   | Set  |      |      |      |      |     |    |    |     |    |     |    |     |   |    |    | 38   |

|                 | 2.3.5     | Tin   | ning  | and   | Pr   | iori | ty ( | Con  | tro  | 1.  |    |    |     |    |     |    |     |   |    |    | 46   |

|                 | 2.3.6     | Mer   | nory  | 7     |      |      |      |      |      |     |    |    |     |    |     |    |     |   |    |    | 46   |

| Secti | on   | <u>P</u>                                | age  |

|-------|------|-----------------------------------------|------|

|       |      | 2.3.7 Input/Output                      | 47   |

|       |      | 2.3.8 Standby Operation                 | 48   |

|       |      | 2.3.9 DSKY Characteristics              | 48   |

|       | 2.4  | Computer Mechanical Description         | 51   |

|       | 2.5  | DSKY Mechanical Description             | 53   |

| 3.0   | COME | PUTER DESIGN DESCRIPTION                | 55   |

|       | 3.1  | Introduction                            | 55   |

|       | 3.2  | Logic Design                            | 61   |

|       |      | 3.2.1 Logic Circuit Element             | 61   |

|       |      | 3.2.2 Logic Timing and Sequencing       | 63 . |

|       |      | 3.2.3 Central Processor                 | 67   |

|       |      | 3.2.4 Address and Instruction Decoding  | 71   |

|       |      | 3.2.5 Interrupt Structure               | 71   |

|       |      | 3.2.5.1 Counter Interrupts              | 77   |

|       |      | 3.2.5.2 Program Interrupts              | 80   |

|       | 3.3  | Oscillator Circuit                      | 82   |

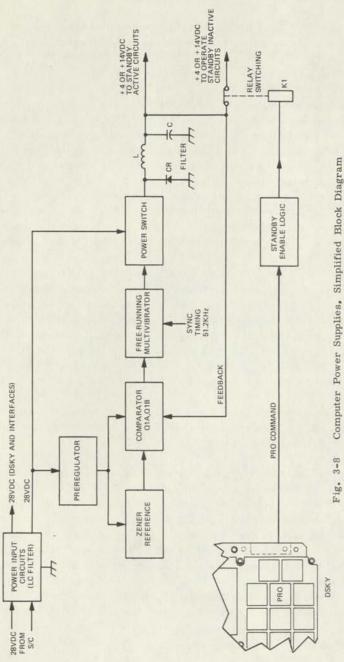

|       | 3.4  | Power Supplies                          | 83   |

|       | 3.5  | Memory Circuits                         | 85   |

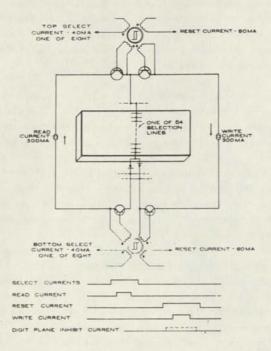

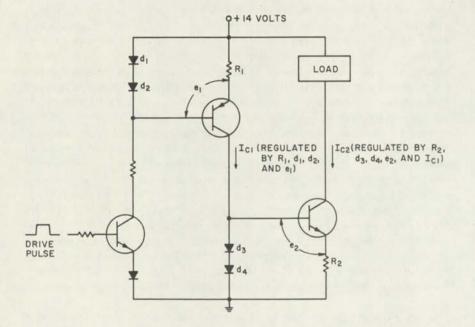

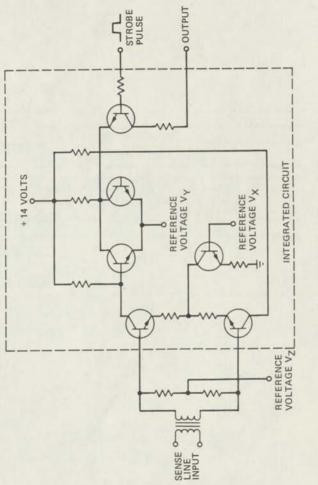

|       |      | 3.5.1 Erasable Memory                   | 87   |

|       |      | 3.5.2 Fixed Memory                      | 91   |

|       | 3.6  | Alarms and Fault Detection              | 93   |

|       | 3.7  | Interface Methods                       | 97   |

|       |      | 3.7.1 Circuits                          | 101  |

|       |      | 3.7.2 Data Format Conversion            | 101  |

|       |      | 3.7.3 Interface Example                 | 103  |

|       | 3.8  | DSKY Description                        | 107  |

|       | 3.9  | Computer Mechanical Description         | 115  |

|       |      | 3.9.1 Detailed Description              | 117  |

|       |      | 3.9.1.1 Tray A Wired Assembly           | 117  |

|       |      | 3.9.1.2 Tray B Wired Assembly           | 121  |

|       |      | 3.9.1.3 Interconnection Header Assembly | 123  |

|       |      | 3.9.1.4 Mid-Spacer and Tray Covers      | 123  |

|       |      | 3.9.1.5 Module Construction Features    | 123  |

|       |      | 3.9.1.6 Assembly Features               | 125  |

|       |      | 3.9.1.7 Thermal Design                  | 130  |

| Section |                       |                                                     | Page  |

|---------|-----------------------|-----------------------------------------------------|-------|

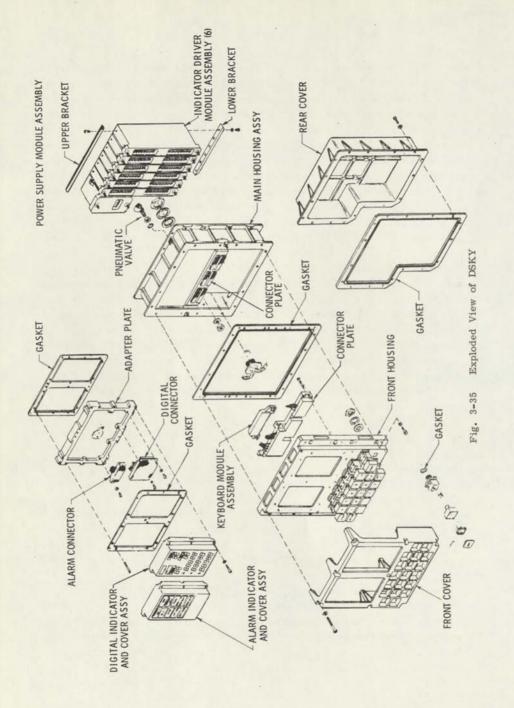

| 3.      | 10 Displ              | ay and Keyboard Unit (DSKY) Mechanical Description. | • 131 |

|         | 3.10.                 | 1 Detailed Description                              | • 133 |

|         |                       | 3.10.1.1 Front Housing Assembly                     | • 133 |

|         |                       | 3.10.1.2 Main Housing Assembly                      | • 136 |

|         |                       | 3.10.1.3 Alarm Indicator and Cover Assembly .       | • 140 |

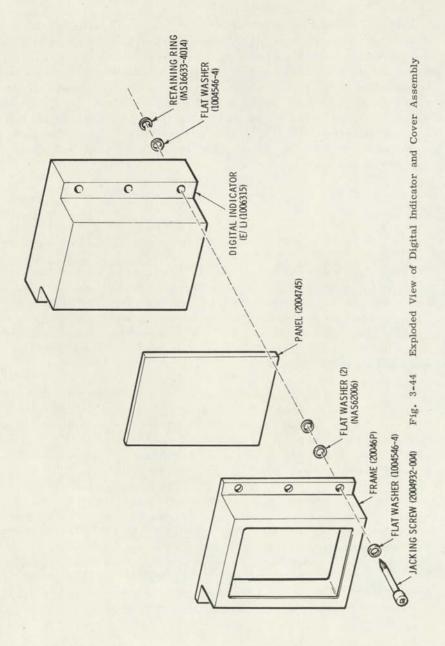

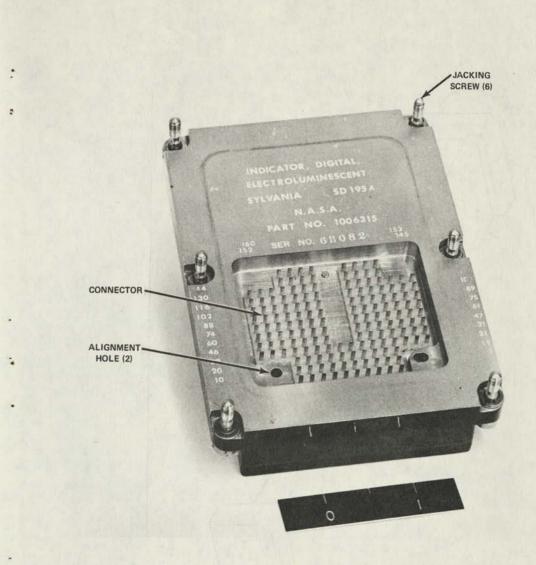

|         |                       | 3.10.1.4 Digital Indicator and Cover Assembly .     | • 145 |

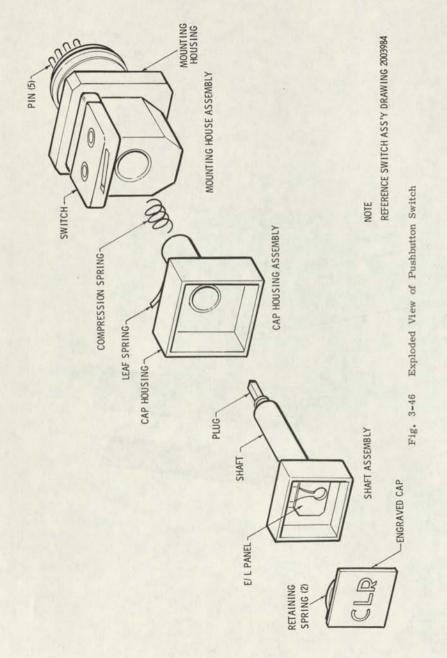

|         |                       | 3.10.1.5 Pushbutton Switch                          | • 149 |

| 4.0 C   | OMPUTER               | SOFTWARE                                            | • 151 |

| 4.      |                       | duction                                             |       |

| 4.      |                       | y Programs                                          |       |

|         | 4.2.1                 |                                                     |       |

|         | 4.2.2                 |                                                     |       |

|         | 4.2.3                 | 8 Waitlist                                          |       |

| 4.      | 3 Displ               | ay and Keyboard                                     |       |

| 4.      |                       | lopment of Computer Self-Check Program              |       |

|         | 4.4.1                 | Block I Versions                                    | • 159 |

|         |                       | 4.4.1.1 Eclipse                                     | . 159 |

|         |                       | 4.4.1.2 Sunrise                                     | • 159 |

|         |                       | 4.4.1.3 Final Block I Version                       | • 162 |

|         | 4.4.2                 | SELFCHK in Block II                                 | • 163 |

| 4.      | 5 Facto               | ory Test Ropes                                      | . 163 |

| 4.      | 6 Fixed               | Memory Fabrication                                  | • 165 |

|         | 4.6.1                 | Program Release                                     | . 165 |

|         | 4.6.2                 | Module Data Verification                            | • 165 |

| 5.0 GI  | ROUND SU              | PPORT EQUIPMENT                                     | . 169 |

| 5.      |                       | duction                                             | 17.55 |

| 5.      | 2 Devel               | lopment of GSE                                      |       |

|         | 5.2.1                 |                                                     |       |

|         | 5.2.2                 |                                                     | • 171 |

|         | 5.2.3                 |                                                     |       |

|         | 5.2.4                 |                                                     |       |

|         | 5.2.5                 |                                                     |       |

| 5.      | and the second second | opment of Software Checkout Aids                    |       |

|         | 5.3.1                 |                                                     |       |

|         |                       | 5.3.1.1 AGC Monitor                                 |       |

| Sectio | n     |          |            |                  | 1                                                     | Page |

|--------|-------|----------|------------|------------------|-------------------------------------------------------|------|

|        |       |          | 5.3.1.2    | Portafam .       |                                                       | 175  |

|        |       | 5.3.2    | Interface  | Simulators .     |                                                       | 176  |

|        |       |          | 5.3.2.1    | Interface Te     | est Console (ITC)                                     | 176  |

|        |       |          | 5.3.2.2    | Uplink-Down      | link Exercisers                                       | 177  |

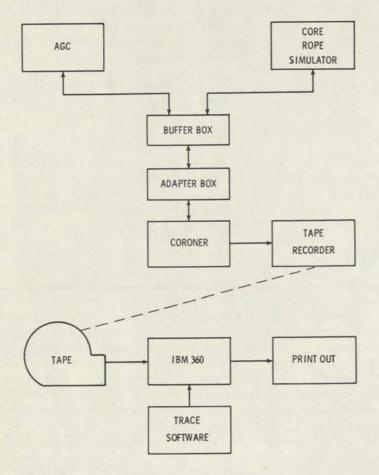

|        |       | 5.3.3    | Trace Sy   | stem             |                                                       | 177  |

|        |       |          | 5.3.3.1    | Coroner Cha      | aracteristics                                         | 177  |

|        |       |          | 5.3.3.2    | Trace Analy      | tical Software                                        | 179  |

| 6.0    | SYSTI | EMS INTE | GRATION    |                  |                                                       | 181  |

|        | 6.1   | Introdue | ction      |                  |                                                       | 181  |

|        | 6.2   | Develop  | ment and s | Specification of | of Interface                                          | 182  |

|        |       | 6.2.1    | Circuit T  | ypes             |                                                       | 185  |

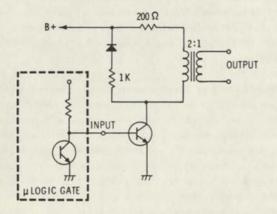

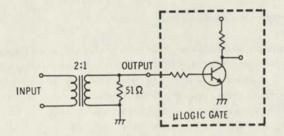

|        |       |          | 6.2.1.1    | Transforme       | r - Coupled Interface Circuits.                       | 187  |

|        |       |          |            | 6.2.1.1.1        | Transformer - Coupled ·<br>Output Circuit (X Circuit) | 187  |

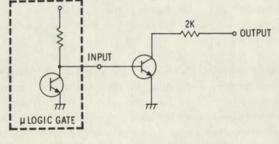

|        |       |          |            | 6.2.1.1.2        | Transformer - Coupled<br>Input Circuit (Y Circuit)    | 189  |

|        |       |          | 6.2.1.2    | Direct Coup      | led Interface Circuits                                | 189  |

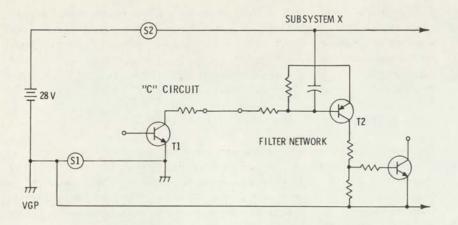

|        |       |          |            | 6.2.1.2.1        | DC Output Circuit (C Circuit)                         | 189  |

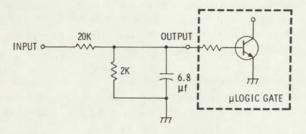

|        |       |          |            | 6.2.1.2.2        | DC Input Circuit (D Circuit).                         | 191  |

|        |       |          | 6.2.1.3    | Special Circ     | uits                                                  | 193  |

|        |       |          |            | 6.2.1.3.1        | Hand Controller Interface                             | 193  |

|        |       |          |            | 6.2.1.3.2        | DC Power Interface                                    | 195  |

|        |       | 6.2.2    | Interface  | Control Docu     | iments (ICD's)                                        | 196  |

|        |       | 6.2.3    | Summary    |                  |                                                       | 196  |

|        | 6.3   | Electro  | magnetic I | nterference.     |                                                       | 197  |

|        |       | 6.3.1    | EMI Phil   | osophy           |                                                       | 197  |

|        |       | 6.3.2    | Milestone  | es               |                                                       | 198  |

|        |       | 6.3.3    | Specificat | tion Problem     |                                                       | 200  |

|        |       |          | 6.3.3.1    | Susceptibilit    | y Testing                                             | 200  |

|        |       |          |            | 6.3.3.1.1        | Power Line Transient<br>Susceptibility                | 200  |

|        |       |          |            | 6.3.3.1.2        | Conducted Audio Suscepti-<br>bility                   | 201  |

|        |       |          |            | 6.3.3.1.3        | Radiated Susceptibility · · ·                         | 201  |

| Sectio | on   |         |                              |                        |                              |        |       |       |   | Page |

|--------|------|---------|------------------------------|------------------------|------------------------------|--------|-------|-------|---|------|

|        |      |         | 6.3.3.2                      | Interference           | e Testing                    |        |       |       |   | 202  |

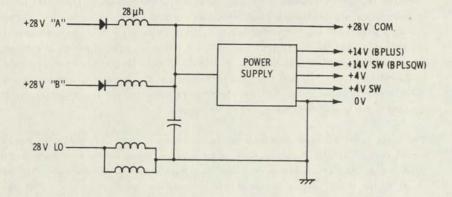

|        |      |         |                              | 6.3.3.2.1              | Power Line<br>Interference   |        |       |       |   | 202  |

|        |      |         |                              | 6.3.3.2.2              | Signal Leads<br>Interference | Condu  | cted  |       |   | 202  |

|        |      |         |                              | 6.3.3.2.3              | Radiated Inte                | rferen | ce    |       |   | 203  |

|        |      |         | 6.3.3.3                      | Grounding a            | and Shielding .              |        |       |       |   | 203  |

|        |      | 6.3.4   | EMI Spec                     | ification Lin          | nits                         |        |       |       |   | 204  |

|        |      | 6.3.5   | Electrom                     | agnetic Inter          | ference Proble               | ms     |       |       |   | 205  |

|        |      | 6.3.6   | EMI Test                     | s                      |                              |        |       |       |   | 205  |

|        |      | 6.3.7   | Conclusio                    | ons and Reco           | mmendations .                |        |       |       |   | 215  |

|        | 6.4  | Field E | xperience                    |                        |                              |        |       |       |   | 217  |

|        |      | 6.4.1   | Uplink Pr                    | roblem - APO           | OLLO 6 Missio                | n      |       |       |   | 218  |

|        |      | 6.4.2   | Test Con                     | nector Interf          | ace Problem .                |        |       |       |   | 219  |

|        |      | 6.4.3   | TC Trap                      | Problem                |                              |        |       |       |   | 221  |

|        |      | 6.4.4   | Radar Pr                     | oblem                  |                              |        |       |       |   | 223  |

|        |      | 6.4.5   | Miscellar                    | neous                  |                              |        |       |       |   | 224  |

| 7.0    | DELT | ABILITY |                              |                        |                              |        |       |       |   |      |

| 1.0    | 7.1  | Introdu |                              |                        |                              | • • •  |       | 5 .*. | • | 227  |

|        | 7.2  |         | nent Develo                  | · · · · · ·            |                              |        | 10.40 | •     |   | 227  |

|        | 1.4  | 7.2.1   |                              | nt Selection           |                              | • • •  |       | •     |   | 227  |

|        |      | 7.2.2   | and the second second        | ing Qualificat         | · · · · · · · ·              |        |       |       | • | 228  |

|        |      | 7.2.3   | Specifica                    |                        |                              |        | •     | • •   | • | 229  |

|        |      | 7.2.4   | Charles in the cost of the   | ocessing Spe           | cifications                  | • • •  | •     | •     | • | 233  |

|        | 7.3  |         | and the second second        | ocedures               | culcations                   | • • •  |       | •     | • | 233  |

|        | 1.0  | 7.3.1   | and the second second second | Control                |                              |        |       |       | • | 241  |

|        |      | 7.3.2   |                              |                        |                              |        | •     |       | • | 241  |

|        | 7.4  |         |                              | energiane en er        |                              | • • •  | •     | • •   | • | 242  |

|        | 1.4  | 7.4.1   | cturing Pro                  |                        |                              | • • •  | •     |       | • | 242  |

|        |      | 1.4.1   | 7.4.1.1                      | nt Defects .<br>Diodes |                              |        |       | •     |   | 243  |

|        |      |         |                              |                        |                              | • • •  |       | •     | • | 243  |

|        |      |         | 7.4.1.2                      | Transistors            |                              |        |       |       | • | 244  |

|        |      |         | 7.4.1.3                      |                        | le NOR Gate .                |        |       | • •   |   |      |

|        |      |         | 7.4.1.4                      |                        | tpack Dual NO                | R Gate |       | • •   | • | 245  |

|        |      |         | 7.4.1.5                      | DSKY Relay             | ·s                           | • • •  | •     | • •   | • | 247  |

|        |      | 7.4.2   | and the second second        | efects                 |                              |        |       | • •   | • | 248  |

|        |      |         | 7.4.2.1                      |                        |                              |        |       |       | • | 248  |

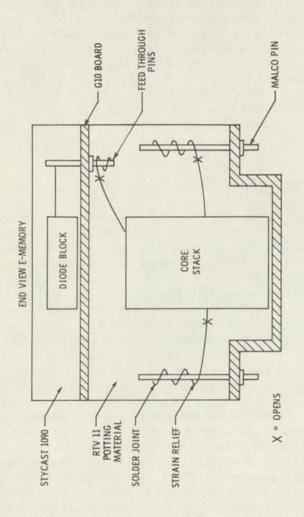

|        |      |         | 7.4.2.2                      | Erasable M             | emory Module                 | • • •  | •     | • •   | • | 249  |

| Sectio | on     |         |            |          |       |     |    |     |     |    |    |   |   |   |   |   |   |   |   | Pa  | age |

|--------|--------|---------|------------|----------|-------|-----|----|-----|-----|----|----|---|---|---|---|---|---|---|---|-----|-----|

|        |        |         | 7.4.2.3    | "Blue    | Nos   | e"  | P  | rol | ole | m  |    |   |   |   | • |   |   |   | • | • : | 251 |

|        |        |         | 7.4.2.4    | Diode    | Swi   | tch | in | g I | Pro | b1 | en | n | • | • |   | • | • | • | • | • : | 254 |

|        | 7.5    | Field E | xperience  |          |       |     | •  | •   | •   | •  | ÷  | • | • | • | • | ٠ | • | • | • | • : | 254 |

| 8.0    | SUMM   | ARY     |            |          |       |     |    |     |     |    |    |   |   |   |   |   |   |   |   | • : | 269 |

|        | 8.1    | Design  | and Develo | pment    |       |     |    | •   | •   | •  | •  | • | • | • | • | • | • | • | • | • : | 269 |

|        | 8.2    | Contrac | tual Arran | gement   | s.    |     |    |     | •   | •  | •  | • | • | • | • | • | • | • | • | • : | 272 |

|        | 8.3    | Approad | hes to Rel | iability |       |     |    |     |     | •  | •  |   | • | • | • | • |   |   | • | • : | 272 |

|        | 8.4    | Design  | Features.  |          |       |     | •  | •   | •   | •  | •  | • |   | • | • |   |   | • |   | • : | 274 |

|        |        | 8.4.1   | Read-Onl   | y Mem    | orie  | s - | R  | op  | es  | •  | •  |   | • |   |   | • |   | • | • | + 1 | 274 |

|        |        | 8.4.2   | The 16 B   | it Word  | Le    | ngt | h  |     |     |    |    |   |   | • |   |   | • | • |   | . : | 275 |

|        |        | 8.4.3   | Interface  | Design   | i     |     |    |     | •   |    |    |   |   | • |   |   |   | • | • | • : | 275 |

|        |        | 8.4.4   | General    | Capabil  | ity . |     |    | •   | •   |    | •  | • | • | • | • | • | • | • | • | • 3 | 275 |

| REFI   | ERENCE | s       |            |          |       |     |    |     |     |    |    |   |   |   |   |   |   |   |   |     | 279 |

### LIST OF ILLUSTRATIONS

| Figure | <u>e</u>                                                                    |   | Page |

|--------|-----------------------------------------------------------------------------|---|------|

| 1-1    | AGC-3 Core-Transistor Logic                                                 |   | 4    |

| 1-2    | AGC-4 Engineering Model                                                     |   | 6    |

| 1-3    | AGC-4 Front View                                                            |   | 8    |

| 1-4    | AGC-4 Back Panel View                                                       |   | 8    |

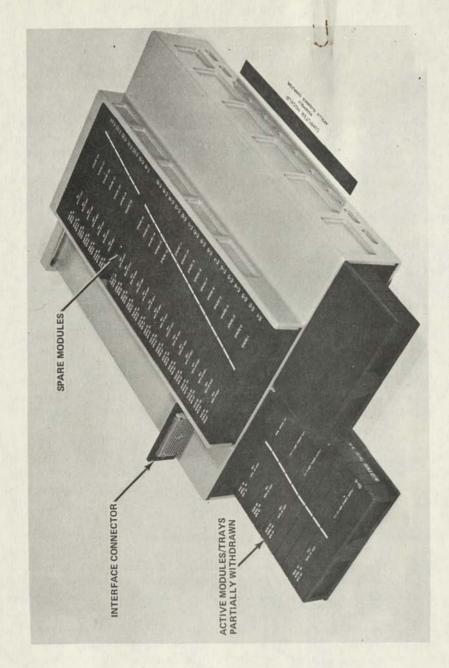

| 1-5    | Computer Modular Construction                                               |   | 12   |

| 1-6    | Block 0 Computer                                                            |   | 14   |

| 1-7    | Dual Computer Model                                                         |   | 14   |

| 1-8    | Block I Computer and DSKYs                                                  |   | 16   |

| 1-9    | Block II Computer and DSKY                                                  | • | 17   |

| 2-1    | CM Main Display and Control Panel                                           |   | 24   |

| 2-2    | CM Lower Equipment Bay                                                      |   | 25   |

| 2-3    | LM Display and Control Panel                                                |   | 26   |

| 2-4    | Computer Simplified Block Diagram                                           |   | 28   |

| 2-5    | DSKY Front Panel                                                            |   | 31   |

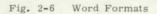

| 2-6    | Word Formats                                                                |   | 34   |

| 2-7    | Illustrative Examples of Properties of Modified One's Complement<br>System. | ŧ | 36   |

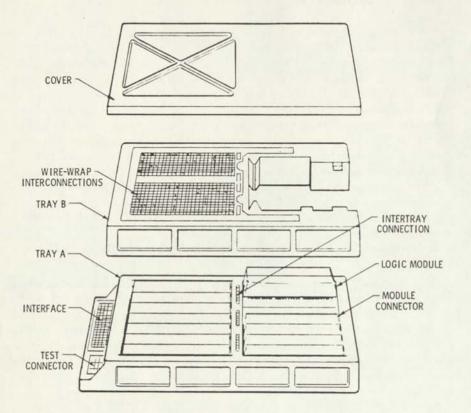

| 2-8    | Exploded Artist's Concept of Block II Computer                              | ÷ | 50   |

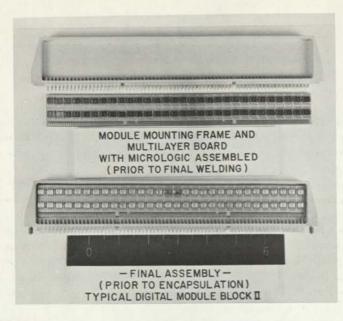

| 2-9    | Logic Module Containing 120 Microcircuit Units                              |   | 52   |

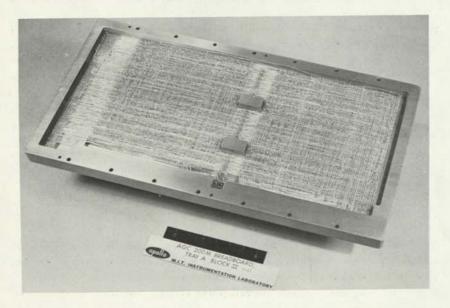

| 2-10   | Photograph of Wire-Wrapped Tray Connections                                 |   | 52   |

| 3-1    | Block I and Block II Integrated Circuit Logic Gates                         |   | 60   |

| 3-2    | Equivalent Logic, NOR Circuits in Computer Central Registers .              |   | 63   |

| 3-3    | Timing Logic Functional Diagram.                                            |   | 64   |

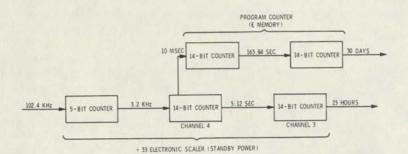

| 3-4    | Programming Counter and Scaler Configuration                                |   | 64   |

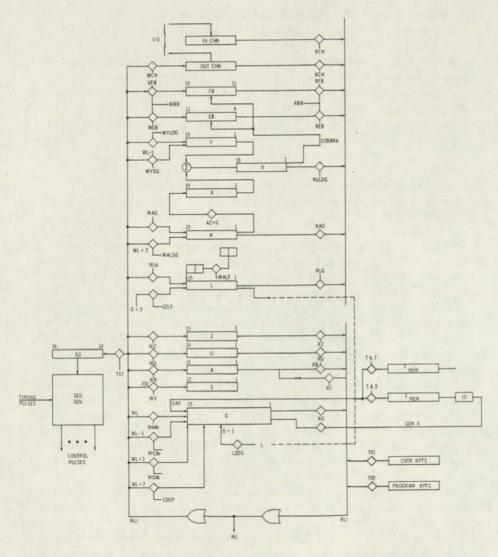

| 3-5    | Central Processor                                                           |   | 66   |

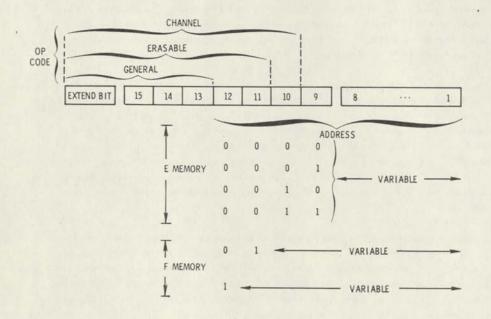

| 3-6    | Computer Instruction Word.                                                  |   | 72   |

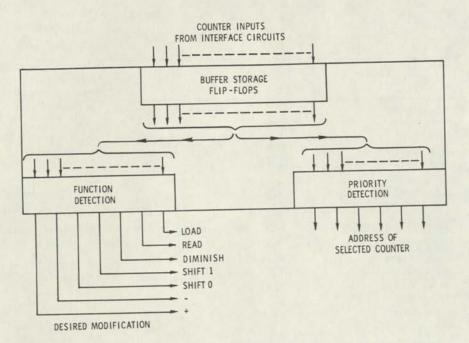

| 3-7    | Structure of Computer Priority Circuit                                      |   | 76   |

| 3-8    | Computer Power Supplies, Simplified Block Diagram                           |   | 84   |

| 3-0    | Erasable Memory Current Switching                                           |   | 86   |

### LIST OF ILLUSTRATIONS (Cont)

| Figure |                                                               |     |     | Pag   | e |

|--------|---------------------------------------------------------------|-----|-----|-------|---|

| 3-10   | Regulated Pulsed Current Driver Circuit                       |     |     | . 88  | 3 |

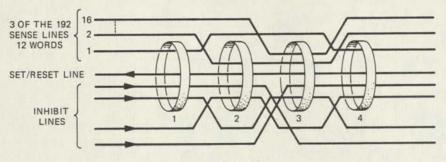

| 3-11   | Sense Amplifier Circuit                                       |     |     | 1220  | 9 |

| 3-12   | Core Rope Simplified Schematic                                |     | • 3 | . 90  | ) |

| 3-13   | Rope Sense Line Switching Simplified Diagram                  |     |     | . 92  | 2 |

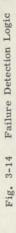

| 3-14   | Failure Detection Logic                                       |     |     | . 94  | 1 |

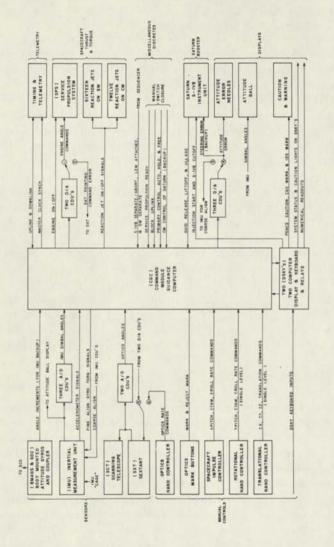

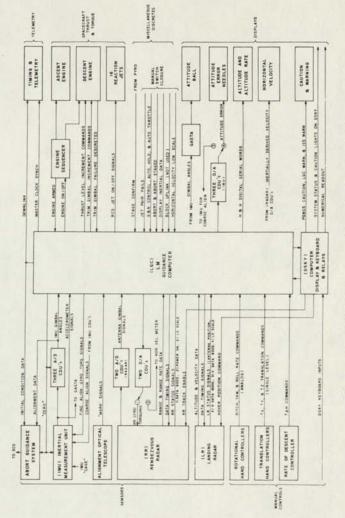

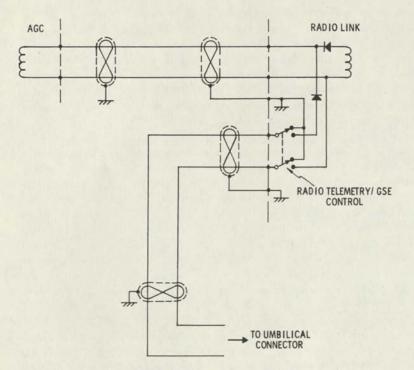

| 3-15   | GN&C Interconnections in Command Module                       |     |     | . 98  | B |

| 3-16   | GN&C Interconnections in Lunar Module                         |     |     | . 99  | 9 |

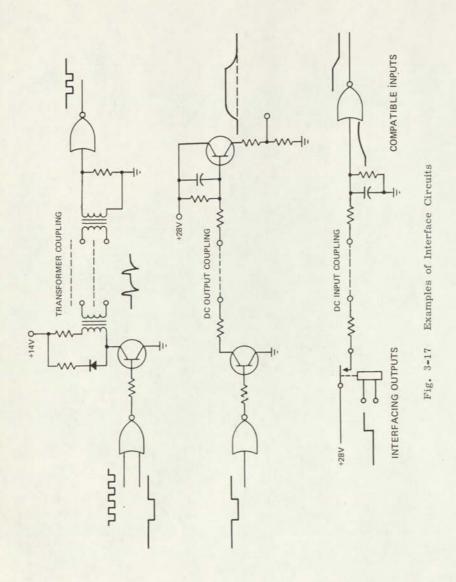

| 3-17   | Examples of Interface Circuits                                |     |     | . 100 | D |

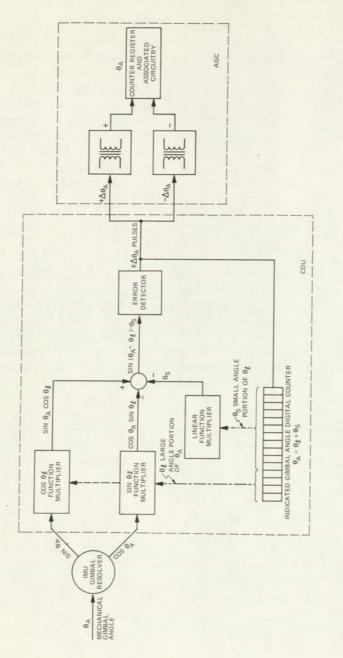

| 3-18   | Gimbal Resolver Coupling Data Unit - Computer Interface       | •   |     | . 104 | 4 |

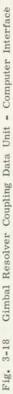

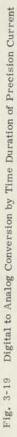

| 3-19   | Digital to Analog Conversion by Time Duration of Precision Co | uri | ren | t 105 | 5 |

| 3-20   | Digital to Analog Conversion by Resistance Ladder             |     |     | . 106 | 6 |

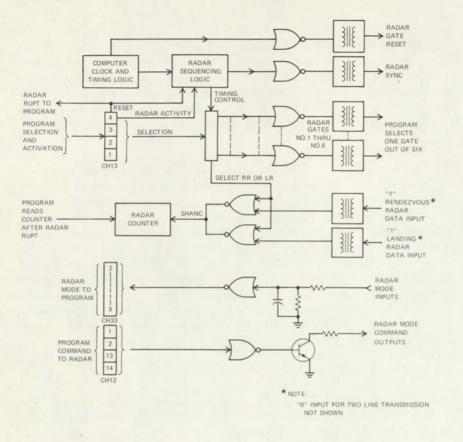

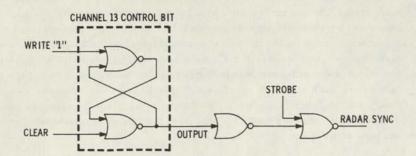

| 3-21   | Radar-Computer Interface Functional Diagram                   |     | •   | . 108 | В |

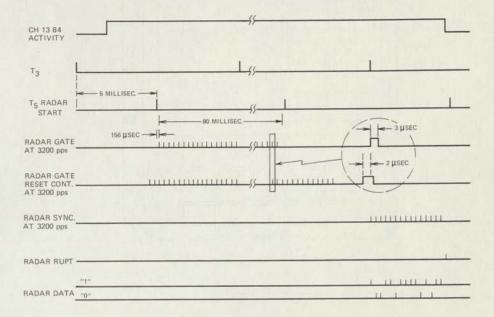

| 3-22   | Radar-Computer Interface Timing Diagram                       |     |     | . 109 | 9 |

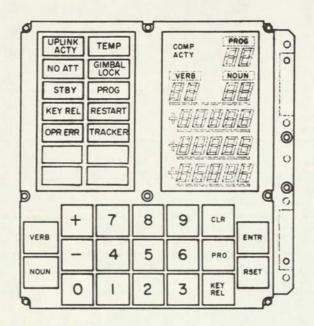

| 3-23   | DSKY Display and Control Panel                                | •   | •   | . 110 | 0 |

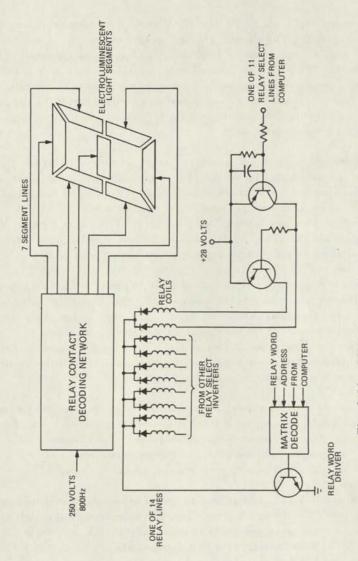

| 3-24   | DSKY Display Circuits - Simplified Diagram                    |     |     | . 111 | 2 |

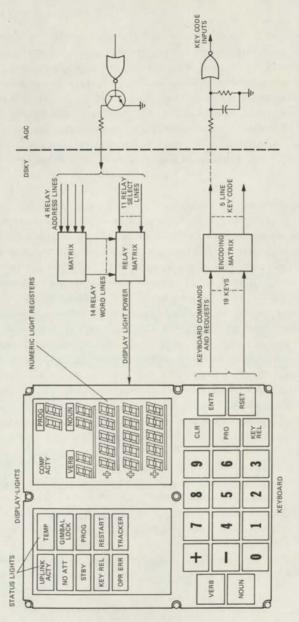

| 3-25   | DSKY Block Diagram                                            | *   |     | . 113 | 3 |

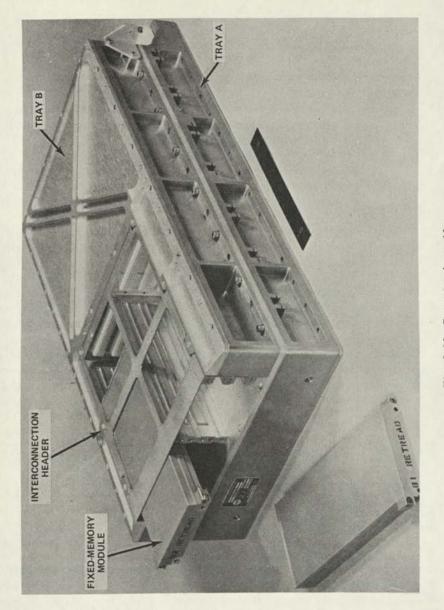

| 3-26   | Computer Assembly                                             | •   | •   | . 110 | 6 |

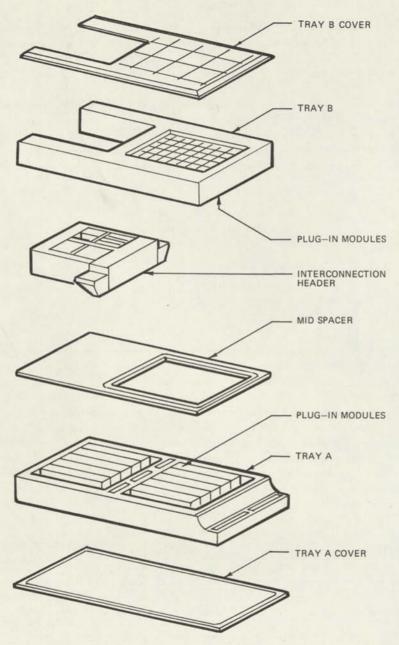

| 3-27   | Exploded View of Computer                                     |     | •   | . 11  | 8 |

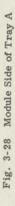

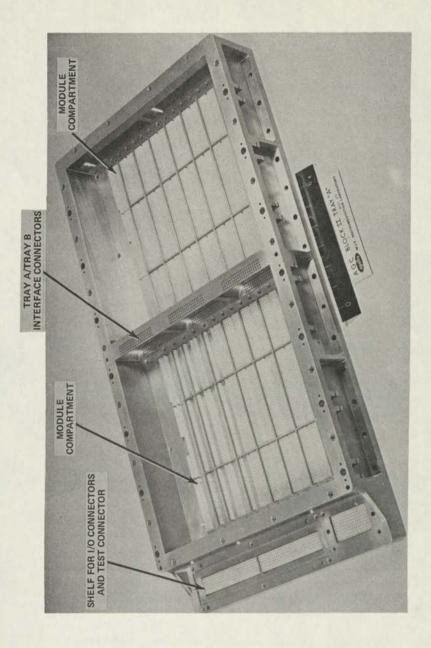

| 3-28   | Module Side of Tray A                                         | •   | •   | . 11  | 9 |

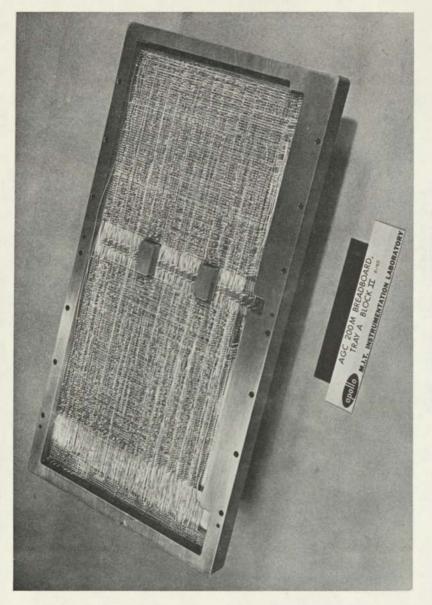

| 3-29   | Wire-Wrap Side of Tray A                                      |     |     | . 12  | 0 |

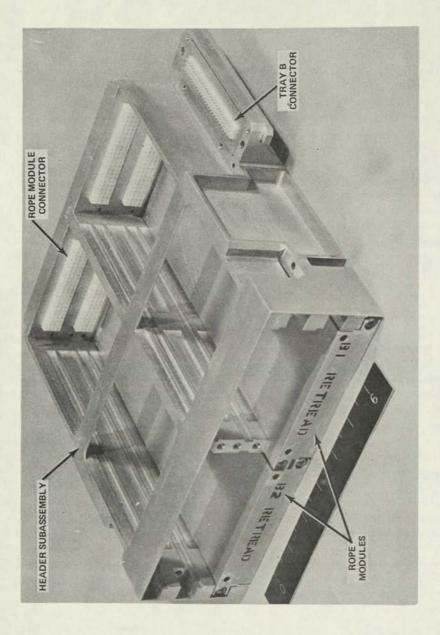

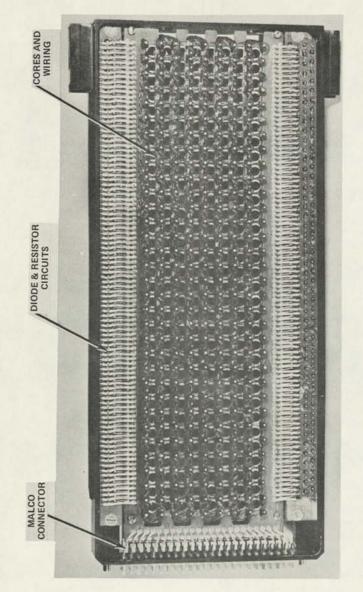

| 3-30   | Interconnection Header Assembly                               | •   |     | · 12  | 2 |

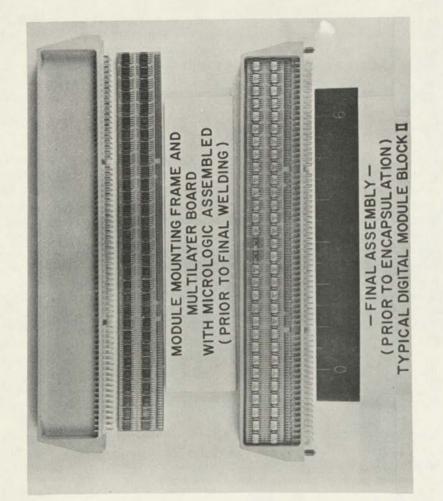

| 3-31   | Typical Logic Module Construction                             | •   |     | · 12  | 4 |

| 3-32   | Typical Welded Cordwood Construction                          | •   | •   | · 12  | 6 |

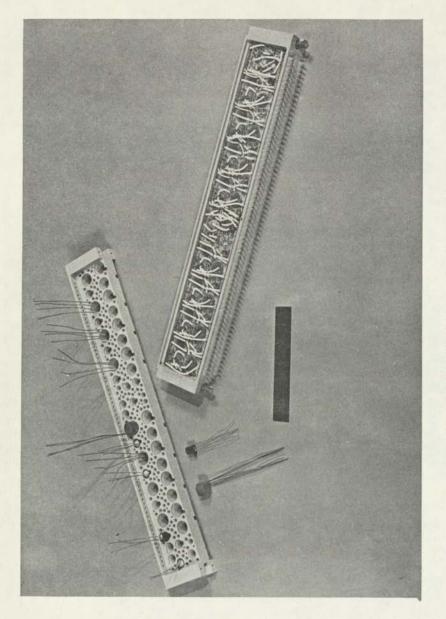

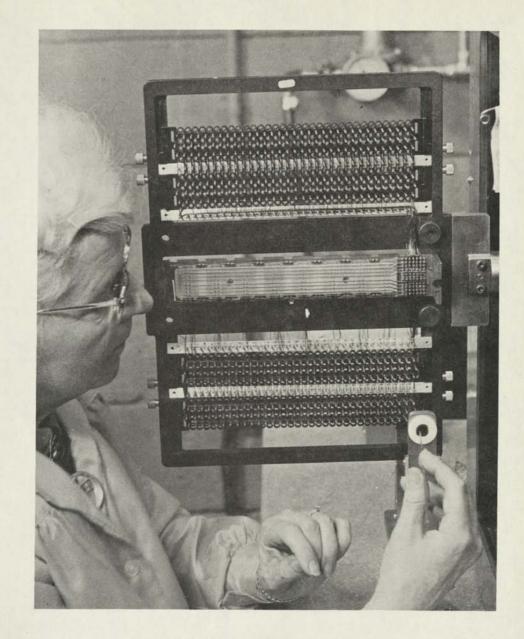

| 3-33   | Core Rope Module Sense Line Wiring                            | •   |     | · 12  | 7 |

| 3-34   | Core Rope Module                                              |     | •   | · 12  | 8 |

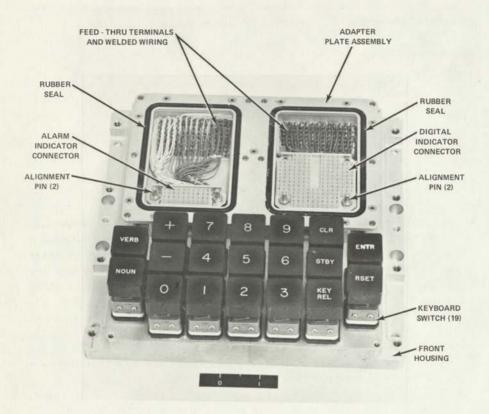

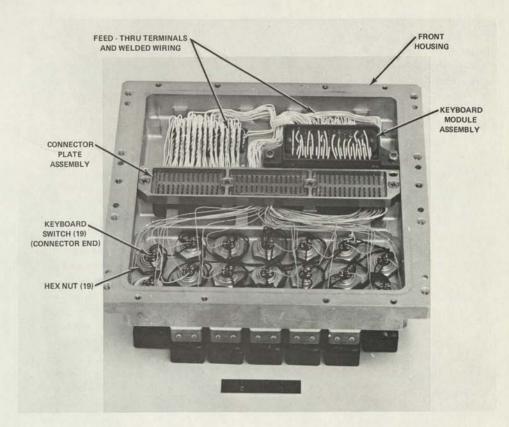

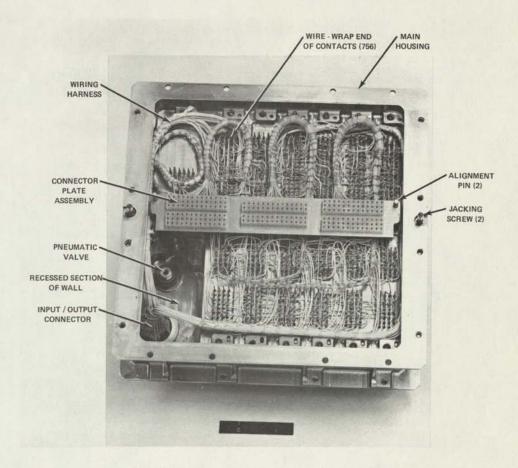

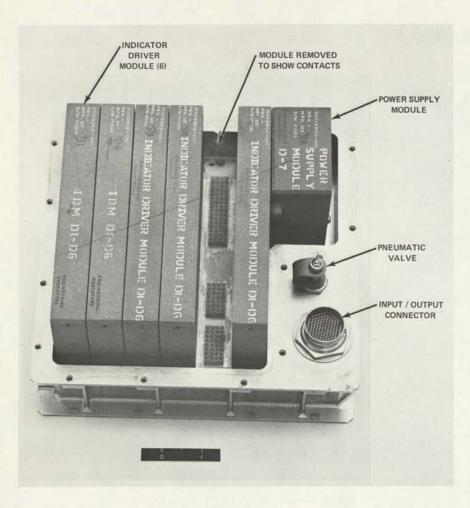

| 3-35   | Exploded View of DSKY                                         | •   | •   | • 13  | 2 |

| 3-36   | Front Side of Front Housing Assembly                          | •   | •   | · 13  | 4 |

| 3-37   | Rear Side of Main Housing Assembly                            | •   | •   | • 13  | 5 |

| 3-38   | Front Side of Main Housing Assembly                           | •   | •   | · 13  | 7 |

| 3-39   | Rear Side of Main Housing Assembly                            | •   | •   | · 13  | 8 |

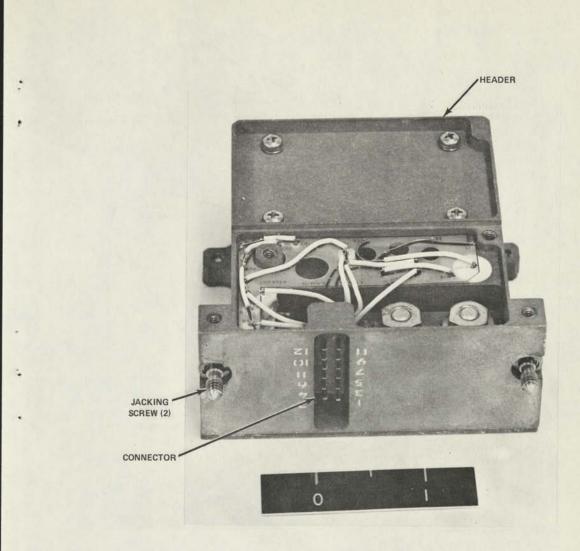

| 3-40   | Power Supply Module                                           | •   | •   | · 14  | 1 |

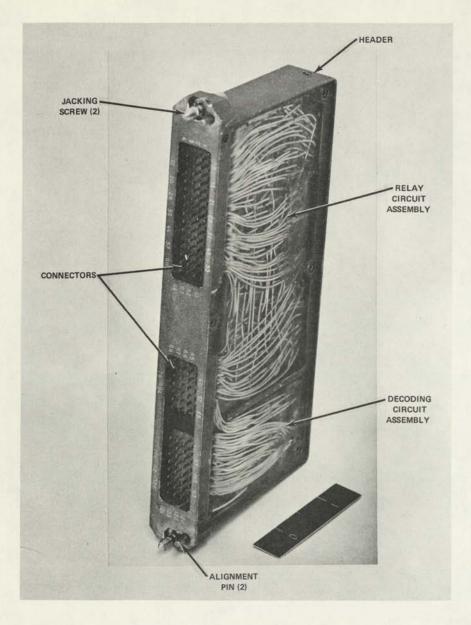

| 3-41   | Typical Indicator Driver Module                               |     | •   | • 14  | 2 |

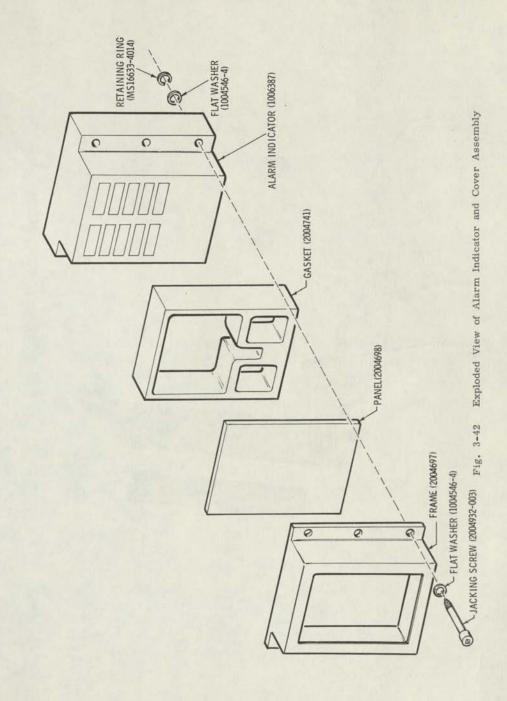

| 3-42   | Exploded View of Alarm Indicator and Cover Assembly           | •   | •   | • 14  | 3 |

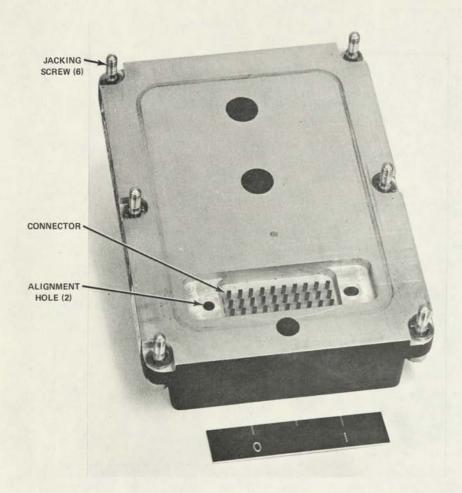

| 2.49   | Rear Side of Alarm Indicator                                  |     |     | . 14  | 4 |

### LIST OF ILLUSTRATIONS (Cont)

### Figure

| 3-44 | Exploded View of Digital Indicator and Cover Assembly                          |      | 146 |

|------|--------------------------------------------------------------------------------|------|-----|

| 3-45 | Rear Side of Digital Indicator                                                 |      | 147 |

| 3-46 | Exploded View of Pushbutton Switch                                             | • •  | 148 |

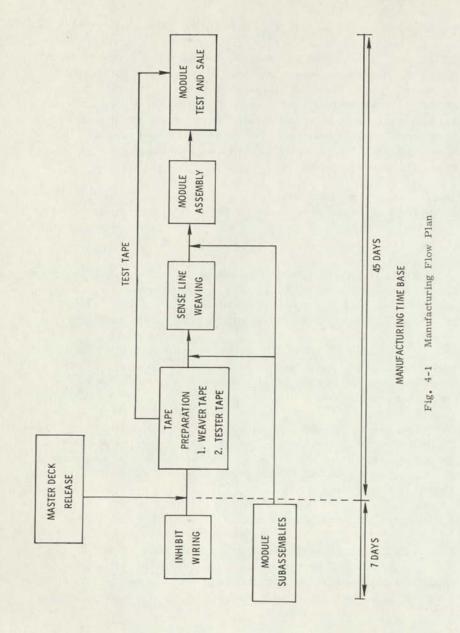

| 4-1  | Manufacturing Flow Plan                                                        |      | 164 |

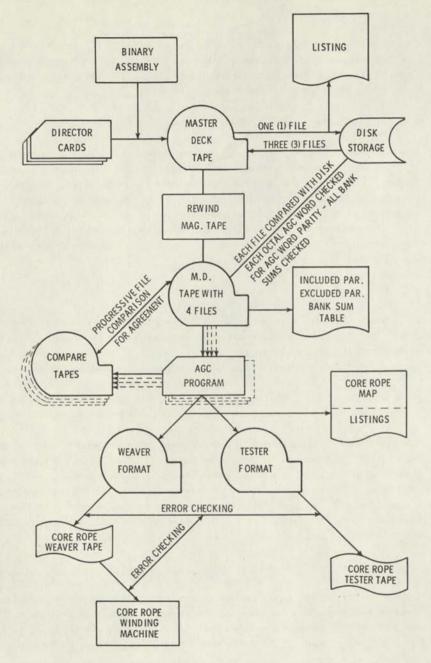

| 4-2  | Functional Diagram of Data Processing and Verification during<br>Manufacturing |      | 166 |

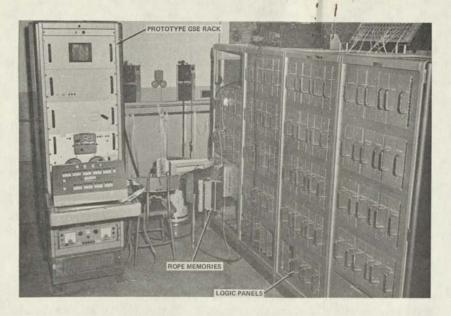

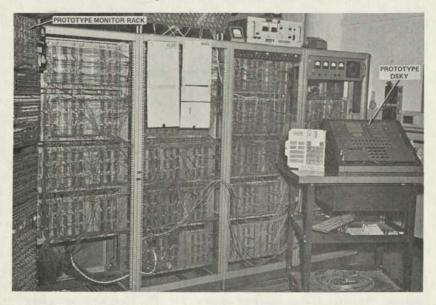

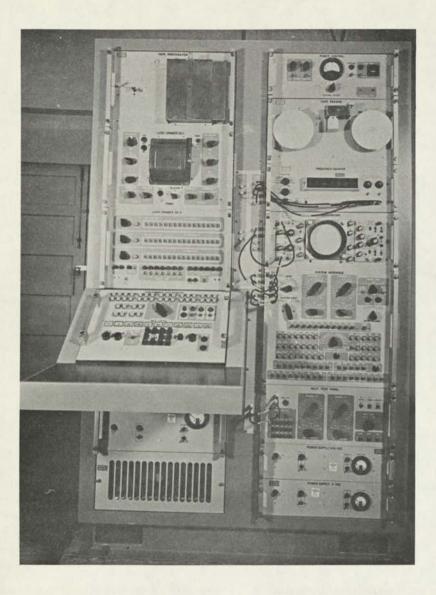

| 5-1  | Computer Test Set                                                              |      | 170 |

| 5-2  | Trace System Block Diagram                                                     | • •  | 178 |

| 6-1  | Transformer Coupled Output Circuit                                             |      | 186 |

| 6-2  | Transformer Coupled Input Circuit                                              |      | 188 |

| 6-3  | DC Output Circuit                                                              | • •  | 188 |

| 6-4  | "C" Circuit Application                                                        |      | 190 |

| 6-5  | Discrete (D) Input Circuit                                                     |      | 190 |

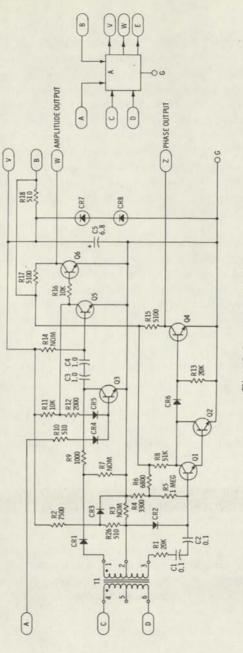

| 6-6  | "A" Circuit                                                                    |      | 192 |

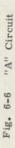

| 6-7  | 28 Volt DC Input Power                                                         | • •  | 194 |

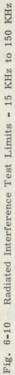

| 6-8  | Power Line Conducted Interference Test Limits Using Current Pr                 | robe | 206 |

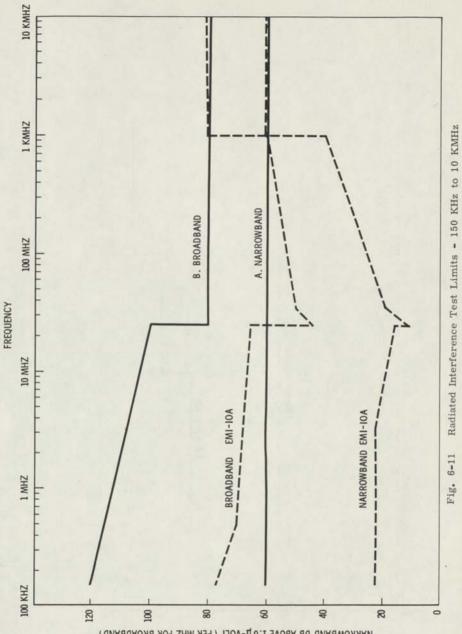

| 6-9  | Conducted Interference Test Limits                                             |      | 207 |

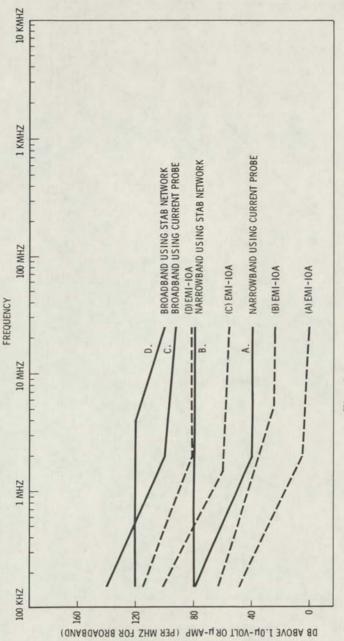

| 6-10 | Radiated Interference Test Limits - 15 KHz to 150 KHz                          |      | 208 |

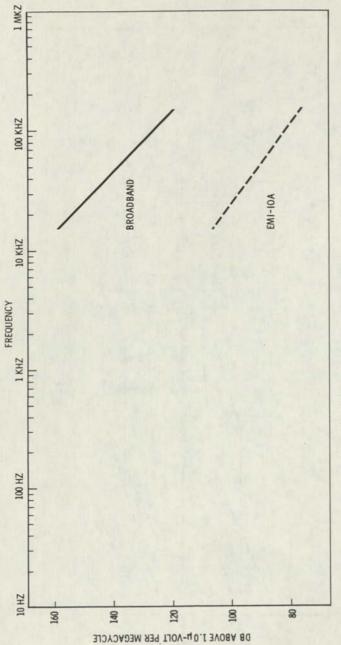

| 6-11 | Radiated Interference Test Limits - 150 KHz to 10 KMHz                         |      | 209 |

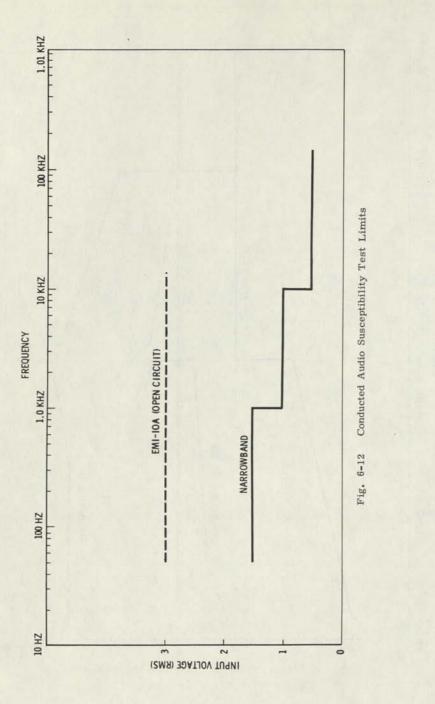

| 6-12 | Conducted Audio Susceptibility Test Limits                                     |      | 210 |

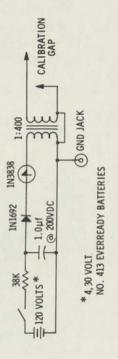

| 6-13 | Spark Generator for Radiated Transient Test                                    |      | 213 |

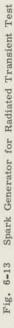

| 6-14 | Induced Signals from Unbalance Lines                                           |      | 216 |

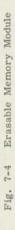

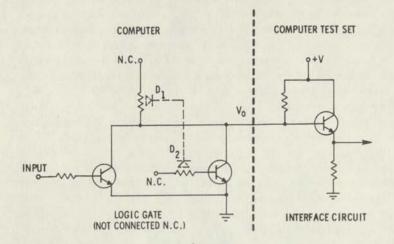

| 6-15 | Uplink Interface Circuit                                                       |      | 220 |

| 6-16 | Radar Interface Anomaly                                                        |      | 222 |

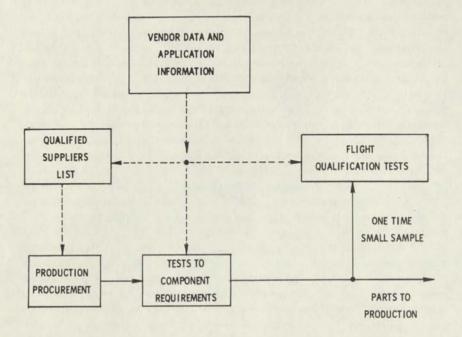

| 7-1  | Procedure for Component Selection and Qualification                            |      | 230 |

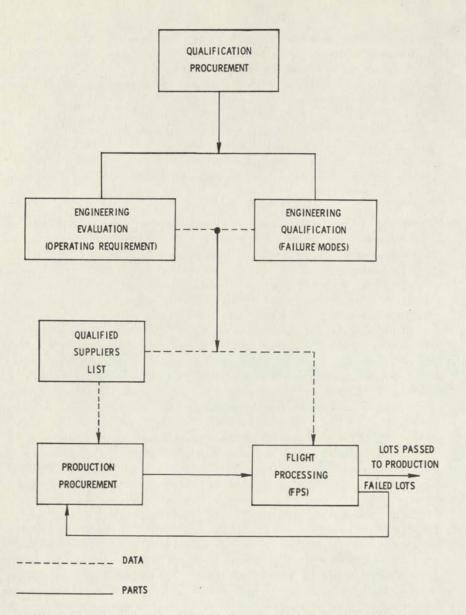

| 7-2  | Procedure for Critical Component Selection and Qualification .                 |      | 232 |

| 7-3  | Block Diagram of the Flight Processing Specification Procedure .               |      | 236 |

| 7-4  | Erasable Memory Module                                                         |      | 250 |

| 7-5  | Integrated Circuit Gate Illustrating "Blue Nose" Problem                       |      | 252 |

| 7-6  | First Pulse of Pulse Train                                                     |      | 252 |

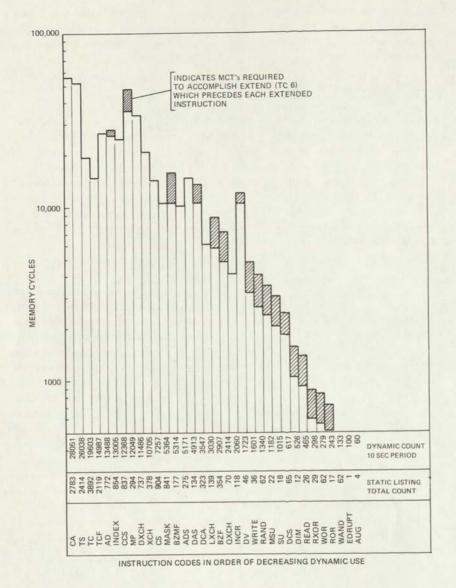

| 8-1  | Voluntary Instruction Code Statistics                                          |      | 276 |

### LIST OF TABLES

| Table  | Page                                                         |

|--------|--------------------------------------------------------------|

| 2-I    | Computer Characteristics                                     |

| 2-II   | Addressable Central and Special Registers                    |

| 2-III  | Instruction Classes                                          |

| 2-IV   | Normal Instructions                                          |

| 2-V    | Special Instructions                                         |

| 3-I    | Major Milestones                                             |

| 3-II   | Block I Development Summary                                  |

| 3-III  | Block II Development Summary                                 |

| 3-IV   | Special Addressable Registers                                |

| 3-V    | Fixed and Erasable Addressing Locations                      |

| 3-VI   | Instruction Codes                                            |

| 3-VII  | Special Prupose Counters                                     |

| 3-VIII | Channel Register Functions                                   |

| 4-I    | Listing of Computer Program Assemblies                       |

| 4-II   | Computer Program Assemblies Released for APOLLO Missions 153 |

| 4-III  | Partial List of Interpretive Operators                       |

| 6-I    | AGC Interface Circuits                                       |

| 6-11   | Test Connectors (Micrologic Interfaces)                      |

| 6-III  | Conducted RF Susceptibility Test Limits (LSN)                |

| 6-IV   | Radiated RF Susceptibility Test Limits                       |

| 6-V    | Transient Testing                                            |

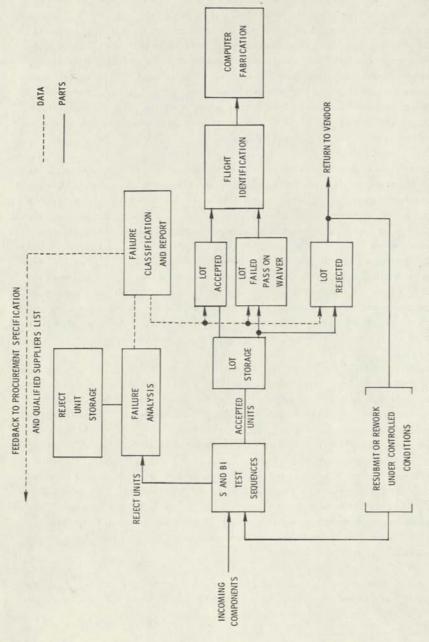

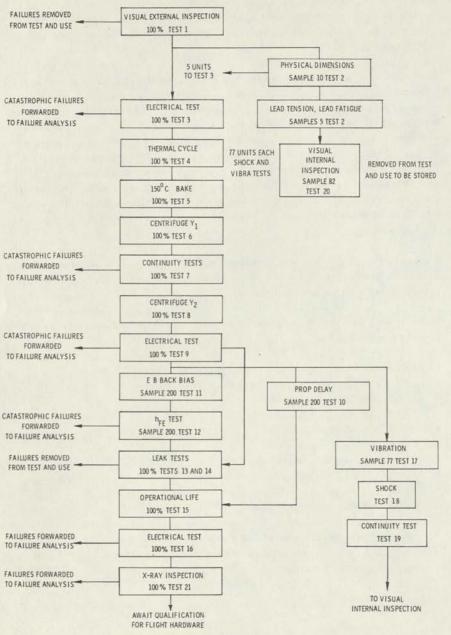

| 7-I    | Flow Diagram for the Test Sequence                           |

| 7-II   | Failure Acceptance Criteria for NOR Gate                     |

| 7-III  | AFR Cause Classification                                     |

| 7-IV   | AGC Census                                                   |

| 7-V    | Failure Calssification                                       |

| 7-VI   | DSKY Census                                                  |

| 7-VII  | AGC Reliability Statistics                                   |

| 7-VIII | AGC Parts Count                                              |

| 8-I    | Involuntary Instruction Code Statistics                      |

### PREFACE

"I believe this nation should commit itself to achieving the goal before this decade is out of landing a man on the moon and returning him safely to earth." With these words, spoken on 25 May 1961, President John Fitzgerald Kennedy stated for all Americans the challenge of the APOLLO project. The Massachusetts Institute of Technology Instrumentation Laboratory<sup>\*</sup> was selected to design and develop the hardware and software of the APOLLO Guidance, Navigation and Control system for safe and self-sufficient translunar flight, lunar landing, and return. This Final Report describes that work — a most demanding, innovative, and rewarding task.

This report presents the Draper Laboratory's efforts in Project APOLLO from the original contract award in mid-1961 through July 1969. The report is organized in five volumes:

VOLUME I: PROJECT MANAGEMENT AND SYSTEMS DEVELOPMENT VOLUME II: OPTICAL, RADAR, AND CANDIDATE SUBSYSTEMS VOLUME III: COMPUTER SUBSYSTEM VOLUME IV: INERTIAL SUBSYSTEM VOLUME V: THE SOFTWARE EFFORT

Volume I emphasizes what was done in terms of resource allocation and systems development and contains Appendices A and B; Volumes II through IV describe the hardware subsystems in detail, with emphasis on the final design configurations; Volume V fully treats the Laboratory's software effort. Appendix A presents abstracts of significant research and engineering reports and theses written under Contracts NAS 9-153 and NAS 9-4065. Appendix B is a bibliography of all such reports and theses prepared through June 1969. This date is also the cutoff for all discussions within this report, except for APOLLO 11 — the first manned lunar landing and return.

\*The Laboratory was renamed the Charles Stark Draper Laboratory in January 1970.

### SECTION 1.0 SUBSYSTEM DEVELOPMENT

### 1.1 EVOLUTION OF THE COMPUTER SUBSYSTEM

The APOLLO guidance computer (AGC) is a real time digital control computer whose conception and development took place in the early part of 1960. The computer may be classifed as a parallel, general-purpose or whole number binary computer. This class of computer is representative of most of the ground based digital computers, in existence in the late 1950s, when the precursors of the AGC were being designed. Few computers of this class had been designed by that time for the aerospace environment, and those few embodied substantial compromises in performance for the sake of conserving space, weight, and power.

The APOLLO guidance computer was a descendant of a series of MIT/IL designs. In 1959 and 1960, MIT/IL designed a unique machine with a self-contained guidance and navigation capability intended for use in a proposed space vehicle to photograph Mars and return. This machine, although never built, was designed to use magnetic core-transistor logic. This type of logic circuitry is desirable because of its low power consumption, but it tends to be slow and bulky. The Mars computer had very limited capabilities due to the constraint on physical size but, since computation speed requirements were not severe, an adequate machine was possible within the state-of-the-art at that time. The instruction repertoire, word length, and number of erasable memory cells were also very limited. Provision was made, however, for a moderately large amount of fixed memory for instructions and constants. A high density memory of the read-only type, called a rope memory, was developed especially for this purpose and was carried over into the design of the APOLLO computer.

The rope memory, being a transformer type, depends for its information storage on the patterns with which its sensing wires are woven at the time of manufacture. Once a rope memory is built, its information content is fixed and is unalterable by electrical excitation; it can be altered only by re-manufacture, repair, or destruction. An erasable memory, on the other hand, is characterized by its ability to be loaded and altered electrically at any time. Rope memories were used in the APOLLO guidance computer because of their high density and information retention advantages. However, ropes placed a burden on software delivery schedules because of the

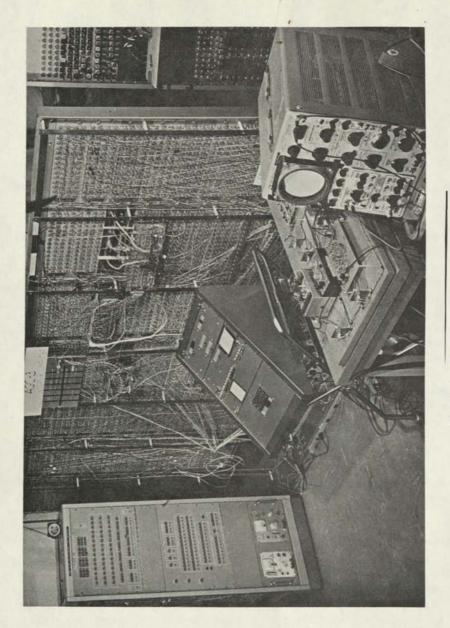

Fig. 1-1 AGC-3 Core-Transistor Logic

×.

additional time required for manufacturing the rope memories. Also system integration and testing was less flexible than was desirable, but these disadvantages were considered acceptable when compared with the advantages of high density and reliability.

The Mars computer incorporated a method of accommodating real time inputs and outputs that was unusual at the time but is widely used now. This was the program interrupt method which had been introduced in large scale computers a few years previously. A novel use of the interrupt was for single accesses to memory for trivial processes such as incrementing or shifting. This process has become known as memory cycle stealing and is widely used in linking computers to such peripheral units as magnetic tape units and card readers. The use of the interrupt in its various forms was an important addition to the aerospace computer field, and was a major architectural attribute of the AGC.

Another important aspect of the Mars computer which had evolutionary significance for the APOLLO computer was the use of an interpretive program; that is, a large library of subroutines which perform various higher level arithmetic and language operations. Without the interpretive instructions, the limited instruction repertoire of the computer could have been costly in the amount of memory needed to contain the mission program. The interpretive program is a means of trading off execution speed against instruction repertoire. The Mars computer appeared to have a commodious set of instructions, that allowed substantial economies in program writing, where the more powerful "instructions" were actually executed by subroutines written in the more restrictive basic instruction repertoire.

The Mars computer design was followed by a number of subsequent revisions and additions embodied in several models designated Mod 1A, 1B, 3C, and AGC3 each of which incorporated the rope memory, core-transistor logic, and the same general architecture relating to interrupts, word length, and instruction repertoire. Word length varied from 12 to 24 bits and instruction repertoire from 4 to 32 basic instructions with additional involuntary and interpretive instructions.

Mod 3C was notable in this series for the introduction of a 512-word 16-bit coincident-current magnetic core erasable memory. This followed the commercial development of lithium ferrite cores with a low enough temperature coefficient to be practicable in a broad temperature range application. The Mod 3C hardware was eventually converted to the AGC3. See Figure 1-1. This was the last in the series of core-transistor logic computers and the first prototype computer developed for the APOLLO guidance system.

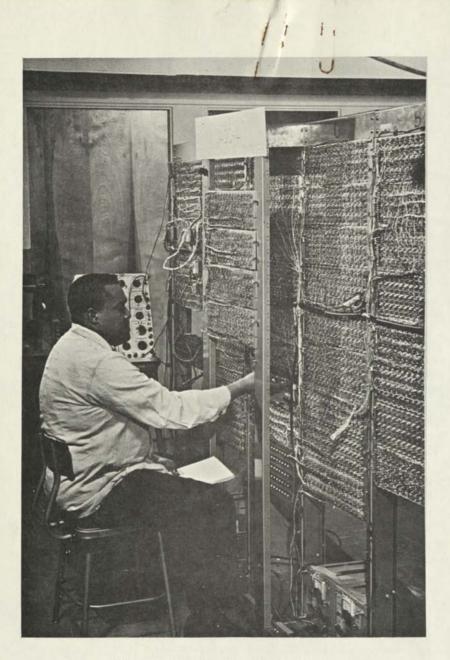

Fig. 1-2 AGC-4 Engineering Model

In AGC3 the erasable memory had 1024 words, also 16 bits long. Its rope memory held 12,288 words, and it had 11 instructions in its repertoire. Normal instruction execution time was 40 microseconds, of which approximately 20 microseconds were consumed by the two memory access cycles required to fetch (or store) instructions and data. The remaining time was occupied in manipulation and transfer of numbers among the central and special registers, including the adder and various buffering and editing registers.

The editing and input/output operations, which are commonly handled by special instructions, were processed by special memory cells instead. For example, to shift a word in this family of machines, the word is stored in a special register designed for this purpose and read out again. The shifting is accomplished between the store and read registers. This technique sacrifices memory, but is essential in cases where the instruction repertoire is severely limited.

During the evolutionary period of the Mars computer and its descendants (1958 to 1962), the hardware technology available to the aerospace computer designer was developing rapidly. Mention has already been made of the adaptation of the three-dimensional magnetic core array to the temperature environment. Another important line of evolution was in semiconductor technology, where silicon transistors progressed to planar forms, then epitaxial form. Ultimately monolithic integrated circuits were developed. Still another area of development was in packaging, where the introduction of welding, matrix interconnection techniques, and machine wirewrapping allowed significant reductions in volume and weight while coincidently enhancing reliability. These packaging techniques were reduced to practice and used by MIT/IL in the development of the POLARIS guidance computer. The experience gained and the techniques developed during the POLARIS program were used more or less directly in the APOLLO computer design.

Integrated circuits were in development by the semiconductor industry during the late 1950s under Air Force sponsorship. In late 1961, MIT/IL evaluated a number of integrated circuits for the APOLLO guidance computer. An integrated circuit equivalent of the Mod 3C computer was constructed and tested in mid-1962 to discover any problems the circuits might exhibit when used in large numbers. This became the engineering model of AGC4. (See Figure 1-2.) Reliability, power consumption, noise generation, and noise susceptibility were the primary subjects of concern in the use of integrated circuits in the AGC. The performance of the units under evaluation was sufficient to justify their exclusive use in place of core-transistor logic with the exception of a portion of the erasable memory addressing circuitry, where metal tape cores were retained as a medium for current switch selection.

Fig. 1-3 AGC-4 Front View

Fig. 1-4 AGC-4 Back Panel View

Accordingly, the APOLLO Block I computer was designed to use integrated circuit logic along the functional lines of, and as a replacement for, the core transistor logic of the AGC3 computer.

1

The first rack-mounted guidance computer emerged in early 1963 as AGC4 (see Figures 1-3 and 1-4) with integrated circuit logic, fixed rope memory, coincidentcurrent-erasable memory, and discrete-component circuits for the oscillator, power supplies, certain alarms, interface, and memory electronics. The rope memory contained 12.288 words, but this figure was shortly revised upward to 24,576, made possible by designing the rope modules with the eventual expansion in mind. No particular mission-related need for this expansion had been identified other than an uneasiness about the possible insufficiency of the 12K memory. Within a year, when the first mission program requirements had been conceived, documented, and collected, there was increasing concern about the possible insufficiency of the 24K memory, which prompted further expansion of the computer memory by mid-1964 to 36K. Figures 1-3 and 1-4 also show some of the early engineering test equipment. including the early ground support equipment (GSE), the monitor equipment, and display and keyboard (DSKY). The circuit and functional characteristics designed into the AGC-4 computer, together with the DSKY and the GSE, became the basis for the first (or Block I) production version of the APOLLO computer. The term, Block I, was used to distinguish this equipment from that which was developed later. and that was classified as Block II.

The erasable memory contained 1024 words, of which the first 16 locations were reserved for the central and special registers external to the core memory unit. These registers were used as flip-flops in the logic of the computer.

Both the fixed and erasable memories were operated at approximately a 12 microsecond memory cycle time (MCT), which is the time interval between erasable memory accesses. This was quite leisurely for the erasable memory, and allowed for content modification between reading and writing such as incrementing and shifting functions that were needed for memory cycle stealing operations. The rope memory is inherently slow, and was operating a good deal less leisurely. There was no hierarchical distinction between the fixed and erasable memories; both were accessible by any instruction. The instructions writing into memory would of course fail to alter the contents of fixed memory.

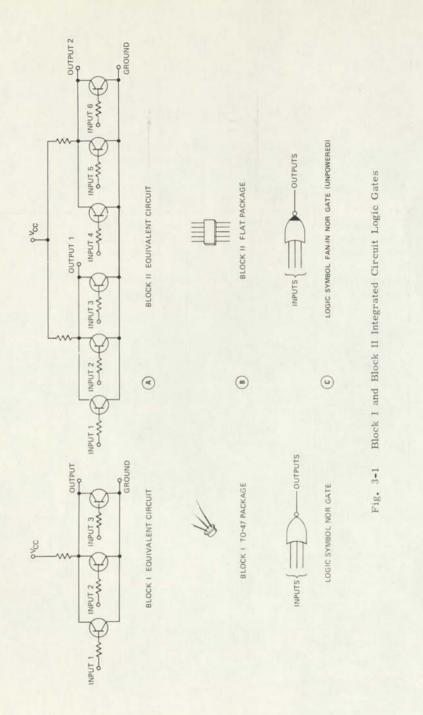

The integrated circuit logic section for the Block I computer was designed using a three-input NOR gate as a building block, with one gate in a TO-47 type package. These gates were relatively simple in form, consisting of the equivalent of three NPN bipolar transistors and four resistors connected as a modified direct-coupled transistor logic or DCTL NOR gate. The arrangement is also referred to, less precisely, as resistor-transistor logic or an RTL NOR gate. The gates were interconnected using a welded nickel ribbon matrix and packaged in modules containing 120 gates and a 140-pin connector. With this method of packaging, thirty-six logic modules were required for the logic functions of the Block I computer. The computer would have required fewer integrated circuit packages if a variety of logic building blocks had been used including, for example, a gated flip-flop. It was estimated, however, that the problem of producing and qualifying even a second circuit type would have outweighed the advantages of a variety of logic types. In retrospect, this estimation was correct. The single logic type simplified packaging, manufacturing, and testing, and gave higher confidence to the reliability predictions.

One other integrated circuit was used in the Block I computer, a differential amplifier for sensing memory outputs. This device was developed especially for the guidance computer, since a differential amplifier capable of memory sensing was not available at that time. The sense amplifier contained the equivalent of six NPN bipolar transistors and eight resistors. Such units were preferred over discrete-component sense amplifiers not only for their small size, but also for the close match of characteristics and tracking desired between components of the differential stage.

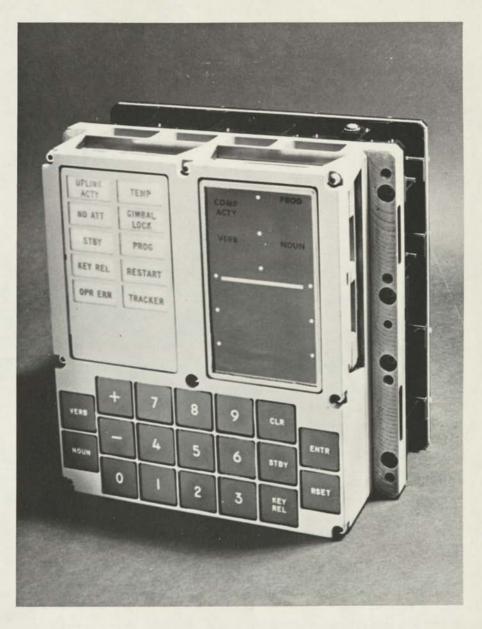

As an adjunct to the APOLLO guidance computer, a display and keyboard unit was required as an information interface with the crew. The original design was made during the latter stages of development of the Mod 3C computer, at which time neon numeric indicator tubes of the "Nixie" variety were used to generate three 4-digit displays for information, plus three 2-digit displays for identification. These were the minimum considered necessary, and they provided the capability of displaying three-space vectors with sufficient precision for crew operations. The 2-digit indicators were used to display numeric codes for verbs, nouns, and program numbers. The verb-noun format permitted communication in language with syntax similar to that of spoken language. Examples of verbs were "display", "monitor", "load", and "proceed," and examples of nouns were "time", "gimbal angles", "error indications", and "star identification number." A keyboard was incorporated along with the display to allow the entering of numbers and codes for identifying them. The unit acquired the designation DSKY, for display and keyboard.

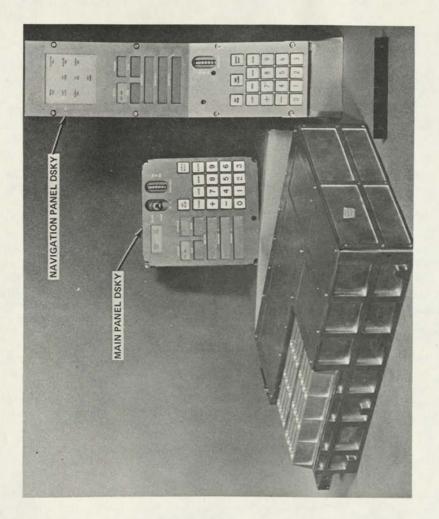

The DSKY design incorporated segmented electroluminescent numeric displays instead of neon, and a 5-digit instead of 4-digit display to accommodate a base eight (octal) display of a 15-bit computer word. In the Block I computer, two different physical outlines were generated for the DSKY, one for the navigation station in the

vicinity of the GN&C system (lower equipment bay), and one for the main control panel located above the crew couches. Figure 1-4 shows a main panel DSKY beside an engineering version of the design.

In 1964, when the APOLLO GN&C system underwent redesign for both the command module (CM) and lunar module (LM) spacecraft, the requirements for the current operational version of the APOLLO computer and DSKY were conceived. This version of the computer became known by the various designations AGC, Block II AGC, LGC (lunar module guidance computer), and CMC (command module computer).

As was stated previously, the need was evident for an increased capability in both the fixed and erasable memories over the Block I computer. There were two major reasons for this: one was the experience gained with mission-related programs for Block I, and the other was the identification of new functions for the BLOCK II system, including the ambitious digital autopilot function. Both memory expansions were accommodated with a moderate impact on existing designs. The braid memory, a new form of fixed memory with some similarities to the rope memory but with several potential advantages, was under development for possible inclusion into the Block II computer. But, because braid development was not sufficiently fast for the Block II schedule, the rope memory was retained, with an increase in capacity from 24,596 words to a total of 36,864, a factor of 1.5 over Block I. This was made possible by increasing the number of sense lines in each module. The mechanical design of the rope modules and computer was changed to allow rope removal and insertion without removing the computer from the spacecraft or breaking any connections other than those of the rope modules themselves.

The erasable memory capacity was doubled to 2048 words. This increase was made with a small increase in driving circuitry, twice the number of cores, and an overall volume reduction owing to more efficient space usage and the use of smaller driving transistors.

In the logic design area, the number of input/output operations was greater than in Block I, and the overall speed requirement was similarly greater, both largely due to the incorporation of the autopilot function into the computer. The input/output requirement was met by adding a number of special circuits for such interfaces as the radar and hand controller, and increasing the number of interface circuits used in Block I, such as counter (memory cycle stealing) inputs, and discrete inputs and outputs. The speed requirement was met by reducing the number of memory cycles required to perform some of the instructions and expanding the instruction repertoire. In order to conserve power, the logic circuitry was made slightly slower in the

۰,

à,

.

.

Block II design because of a change to low power integrated circuit logic. The number of instructions was increased from 11 to 34 to include more flexible branching and data handling, some double-precision capability, and special input/output instructions. Some instructions, including multiply and divide, were made faster through the use of extra logic, particularly in the adder circuitry, where the time to propagate carries was reduced to about one-third its duration in Block I. As a result of these changes, the number of gates rose about 1400, from about 4300 to approximately 5700.

Improvements in integrated circuit technology led to the adoption of the new low power NOR gate for the Block II computer. Though still a modified DCTL three-input gate, this circuit dissipated less than half the power of the Block I gate. Additionally, two of these gates were made on a single silicon chip and mounted in a 10-lead "flatpack" container. This resulted in doubling the packaging density relative to the Block I approach. The power reduction was obtained in these logic units by increasing the output impedance, resulting in an increased rise-time sensitivity to stray wiring capacitances. Two steps were taken to permit the use of the new device and effect a saving in power: one, multilayer etched boards were adopted as the means of interconnection within modules in place of the welded ribbon matrices, the change decreased the stray capacitance, and two, the clock timing circuit was improved to accommodate greater uncertainties in signal propagation delays.

The Block II computer design resulting from the change in technology roughly doubled the speed, raised between 1.5 and 2 times the memory capacity, increased input/ output capability, decreased size, and decreased power consumption. The Block II DSKY was similarly redesigned. The functional characteristics of the DSKY were essentially unchanged. The new design that resulted was mainly a smaller mechanical envelope, that was the same for the three locations: two in the command module and one in the lunar module. Additionally, the Block II computer and DSKY were constrained by new mechanical requirements such as the environmental seal on all connectors or modules that could be subjected to, and damaged by, the high moisture content of the spacecraft.

The mechanical design concepts, derived from experience with welded cordwood construction and other construction techniques, were applied very successfully to the packaging of the POLARIS guidance system and guidance computer. The major APOLLO mission requirements that had significant impact on the early configurations were: the requirements for inflight repair, for mounting on the spacecraft cold plate structure, and for the spacecraft cabling interface. This resulted in a configuration having modular construction and removable trays. Refer to Figure 1-5. The housing also contained a tray with spare modules.

13

۰.

Fig. 1-6 Block 0 Computer

Fig. 1-7 Dual Computer Model

Various mechanical and thermal interface problems dictated a change in configuration to what became the Block 0 computer shown in Figure 1-6. The early production computers were of this configuration. The mechanical design was not stabilized, however, until the requirement for inflight repair yielded to the more important requirement for moisture proofing. This in turn led to a significant change in mechanical configuration using the same module designs that were used in Block 0. Figure 1-7 is a photograph of the design resulting from moisture proofing. This was the final Block I mechanical configuration for the computer and DSKYs.

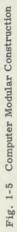

Before the inflight repair requirement was deleted, there were a series of mechanical designs, coupled with studies, to determine the feasibility of fault isolation in flight or the feasibility of dual computer operation with manual switchover. Figure 1-8 is a mockup of one version that provided one complete set of spare trays. If the problems of switchover could be solved, the spare trays could be interconnected in a dual operating mode. The configuration, shown in Figure 1-6, is the only version of this general configuration that was built with space for two spare trays mounted beside the two active trays. Other constraints on this design included: the right-hand tray containing cabling to interconnect the computer with the rest of the GN&C system through the top and with the spacecraft cabling through the front connectors, and the "thermal fuzz" material to provide heat transfer to the spacecraft cold plate. The change to the final Block I design (Figure 1-7) was accomplished after the requirement for spares and "thermal fuzz" were eliminated.

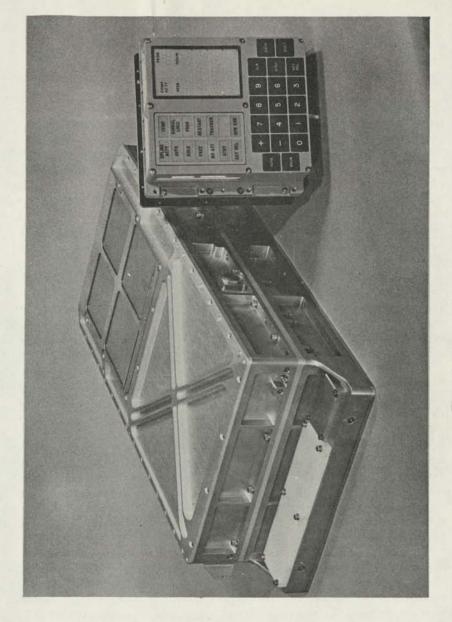

The increased functional requirements resulting in the Block II design, discussed earlier, also resulted in a new mechanical design. The resulting design of computer and DSKY is illustrated in Figure 1-9. This was a complete mechanical redesign: the end product was not only smaller and lighter than Block I, but also provided better environmental sealing, easy access to fixed memory for replacement in the spacecraft, and commonality between the lunar and command module mounting. Internally, the same type of modular construction was used as in the Block I version.

### 1.2 INITIAL DECISIONS

Many of the initial decisions surrounding the computer development could be easily categorized by the single statement that the task was seriously underestimated. The realization that reliability, weight, volume, and power consumption would be critical factors governing the success of the missions made for a limited view of the computational requirements. The result was excessive emphasis on minimizing the functional capacity of the computer. In addition, program costs, scheduling requirements, and the state-of-the-art of components constrained the initial

Fig. 1-8 Block I Computer and DSKYs

t

Fig. 1-9 Block II Computer and DSKY

considerations for adequate functional capacity. Also, in the light of the early limited knowledge of the mission requirements, it would have been impossible to justify a computer with the capacity and features of the Block II configuration.

Power, weight, and volume factors were prime considerations in determining word length, memory size, instructions, and interfaces. A word length of 15 bits, for example, was considered sufficient for most arithmetic and control operations. Double-precision computation (28 bits) was sufficient to provide the accuracy for navigation computations. Memory size necessitated consideration of memory type. For scratch pad memories, the only suitable candidate was the coincident-current ferrite-core type, and since these were costly in terms of power consumption and volume, it was important to minimize both the number and length of words. The problem of size and power consumption, as well as the reliability of data storage. was strong justification for using a fixed memory and resulted in the proposal for a wired rope type memory. An erasable capacity of 512 words was considered very marginal; therefore, the capacity was increased to 1024 words very early in the design process. The design philosophy of limited capacity was followed by the use of a minimum number of simple instructions, a limited interface capacity, as well as a limited memory capacity. This philosophy was a logical balance between computing capacity, the computer's mechanical limitations and component state-ofthe-art.

In consideration of the control and display capability, there was a great deal of interest in an oscilloscope-type display subsystem, but the complexity of the electronics and the complexity of the computer required to format the data were sufficient to eliminate this concept. An alternative approach resulted in the DSKY design that was considered an absolute minimum for the lunar mission. Other spacecraft display and control interfaces with the computer were ruled out in Block I design for various reasons. Typically, they involved the whole question of reliable operation of a digital computer. The philosophy of limited control and display through the computer restricted the flexibility of the GN&C system. While the Block II design provided expansion in the control and display area, even this later configuration was limited by these earlier decisions.

One of the major early decisions, that greatly influenced design and computer operation, was the provision for inflight repair. To some extent, this decision affected the design of both the display hardware and software, since inflight repair implies the ability to detect and diagnose a failure. Inflight repair was later eliminated as a requirement, but the failure detection and software restart capability remained. Additional decisions, considered to be major contributions to the success of the program, were as follows:

- 1. Hardware provisions for an interrupt structure, with software containing an executive, wait list, and an interpreter to aid real-time computation for guidance and control.

- 2. Hardware provisions for a limited but powerful instruction set, 1's complement arithmetic, and the ability to perform multiple precision arithmetic simply.

- Hardware provisions for uplink, downlink, and compatible onboard displays for relatively simple man-machine communications, both onboard and on the ground.

- Emphasis upon "make it right" to obtain reliability, rather than upon redundancy at the component level.

- Use of mechanical packaging techniques of proven manufacturability and reliability.

### 1.3 EXPANDING REQUIREMENTS

The following is a partial listing of mission type requirements that had an impact on computer designs. The time period during which the requirement was in a state of flux is indicated.

### 1.3.1 Memory Size (1962 to 1969)

During the entire program there was concern over the limited memory size. The debate included the ratio between fixed and erasable memory. At various points in time during the software development there were requests for expansion of the fixed memory. At other times the request was to expand the erasable memory. There was continuous evaluation of the hardware and supporting hardware developments designed to expand either fixed or erasable. Partially due to the lack of a firm requirement for expansion in memory but also due to the available memory technology, there were very few attempts to expand the memory beyond the Block II capacity. The latest design exercises occurred in early 1969 with a proposed expansion of the erasable memory from 2K to 16K words. The proposal was rejected because of insufficient justification. This was the only proposed increase in memory since the changes introduced in the Block II design, but it was fairly clear that the requirement for the additional memory was not firm enough to justify the change. The other changes in memory size came early enough in the development to make the justification somewhat simpler. In general, the memory sizing was determined

more by what the hardware technology could provide rather than a requirement established for the mission.

### 1.3.2 Implementation Meetings - 1964

This was a series of meetings between MSC, MIT, and the two spacecraft contractors which were to determine the system requirements. The output of these meetings resulted in the determination of many new computer requirements that lead to the change from Block I to II. The major changes affecting the computer were expanded functional requirements such as the digital autopilot, increased mode control, definition of radar interface, hand controller interfaces, hermetic packages for moisture-proofing, compatible lighting between spacecraft and DSKY, and other human factor requirements.

These new requirements justified the increase in memory size, increase in interface capacity, increase in overall functional capability, and the introduction of the constraints on the DSKY that lead to the Block II universal design.

Another result of the implementation meetings was a definition of the philosophy for guidance system backup and redundancy. This philosophy provided for operating modes with independent means for guidance and control if the guidance system failed. In the case of the command module, the ground control would provide the capability of safe return to earth and, in the case of the lunar module, there was a separate guidance system to provide abort capability. With these guidance backup modes it was no longer necessary to have inflight repair or a redundant computer in order to meet the crew safety requirements of guidance. The relaxation of the requirement to provide backup to the computer within the guidance system, and the introduction of moisture-proofing provided a definite guide to mechanical configuration of the Block II.

1.3.3 Weight Savings (1962 to 1965)

A concerted effort to save weight was instrumental in initiating many design studies that resulted in changing the Block II computer frame design from aluminum to magnesium. The design change saved about 12 pounds. In parallel with, and partially resulting from the change to magnesium, was an increased concern about materials in general. The magnesium required a corrosive-resistant finish that would meet the contamination and corrosion-resistance requirements of the spacecraft.

# 1.3.4 Electromagnetic Interference Specifications - 1963

The contract requirement for the system to meet EMI specifications was added late in 1963. The Block I design at that point was well along and had considered some of the requirements. It was quite well known that a strict interpretation of the requirements could not be met by the computer. After the specification was added as a contractual requirement, the design impact was evaluated, and Block II was designed to meet or exceed the requirements. Since digital computers are quite susceptible to errors induced by external electromagnetic interference, both designs had features which would reduce the sensitivity to interference.

#### 1.3.5 Fire Proofing - 1967

The requirement to investigate and fire-proof the system resulted from the APOLLO 4 accident. This added a new dimension to the materials problem but had no impact on the computer design. The DSKY design was changed to provide a cover for the alarm panel and fire proof caps on the keys, since the material in the panel and key caps were flammable.

# SECTION 2.0 COMPUTER SYSTEM DESCRIPTION

### 2.1 INTRODUCTION

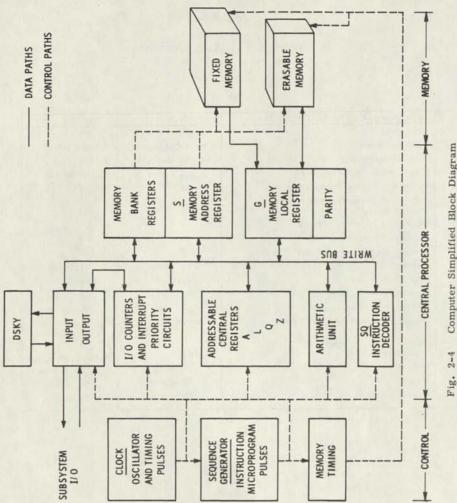

The computer subsystem is the control and processing center of the guidance, navigation and control system. It processes data and issues discrete output and control pulses to the guidance system and other spacecraft systems. Functionally, the computer subsystem consists of the APOLLO guidance computer (AGC) and the display and keyboard unit (DSKY). The computer is a parallel digital real time control computer with many features of a general purpose computer. As a control computer, some of the major control functions are: alignment of the inertial measurement unit, processing of radar data, management of astronaut display and controls and generation of commands for spacecraft engine control. As a general purpose computer, the AGC solves the guidance and navigation equations required for the lunar mission.

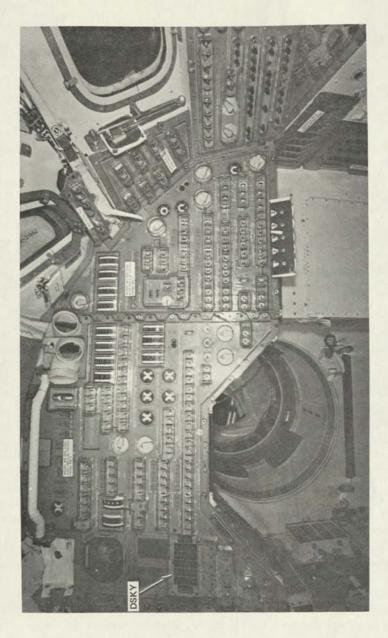

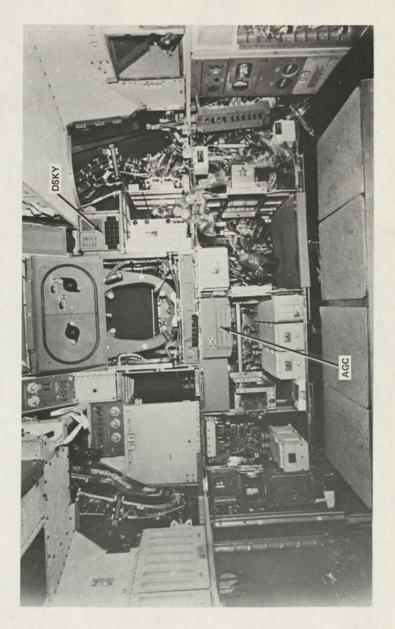

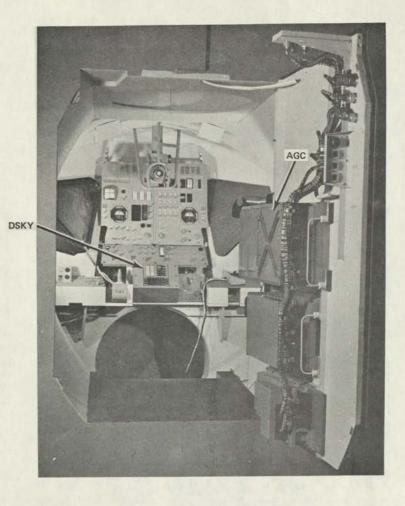

An operational APOLLO spacecraft contains two guidance computers and three DSKYs, with one computer in the command module, and one in the lunar module. The computers are electrically identical, but differ in the use of computer software. There are two DSKY units in the command module, a DSKY mounted on the main display and control panel and a DSKY in the lower equipment bay at the navigation station. (See Figures 2-1 and 2-2). The lunar module has a single DSKY unit. (See Figure 2-3). In this chapter, because it is concerned primarily with the hardware aspects of the APOLLO guidance computer, no distinction is made between the command module and lunar module computers, except where significant operational differences exist. References to the "APOLLO guidance computer", the "computer", and the "AGC" are equivalent in meaning. Other project APOLLO documentation may refer to the command module computer (CMC), the lunar module computer (LGC). These designations are not used in this report unless specifically defined.

Section 1.0 described the evolution of the Block II AGC configuration through a series of technological developments, including the Block I prototype design, and also examination of the requirements. Since the Block II design was the only configuration used for manned operational flights, the following functional description concentrates on the Block II configuration, but identifies the more significant functional differences in the Block I design. The Block II DSKY was functionally equivalent but mechanically different from Block I. Table 2-I compares the functional characteristics of the two computers.

Fig. 2-1 CM Main Display and Control Panel

Fig. 2-2 CM Lower Equipment Bay

Fig. 2-3 LM Display and Control Panel

# TABLE 2-I

# COMPUTER CHARACTERISTICS

| PERFORMANCE CHARACTERISTICS                                        | BLOCK I                       | BLOCK II          |

|--------------------------------------------------------------------|-------------------------------|-------------------|

| Word Length                                                        | 15 Bits + Parity              | 15 Bits + Parity  |

| Number System                                                      | One's Complement              | One's Complement  |

| Fixed Memory Registers                                             | 24,576 Words                  | 36, 864 Words     |

| Erasable Memory Registers                                          | 1,024 Words                   | 2,048 Words       |

| Number of Normal Instructions                                      | 11                            | 34                |