ND-1021042

# PROJECT

LUNAR EXCURSION MODULE

### PRIMARY GUIDANCE, NAVIGATION, AND CONTROL SYSTEM MANUAL

VOLUME II

ND-1021042 REV LETTER ON VOL I

## APOLLO

LUNAR EXCURSION MODULE

## PRIMARY GUIDANCE, NAVIGATION, AND CONTROL SYSTEM MANUAL

VOLUME II OF II

PREPARED FOR

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION MANNED SPACECRAFT CENTER

BY

AC ELECTRONICS DIVISION OF GENERAL MOTORS MILWAUKEE, WISCONSIN 53201

NASA CONTRACT NAS 9 - 497

#### ND-1021042

1 FEB 1966

REVISION AK INITIAL TDRR 26432 TYPE II APPROVED BY NASA

APOLLO

. . .

LUNAR EXCURSION MODULE

### PRIMARY GUIDANCE, NAVIGATION, AND CONTROL SYSTEM MANUAL

**VOLUME | OF ||**

PREPARED FOR

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION MANNED SPACECRAFT CENTER

ΒY

DELCO ELECTRONICS DIVISION OF GENERAL MOTORS MILWAUKEE,WISCONSIN 53201

NASA CONTRACT NAS 9-497

And Annual and Annual and Annual and

| Rev | Dote     | TORR   | Pages Revised                   | Approvol |      |  |

|-----|----------|--------|---------------------------------|----------|------|--|

| Let | Dore     | Number | Fuges Revised                   | ССВ      | NASA |  |

| AC  | 7-25-68  | 36590  | Title/I-ii, I-ivK/I-ivL, I-vii  | EA 21)   |      |  |

|     |          |        | thru I-viiiB, I-ix thru I-xB,   |          |      |  |

|     |          |        | I-xii, I-xviii, I-xxxI/I-xxxJ,  |          |      |  |

|     |          |        | 3-2A thru 3-2C, 3-11 thru       |          |      |  |

|     |          |        | 3-12E, 4-437, 4-481/4-482,      |          |      |  |

|     |          |        | 4-539, 6-1, 6-2, 6-4, 7-13,     |          |      |  |

|     |          |        | 7-16, 7-16A/7-16B, 7-21/7-22,   |          |      |  |

|     |          |        | 8-14                            |          |      |  |

|     |          |        |                                 |          |      |  |

| AD  | 11-4-68  | 36977  | Title/I-ii, I-ivK/I-ivL, I-vii  | EA SUS   |      |  |

|     |          |        | thru I-viii, I-xB, I-xxxI thru  | Q        |      |  |

|     |          |        | I-xxxJ, 3-2A, 3-2L thru 3-2Q,   |          |      |  |

|     |          |        | 7-19/7-20, 7-21/7-22, 8-2,      |          |      |  |

|     |          |        | 8-6E, 8-7, 8-14 thru 8-15/8-16  |          |      |  |

| AE  | 12-16-68 | 37124  | Title/I-ii, I-ivK/I-ivL, I-vii, | EA BER   |      |  |

|     |          |        | I-viii, I-xxxJ, 3-2A, 3-2V,     |          |      |  |

|     |          |        | 3-2W                            |          |      |  |

|     |          |        |                                 |          |      |  |

| AF  | 1-20-69  | 37232  | Title/I-ii, I-ivK/I-ivL,I-vii,  | EA D     |      |  |

|     |          |        | I-xB, 7-16, 7-16A/7-16B,        | . (      |      |  |

|     |          |        | 8-8, 8-8A/8-8B                  |          |      |  |

|     |          |        |                                 |          |      |  |

| AG  | 8-11-69  | 37755  | Title/I-ii, 1-ivK/I-ivL, I-vii, | EA 2     |      |  |

|     |          |        | 1-viii, 1-xxxA, I-xxxG, I-xxxH, |          |      |  |

|     |          |        | I-xxxJ, 3-2A thru 3-2P,         |          |      |  |

|     |          |        | 3-2R thru 3-2U, 3-2W, 3-2X,     |          |      |  |

|     |          |        | 3-2Z                            |          |      |  |

#### Record of Revisions

Rev. AH

•

I-ivK

| Rev. | Dote    | TORR   |                                   | Appro | Approval |  |  |

|------|---------|--------|-----------------------------------|-------|----------|--|--|

| Let. | Dore    | Number | Fuges nevised                     | ССВ   | NASA     |  |  |

| AH   | 5-26-70 | 38111  | Title/I-ii, I-ivK, I-ivL, I-vii,  | EA KK |          |  |  |

|      |         |        | I-viii, I-xiii, I-xxv, I-xxxJ,    |       |          |  |  |

|      |         |        | 3-2A, 3-2L, 3-2L-1/3-2L-2,        |       |          |  |  |

|      |         |        | 3-2M, 3-22M, 3-22N                |       |          |  |  |

| AJ   | 8-5-71  | 38455  | Title/I-ii, I-ivL, I-vii, I-viii, | EA    |          |  |  |

|      |         |        | I-xxxJ, 3-2A, 3-2F, 3-2G,         |       |          |  |  |

|      |         |        | 3-2H, 3-2I                        |       |          |  |  |

| AK   | 7-6-72  | 38664  | Title/I-ii, I-ivL, I-vii, I-viii, | JS JA | 100      |  |  |

|      |         |        | I-xxxJ, 3-2A, 3-2V, 3-2W          |       |          |  |  |

|      |         |        |                                   |       |          |  |  |

|      |         |        |                                   |       |          |  |  |

|      |         |        |                                   |       |          |  |  |

|      |         |        |                                   |       |          |  |  |

|      |         |        |                                   |       |          |  |  |

|      |         |        |                                   |       |          |  |  |

|      |         |        |                                   |       |          |  |  |

|      |         |        |                                   |       |          |  |  |

|      |         |        |                                   |       |          |  |  |

|      |         |        |                                   |       |          |  |  |

|      |         |        |                                   |       |          |  |  |

|      |         |        |                                   |       |          |  |  |

|      |         |        |                                   |       |          |  |  |

|      |         |        |                                   |       |          |  |  |

|      |         |        |                                   |       |          |  |  |

|      |         |        |                                   |       |          |  |  |

#### Record of Revisions

.

#### LIST OF EFFECTIVE PAGES TOTAL NUMBER OF PAGES IN THIS PUBLICATION IS 1364 CONSISTING OF THE FOLLOWING:

Rev. AK

ND-1021042

#### LIST OF EFFECTIVE PAGES (cont)

| Page No.        | Rev.     | Page No.               | Rev.       |

|-----------------|----------|------------------------|------------|

| 2-42B Blank     | в        | 3-21 thru 3-22B        | AB         |

| 2-43            | В        | 3-22C thru 3-22L Added | AB         |

| 2-44 Blank      | Original | 3-22M thru 3-22N       | AH         |

| 2-45            | F        | 3-23                   | Original   |

| 2-46 thru 2-60  | Original | 3-24                   | AA         |

| 3-1 thru 3-2    | Н        | 3-24A thru 3-24D Added | . L        |

| 3-2A            | AK       | 3-25                   | W          |

| 3-2B thru 3-2E  | AG       | 3-26                   | . V        |

| 3-2F thru 3-2I  | AJ       | 3-26A Added            | V V        |

| 3-2J thru 3-2K  | AG       | 3-26B Blank            | • V        |

| 3-2L            | AH       | 3-27                   | . AA       |

| 3-2L-1 Added    | AH       | 3-28                   | F          |

| 3-2L-2 Added    | AH       | 3-29                   | . AA       |

| 3-2M            | AH       | 3-30                   | . В        |

| 3-2N thru 3-2P  | AG       | 4-1 thru 4-14          | . Original |

| 3-2Q            | AD       | 4-15                   | . W        |

| 3-2R thru 3-2U  | AG       | 4-16 thru 4-18         | . Original |

| 3-2V thru 3-2W  | AK       | 4-19                   | . Т        |

| 3-2X            | AG       | 4-20 thru 4-21         | . В        |

| 3-2Y            | Y        | 4-22                   | . Original |

| 3-2Z            | AG       | 4-23                   | . Т        |

| 3-2AA           | W        | 4-24 thru 4-25         | . Original |

| 3-2AB Blank     | K        | 4-26                   | . A        |

| 3-3             | J        | 4-27 thru 4-28         | . Original |

| 3-4             | M        | 4-29 thru 4-30         | . A        |

| 3-4A Added      | J        | 4-31                   | . Original |

| 3-4B Blank      | J        | 4-32 thru 4-34         | . A        |

| 3-5             | H        | 4-34A Added            | • A        |

| 3-6             | С        | 4-34B Blank            |            |

| 3-6A Added      | С        | 4-34C                  |            |

| 3-6B Blank      | С        | 4-34D Blank            |            |

| 3-7 thru 3-8    |          | 4-34E Added            |            |

| 3-9             | В        | 4-34F Blank            |            |

| 3-10            | н        | 4-34G thru 4-34I Added |            |

| 3-11 thru 3-12E | AC       | 4-34J Blank            |            |

| 3-12F           | V        | 4-34K Added            |            |

| 3-13            | Original | 4-34L Blank            | • A        |

| 3-14            | В        | 4-34M thru 4-34O Added |            |

| 3-15            | С        | 4-34P Blank            | • A        |

| 3-16            |          | 4-34Q thru 4-34S Added | . A        |

| 3-17            | F        | 4-34T Blank            | • A        |

| 3-18 thru 3-19  | В        | 4-34U Added            | . A        |

| 3-20            | AA       | 4-34V Blank            | . A        |

| ariii           |          |                        | Rev. AK    |

I-viii

Rev. AK

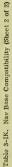

#### LIST OF ENGINEERING CHANGE PROPOSALS (cont)

| ECP No.       | Functional Description                                                       | Retrofit<br>Instruction<br>Bulletin (RIB) No. | Kit<br>No.                               | Incorporated<br>In Manual<br>Revision |

|---------------|------------------------------------------------------------------------------|-----------------------------------------------|------------------------------------------|---------------------------------------|

| 564           | Implementation of Flat Pack<br>Specifications ND 1002359A<br>and ND 1002358B |                                               |                                          | U                                     |

| 631           | RepIace RTV-102 with<br>RTV-109                                              | 0102679<br>0102689<br>0102690                 | 8102752<br>8102755<br>8102754<br>8102766 | U                                     |

| 653           | Modification of IMU Wiring<br>to Reduce IRIG Pre-Amp<br>Oscillation          |                                               | 8102763                                  | U                                     |

| 641           | Non-metallic Materials<br>Modification for DSKY                              | 0104126                                       | 8104241                                  | W                                     |

| 655           | New LGC Mounting Bolts<br>and Spacers                                        |                                               |                                          | W                                     |

| 673           | Redesign of DSKY Push-<br>button Cap Housing<br>Assembly Leaf Spring         | 0104126                                       | 8104241                                  | W                                     |

| 678           | IRIG End Cap Change                                                          | 0102697                                       | $8102767 \\ 8102768$                     | W                                     |

| 633           | AOT Pressure Seal Protec-<br>tion and Other Flammability<br>Fixes            | 0106049<br>0106048                            | 8106069<br>8106073                       | Y                                     |

| 604           | Incorporation of E-memory<br>Vibration Pads                                  |                                               |                                          | Z                                     |

| 688           | Modification of IMU to<br>Reduce Sporadic Oscillation<br>of IRIG Preamps     |                                               | $8102773 \\ 8102774$                     | Z                                     |

| 657           | Conical Sunshade and Radar<br>Shield Assembly for AOT                        | 0106050                                       | 8106076                                  | AC                                    |

| 697<br>Rev. Z | AOT Harness Protective<br>Shield                                             | 0106054                                       | 8106085                                  | AC<br>I <del>-</del> xxxl             |

#### LIST OF ENGINEERING CHANGE PROPOSALS (cont)

| ECP No.     | Functional Description                                                                                        | Retrofit<br>Instruction<br>Bulletin (RIB) No. | Kit<br>No. | Incorporated<br>In Manual<br>Revision |

|-------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------|---------------------------------------|

| 719         | Computer Alarm Module<br>Modification, V-Fail<br>Detection                                                    | 0104132                                       | 8104248    | AD                                    |

| 735         | DSKY 1L and EL Safety<br>Glass Fix                                                                            | 0104135                                       | 8104251    | AD                                    |

| 743         | New Configuration of<br>Installation Kit                                                                      |                                               |            | AD                                    |

| 757         | Design Changes to<br>Correct LEM PSA<br>Reverse Power<br>Problem                                              |                                               |            | AE                                    |

| 768         | DSKY EL thermal/<br>Vacuum Screen modification                                                                | 0104138                                       | 8103954    | AG                                    |

| 739         | Addition of 4 lights on<br>DSKY indicator panel                                                               | 0104136                                       | 8103952    | AG                                    |

| 780         | Taping of AOT cable                                                                                           |                                               |            | AG                                    |

| 781         | ECDU mounting bolt<br>change in length                                                                        | 0102703                                       | 8102789    | AG                                    |

| 815         | Replace AGC Connector<br>Assembly with a restart<br>monitor                                                   | 0102705                                       | 8102793    | AH                                    |

| 1017 & 1032 | Replace blower motor in<br>IMU to increase reliability                                                        | -                                             | 8102796    | AJ                                    |

| 1030        | Replace ECDU modules con-<br>taining 1010274 transformers<br>to increase reliability                          | -                                             | -          | AJ                                    |

| 1040        | Modification of 800 Hz 5%<br>amplifier in PSA to eliminate<br>amplifier oscillation during<br>system turn-on. | -                                             | -          | AK                                    |

Rev. AK

•

#### CONTENTS

| Chapter  |        |                                                     | Volume II                                                                                | Page                     |

|----------|--------|-----------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------|

| 4 (cont) |        | 4-5.5<br>4-5.6<br>4-5.7<br>4-5.8<br>4-5.9<br>4-5.10 | Central Processor                                                                        |                          |

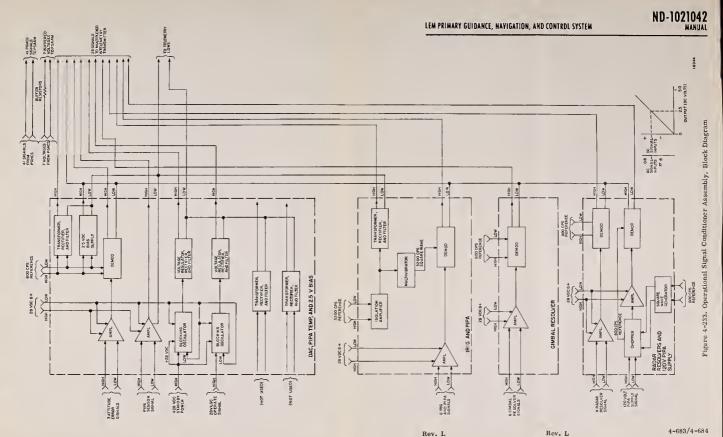

|          | 4-6    | Signal Co                                           | nditioner Assembly                                                                       | 4-675                    |

|          |        | 4-6.1<br>4-6.2<br>4-6.3                             | Signal Conditioner Modules<br>Signal Conditioning Circuits<br>Reference Voltage Circuits | 4 - 676                  |

|          | 4-7    | Deleted                                             |                                                                                          |                          |

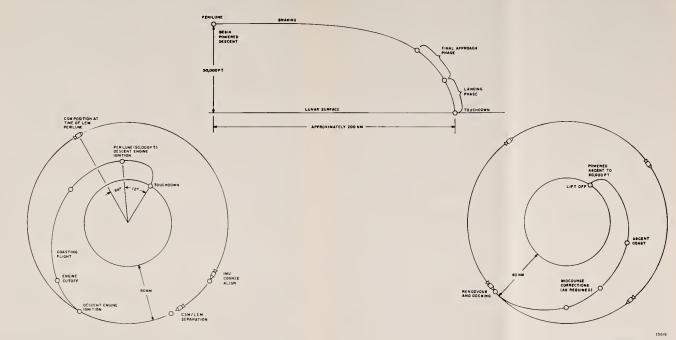

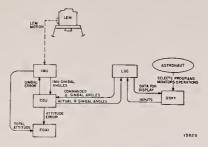

| 5        | MISSIC | ON OPERA                                            | TIONS                                                                                    | 5-1                      |

|          | 5-1    | Scope                                               |                                                                                          | 5-1                      |

|          | 5+2    | IMU Coar                                            | se Alignment                                                                             | 5-1                      |

|          | 5-3    | IMU Fine                                            | Alignment                                                                                | 5-1                      |

|          | 5-4    | Transfer                                            | Orbit                                                                                    | 5-2                      |

|          | 5-5    | Powered 1<br>5-5.1<br>5-5.2<br>5-5.3                | Descent<br>Phase I - Braking<br>Phase II - Final Approach<br>Phase III - Landing         | 5-2<br>5-2<br>5-2<br>5-7 |

|          | 5-6    | Lunar Sta                                           | y                                                                                        | 5-7                      |

|          | 5-7    | Ascent                                              |                                                                                          | 5-7                      |

|          | 5-8    | Rendezvo                                            | us and Docking                                                                           | 5-7                      |

| 6        | CHEC   | KOUT AND                                            | MAINTENANCE EQUIPMENT                                                                    | 6-1                      |

|          | 6-1    | Scope                                               |                                                                                          | 6-1                      |

| 7        | CHEC   | KOUT                                                |                                                                                          | 7-1                      |

|          | 7-1    | Scope                                               |                                                                                          | 7-1                      |

|          | 7-2    | Primary (<br>7-2.1<br>7-2.2<br>7-2.3                | Guidance, Navigation, and Control System<br>Preparation<br>Checkout<br>Test Descriptions | 7-1<br>7-1<br>7-1<br>7-1 |

•

9

II-iii

#### CONTENTS (cont)

| Chapter |                                                        | Page                                                                                                                                                                                                                                                                                                                                                                          |

|---------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 7-3                                                    | Inertial Subsystem                                                                                                                                                                                                                                                                                                                                                            |

|         | 7-4                                                    | Computer Subsystem         .7-2L           7-4.1         Preparation         .7-2L           7-4.2         Checkout         .7-2L                                                                                                                                                                                                                                             |

|         | 7-5                                                    | Alignment Optical Telescope         .7-2L           7-5.1         Preparation         .7-2L           7-5.2         Checkout         .7-2L                                                                                                                                                                                                                                    |

|         | 7-6                                                    | Signal Conditioner Assembly.         .7-2L           7-6.1         Preparation         .7-2L           7-6.2         Checkout         .7-2L                                                                                                                                                                                                                                   |

| 8       | MAIN                                                   | TENANCE                                                                                                                                                                                                                                                                                                                                                                       |

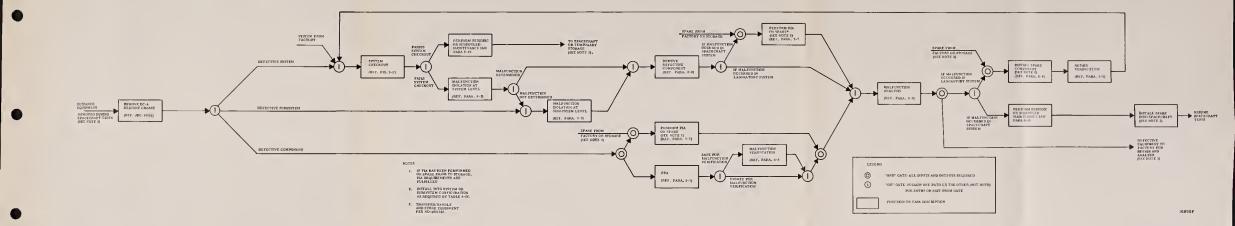

|         | 8-1<br>8-2<br>8-3                                      | Scope       8-1         Maintenance Concept       8-1         Malfunction Isolation-Analysis       8-2         8-3.1       Electrical Adapter Cable Assembly Set       8-2         8-3.2       Arrangement of ND-1021040 Supplement B       8-2A         8-3.3       Test Point Signal Characteristics       8-2B         8-3.4       CSS Malfunction Isolation       8-2B    |

|         | 8-4<br>8~5<br>8-6<br>8-7<br>8-8<br>8-9<br>8-10<br>8-11 | Removal and Replacement         8-2B           Repair Verification         8-2B           Pre-Installation Acceptance         8-9           Pre-Power Assurance         8-13           Malfunction Verification         8-13           Malfunction Analysis         8-14           Maintenance Schedule         8-14           Auxiliary Airborne Equipment         8-15/8-16 |

| APPENDI | X A                                                    | LIST OF TECHNICAL TERMS AND ABBREVIATIONS $\hfill \hfill A-1$                                                                                                                                                                                                                                                                                                                 |

| APPENDI | хв                                                     | RELATED DOCUMENTATION B-I/B-2                                                                                                                                                                                                                                                                                                                                                 |

| APPENDI | хс                                                     | LOGIC SYMBOLS                                                                                                                                                                                                                                                                                                                                                                 |

•

#### ILLUSTRATIONS

Figure

8

•

Page

#### Volume II

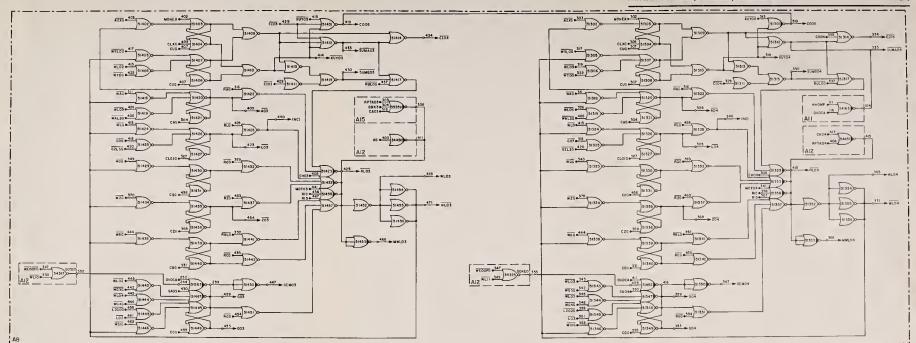

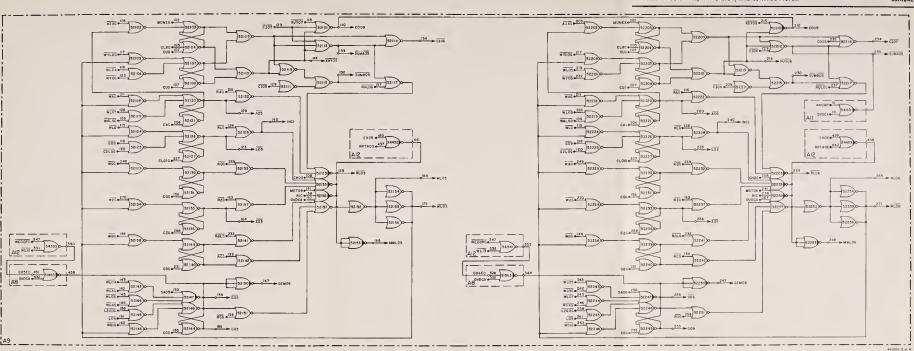

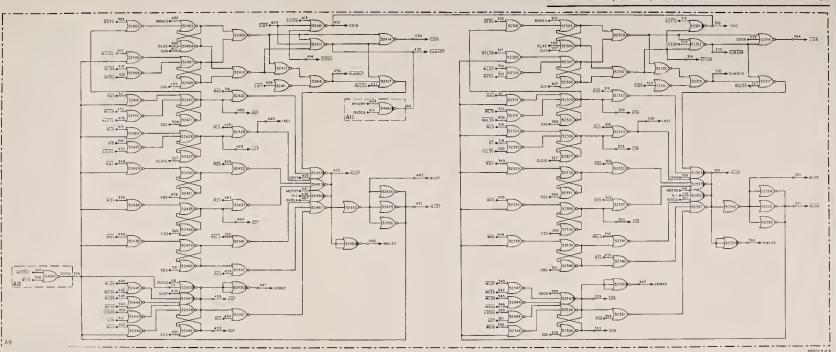

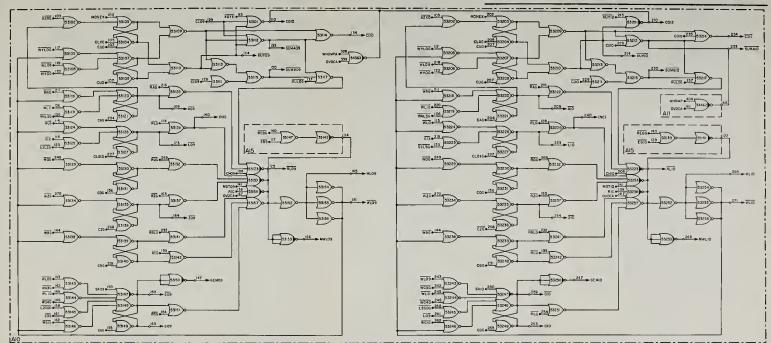

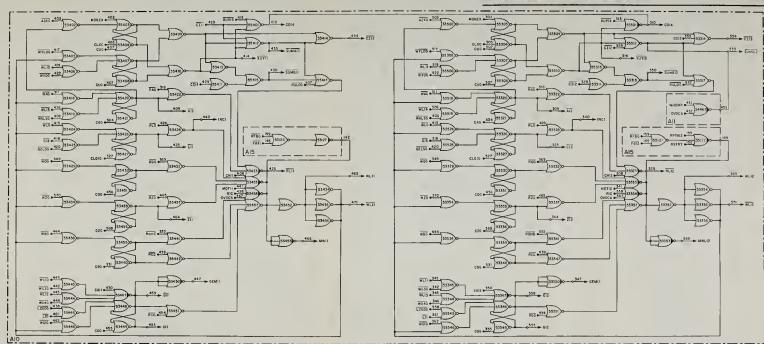

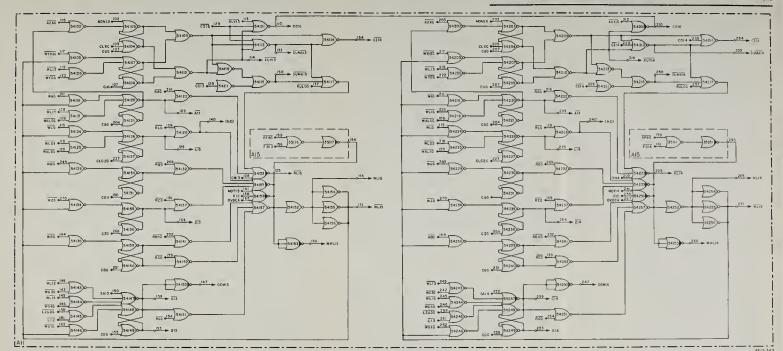

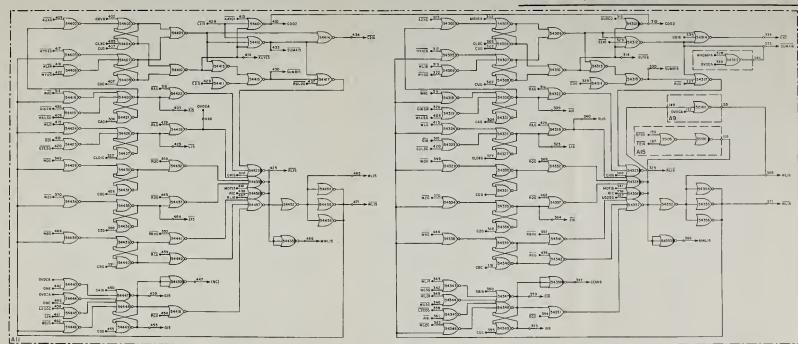

| 4-125  | Order Code Processor, Block Diagram                | 4-233         |

|--------|----------------------------------------------------|---------------|

| 4-126  | Command Generator, Block Diagram                   | 4-235         |

| 4-127  | Control Pulse Generator, Block Diagram             | 4-236         |

| 4-128  | Register SQ Control, Logic Diagram                 | 4-239/4-240   |

| 4-129  | Register SQ and Decoder, Logic Diagram             | 4-243/4-244   |

| 4-120  | Stage Counter and Decoder, Logic Diagram           | 4-247/4-248   |

| 4-131  | Subinstruction Decoder, Logic Diagram              | 4-257/4-258   |

| 4-131  | Instruction Decoder, Logic Diagram                 | 4-269/4-270   |

| 4-132  | Counter and Peripheral Instruction Control Logic   | 4-273/4-274   |

| 4-134  | Crosspoint Generator, Logic Diagram                | 4-281/4-282   |

| 4-134  | Control Pulse Gates, Logic Diagram                 | 4-351         |

| 4-136  | Branch Control, Logic Diagram                      | 4-359/4-360   |

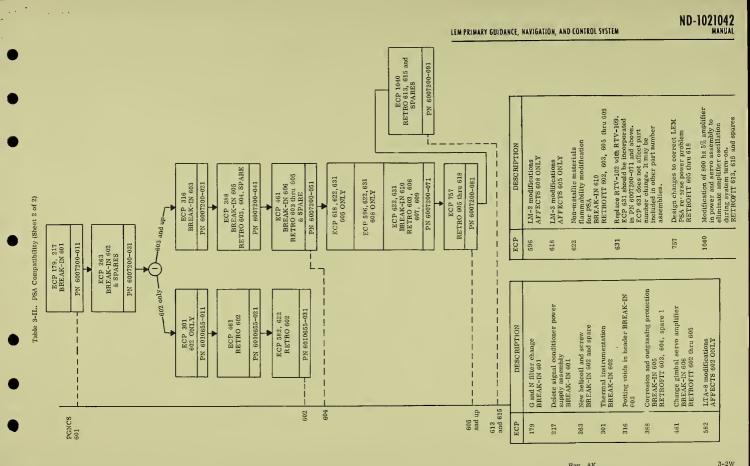

| 4-137  | Word Formats                                       | 4-366         |

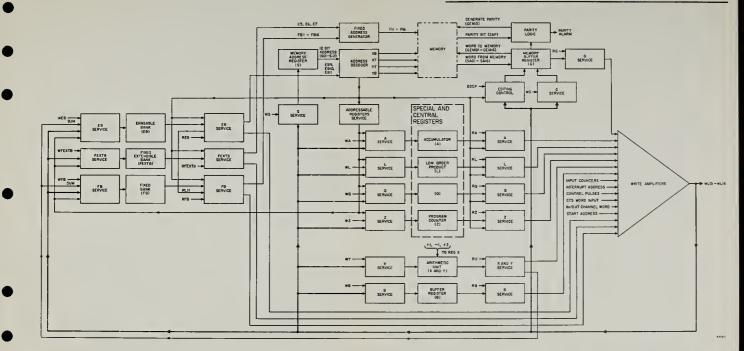

| 4-138  | Central Processor, Functional Diagram.             | 4-368A/4-368B |

| 4-138A | Data Flow to Erasable, Fixed, and Fixed Extendible |               |

| 4-1001 | Registers                                          | 4-368C/4-368D |

| 4-138B | Data Flow from Erasable, Fixed, and Fixed          |               |

| 4-130D | Extendible Registers                               | 4-369         |

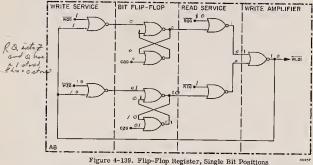

| 4-139  | Flip-Flop Register, Single Bit Positions           | 4-370         |

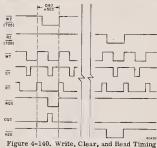

| 4-140  | Write, Clear, and Read Timing                      | 4-372         |

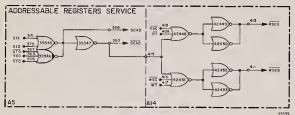

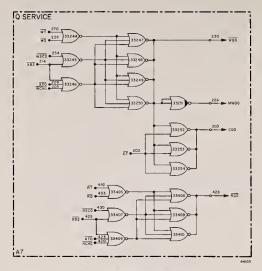

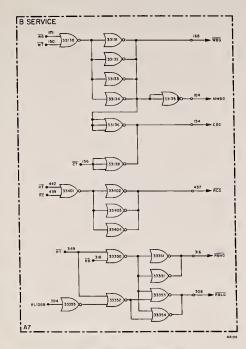

| 4-141  | Addressable Registers Service                      | 4-373/4-374   |

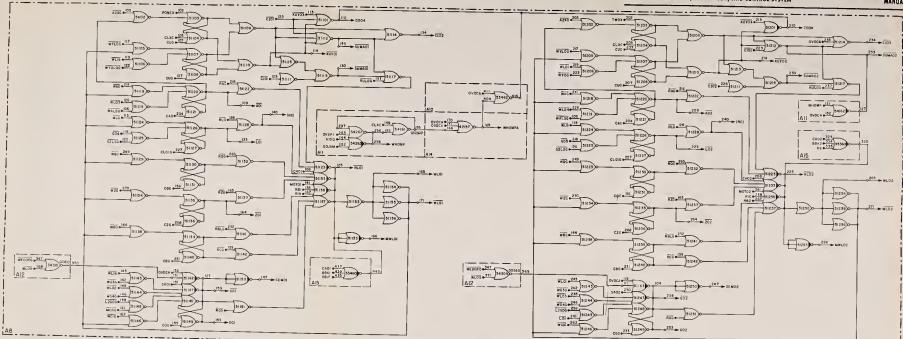

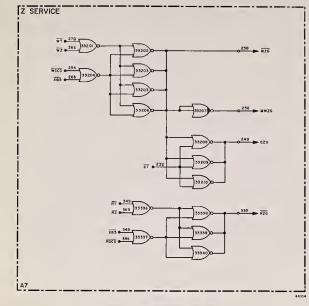

| 4-142  | Flip-Flop Registers                                | 4-375/4-376   |

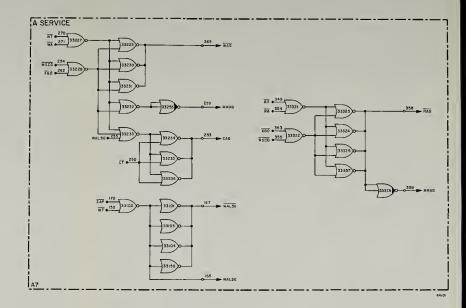

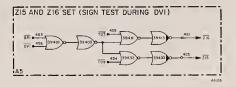

| 4-143  | Register A Service                                 | 4-391/4-392   |

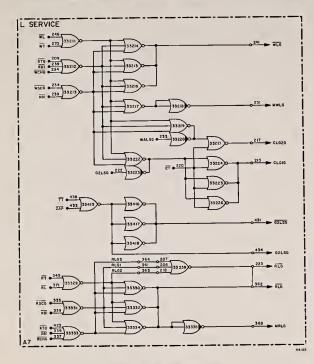

| 4-144  | Register I. Service                                | 4-395         |

| 4-145  | Register Q Service                                 | 4-396         |

| 4-146  | Register Z Service                                 | 4-397         |

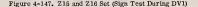

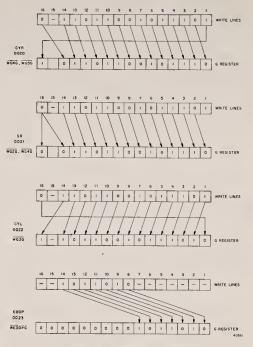

| 4-147  | Z 15 and Z 16 Set (Sign Test During DV 1)          | 4-398         |

| 4-148  | Register B Service                                 | 4-399         |

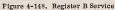

| 4-149  | Register G Service                                 | 4-401/4-402   |

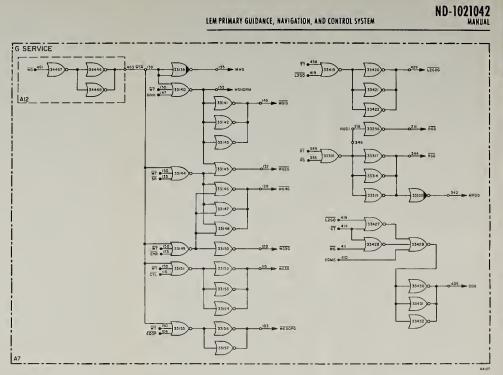

| 4-150  | Editing Control                                    | 4-403         |

| 4-151  | Editing Transformations                            | 4-404         |

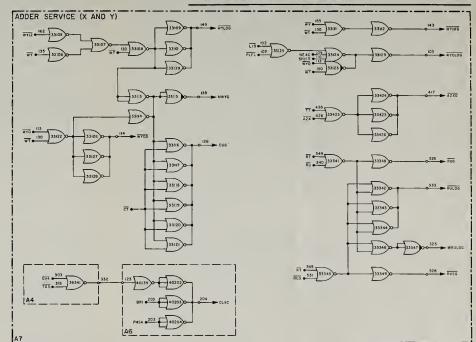

| 4-152  | Adder Service (Registers X and Y)                  | 4-409/4-410   |

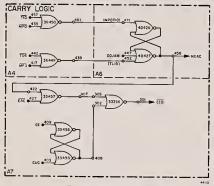

| 4-153  | Carry Logic                                        | 4-411         |

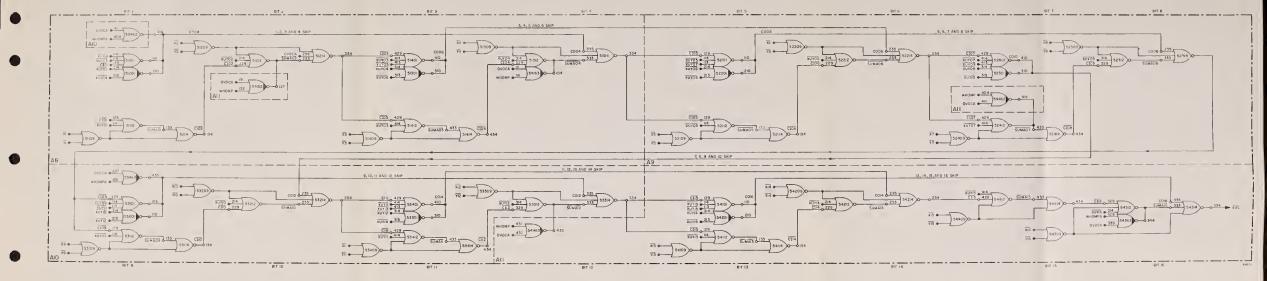

| 4-153A | Adder Carry-Propagate and Carry Skip Chains        | 4-412A/4-412B |

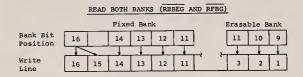

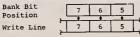

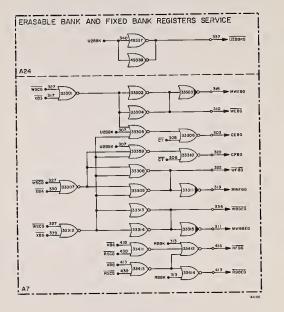

| 4-153B | Erasable and Fixed Bank Registers Services         | 4-412D        |

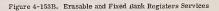

| 4-153C | Erasable Bank, Fixed Bank, and Fixed Bank          |               |

|        | Extendible Registers                               | 4-412G/4-412H |

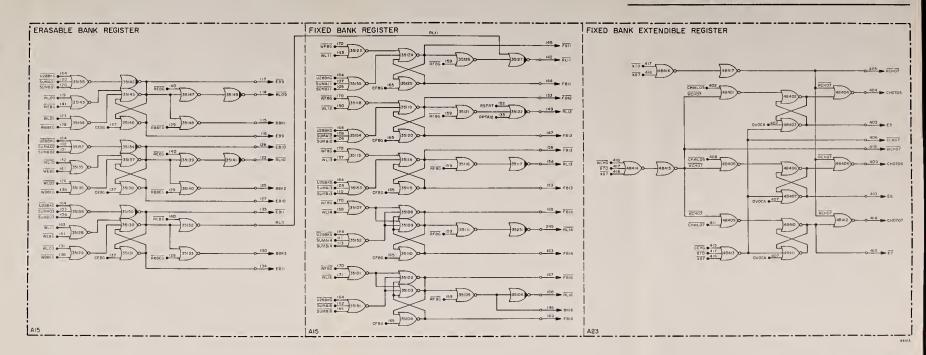

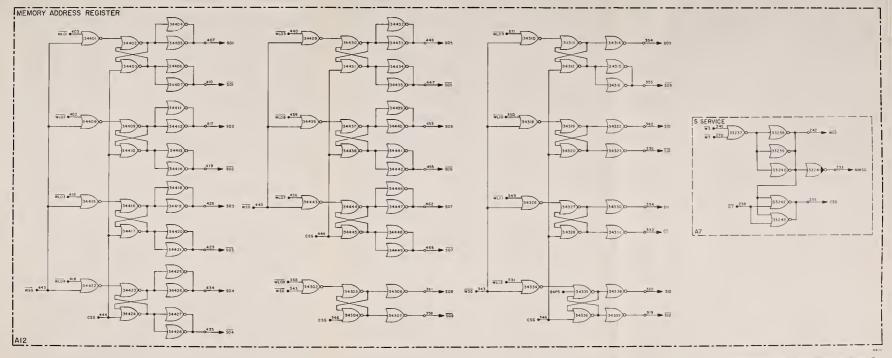

| 4-154  | Memory Address Register (S)                        | 4-417/4-418   |

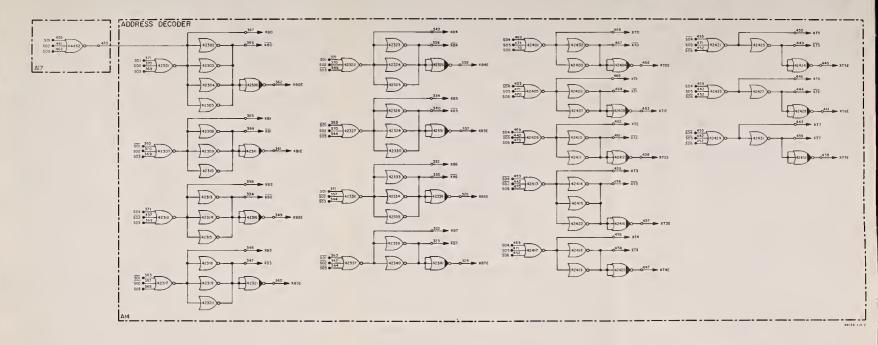

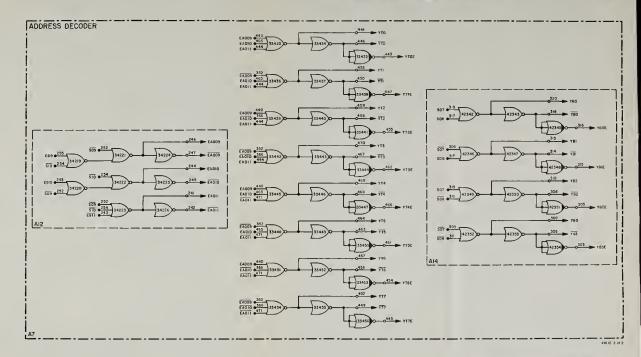

| 4-155  | Address Decoder                                    | 4-421/4-422   |

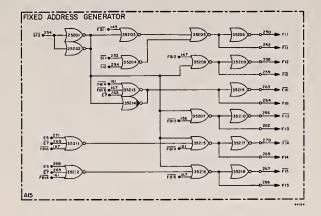

| 4-155A | Fixed Address Generator                            | 4-424A/4-424B |

ND-1021042

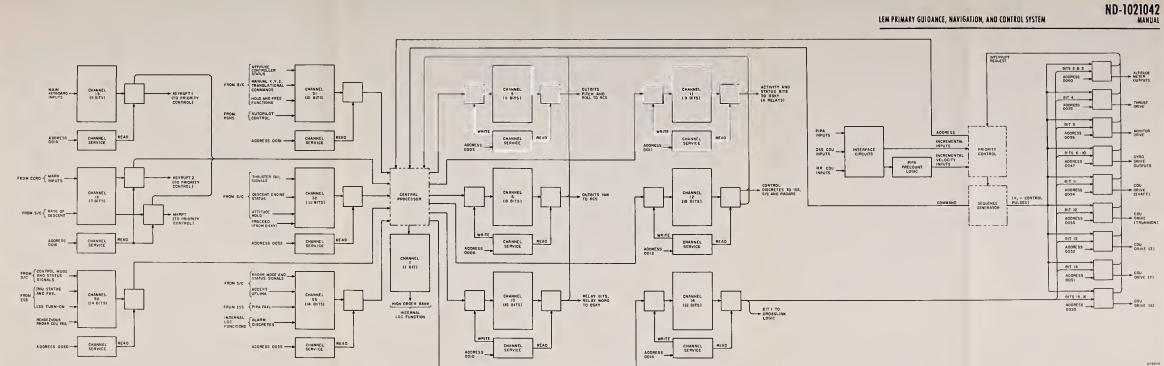

LEM PRIMARY GUIDANCE, NAVIGATION, AND CONTROL SYSTEM

#### ILLUSTRATIONS (cont)

#### Figure

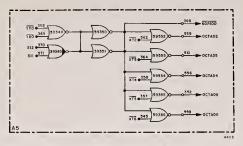

| 4-156   | Counter Address Signals                                 | 4-427       |

|---------|---------------------------------------------------------|-------------|

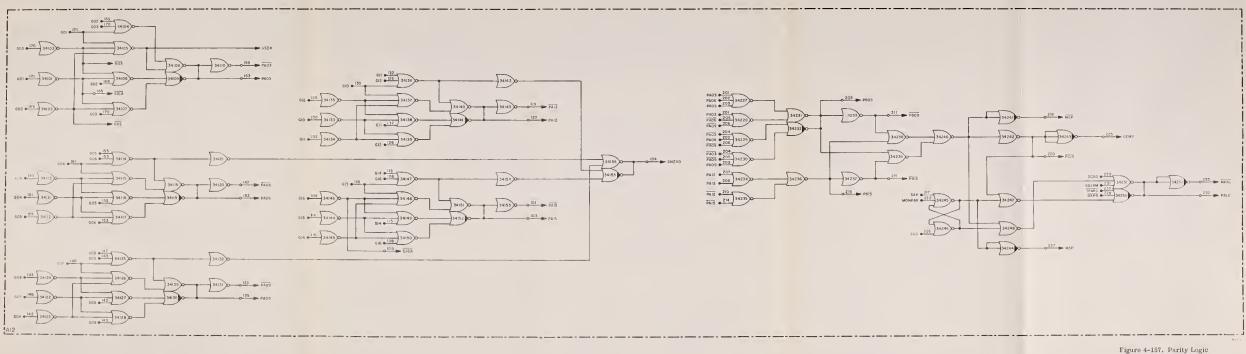

| 4-157   | Parity Logic                                            | 4-429/4-430 |

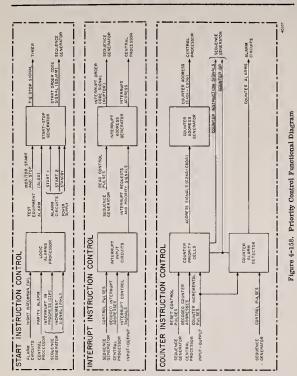

| 4-158   | Priority Control Functional Diagram                     | 4-431       |

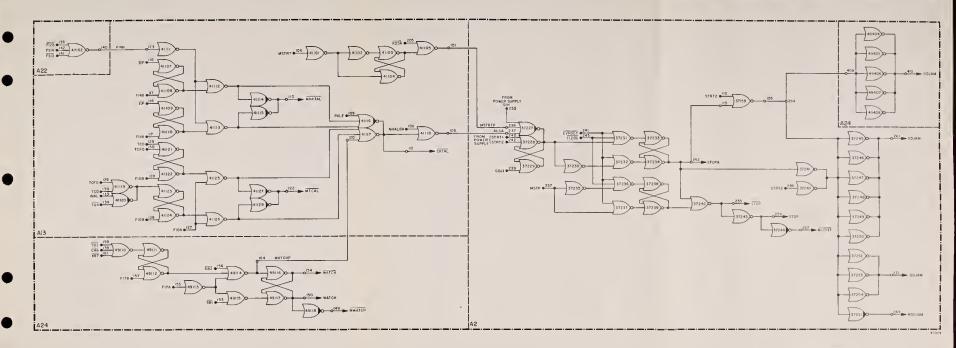

| 4-159   | Start Instruction Control Detailed Logic                | 4-435/4-436 |

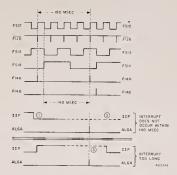

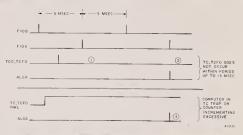

| 4~160   | RUPT Alarm Logic Timing Diagram                         | 4-437       |

| 4-161   | Transfer Control Alarm Logic Timing Diagram             | 4-438       |

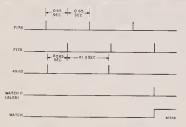

| 4-162   | Watch Alarm Timing                                      | 4-439       |

| 4-163   | Interrupt Instruction Control Detailed Logic            | 4-441/4-442 |

| 4-164   | Counter Priority Cells                                  | 4-447/4-448 |

| 4-165   | Counter Address Generator                               | 4-461/4-462 |

| 4-166   | Counter Alarm Detector                                  | 4-465/4-466 |

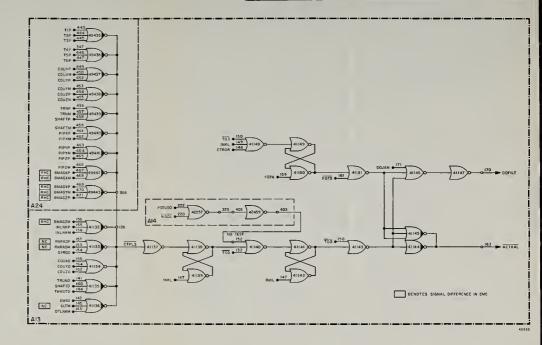

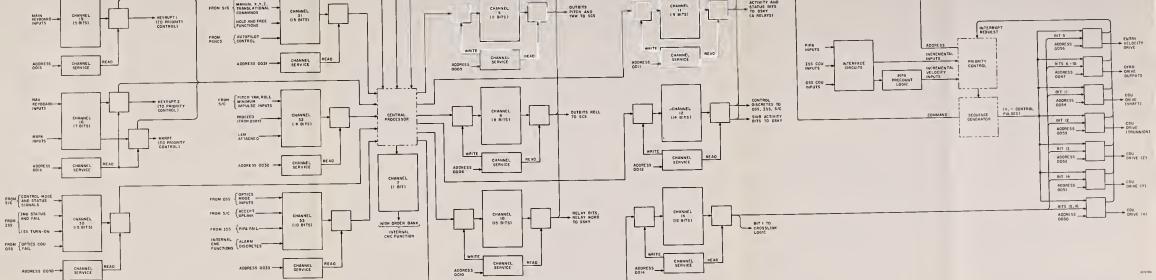

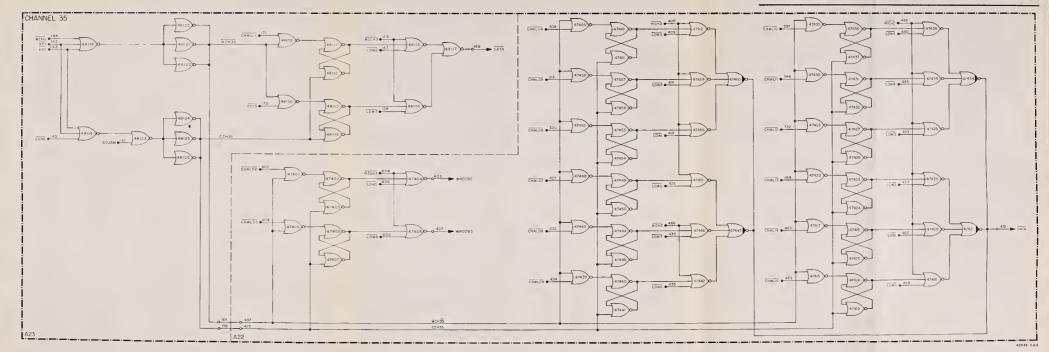

| 4-167   | Input-Output Channels Functional Diagram - LGC          | 4-469/4-470 |

| 4-168   | Input-Output Channels Functional Diagram - CMC          | 4-471/4-472 |

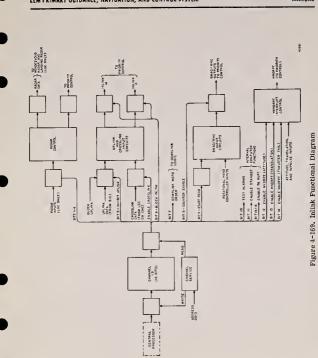

| 4-169   | Inlink Functional Diagram                               | 4-473       |

| 4 - 170 | Outlink Functional Diagram                              | 4-475/4-476 |

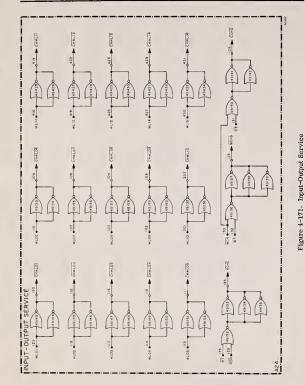

| 4-171   | Input-Output Service                                    | 4-477       |

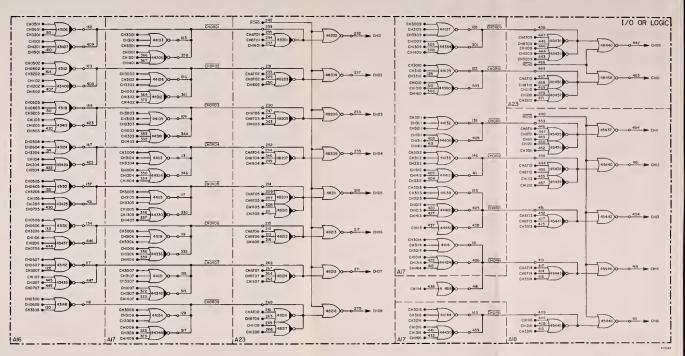

| 4-172   | Input-Output OR Configuration                           | 4-479/4-480 |

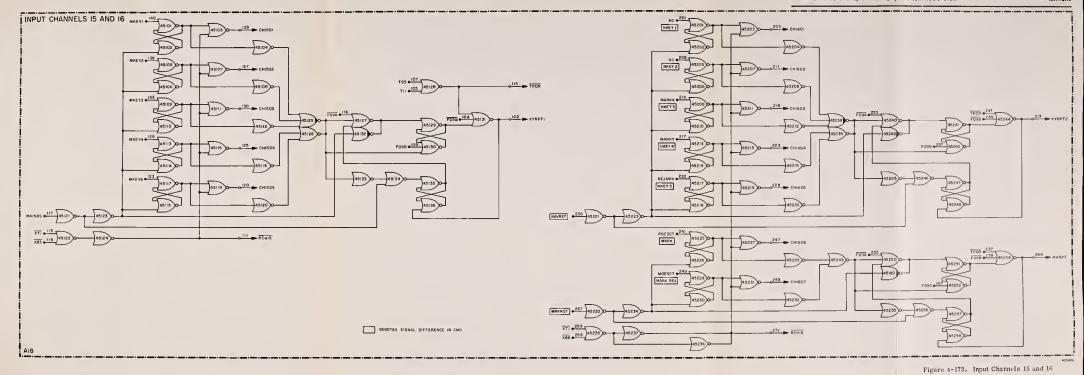

| 4 - 173 | Input Channels 15 and 16                                | 4-481/4-482 |

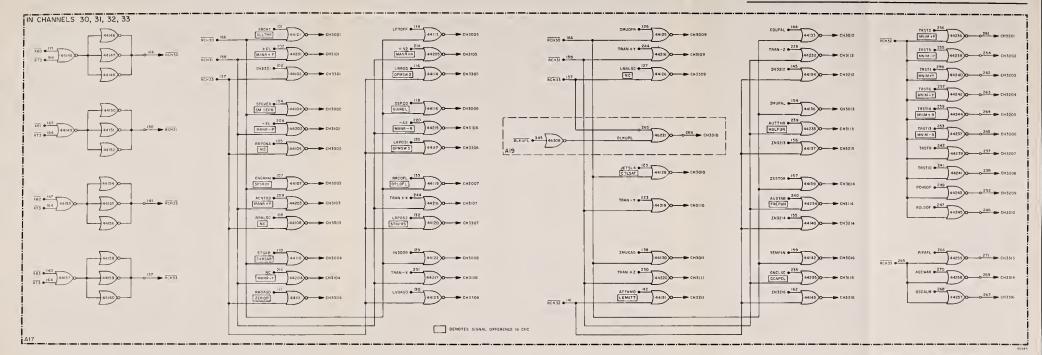

| 4-174   | Input Channels 30, 31, 32, and 33                       | 4-485/4-486 |

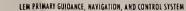

| 4-175   | PIPA Precount Logic                                     | 4-501/4-502 |

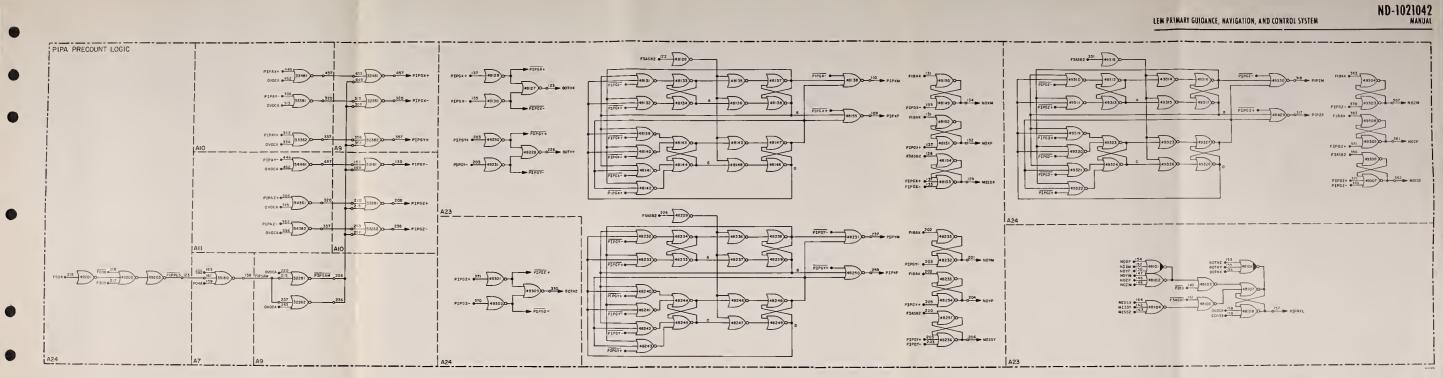

| 4-176   | Output Channels 05 and 06                               | 4-505/4-506 |

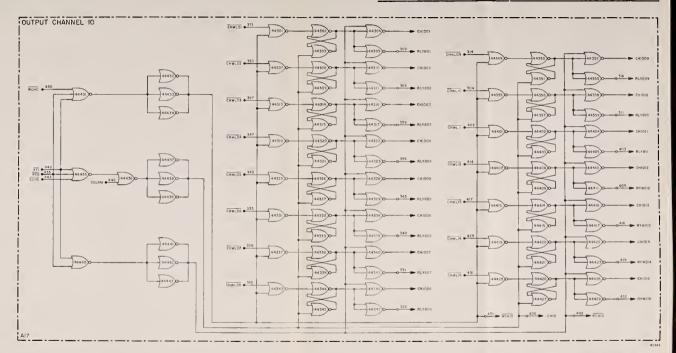

| 4-177   | Output Channel 10                                       | 4-507/4-508 |

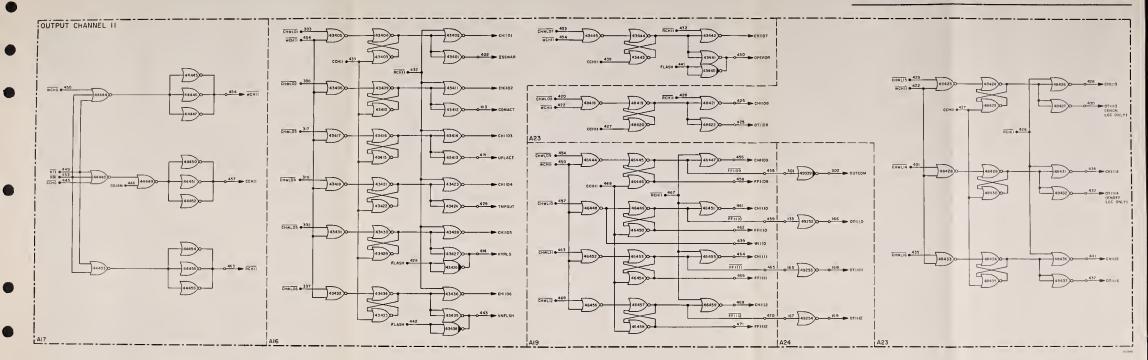

| 4-178   | Output Channel 11                                       | 4-509/4-510 |

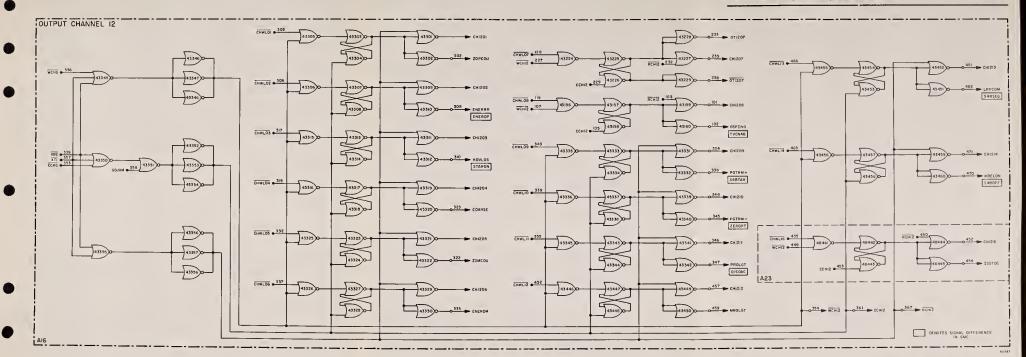

| 4 - 179 | Output Channel 12                                       | 4-511/4-512 |

| 4 - 180 | Channel 13 Service                                      | 4-517       |

| 4-181   | Radar Control Logic                                     | 4-519/4-520 |

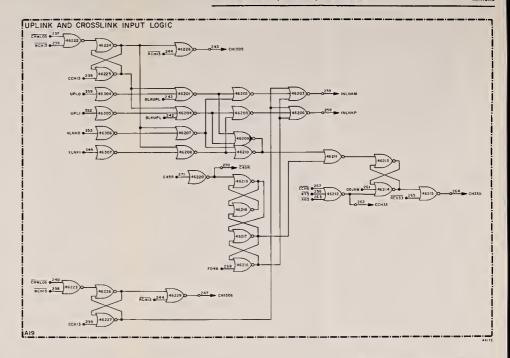

| 4-182   | Uplink and Crosslink Input Logic                        | 4-523/4-524 |

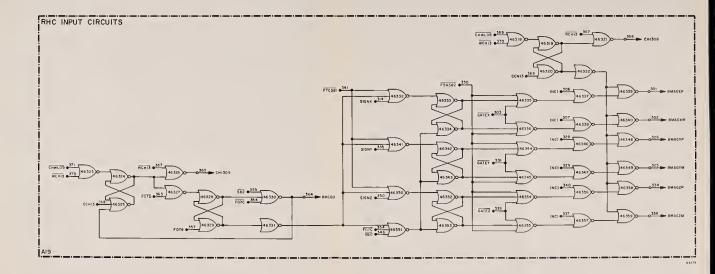

| 4-183   | RHC Input Logic                                         | 4-525/4-526 |

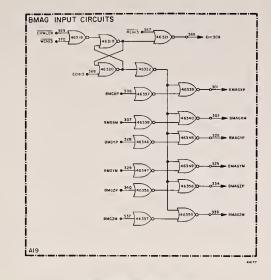

| 4-184   | BMAG Input Logic                                        | 4-527       |

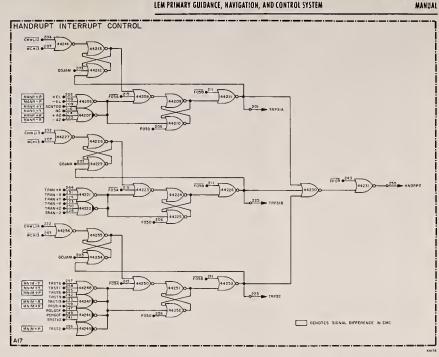

| 4-185   | Handrupt Interrupt Control Logic                        | 4-529/4-530 |

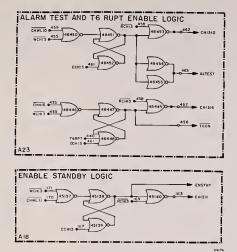

| 4-186   | Alarm Test, T6RUPT, and Enable Standby Logic            | 4-531       |

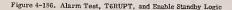

| 4-187   | Crosslink, Attitude Meter, EMS and Thrust Drive Control |             |

|         | Logic                                                   | 4-533/4-534 |

| 4-188   | Crosslink Timing                                        | 4-535       |

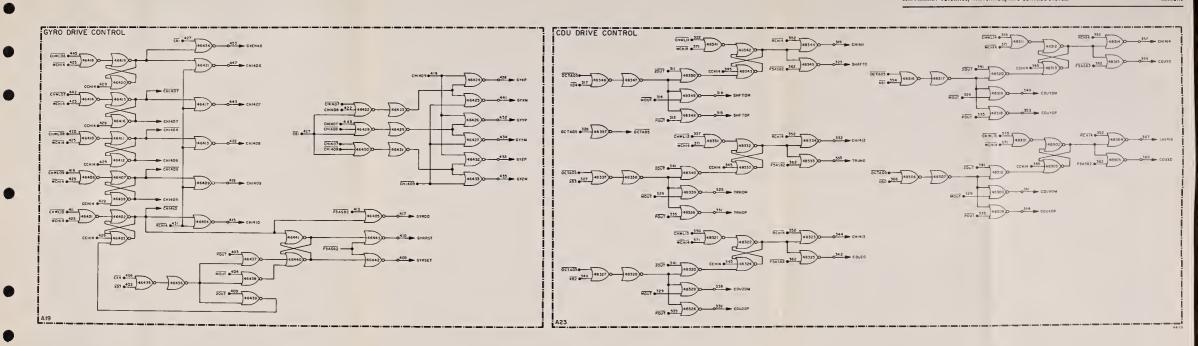

| 4-189   | Gyro and CDU Drive Control Logic                        | 4-537/4-538 |

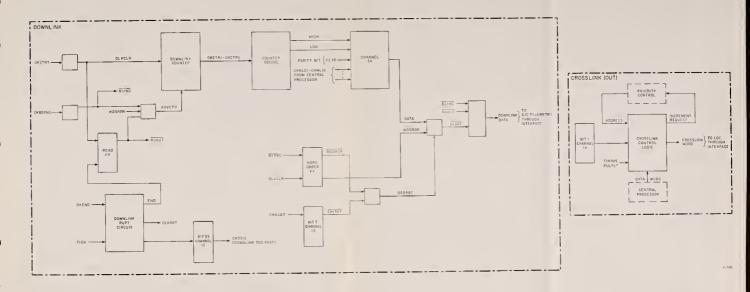

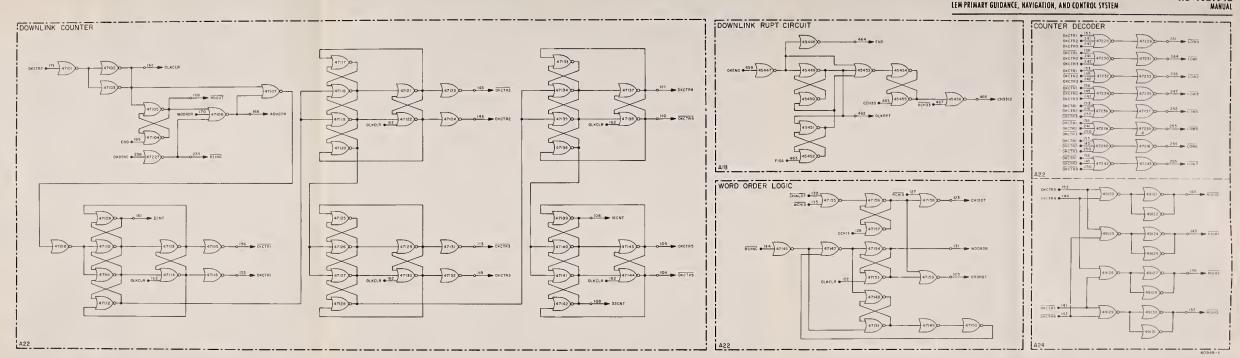

| 4-190   | Downlink Control Logic                                  | 4-541/4-542 |

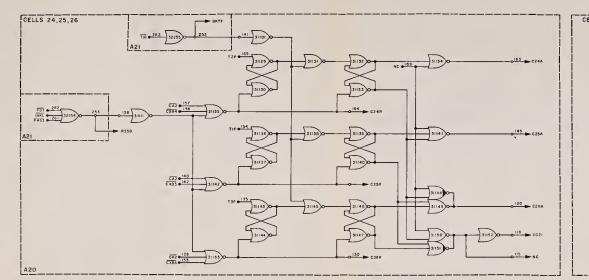

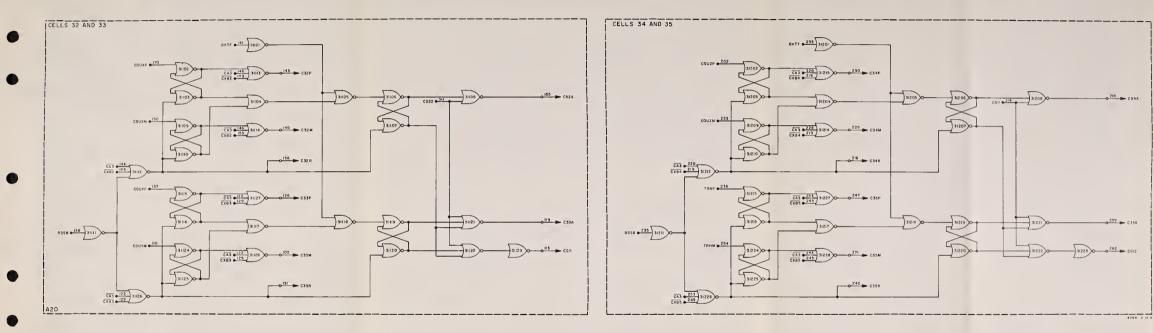

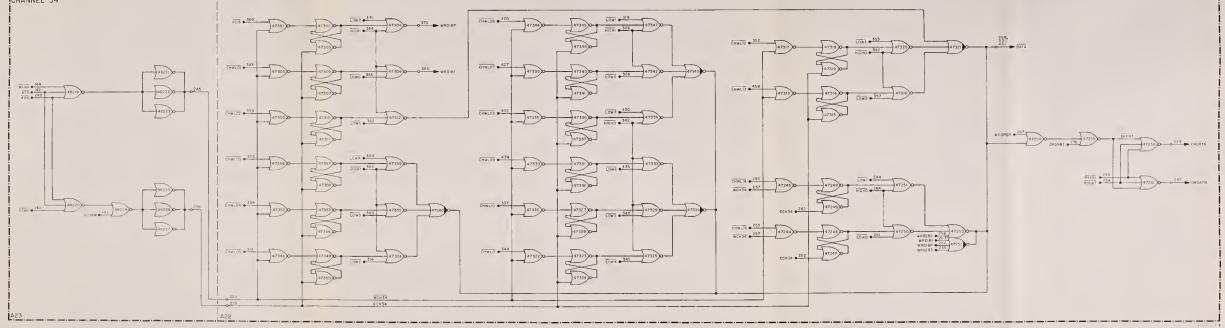

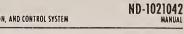

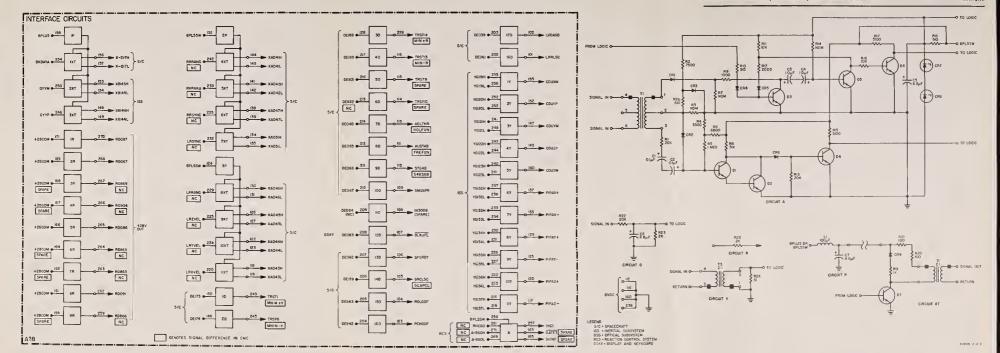

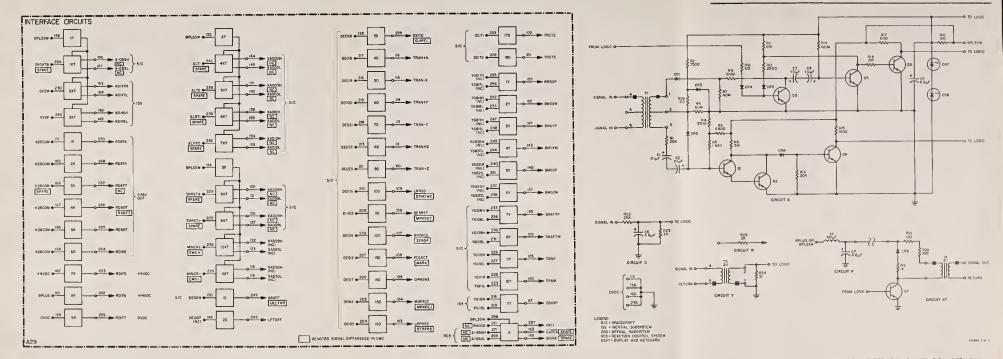

| 4-191   | Interface Modules A25 and A26                           | 4-547/4-548 |

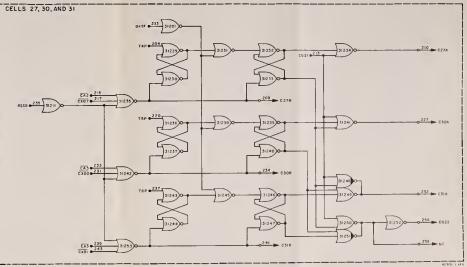

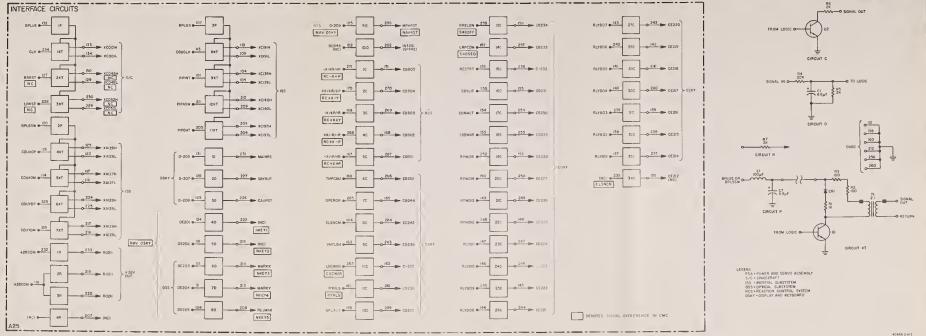

| 4-192   | Interface Modules A27, A28, and A29                     | 4-551/4-552 |

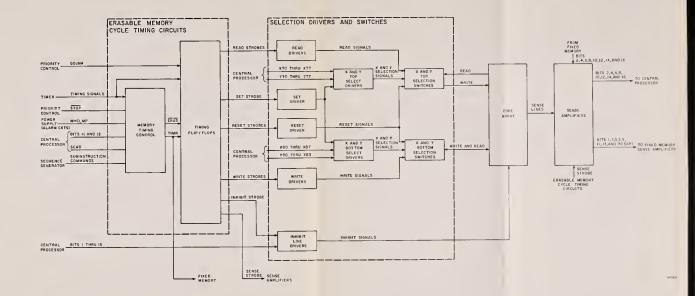

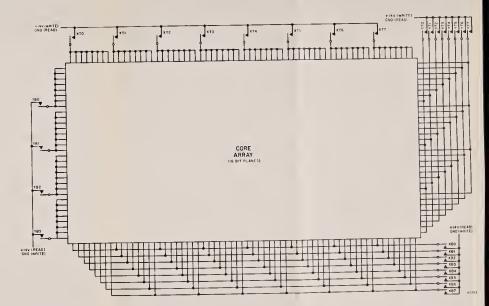

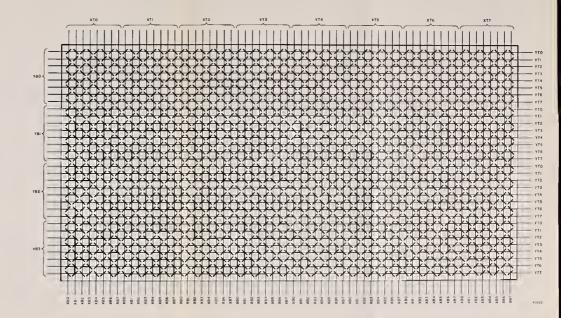

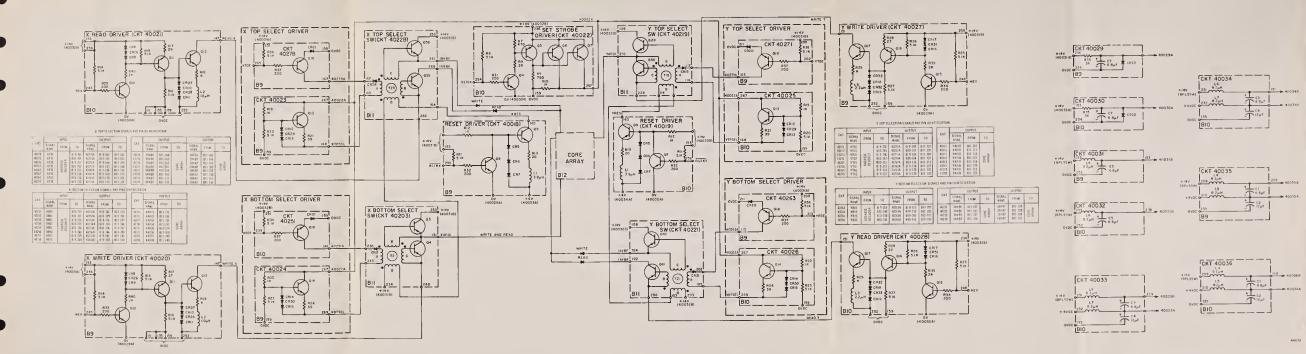

| 4-193   | Erasable Memory Functional Diagram                      | 4-561/4-562 |

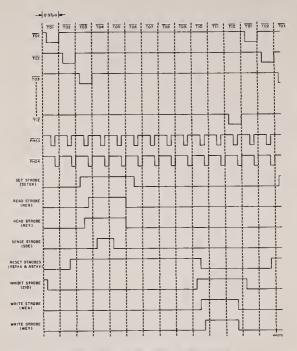

| 4-194   | Erasable Memory Timing Diagram                          | 4-564       |

| 4-195   | X and Y Selection, Simplified Diagram                   | 4-567/4-568 |

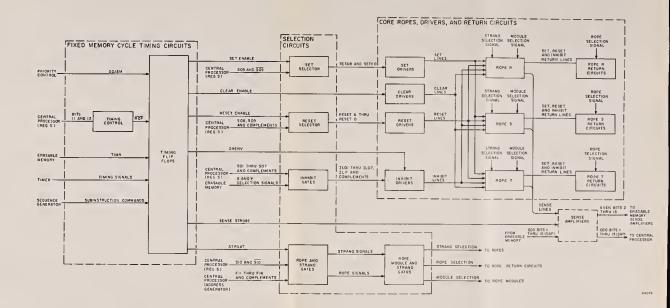

| 4-196   | Fixed Memory, Functional Diagram                        | 4-569/4-570 |

•

#### ND-1021042 MANUAL

#### ILLUSTRATIONS (cont)

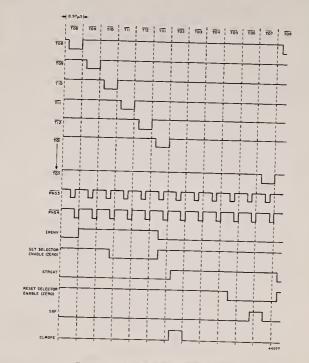

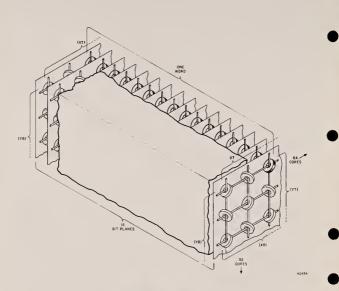

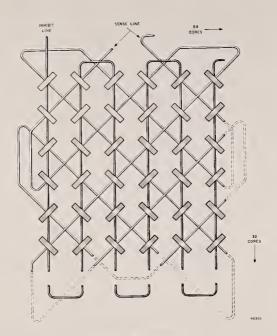

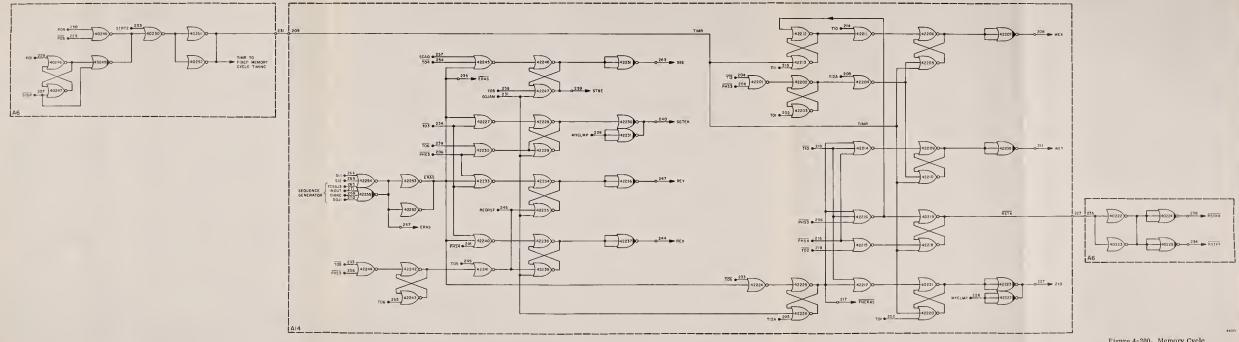

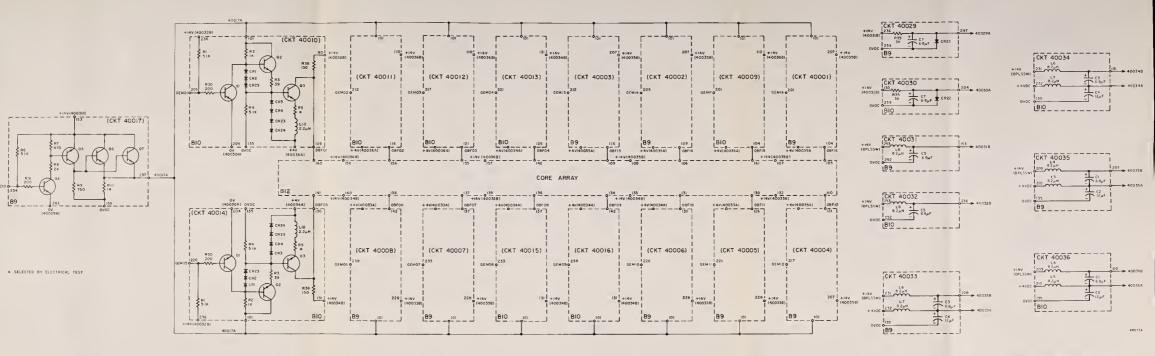

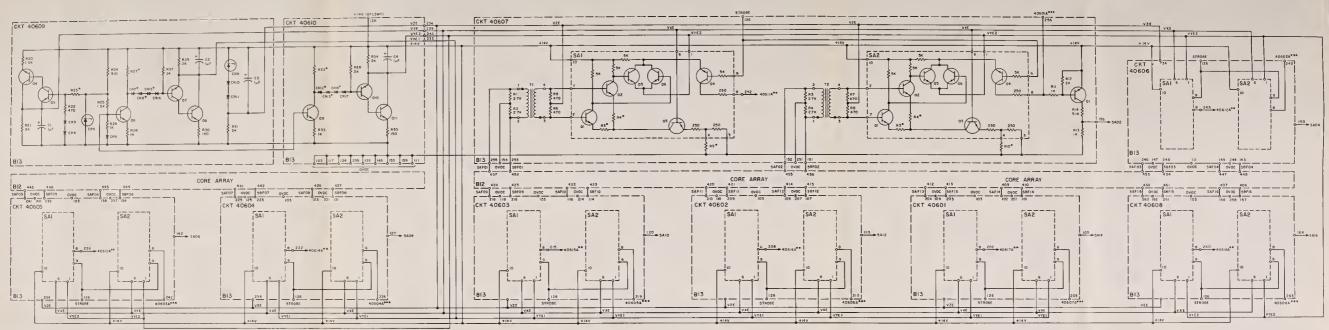

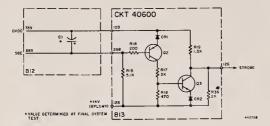

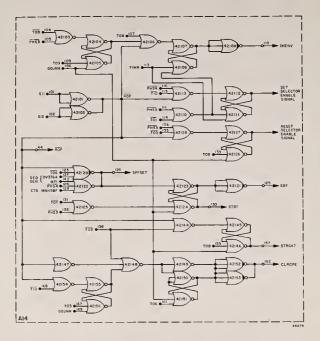

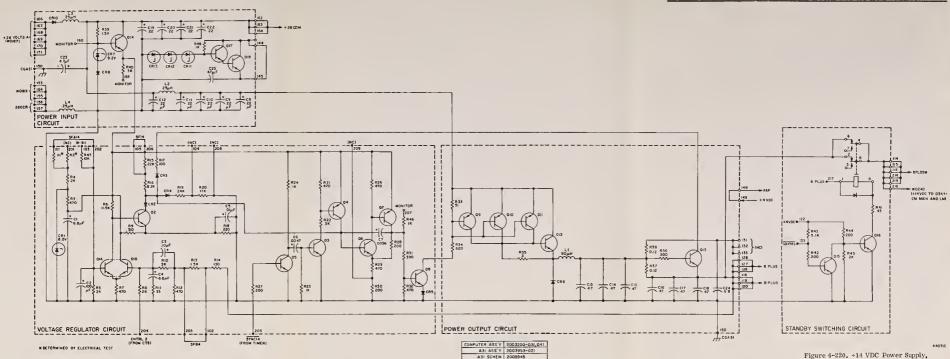

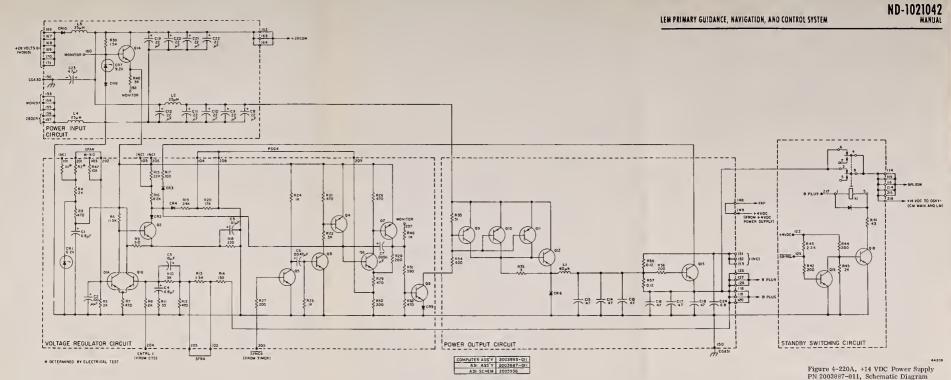

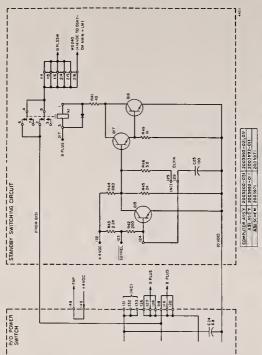

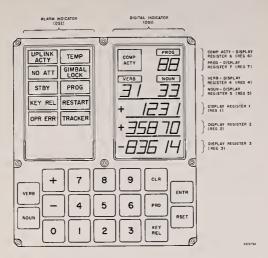

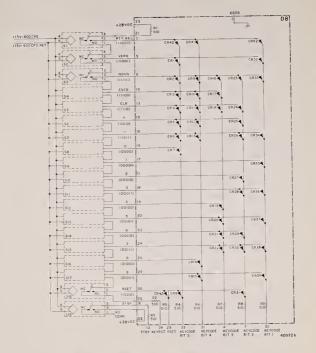

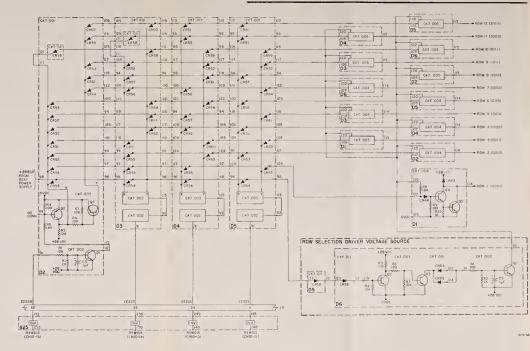

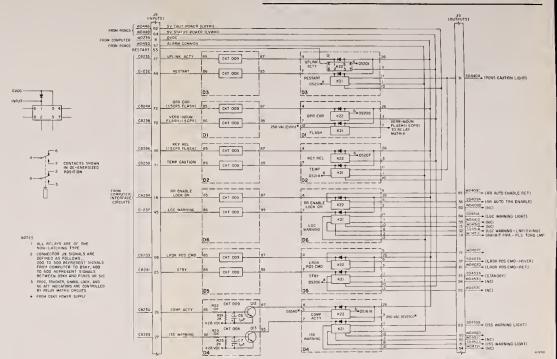

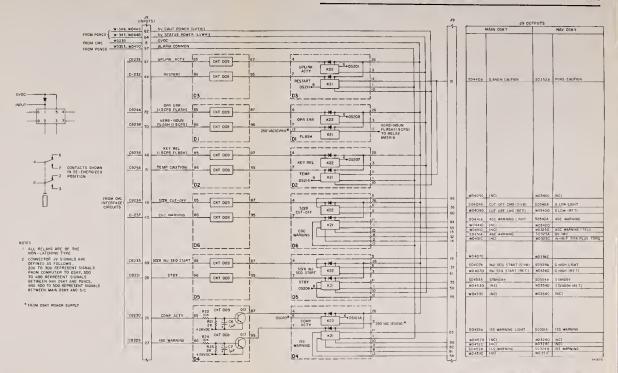

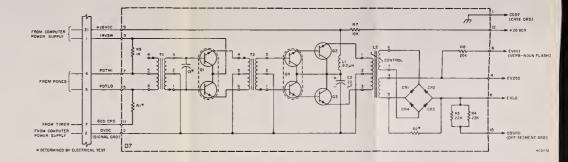

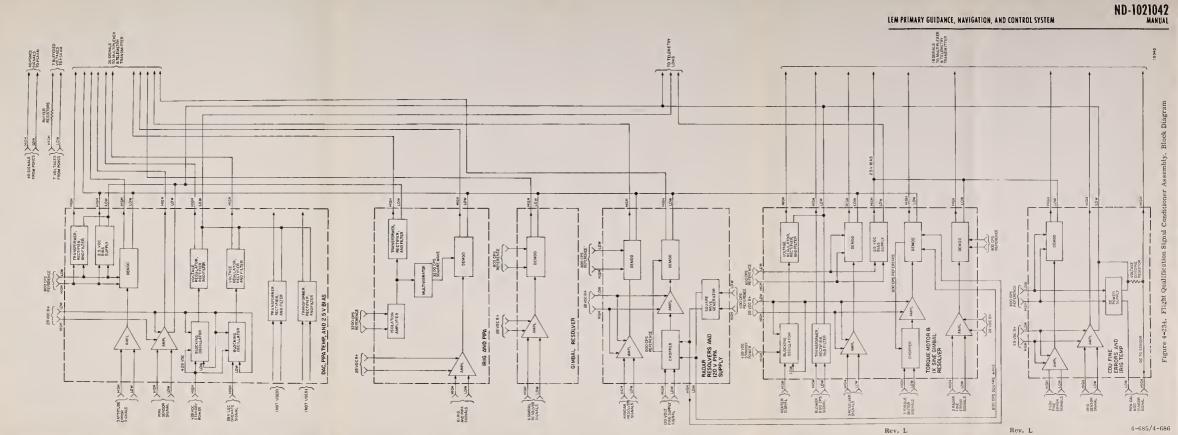

#### Figure 4 - 197Fixed Memory, Timing Diagram ..... 4 - 5764 - 5784 - 198Core Array. 4 - 199Bit Plane ..... 4 - 5794-200 4 - 2014-202 4-203 4 - 2044-205 Strobe Driver, Erasable ..... 4-593 Memory Cycle Timing, Fixed ..... 4-596 4 - 2064 - 2074 - 2084-209 4 - 2104 - 2114 - 2124 - 2134-214 4 - 2154 - 2164 - 2174-218 4 - 2194-220 4 - 2214 - 2224-653 4 - 223Keyboard and Display Front Panel ..... 4-654 4 - 224DSKY Keyboard Schematic Diagram 4 - 2254 - 2264 - 2274-228 DSKY Display Locations ..... 4 - 6654 - 229Status and Caution Circuit Schematic Diagram (LGC) ...... 4-669/4-670 4 - 2304 - 231Status and Caution Circuit Schematic Diagram (CMC) . . . . . . . 4-671/4-672 4 - 2324 - 233Operational Signal Conditioner Assembly, Block Diagram . . . . 4-683/4-684 Flight Qualification Signal Conditioner Assembly, 4 - 234

Page

#### ILLUSTRATIONS (cont)

#### Figure

| 5-1  | LEM Mission                                              | 5-3/5-4   |

|------|----------------------------------------------------------|-----------|

| 5-2  | LEM IMU Coarse Alignment                                 | 5-5       |

| 5-3  | LEM IMU Fine Alignment                                   | 5-5       |

| 5-4  | Powered Descent                                          | 5-6       |

| 5-5  | Powered Ascent                                           | 5-8       |

|      |                                                          |           |

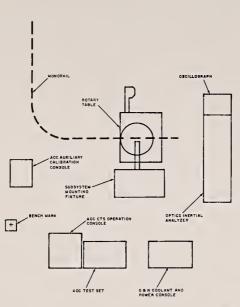

| 6-1  | Typical Universal Test Station Layout                    | 6-11/6-12 |

|      | D to a gother with testing and Graterial Grateria Martin |           |

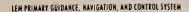

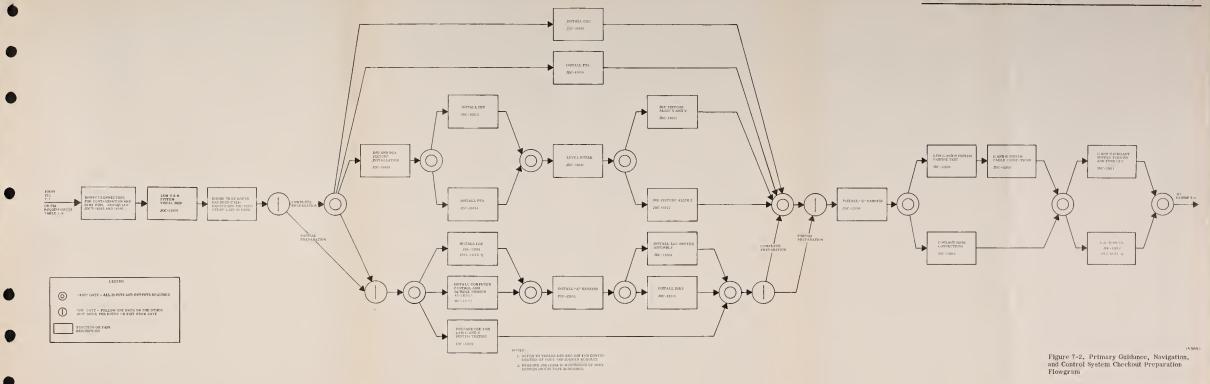

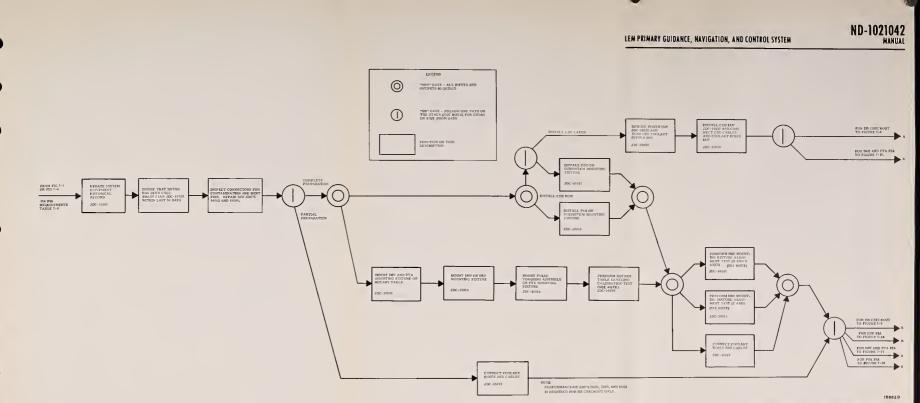

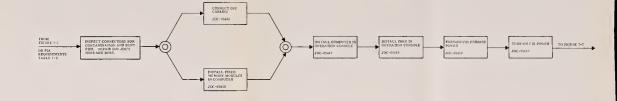

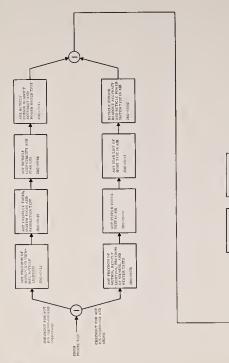

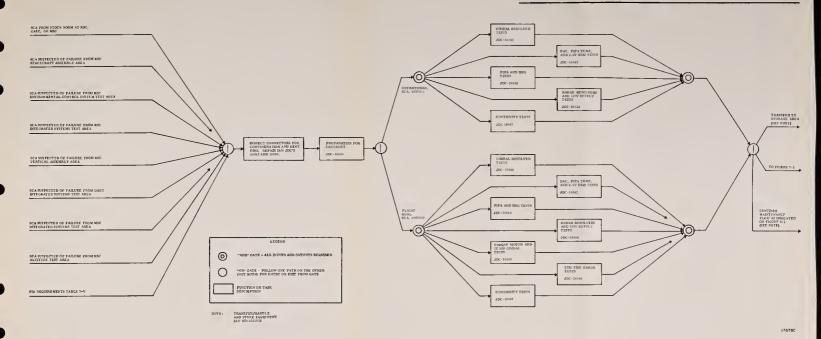

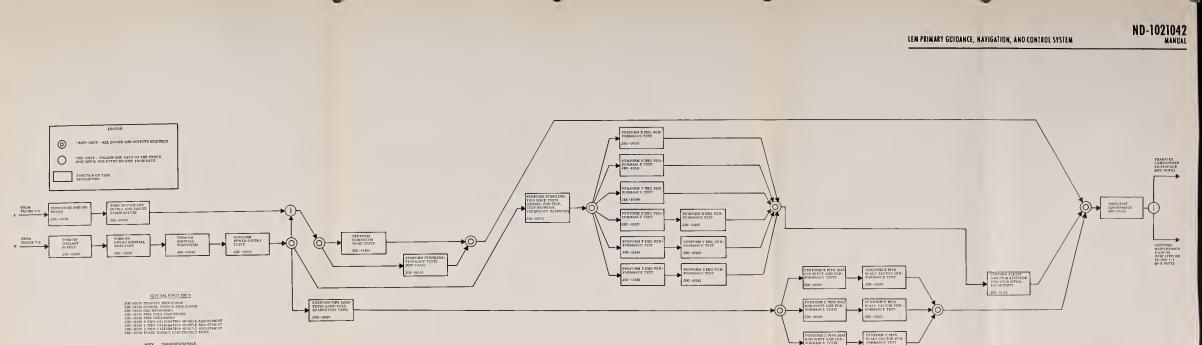

| 7-1  | Primary Guidance, Navigation, and Control System Master  | /         |

|      | Checkout Flowgram                                        | 7-17/7-18 |

| 7-2  | Primary Guidance, Navigation, and Control System         |           |

|      | Checkout Preparation Flowgram                            | 7-19/7-20 |

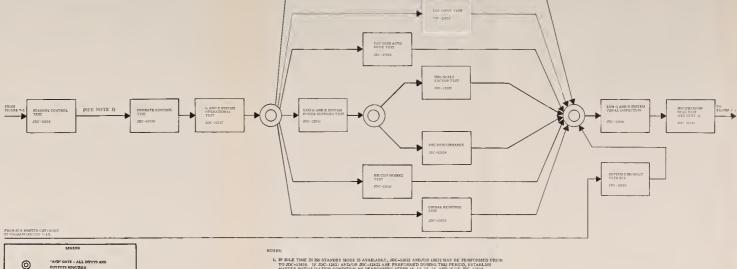

| 7-3  | Primary Guidance, Navigation, and Control System         |           |

|      | Checkout Flowgram                                        | 7-21/7-22 |

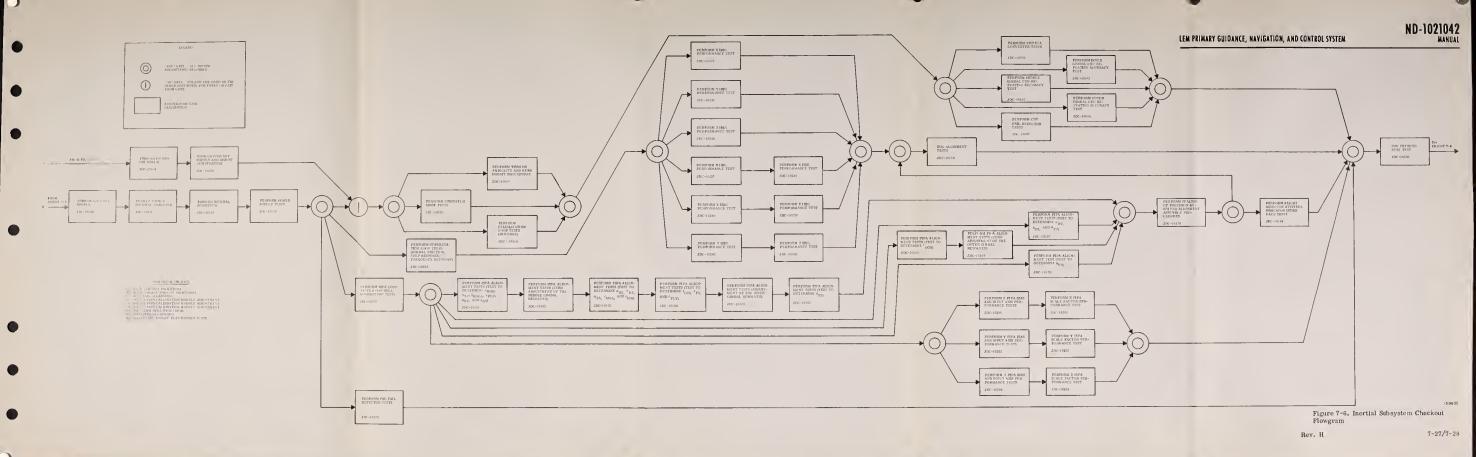

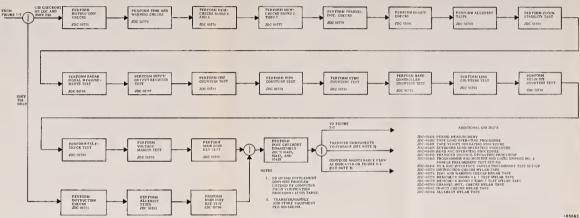

| 7-4  | Inertial Subsystem Master Checkout Flowgram              | 7-23/7-24 |

| 7-5  | Inertial Subsystem Checkout Preparation Flowgram         | 7-25/7-26 |

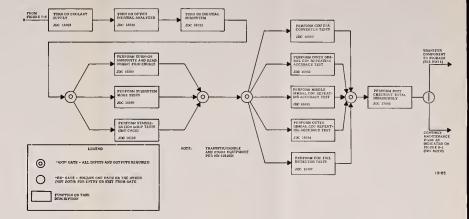

| 7-6  | Inertial Subsystem Checkout Flowgram                     | 7-27/7-28 |

| 7-7  | Computer Subsystem Master Checkout Flowgram              | 7-29/7-30 |

| 7-8  | Computer Subsystem Checkout Preparation Flowgram         | 7-31/7-32 |

| 7-9  | Computer Subsystem Checkout Flowgram                     | 7-33/7-34 |

| 7-10 | AOT Master Checkout Flowgram                             | 7-35/7-36 |

| 7-11 | AOT Checkout Preparation Flowgram                        | 7-37      |

| 7-12 | AOT Checkout Flowgram                                    | 7-38      |

| 7-13 | SCA Master Checkout Flowgram                             | 7-39/7-40 |

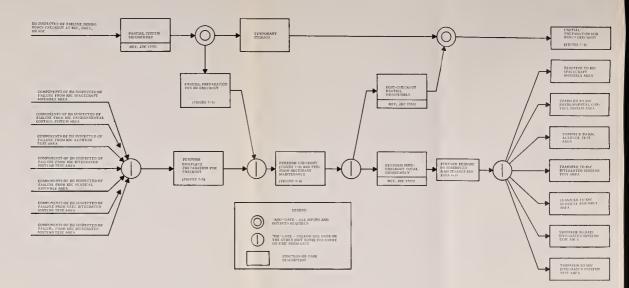

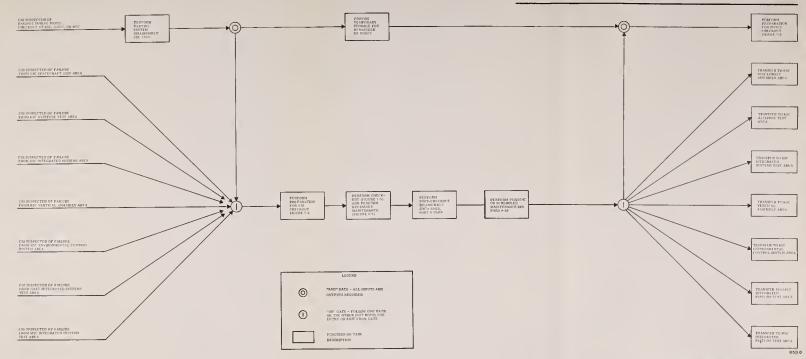

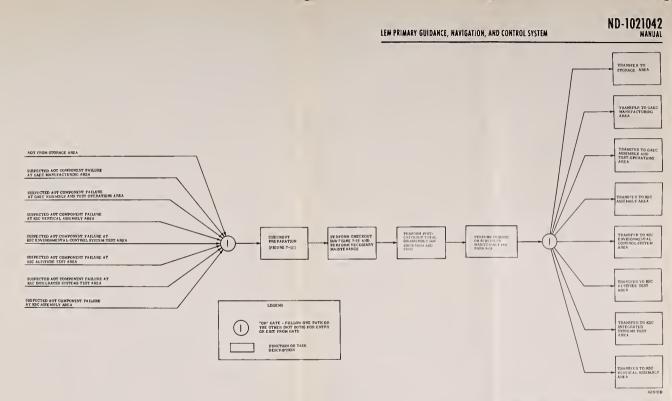

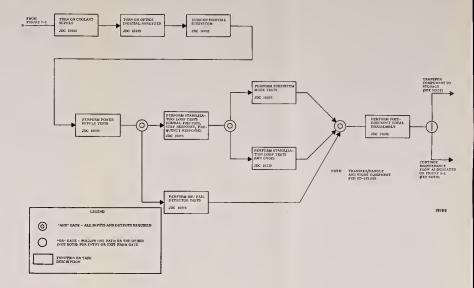

| 8-1  | Master Maintenance Flowgram                              | 8-3/8-4   |

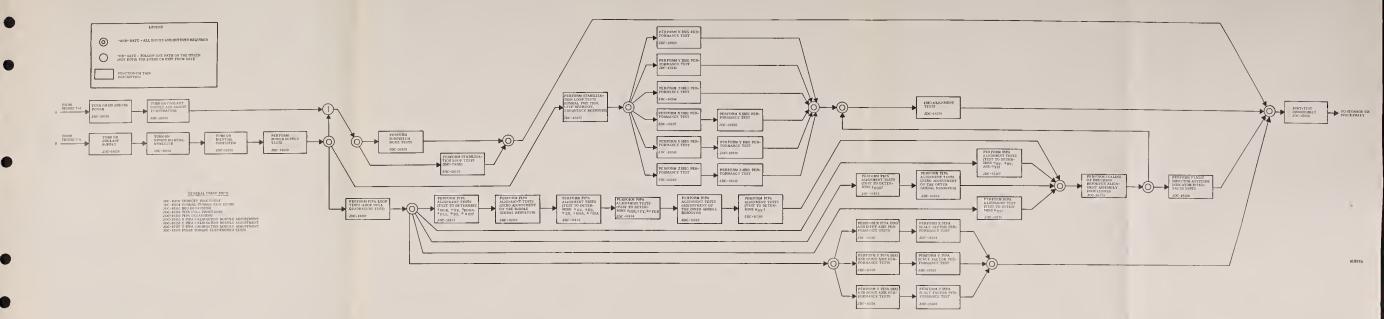

| 8-2  | IMU and PTA Pre-Installation Acceptance Test Flowgram    | 8-11/8-12 |

|      |                                                          |           |

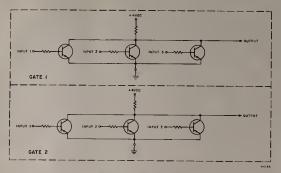

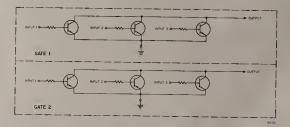

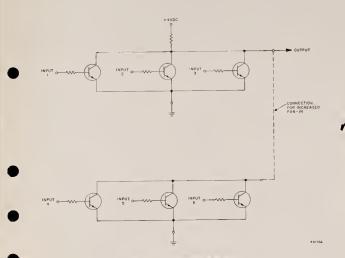

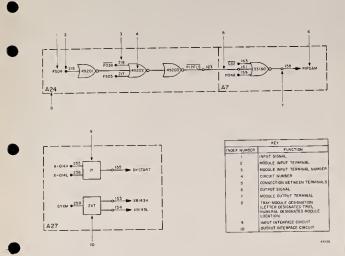

| C-1  | NOR Gate Symbols                                         | C-2       |

| C-2  | NOR Gate Schematic                                       | C-2       |

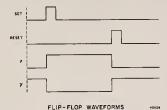

| C-3  | NOR Gate Flip-Flop                                       | C-5       |

| C-4  | Logic Diagram Symbols                                    | C-6       |

|      |                                                          |           |

#### TABLES (cont)

| Number                                                                            |                                                                                                                                                                                                      | Page                                                                                                |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| 4-хСІV<br>4-ХСV<br>4-ХСVІ<br>4-ХСVІІ<br>4-ХСІХІІ<br>4-ХСІХ<br>4-С<br>4-СІ<br>4-СІ | Channel 12 Output Signals - CMC<br>Radar Data Processing<br>Gyro Drive Pulses<br>E Addressing<br>F Addressing<br>Power Distribution<br>Relay Matrix Codes<br>Digri Code<br>Circuits in SCA Modules . | $\begin{array}{r} 4-515\\ 4-518\\ 4-539\\ 4-563\\ 4-572\\ 4-661\\ 4-661\\ 4-662\\ 4-677\end{array}$ |

| 6-І<br>6-П<br>6-ПІ                                                                | Checkout and Maintenance Test Equipment<br>Checkout and Maintenance Tools<br>List of Operating Procedure JDC's for GSE                                                                               | 6-1<br>6-5<br>6-6                                                                                   |

| 7-I<br>7-II<br>7-III<br>7-IV                                                      | Equipment Required for Checkout .<br>PGNCS Interconnect Cables .<br>Inertial Subsystem Interconnect Cables .<br>Computer Subsystem Interconnect Cables .                                             | 7-2L<br>7-4<br>7-10<br>7-14                                                                         |

| 8-I<br>8-IA<br>8-II<br>8-III<br>8-IV<br>8-IVA<br>8-IVA<br>8-V<br>8-V              | PGNCS and ISS Loop Diagrams and Schematics                                                                                                                                                           | 8-5<br>8-6D<br>8-7<br>8-8<br>8-8A/8-8B<br>8-9<br>8-13                                               |

#### TABLES

Number

Page

#### Volume II

|           | vorume n                                       |       |

|-----------|------------------------------------------------|-------|

| 4-IX      | Commands Per Subinstruction                    | 4-251 |

| 4-X       | Subinstructions Per Command                    | 4-264 |

| 4-XI      | Counter Cell Signals                           | 4-278 |

| 4-XII     | Subinstruction CCS0                            | 4-280 |

| 4-XIII    | Subinstruction DV0                             | 4-303 |

| 4-XIV     | Subinstruction DV1, Part 1                     | 4-304 |

| 4-XV      | Subinstructions DV3, DV7, and DV6, Part 1      | 4-305 |

| 4-XVI     | Subinstructions DV1, DV3, DV7, and DV6, Part 2 | 4-306 |

| 4-XVII    | Subinstruction DV4                             | 4-307 |

| 4-XVIII   | Subinstruction MP0                             | 4-309 |

| 4-XIX     | Subinstruction MP1                             | 4-310 |

| 4-XX      | Subinstruction MP3                             | 4-311 |

| 4-XXI     | Crosspoint Pulse ZIP                           | 4-312 |

| 4-XXII    | Subinstruction STD2                            | 4-314 |

| 4-XXIII   | Subinstruction TC0                             | 4-314 |

| 4-XXIV    | Subinstruction TCF0                            | 4-315 |

| 4-XXV     | Subinstruction TCSAJ3                          | 4-315 |

| 4-XXVI    | Subinstruction GOJ1                            | 4-315 |

| 4-XXVII   | Subinstruction DAS0                            | 4-316 |

| 4-XXVIII  | Subinstruction DAS1                            | 4-317 |

| 4-XXIX    | Subinstruction LXCH0                           | 4-318 |

| 4-XXX     | Subinstruction INCR0                           | 4-318 |

| 4-XXXI    | Subinstruction ADS0                            | 4-319 |

| 4-XXXII   | Subinstructions CA0 and DCA1                   | 4-320 |

| 4-XXXIII  | Subinstructions CS0 and DCS1                   | 4-320 |

| 4-XXXIV   | Subinstruction NDX0                            | 4-321 |

| 4-XXXV    | Subinstruction RSM3                            | 4-321 |

| 4-XXXVI   | Subinstruction NDX1                            | 4-322 |

| 4-XXXVII  | Subinstruction XCH0                            | 4-323 |

| 4-XXXVIII | Subinstruction DXCH0                           | 4-324 |

| 4-XXXIX   | Subinstruction DXCH1                           | 4-324 |

| 4-XL      | Subinstruction TS0                             | 4-325 |

| 4-XLI     | Subinstruction AD0                             | 4-326 |

| 4-XLII    | Subinstruction MASK0                           | 4-327 |

| 4-XLIII   | Subinstruction BZF0                            | 4-328 |

| 4-XLIV    | Subinstruction MSU0                            | 4-329 |

| 4-XLV     | Subinstruction QXCH0                           | 4-330 |

| 4-XLVI    | Subinstruction AUG0                            | 4-330 |

| 4-XLVII   | Subinstruction DIM0                            | 4-331 |

| 4-XLVIII  | Subinstruction DCA0                            | 4-332 |

| 4-XLIX    | Subinstruction DCS0                            | 4-333 |

| 4-L       | Subinstruction SU0                             | 4-334 |

#### TABLES (cont)

| Number     |                                           | Page    |

|------------|-------------------------------------------|---------|

| 4-LI       | Subinstruction NDXX0                      | 4-334   |

| 4-LII      | Subinstruction NDXX1                      | 4-335   |

| 4-LIII     | Subinstruction BZMF0                      | 4-336   |

| 4-LIV      | Subinstruction READ0                      | 4-337   |

| 4-LV       | Subinstruction WRITE0                     | 4-338   |

| 4-LVI      | Subinstruction RAND0                      | 4-339   |

| 4-LVII     | Subinstruction WAND0                      | 4-340   |

| 4-LVⅢ      | Subinstruction ROR0                       | 4-341   |

| 4-LIX      | Subinstruction WOR0                       | 4 - 341 |

| 4-LX       | Subinstruction RXOR0                      | 4-342   |

| 4-LXI      | Subinstruction RUPT0                      | 4-343   |

| 4-LXII     | Subinstruction RUPT1                      | 4-343   |

| 4-LXIII    | Subinstruction PINC                       | 4-344   |

| 4-LXIV     | Subinstruction MINC                       | 4-344   |

| 4-LXV      | Subinstruction PCDU                       | 4-345   |

| 4-LXVI     | Subinstruction MCDU                       | 4-345   |

| 4-LXVII    | Subinstruction DINC                       | 4-346   |

| 4-LXVIII   | Subinstruction SHINC                      | 4-347   |

| 4-LXIX     | Subinstruction SHANC                      | 4-347   |

| 4-LXX      | Subinstruction INOTRD                     | 4-348   |

| 4-LXXI     | Subinstruction INOTLD                     | 4-348   |

| 4-LXXII    | Subinstructions FETCH0 and STORE0         | 4-349   |

| 4-LXXIII   | Subinstruction FETCH1                     | 4-349   |

| 4-LXXIV    | Subinstruction STORE1                     | 4-350   |

| 4-LXXV     | Control Pulse Origin                      | 4-357   |

| 4-LXXVI    | Register A and L Write Line Inputs        | 4-393   |

| 4-LXXVII   | Write Amplifiers External Inputs          | /4-414  |

| 4-LXXVIII  | Erasable Memory Address Selection 4-425.  | /4-426  |

| 4-LXXIX    | LGC/CMC Interrupts                        | 4-432   |

| 4-LXXX     | LGC/CMC Interrupt Functions               | 4-443   |

| 4-LXXXI    | LGC/CMC Counter Cell/Register Assignments | 4-445   |

| 4-LXXXII   | Input Channel 30 - LGC                    | 4-487   |

| 4-LXXXIII  | Input Channel 31 - LGC                    | 4-489   |

| 4-LXXXIV   | Input Channel 32 - LGC                    | 4-491   |

| 4-LXXXV    | Input Channel 33 - LGC                    | 4-493   |

| 4-LXXXVI   | Input Channel 30 - CMC.                   | 4-495   |

| 4-LXXXVII  | Input Channel 31 - CMC                    | 4-497   |

| 4-LXXXVIII | Input Channel 32 - CMC.                   | 4-498   |

| 4-LXXXVIX  | Input Channel 33 - CMC.                   | 4-499   |

| 4-XC       | Truth Table for Z Axis PIPA Counter       | 4-503   |

| 4-XCI      | RCS Control Signals - LGC and CMC         | 4-504   |

| 4-XCII     | Channel 11 Output Signals                 | 4-513   |

| 4-XCIII    | Channel 12 Output Signals - LGC           | 4-514   |

#### TABLES (cont)

| Number   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 4-XCIV   | Channel 12 Output Signals - CMC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-515 |

| 4-XCV    | Radar Data Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-518 |

| 4-XCVI   | Gyro Drive Pulses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-539 |

| 4-XCVII  | E Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-563 |

| 4-XCVIII | F Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-572 |

| 4-XCIX   | Power Distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-637 |

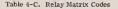

| 4-C      | Relay Matrix Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-661 |

| 4-CI     | Digit Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4-662 |

| . 01     | Digit Coder i i i i i i i i i i i i i i i i i i i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| 6-I      | Checkout and Maintenance Test Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6-1   |

| 6-II     | Checkout and Maintenance Tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6-5   |

| 6-III    | List of Operating Procedure JDC's for GSE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6-6   |

|          | bibliot of operands a construction of the cons | 0-0   |

| 7-I      | Equipment Required for Checkout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7-2   |