# APOLLO BLOCK II and LEM

**COMPUTER DESIGN REVIEW**

9 May 1966 REVISED

# APOLLO

# BLOCK II AND LEM

#### COMPUTER DESIGN REVIEW

9 May 1966

Revised

23 May 1966

3 June 1966

8 June 1966

LA-3544

# TABLE OF CONTENTS

| SECTION | TITLE                                     | PAGE |

|---------|-------------------------------------------|------|

| 0       | PRELIMINARY MIT/IL COMMENTS               | 0-1  |

|         | 0.1 Responsibilities                      | 0-1  |

|         | 0.2 Constraints on Design                 | 0-1  |

|         | 0.3 Critique of Committee Reports Results | 0-3  |

| I       | INTRODUCTION AND SUMMARY                  | 1-1  |

|         | 1.1 Background                            | 1-1  |

|         | 1.2 Scope of the Investigation            | 1-1  |

|         | 1.3 Method of Investigation               | 1-2  |

|         | 1.4 Categories of Findings                | 1-4  |

|         | 1.5 Summary of Findings                   | 1-5  |

|         | 1. 6 Recommended Actions                  | 1-10 |

|         | 1.6.1 Continued Design Review             | 1-10 |

|         | 1.6.2 Engineering Tests                   | 1-10 |

|         | 1.6.3 Documentation                       | 1-11 |

|         | 1.6.4 Test Plans                          | 1-12 |

|         | 1.6.5 Design Tasks                        | 1-13 |

|         | 1.7 Organization of This Report           | 1-14 |

| II      | BLOCK II APOLLO GUIDANCE COMPUTER (AGC)   | 2-1  |

|         | 2.1 Functional Aspects                    | 2-1  |

| *       | 2.1.1 Alarms and Restart                  | 2-1  |

|         | 2.1.2 Interrupts and Counter Increments   | 2-7  |

|         | 2.1.3 Maintenance and Logistics           | 2-8  |

|         | 2.2 Mechanical Design                     | 2-9  |

|         | 2.2.1 Structure                           | 2-9  |

|         | 2.2.2 Materials and Finishes              | 2-11 |

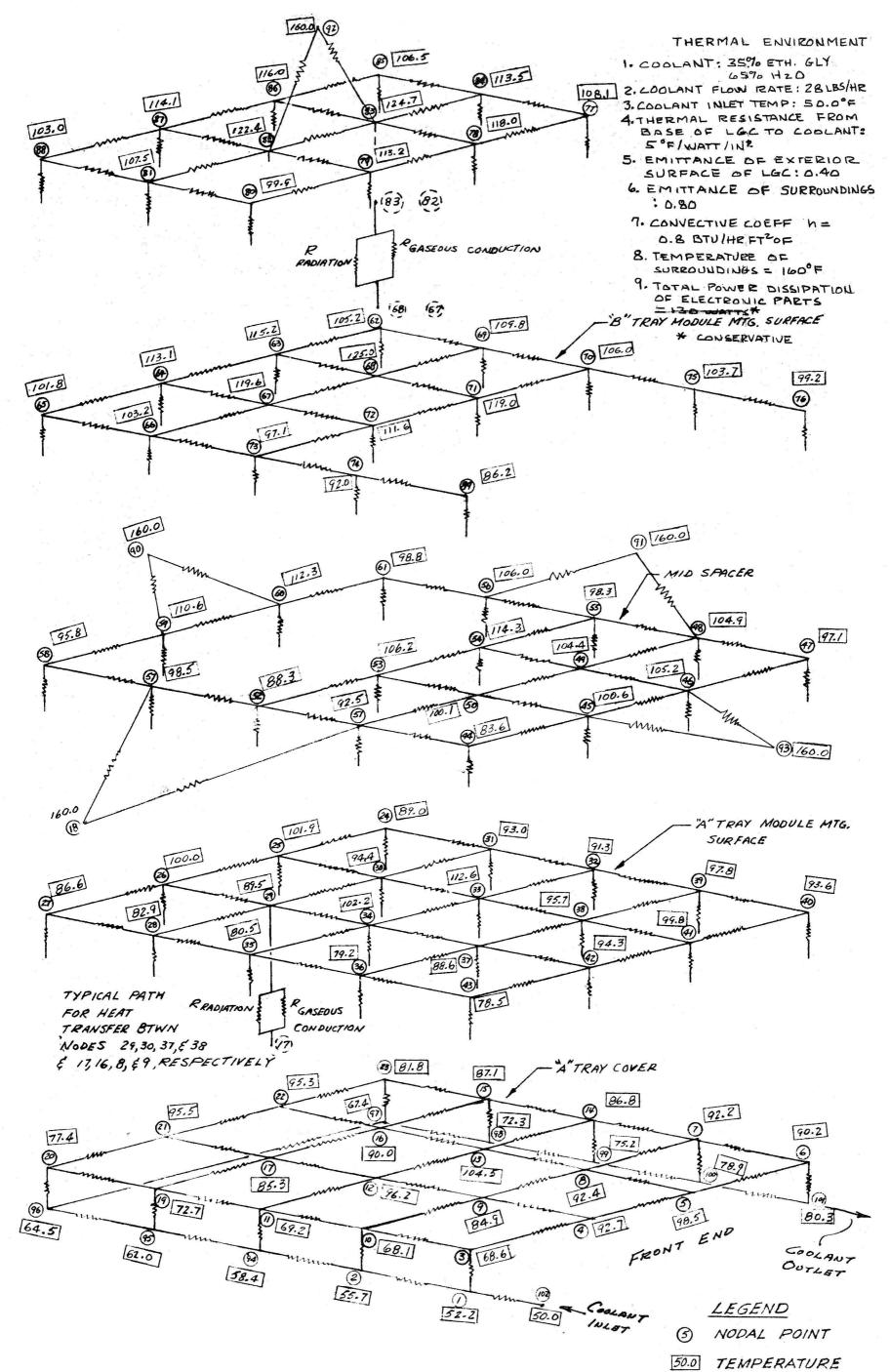

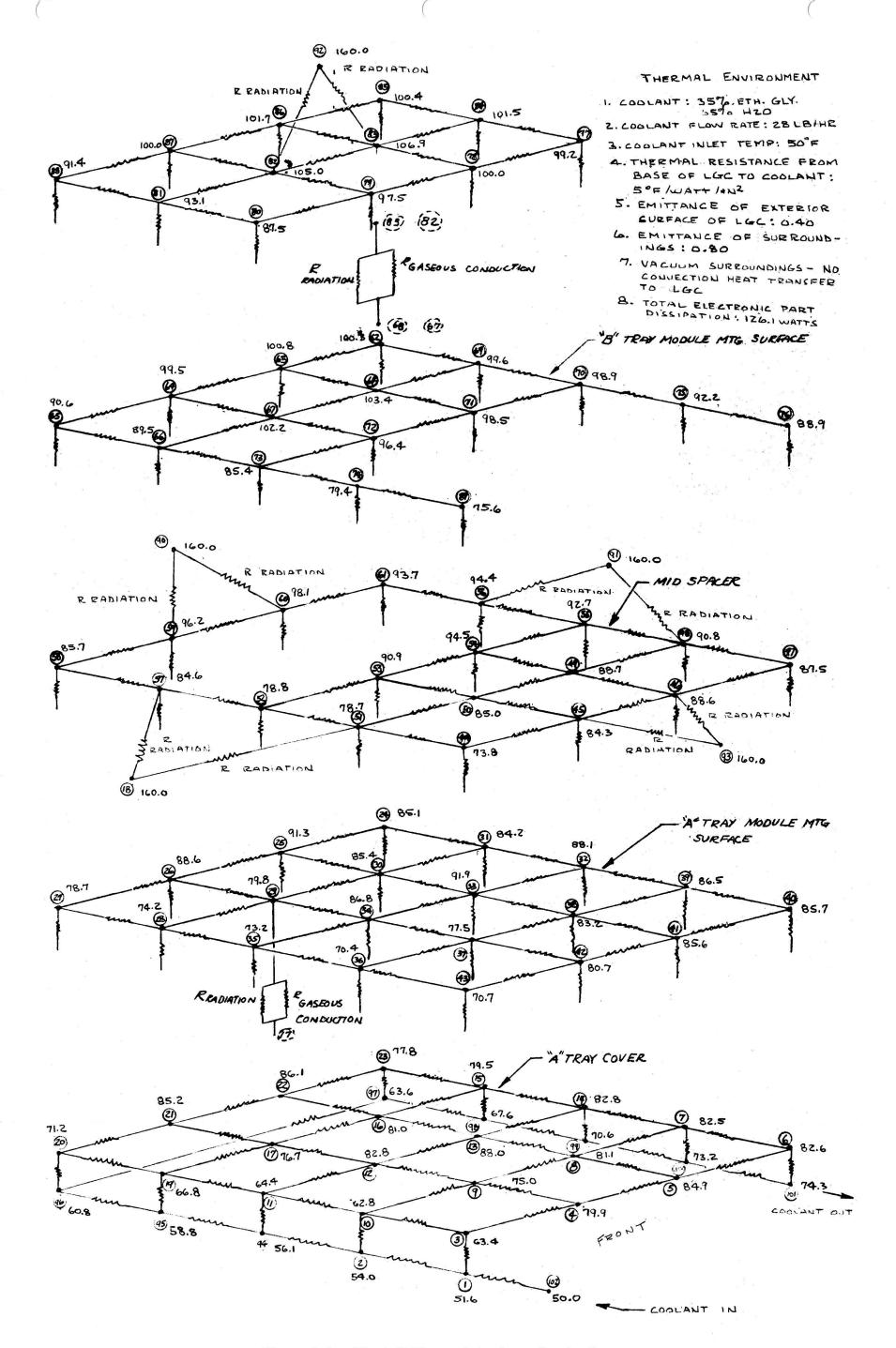

|         | 2.2.3 Thermal                             | 2-11 |

|         | 2.2.4 Module Interconnections             | 2-12 |

|         | 2.3 Power Supply                          | 2-17 |

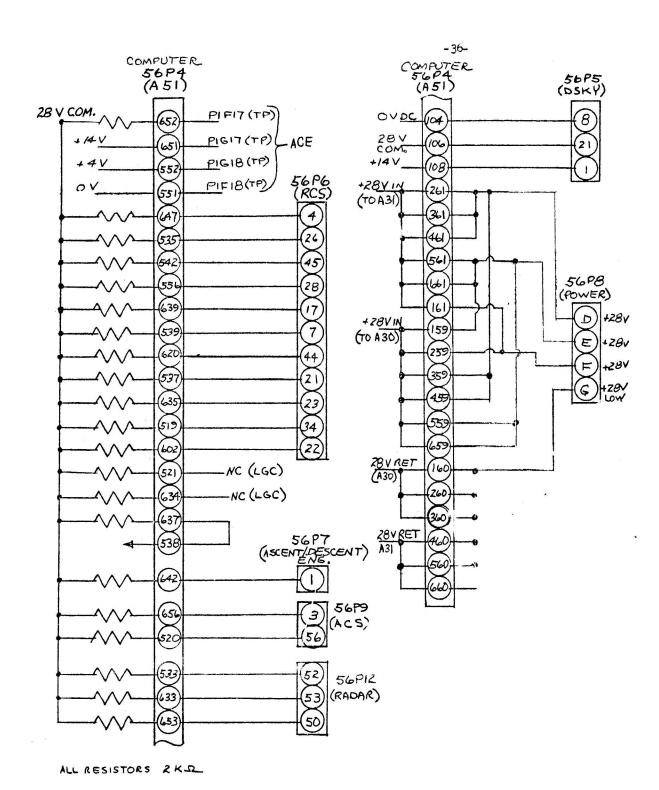

|         | 2.3.1 Power Distribution and Grounding    | 2-17 |

|         | 2.3.2 Power Supply Circuits               | 2-18 |

|         | 2.4 Logic                                 | 2-21 |

|         | 2.4.1 Noise Margin                        | 2-21 |

|         | 2.4.2 Timing Margin                       | 2-23 |

|         | 2.4.3 Blue Nose                           | 2-25 |

# TABLE OF CONTENTS (contd)

| SECTION | TITLE                                              | PAGE |

|---------|----------------------------------------------------|------|

| II      | 2.4.4 Ring Counter                                 | 2-25 |

|         | 2.4.5 Module A18 Standby Flip-Flop                 | 2-25 |

|         | 2.4.6 Standby Indicator                            | 2-25 |

|         | 2.5 Erasable Memory                                | 2-26 |

|         | 2.5.1 Mechanical Design                            | 2-26 |

|         | 2.5.2 Magnetic Design                              | 2-26 |

|         | 2.5.3 Memory Circuits                              | 2-32 |

|         | 2.6 Fixed Memory                                   | 2-33 |

|         | 2.6.1 Mechanical Design                            | 2-33 |

|         | 2.6.2 Fixed Memory Circuits                        | 2-33 |

|         | 2.7 Oscillator                                     | 2-35 |

|         | 2.8 Alarm Circuits                                 | 2-36 |

|         | 2.8.1 Voltage Alarm                                | 2-36 |

|         | 2.8.2 Oscillator Alarm                             | 2-36 |

|         | 2.8.3 Scalar Alarm                                 | 2-37 |

|         | 2.8.4 MYCLMP Circuit                               | 2-37 |

|         | 2.8.5 Warning Integrator                           | 2-39 |

|         | 2.8.6 Double Frequency Scalar Alarm                | 2-39 |

|         | 2.8.7 5 VDC Source                                 | 2-40 |

|         | 2.9 Computer Interface                             | 2-40 |

|         | 2.9.1 Signal Distribution and Grounding            | 2-40 |

|         | 2.9.2 The "A" Circuit                              | 2-41 |

|         | 2.9.3 The "C" Circuit                              | 2-41 |

|         | 2.9.4 The "XT" Circuit                             | 2-41 |

| III     | DISPLAY AND KEYBOARD (DSKY)                        | 3-1  |

|         | 3.1 Mechanical Design                              | 3-1  |

|         | 3.1.1 Indicator Driver Module (IDM), Power Supply  |      |

|         | Module (PSM), and Keyboard Module                  | 3-1  |

|         | 3.1.2 Digital Indicator Light (Electroluminescent) | 3-2  |

|         | 3.1.3 Indicator Alarm Light (Incandescent)         | 3-2  |

|         | 3.1.4 Push-Button Switches                         | 3-2  |

|         | 3.1.5 Structure                                    | 3-2  |

|         | 3.1.6 Environmental Testing                        | 3-3  |

|         | 3.2 Thermal                                        | 3-3  |

|         | 3.3 Indicator Driver Modules                       | 3-7  |

|         | 3.4 Power Supply Module                            | 3-9  |

|         | 3.5 Electroluminescent Panels                      | 3-10 |

# TABLE OF CONTENTS (contd)

| SECTION      | TITLE                                                        | PAGE |

|--------------|--------------------------------------------------------------|------|

| IV           | PIECE PARTS                                                  | 4-1  |

|              | 4.1 Flight Specifications                                    | 4-1  |

|              | 4.2 Integrated NOR Gate (1006321, 1006394)                   | 4-2  |

|              | 4.3 Multilayer Boards (100365)                               | 4-3  |

|              | 4.4 Malco Pins (1006781, 1006782)                            | 4-5  |

|              | 4.5 Thermistor (1006291)                                     | 4-5  |

|              | 4.6 Variable Inductor (1006324)                              | 4-5  |

|              | 4.7 Relays (1006282, 1006304, 1010784)                       | 4-6  |

|              | 4.7.1 Contamination                                          | 4-6  |

|              | 4.7.2 Open Coils                                             | 4-6  |

|              | 4.7.3 Shorts                                                 | 4-7  |

|              | 4.8 Electroluminescent Panels (1006315)                      | 4-7  |

|              | 4.9 Switch (1010901-2)                                       | 4-7  |

|              | 4.10 "Wire-Wrap" Wire (1006376)                              | 4-7  |

|              | 4.11 Tape Wound Core (1006320)                               | 4-8  |

|              | 4. 12 Crystal (1006847)                                      | 4-8  |

|              | 4. 13 Transistors and Diodes (1006323, 1006310, and 1006751) |      |

|              | 4. 14 Audio Transformer (1010291)                            | 4-9  |

|              | 4. 15 Resistors (1006750, 1006760, 1006714, 1006712,         | 4-9  |

|              | 1006788, 1006802)                                            | 4.0  |

|              | 4. 16 Capacitors (1006755, 1006777, 1006793)                 | 4-9  |

|              | 4. 17 Inductors (1006327, 1006325, 1010406)                  | 4-9  |

|              | 4. 18 Power Inductor (1006328)                               | 4-9  |

|              | 4. 19 Transformers (Pulsed) (1006319, 1006293)               | 4-9  |

|              | 1. 10 11 and 101 mers (1 dised) (1000519, 1000295)           | 4-9  |

| $\mathbf{v}$ | TESTING                                                      | 5-1  |

|              | 5.1 Qualification Testing                                    | 5-1  |

|              | 5. 1. 1 Computer                                             | 5-1  |

|              | 5. 1. 2 Modules                                              | 5-2  |

|              | 5. 1.3 Parts Qualification                                   | 5-2  |

|              | 5.2 Acceptance Testing                                       | 5-3  |

|              | 5. 2. 1 Computer                                             | 5-3  |

|              | 5.2.2 Modulos                                                |      |

#### AC ELECTRONICS DIVISION

# GENERAL MOTORS CORPORATION

# TABLE OF CONTENTS (contd)

| SECTION | TITLE                              | PAGE |

|---------|------------------------------------|------|

| VI      | DOCUMENTATION                      | 6-1  |

|         | 6.1 Interface Control Documents    | 6-1  |

|         | 6.2 Failure Reporting              | 6-2  |

|         | 6.3 Logic Drawings and Wire Lists  | 6-3  |

|         | 6.4 System Specifications          | 6-3  |

|         | 6.5 Programming Manual             | 6-5  |

| VII     | PROGRAMS                           | 7-1  |

|         | 7.1 Mission Programs               | 7-1  |

|         | 7.1.1 Programming Restrictions     | 7-1  |

|         | 7.1.2 Interrupt Programs           | 7-2  |

|         | 7.1.3 Self-Test                    | 7-2  |

|         | 7.1.4 Restart                      | 7-3  |

|         | 7.2 Simulator                      | 7-3  |

|         | 7.2.1 Apollo Program Verification  | 7-4  |

|         | 7.2.2 Conclusions                  | 7-5  |

|         | 7.3 Factory Test Programs          | 7-6  |

| VIII    | MISCELLANEOUS                      | 8-1  |

|         | 8.1 Coupling Data Unit (CDU)       | 8-1  |

|         | 8. 1. 1 Logic Circuits             | 8-1  |

|         | 8.1.2 Mechanical Design            | 8-3  |

|         | 8. 1. 3 Power Supply               | 8-3  |

|         | 8.1.4 Grounding                    | 8-3  |

|         | 8.2 Ground Support Equipment (GSE) | 8-4  |

|         | 8.2.1 Overvoltage Protection       | 8-4  |

|         | 8.2.2 Buffer Box                   | 8-4  |

|         | 8.2.3 Temperature and Monitors     | 8-5  |

|         | 8.2.4 Marginal Testing             | 8-5  |

|         | 8.3 Manufacturing                  | 8-5  |

|         | 8.3.1 Selection of Nominals        | 8-5  |

|         | 8.3.2 Hand Tools                   | 8-6  |

|         | 8.3.3 Welding to Multilayer Boards | 8-6  |

# TABLE OF CONTENTS (contd)

| SECTION      | TITLE                                                                                                                                                                                                                                                                                                                                                                                                                                           | PAGE |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| IX           | MIT COMMENTARY                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|              | 9.1 Documentation 9.1.1 General 9.1.2 Interface Control Documents 9.2 Computer Testing and Qualification 9.2.1 Parts 9.2.2 Modules 9.2.3 Computer 9.3 Design 9.3.1 Worst-Case Philosophy 9.3.2 Logic 9.3.3 Erasable Memory 9.3.4 Fixed Memory 9.3.5 Power Supply 9.3.6 Alarms and Logical Design Items 9.3.7 Interfaces 9.3.8 DSKY 9.3.9 Overall Mechanical Design 9.3.10 Coupling Data Unit 9.4 Programs 9.5 Miscellaneous 9.6 Proposed Action |      |

| APPENDIX A   | POWER SUPPLY                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| APPENDIX B   | COUNTER FAIL REDESIGN                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| A PPE NDIX C | NOISE MARGIN ANALYSIS                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| A PPE NDIX D | LOGIC OVERLOADS                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

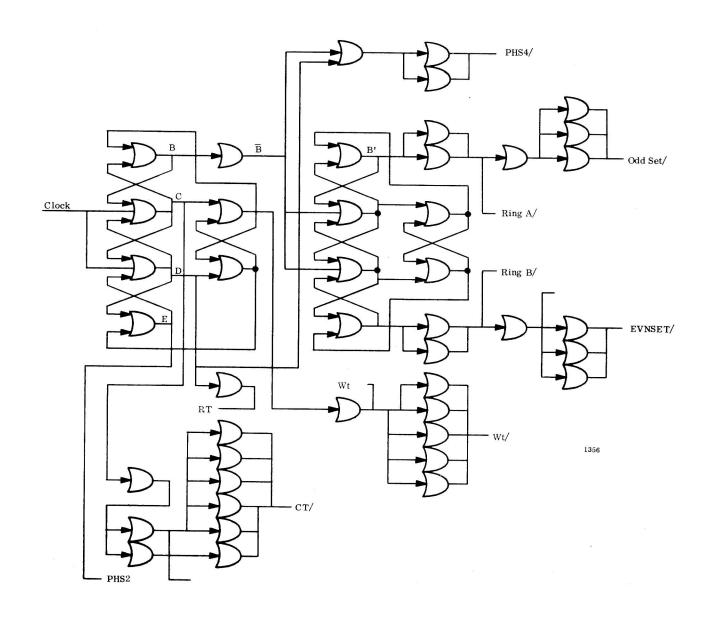

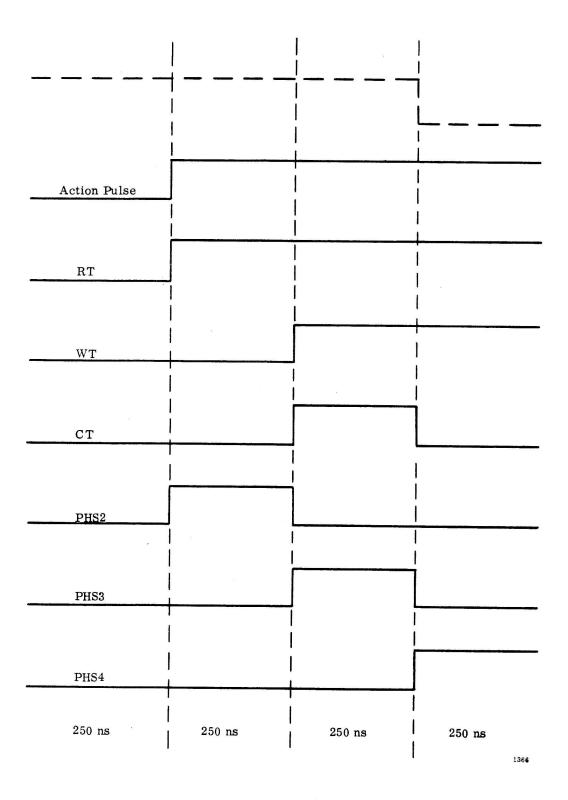

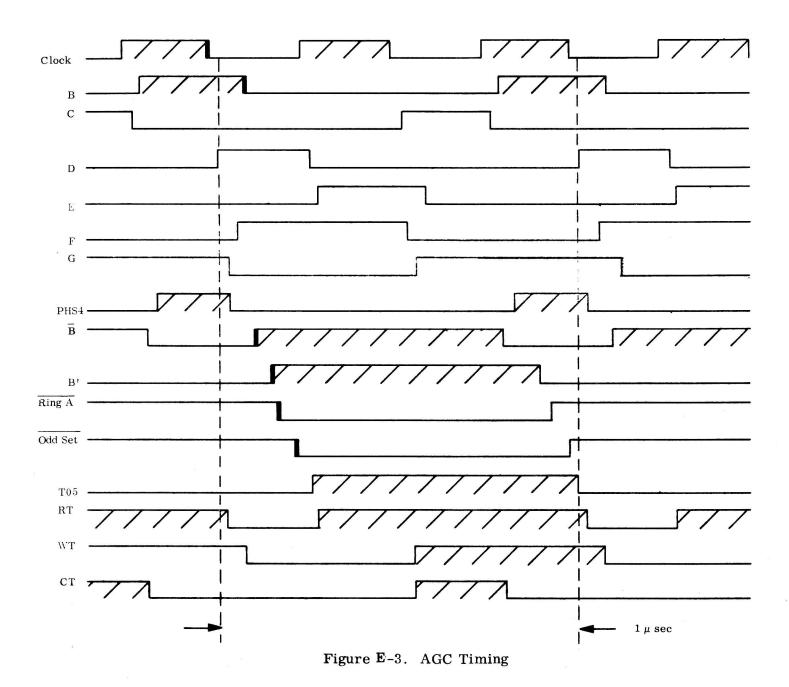

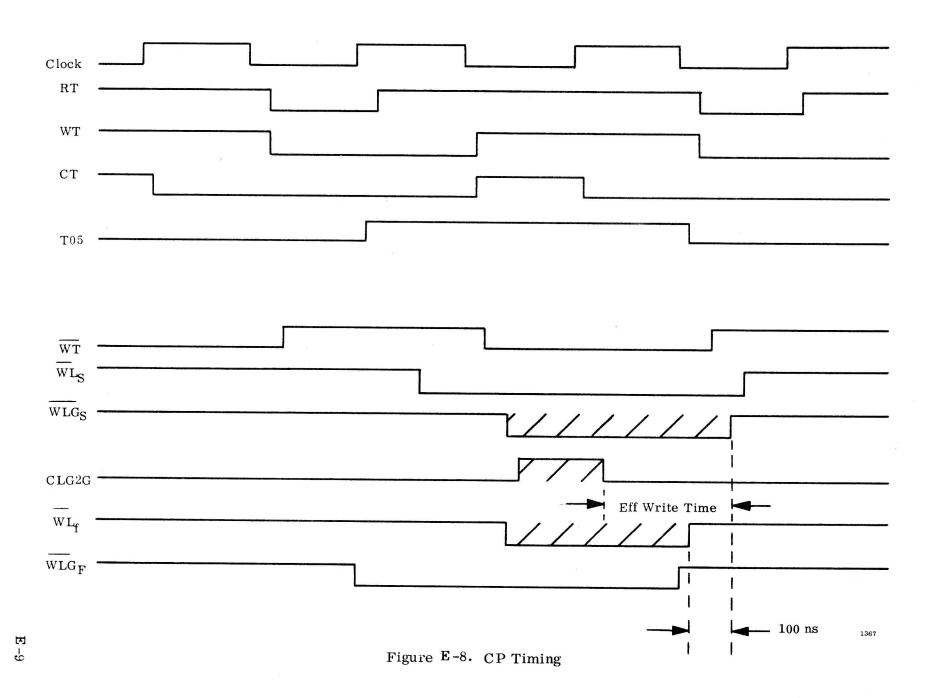

| A PPENDIX E  | TIMING SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

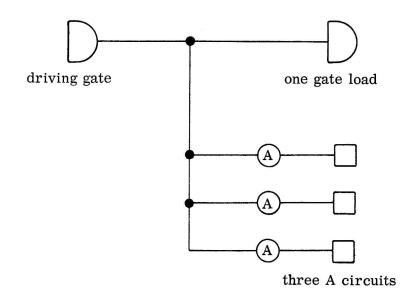

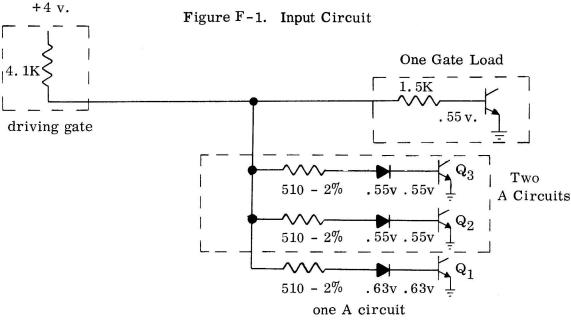

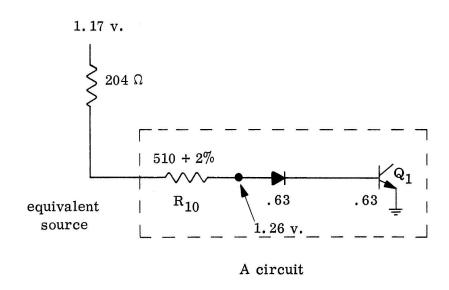

| APPENDIX F   | INTERFACE CIRCUITS                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

DSKY RELAY CIRCUIT ANALYSIS

WORK TO BE ACCOMPLISHED

APPENDIX G

APPENDIX H

# IX COMMENT BY MIT ON COMMITTEE FINDINGS

| 9.1    | DOCUMENTATION                        | 9-2           |

|--------|--------------------------------------|---------------|

| 9.1.1  | General                              | 9-2           |

| 9.1.2  | Interface Control Documents (ICD's)  | 9-2           |

| 9.2    | TESTING AND QUALIFICATION            | 9-4           |

| 9.2.1  | Parts                                | 9-4           |

| 9.2.2  | Modules                              | 9-6           |

| 9.2.3  | Computers                            | 9-6           |

| 9.3    | DESIGN                               | 9-12          |

| 9.3.1  | "Worst Case" Design Philosophy       | 9-12          |

| 9.3.2  | Logic                                | 9-13          |

| 9.3.3  | Erasable Memory                      | 9-14          |

| 9.3.4  | Fixed Memory                         | 9-17          |

| 9.3.5  | Power Supply                         | 9 <b>-</b> 18 |

| 9.3.6  | Alarms and Logical Design Items      | 9-18          |

| 9.3.7  | Interfaces                           | 9-22          |

| 9.3.8  | Displays and Keyboard (DSKY)         | 9-26          |

| 9.3.9  | Overall Computer Design (Mechanical) | 9-27          |

| 9.3.10 | CDU                                  | 9-28          |

| 9.4    | PROGRAMMING                          | 9-29          |

| 9.5    | ERASABLE MEMORY MECHANICAL DESIGN    | 9-31          |

| 9.5.1  | Summary                              | 9-31          |

| 9.5.2  | Detailed Discussion                  | 9-31          |

| 9.6    | MIT PROPOSED ACTION                  | 9-43          |

| 9.6.1  | Logic Circuits and Design            | 9-43          |

| 9.6.2  | Power Supply                         | 9-43          |

| 963    | Interfaces                           | 9-43          |

| 9.6.4  | Erasable Memory       | 9-43 |

|--------|-----------------------|------|

| 9.6.5  | Rope Memory           | 9-44 |

| 9.6.6  | Oscillator            | 9-44 |

| 9.6.7  | Alarms                | 9-44 |

| 9.6.8  | Mechanical            | 9-44 |

| 9.6.9  | Computer P.S.         | 9-44 |

| 9.6.10 | Qualification Testing | 9-45 |

APPENDIX H

# TABLE OF CONTENTS (contd)

| SECTION      | TITLE                                                                                                                                                                                                                                                                                                                                                                                                                                           | PAGE |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| IX           | MIT COMMENTARY                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|              | 9.1 Documentation 9.1.1 General 9.1.2 Interface Control Documents 9.2 Computer Testing and Qualification 9.2.1 Parts 9.2.2 Modules 9.2.3 Computer 9.3 Design 9.3.1 Worst-Case Philosophy 9.3.2 Logic 9.3.3 Erasable Memory 9.3.4 Fixed Memory 9.3.5 Power Supply 9.3.6 Alarms and Logical Design Items 9.3.7 Interfaces 9.3.8 DSKY 9.3.9 Overall Mechanical Design 9.3.10 Coupling Data Unit 9.4 Programs 9.5 Miscellaneous 9.6 Proposed Action |      |

| APPENDIX A   | POWER SUPPLY                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| APPENDIX B   | COUNTER FAIL REDESIGN                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| APPENDIX C   | NOISE MARGIN ANALYSIS                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| A PPE NDIX D | LOGIC OVERLOADS                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| A PPENDIX E  | TIMING SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| APPENDIX F   | INTERFACE CIRCUITS                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| APPENDIX G   | DSKY RELAY CIRCUIT ANALYSIS                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

WORK TO BE ACCOMPLISHED

#### 0. PRELIMINARY MIT/IL COMMENTS

#### 0.1 RESPONSIBILITIES

The design review and examination of the Apollo Guidance System Block II Computer reported herein was intended to reflect only on the technical status of the design and associated supporting operations and documentation. Nowhere in the body of this report should the responsibility for elements of the design under criticism or praise be apparent. The responsibilities are actually shared and they overlap among the principal participants somewhat as follows...

Manned Spacecraft Center of NASA -- Responsible for defining the basic requirements for the design, providing contractual support to accomplish the effort, and passing upon the acceptability of the design.

Instrumentation Laboratory of MIT -- Responsible for the basic design of circuits, hardware, and packaging and the integration of the computer and its functions into the rest of the G&N equipment, the spacecraft, and the ground test facilities.

AC Electronics Division of General Motors -- Responsible for the administration of the production of the computer and the exercise of the qualification testing, acceptance testing, and integrated guidance system testing.

Raytheon -- Responsible for the manufacture of the computer and for the detailed design and design analysis of portions of the equipment.

Space and Information Division of North American Aviation -- Responsible for the integration of the guidance system (with the computer) into the command module, the generation of CM interface documents, and the identification of the interfacing spacecraft circuits, installations constraints, and spacecraft environment.

Grumman Aircraft Engineering Corporation -- Responsible for the integration of the guidance equipment (with the computer) into the lunar excursion module, the generation of LEM interface documents, and the identification of the interfacing spacecraft circuits, installation constraints, and spacecraft environment.

#### 0.2 CONSTRAINTS ON DESIGN

As items of the review are discussed in the body of the report, it will be apparent that no effort was made to provide the justifications or qualifications which led to design features which on some other less confined basis were not "best possible". The design of equipment such as this naturally is the result of tradeoffs among a multitude of conflicting constraints. Some of the more important considerations are outlined here so as to provide a background of the design environment and circumstances.

Schedule -- In October 1963, the basic configuration of the Block II G & N system was substantially identified following negotiations with MSC. However, in June 1964, some basic decisions were made by MSC which lead to considerable changes in the configuration and functions. In particular, the redundant computer was eliminated. the computer was given the task of vehicle stabilization (the digital autopilot) and the computer was required to provide the several new wide bandwidth interfaces with the spacecraft. During this period a sequence of "implementation meetings" among MSC, the spacecraft contractors, and MIT was held to try and define the Block II CM and LEM requirements. A basic outline of the computer configuration definition became available late in 1964. Negotiations on the electrical and mechanical characteristics with the spacecraft contractors offered enough difficulty so that the last computer electrical interface control document was not signed until February 1965, and the last computer mechanical ICD was not signed until July 1965. Meanwhile, in order to meet the needs of the program, a substantially complete release of the computer design was made in the Spring of 1965. Since that time much of the activity has been in making those necessary design changes which became identified as mandatory as a result of problems with the design or as a result of newly identified requirements. The latest requirement changes of note occurred on 13 January 1966, at a LEM "Critical Design Review". This review identified a new interface and new function for the computer ... a three-axis minimum impulse attitude control based upon commands from discrete switches on the rotational hand controllers. In summary, many more optimum designs and many desirable features were deliberately bypassed in order to meet the stringent schedule constraints.

Volume -- Early in the series of implementation meetings in the Summer of 1964, a space for installation of the computer in the command module was negotiated with North American. Although during the implementation meeting series a much more powerful computer was identified and furthermore, that a requirement for moisture proofing resulting in the hermetic sealing of the case was identified, no added volume in the installation was provided. Many compromise decisions were made in the design as a result of the most limited volume allowance.

<u>Miscellaneous</u> -- Other constraints which influenced decisions which might be cited are:

- 1. The extreme effort to hold and reduce the weight of the computer, particularly in the LEM.

- 2. The extreme effort to hold down electrical power consumption.

- 3. The requirement to make physically identical both the computers in the LEM and CM and also to make physically identical the DSKY in LEM with both DSKY locations in the CM. Unfortunately, the physical environment in these two spacecraft is significantly different.

4. The practical desire to save funds and the consequent shortcuts in development testing, comparison designs, etc. This meant that prototype and early production computers could not be made available as desired to provide the early experimental identification of problems and verification of design changes.

# 0.3 CRITIQUE OF COMMITTEE REPORTS RESULTS

The team of computer specialists assembled to make this Block II computer review was made up of members from AC and Raytheon. The substance of their findings is given in Section I through Section VIII and in the appendices. MIT has taken exception with many of these findings and reports its position and justification in Section IX.

#### I INTRODUCTION AND SUMMARY

#### 1.1 BACKGROUND

This review of the Apollo guidance computer design was performed at the request of the NASA Manned Spacecraft Center. The following is a quote from contract change authorization to AC Electronics.

"Description of Change: It is requested that the contractor immediately initiate a complete design review of the electrical and mechanical design margins to insure adequate performance during the lunar landing mission. MIT has been notified that AC Electronics will be conducting this design review and have been requested to provide all available information regarding design criteria, analysis, and testing to date.

Justification for Change: Recently the Block II and LEM computers have had numerous design problems. The blue nose logic situation, the refusal of computer 601 to operate on the cold plate and the apparently inadequate timing margins (based on tests on computers PC-2 and 201) have given rise to doubts regarding the adequacy of the electrical and mechanical margins throughout the computer.

In addition, this authorization suggested that the computer review should be accomplished by June 1, 1966.

In response to this NASA request, a team of computer specialists was convened. Team members from the AC Electronics Digital Computer Laboratory in El Segundo, from the AC Electronics engineering departments in Milwaukee, and from the Raytheon Co. Space and Information Systems Division engineering departments began the requested design review. This report covers the initial findings of this team and spans approximately the first two months of the design review. The review has not been completed, but the number of problem areas discovered to date warrants a fairly complete discussion of the review and the problems at this time.

#### 1.2 SCOPE OF THE INVESTIGATION

This report describes topics ranging considerably beyond the Apollo guidance computer hardware and its electrical and mechanical margins. The review committee realized that "to insure adequate performance during the lunar mission", it would be necessary to investigate more than the design of the computer, per se. Therefore, the committee has also looked into the designs of those equipments which are immediately peripheral to the computer, and into the manufacturing techniques, the testing methods, and the documentation required to realize these designs as functioning elements of a navigation system.

It may at first seem strange that our review did not include the subject of computer reliability. A typical reliability model for an irredundant computer is constructed by counting the piece parts and ascribing failure rates to each part. Little can be done to affect the reliability calculated from such a model once the basic logic structure and electronic parts have been selected. The review has been much concerned with the overall computer dependability, but not in the sense of the conventional reliability model. The review has concentrated on areas of possible design difficulty which would lead to degraded operation rather than to spontaneous failure of the computer components.

#### 1.3 METHOD OF INVESTIGATION

At the outset of the investigation a set of ground rules were developed to guide the committee in performing the design review. These ground rules were as follows.

- 1. This review is an effort to assess the design integrity of the Apollo computer. Cost and schedule impact will not normally be considered as design criteria.

- 2. The review team will not attempt to assign responsibility for any deficiencies which may be illuminated.

- 3. The review team will not perform the designs, but will suggest approaches and techniques, if they are apparent.

- 4. The review team will not assign the design tasks which it recommends.

- 5. MIT will be kept apprised of the significant team findings by the AC Electronics Program Director, or his designee.

The committee has attempted to judge the technical excellence of the various subject matters investigated irrespective of the organization responsible for the particular topic. The design review was conducted as though the computer were critical to the Apollo missions and essential to the safety of the astronauts. That these assumptions may not be true can completely negate the findings with regard to the design adequacy or inadequacy, and certainly will affect the ultimate decision as to the design changes which are put into the computer.

Ordinarily, an investigation of this type would begin with a review of the computer specification and any other documents describing the functional requirements which the system reflects on the computer. The computer design would then be scrutinized and compared with the requirements of the defining documents. Unfortunately, in this case the procurement specifications for the computer and the computer modules do not exist. The functional requirements were apparently determined during the

series of implementation meetings, and the review committee has not read the minutes of these meetings. As a result the review has been limited to those properties of the computer, such as the logic design, circuit design, and mechanical design, which can be judged against good practice applying sound judgment. It was necessary for the review team to accept, without question, many of the basic parameters of the computer, such as the instruction set, the memory capacities, operating speeds, and input-output functions. This means that even if the entire mechanical and electrical designs are corrected as recommended by the committee, the ability of the computer to perform the lunar landing mission may not have been completely guaranteed.

The NASA request was for a review of the Block II and LEM computer designs. The production version of these computers begins with one designated C-1 which is different from all previous prototype and production computers in several significant areas. These changes include some new logic design, the use of the expander gate, new multilayer circuit boards, new memory drivers, new erasable memory mechanical design, new power supply circuits, new electroluminescent panels, new materials and finishes for the computer proper. This first production computer is scheduled for delivery to AC 14 days after NASA had hoped to receive the final review report. The second production computer, C-2, is scheduled to fly. These tight production and flight schedules, combined with many new designs and with further changes as a result of this design review, present a very difficult situation.

Since the design of the first production Block II computer is not complete and since the design criteria documents for this series of computers are largely nonexistent, it was necessary to adopt an oblique approach to the design review. We have, of course, reviewed those documents and those designs which are available for the Block II system. We have also reviewed those designs, documents, and tests of the Block I and Block 100 computers which appear to be pertinent to the Block II design. As a result of this we have inadvertently uncovered some possible difficulties with the flyable computers. Since some of these computers will fly in manned as well as unmanned spacecraft, the review committee feels an obligation to bring these design deficiencies to light. This will be done by publishing a special report on the specific subject of the Block I-100 findings. That report will follow this one as quickly as we can arrange it. It should be emphasized, however, that a thorough investigation of the Block I-100 computers has not been done by this committee. Possibly the most significant recommendation in this regard would be the establishment of a special flight readiness review committee for these earlier systems.

In order to accomplish this review, the committee en masse interviewed members of the AC Electronics computer integration group in Milwaukee and then moved to Boston for four weeks. During the first two weeks, interviews were held with the responsible Raytheon engineers from the checkout, testing, and design groups. Of the next two weeks, approximately one week was spent interviewing the original designers from MIT. The remaining period of time covered by this report has been

spent by the committee members individually reviewing the work presented by the engineers interviewed, preparing this report, and performing detailed individual reviews of specific areas of the computer design.

#### 1.4 CATEGORIES OF FINDINGS

Findings of the review team are categorized later in this report into four major groups as follows:

#### Group A: Adequate

This category applies to those designs which have been reviewed by the committee and which have been found to have adequate design margins.

#### Group B: Marginal

This category applies to those designs which are considered to be inadequate but whose performance is not vital to the success of the mission, or whose inadequacies will manifest themselves only under some worst, worst combination of environments considered to be unrealistic.

#### Group C: Inadequate

This category includes those designs and situations which have been reviewed and have been found to be unsatisfactory. These designs or situations must be corrected at any cost.

#### Group D: Indeterminate

This classification includes those subjects which have not been successfully placed into one of the three categories above. In some cases the indeterminacy was caused by the committee's inability to conduct a thorough review in the elapsed time, and in some cases it has been caused by the lack of design information. Each item in this category must be studied further until it can be placed in one of the above categories.

In subsequent sections of this report the category applying to each numbered paragraph will be indicated in parentheses behind the paragraph title. In some cases the committee has felt that it was impossible or inappropriate to apply one of the above four categories to a specific paragraph, and therefore no such indication is given.

There is, of course, another category which contains all of those designs, documents, and situations which have not been reviewed by the committee at all. The committee has tried to be exhaustive in its review of the Apollo guidance computer but it has not been able to work at every aspect of that computer, its manufacture, testing, and documentation. Unless a particular subject matter is discussed in this report, it is not safe to assume that it is adequate, but should be placed in Category D.

#### 1.5 SUMMARY OF FINDINGS

This section is intended to provide a brief summary of the more important findings of the design review as it has been accomplished so far. The recommended actions are discussed in Paragraph 1.6. There were 17 working members of the Tiger Team, and each would undoubtedly have provided a different summary of the work which has been reviewed, even though there has been general unanimity in the assignment of the categories A, B, C, and D to the specific topics which are discussed in the remaining sections of this report. There has been some difference of opinion as to the relative urgency of correcting those designs which are inadequate and of pursuing those which are indeterminate. This section is organized in such a way as to convey the urgency as it is viewed by the chairman of the review committee. The more important topics are discussed first, topics of lesser importance are discussed next, etc.

Perhaps the most significant fault uncovered to date in the Apollo guidance computer project is the lack of adequate documentation supporting the Block II computer and its design. The review committee has not been able to find a satisfactory functional description of the task which the computer is expected to perform in the command module, although such a description does exist in a functional interface document for the Lunar Excursion Module. Many documents exist which describe the computer design as it presently is, but these documents are informal and uncontrolled. The formal documents contain significant blanks and significant inconsistencies in the data.

A second feature of the Apollo guidance computer project which is regarded as dangerous and in need of correction is the testing philosophy. There is still vacillation with regard to the probable content of the computer qualification test document and there is some danger that document will not be approved in its final form by the time the first qualification test article is delivered by Raytheon. It is the committee's understanding that this test document will, in essence, provide a qualification test of the computer subsystem to the lunar excursion module mission profile and will qualify the entire guidance and navigation system to the command module profile. This is an unsatisfactory philosophy, since the computer must function in either module, and since adequate self-test programs cannot be performed by the computer while it is also providing control and tests of the guidance and navigation system.

Qualification testing at the module level is not recommended. The present environmental test levels are significantly below the levels which the modules will see in the actual computer during its qualification test, and during the acceptance test, and probably in flight. The available test equipment does not exercise the modules thoroughly enough to prove that they will operate with satisfactory margins in the

computer. Rather than invest in the more complex support equipment required to provide adequate exercising of the modules, it is recommended that a better qualification test of the entire computer be provided. With the proper program in the computer memory, the individual modules can be thoroughly exercised. It should be stressed, however, that this program must be very carefully designed to provide a proper exercise.

It is the committee's understanding that the computer qualification test will not include a test for electromagnetic compatibility. This could have serious ramifications during system integration. The present interface control documents do not provide satisfactory guarantees that the various subsystems will not mutually interfere with one another. If a test of the subsystem electromagnetic compatibility is not provided, then this test must be provided at the system level. There is danger, of course, that the test at the system level will not uncover problems early enough that they can be corrected in subsequent redesigns of the subsystem. Therefore, EMI testing at the computer level is recommended.

Qualification of the piece parts is lagging and this matter is considered most urgent. Failure of the parts to pass the qualification test should require one of three actions: a) the parts can be designed out of the system, b) the parts can be subjected to a special screen at receiving inspection to uncover the specific weaknesses which are turned up during the part qualification test, or c) the parts can be procured from a different vendor.

The present acceptance testing procedures are deemed to be inadequate because they do not subject the modules to a satisfactory workmanship test. If the present acceptance tests are carried out, the final flight program ropes will not see vibration until the Apollo system leaves the launching pad. Furthermore, the present acceptance test does not provide for measuring the electrical operating margins of the ropes and therefore provides no assurance that the marriage between a specific set of flight ropes and the electronics in the computer (already installed in the spacecraft) will be successful.

With regard to acceptance testing of the rest of the computer modules, the philosophy presently advocated is adequate only if the currently planned black box level maintenance philosophy is strictly adhered to. Up to the present time, the committee has been unable to find any documentation which sets forth the maintenance philosophy. If, as the committee has recommended, the computer is sealed at the time of the final acceptance test, and if no one is permitted to break that seal and replace a module except in the factory, the present acceptance philosophy for the individual computer modules (except for the ropes as noted above) will provide adequate testing. However, this philosophy has the distinct disadvantage of making it impossible for the manufacturer of these modules to sell them off until they are installed in a computer. The maintenance and sparing philosophy for the computers needs to be examined carefully, to be set forth clearly, and to be enforced completely.

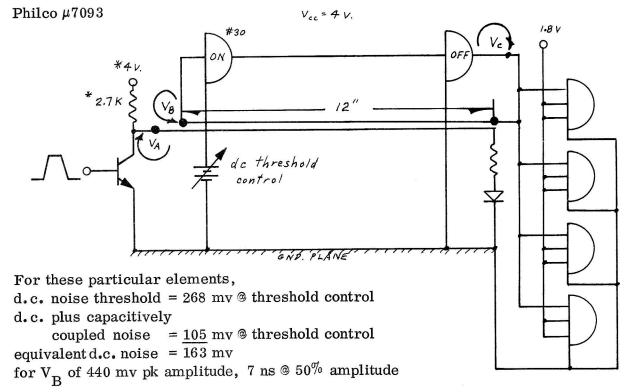

The logic and electrical design of the computer has not been done using a worst-case design philosophy. The committee recognizes that short of providing a completely new design, the problem of fixing up the present design is a very difficult one. It is unlikely that any set of recommended changes will absolutely guarantee a design which will work under all possible circumstances. It is the committee's opinion that the logic overloads must be fixed. Appendix C treats that topic in considerable detail and constitutes the committee's noise analysis. That analysis raises the question whether even fixing the logic overloads is sufficient. Certainly, the noise immunity is improved, but if the noise levels which the committee has seen in its laboratory experiments are actually realized in the operating computer, even a fan-out of five will not provide satisfactory margins. Basically, the answer is we simply do not know what noise margin exists between the tolerance of the circuits and the noise generated in the system.

There is some concern that the present design does not have adequate timing margins, and that it may not work over the temperature range. The review committee has seen no proof that the computer timing design is predictable or that bad timing situations cannot exist in production computers.

The erasable memory design has been questioned in two areas. Much concern has been expressed about the present mechanical design of the module. It is contrary to industry experience that such a module cannot be satisfactorily encapsulated. There is fear that if the present mechanical design is allowed to remain unchanged, wire breakage will result from fatigue of the wires due to the fact that the mass of encapsulation is not mechanically supported.

Electrical design data of the erasable memory is lacking. Paragraph 2.5 presents a discussion of the kinds of tests which are required in order to develop the necessary data for both RCA and EMI modules.

The design margins in the DSKY are certainly unsatisfactory. Mechanically and thermally the design is probably as good as could have been provided by anyone given the constraints which are present in the system. However, the basic decision to use the electroluminescent panels should be re-examined. It is these panels which require the relays which, in turn, have proven to be unreliable piece parts and have also been designed into an unsatisfactory circuit. The electroluminescent panels themselves have serious deficiencies, and have yet to pass their qualification tests. Suitable filamentary segmented displays have existed for some time and some have been qualified for use in military systems. Use of these devices would allow the troublesome relays and electroluminescent panels to be designed out of the system. Use of the incandescent segmented displays would probably require the DSKY to dissipate somewhat more power than it presently does. However, power consumption appears not to be as important today as it was a few years ago. The additional power

consumption will, of course, aggravate an already difficult thermal situation. If the incandescent lamps are used, it would be recommended that the DSKY be provided with a small amount of cooling fluid for the electrical modules.

With regard to the mechanical and thermal design of the computer, the situation appears to be tolerable, but considerable effort has been expended in trying to design a one-foot by two-foot cover which could contain the computer pressurization. There is apparently no firm requirement that the computer have internal pressurization, and there are several critical parts, such as the flight ropes and electrical connectors, which must necessarily be located outside the pressurization.

The use of the Malco pin within the computer structure can be tolerated only so long as field replacement of modules (other than ropes) is absolutely prohibited. The present, needless dissasembly and reassembly of the computer should be stopped, and it is recommended that the quality control man put a seal on the computer at the time of final assembly to prevent unnecessary exposure of the Malco pins to damage.

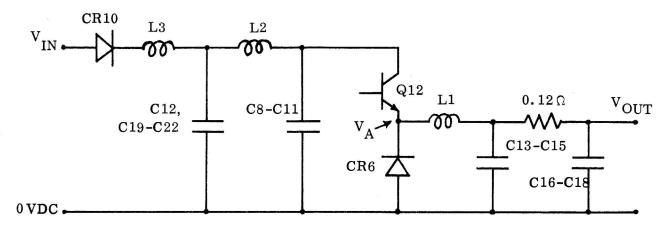

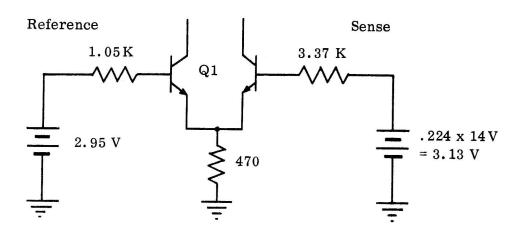

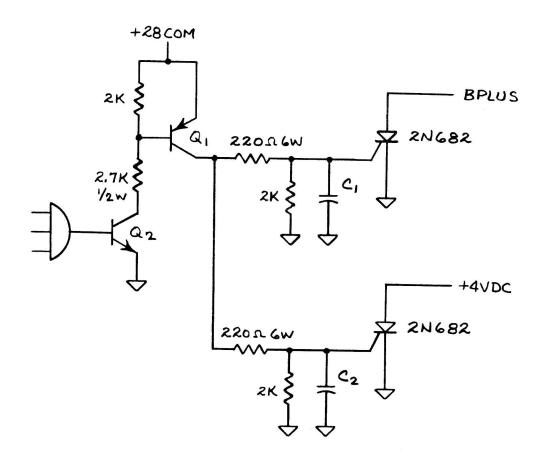

The voltage alarm philosophy has been criticized because the alarms fail to activate an overvoltage protection circuit. This circuit should be within the computer, but must at least be within the ground support equipment. Appendix A suggests that since the power supply itself has internal short-circuit protection, protection of the computer could be supplied by short-circuiting the output of the power supply. A typical circuit is suggested in that appendix.

The flight processing specifications for the piece parts have been given considerable attention by the review committee. That committee is not universally in agreement on all aspects of the problem, but there is general agreement that the flight processing does not seem to be accomplishing what it was intended to accomplish, since it is generally impossible to get the piece parts through these tests without waivers. Obviously, some changes should be made in the system. This is an area of considerable specialization and even those specialists called in by NASA and AC to help with these problems have been unable to agree on a recommended change to the system. The committee, lacking expertise in this particular art, is forced to defer to the review committee expert and accept the recommendations expressed in Paragraph 4.1

The multilayer boards have already been found to exhibit the usual unreliability associated with the conventional multilayer process. One can expect that perfectly excellent boards will be manufactured one day and subsequent production will be unusable. It is quite possible to provide better incoming inspection than is now given to these boards, and such an inspection process is discussed in Section 4.

The programmers place considerable reliance on the all-digital simulation to uncover problem areas in the computer program. The committee recognizes that this all-digital simulation is absolutely essential for program checkout, but such a simulation does not provide the necessary insight which can be gotten by an adequate analytical approach to some specific problems. The committee feels a general, vague apprehension about the ability of the computer to perform the necessary computations in real time under all conditions of loading on the program, and recommends that the counter increments and external interrupts be analyzed to insure that a worst-case buildup of these inputs will not degrade the system performance.

Many of the specification control documents against which the piece parts are purchased, are not satisfactory. In particular, the SCD covering the micrologic, both the dual and the expander gates, contains certain ambiguities, and does not contain satisfactory noise threshold requirements.

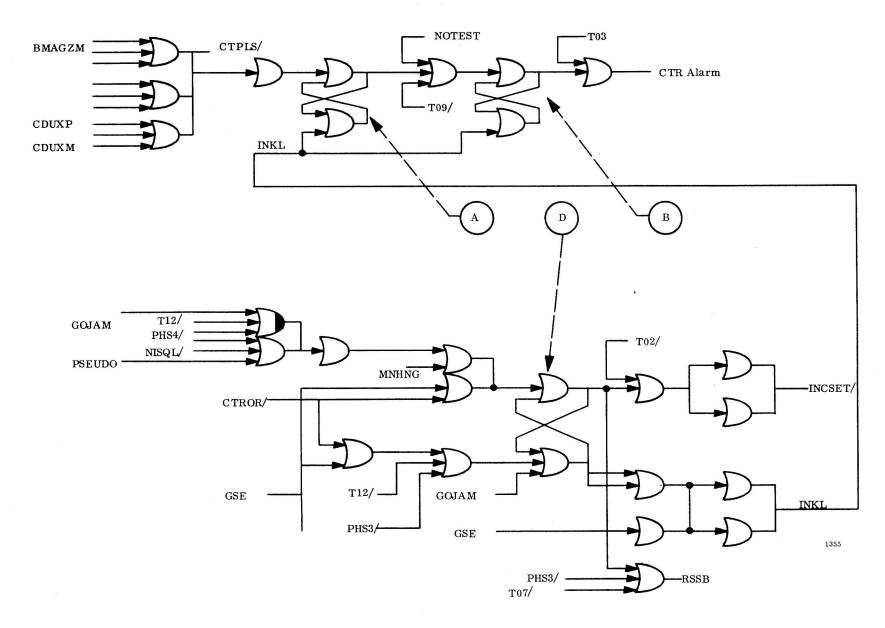

The logic design of the counter fail alarm is considered to be unsatisfactory, since it permits the interface to drop bits without detecting this loss of information. The counter increment analysis referred to previously may show that such a condition is impossible, in which case that aspect of the design would have to be reclassified as acceptable.

The computer power supply module specification allows an unnecessarily large amount of radio frequency noise on the output of the power supply. This noise will detract from the available noise margin of the logic. Adequate filtering and better placement of the parts within the power supply module could effectively reduce the high frequency noise by one or two orders of magnitude.

The standby flip-flop, according to the present logic design, can turn on the standby condition when the computer is first turned on. If the computer operation were momentarily interrupted by a power supply transient, and the computer came back on in the standby condition, some number of seconds must elapse before the astronaut can recognize what has happened and place the computer back in the operating mode. This appears to be a dangerous situation. In addition, the standby indicator is presently driven by logic operated directly from the flip-flop. As a result the light is not an indicator of the true status of the computer.

There are several aspects of the computer which are considered to be adequate, and those are indicated in the following sections of the report. One item not discussed there is the overall logic design of the computer. The fact that the computer can run the several programs which it has run successfully, indicates that, by and large, the logic does what the programmers expect it to do. However, logic design changes are being made fairly continuously and that indicates the need for a detailed logic verification.

#### 1.6 RECOMMENDED ACTIONS

This paragraph presents a brief description of the actions which are recommended as a result of the design review findings summarized in the previous paragraph.

#### 1.6.1 Continued Design Review

This report is not considered a final design review document. The design review should certainly continue until each of the Category D items has been resolved into a more definite category. In addition, the design review to date has not been exhaustive. Certain aspects of the computer and its associated equipments have not been reviewed at all, and are not even mentioned in the body of this report. The complete computer should be reviewed. A detailed breakdown of the Category D items is contained in Section 2 of Appendix H of this report.

## 1.6.2 Engineering Tests

Certain data need to be developed in order to provide a basis for the design of the computer, and for the design of the final acceptance tests for the computer and the computer modules. This paragraph discusses those engineering tests which fall into that category.

The timing analysis is one of the major tasks to be accomplished. This analysis will require the use of an operating, fully potted, production computer; a computer test set; and a program analyzer console. The timing analysis must develop detailed knowledge of the timing margins at the temperature extremes as well as at room temperature.

The same computer which is used for the timing analysis can also be used to determine the margins which exist between the noise thresholds of the circuits and the noise generated within the wiring of the computer.

The results of the detailed timing and noise studies are required before the program can be written which the computer will run during its final acceptance test.

Another significant task is the electrical testing of the erasable memory module to determine the basic operating characteristics of the core assembly. These tests also must be done over the temperature range using modules produced by both vendors. Special equipment is required for these tests, but it should be possible to rent time on satisfactory equipment at one of the vendor's facilities.

The erasable memory mechanical design has been troublesome. A thorough, operating environmental test of the module should be performed to prove out the new mechanical design.

The new core rope mechanical design must be subjected to a thorough engineering evaluation. Vibration, mechanical shock and temperature shock should be performed immediately. These tests should be operating tests, since the operating margins of the fixed memory can be influenced by mechanical stresses applied to the cores, especially in the temperature and vibration environments.

An engineering evaluation of the signal layer means of interconnecting the logic flatpacks should be conducted. This test should demonstrate conclusively whether or not the signal layer is a satisfactory substitute for the multilayer board. This test would presumably be performed by selecting a logic module whose performance is critically dependent on the circuit board wiring capacities and building that module with the improved signal layer process. A comparison can then be made of the performance of that module with the performance of the same module built using the multilayer boards.

The mechanical and thermal design of the computer is still questionable with regard to three problem areas. There is significant danger of corrosion of the magnesium material, especially at the interfaces with the aluminum inserts. The present series of tests to find some means of overcoming this difficulty should be continued. Tests should continue in an effort to determine the capability of the computer to maintain its pressurization during vibration and thermal environments, and the thermal model computer C-0X should be instrumented and a thorough study should be made of the temperatures developed within the computer modules over the full range of temperatures and heat inputs.

#### 1.6.3 Documentation

The design review committee recommends that a serious attempt be made to bring the documentation controlling the computer design, manufacture, and testing up to an acceptable working level. It is strongly recommended that a single organization be given the responsibility of straightening out the documentation, particularly the interface control documents and procurement specifications.

The maintenance and logistics plan for the computer, insofar as the committee has been able to determine, has not been documented. This plan should be developed in detail and documented, and this document should be made a contractual requirement for all of the parties who will be providing maintenance of the Apollo guidance computer.

The specification control drawings against which the piece parts and certain modules are purchased should be revised. Those SCD's which are particularly significant are for the integrated logic circuits, for the multilayer boards, for the erasable memory module, for the fixed memory cores, and for the DSKY relays.

It is strongly recommended that a programmer's manual be compiled to record the restrictions which the computer design places on the programmers.

#### 1.6.4 Test Plans

#### 1.6.4.1 Screen and Burn-in

The present flight processing of semiconductor components is deemed to be generally questionable because of the extreme difficulty of obtaining parts which can pass these tests. While it is agreed that something should be done to make the screen and burn-in tests more reasonable from the vendor's standpoint, there is considerable uncertainty with regard to the detailed recommendations. The committee recommends, therefore, that a study be undertaken to determine if there are testing procedures which can be meaningful in terms of guaranteeing the overall quality of the parts so screened and yet make it possible for the vendors to produce parts which will pass the screen. Certain parts which are not now included in the screen and burn-in process should be; in particular, the relays and the multilayer boards come to mind.

#### 1.6.4.2 Qualification Testing

The committee has recommended that qualification testing at the module level be discontinued but that a satisfactory qualification test plan be developed for the entire computer. This test plan could be a revision of ND 1002037 which would include the worst portions of the mission profiles for both the command module and the lunar excursion module, when the relative severity can be determined. The test should include both profiles if the relative severity cannot be determined.

#### 1.6.4.3 Acceptance Testing

It is necessary to develop a new set of acceptance test plans for the computer and for its modules. This is a significantly difficult task, as is pointed out in some detail in the remainder of this report. It is not feasible to guarantee analytically that the computer has adequate design margins. The acceptance tests must, therefore, guarantee empirically that each computer, as built, has adequate operating margins over the extremes of the environment. The quality of the computer will be as good as the final acceptance test and it is imperative that this final test be exhaustive. The acceptance test procedure must be predicated on data which is developed during the engineering evaluation tests. In particular, the computer acceptance tests must demonstrate adequate margins with regard to computer timing, logic noise margins, erasable and fixed memory sense amplifier thresholds, and erasable and fixed memory drive current tolerances.

The digital computer program which exercises the hardware during these acceptance tests is extremely critical and must be designed specifically to stress those conditions

of the computer which are being tested. In the case of the memory test, the program is almost trivial, it being merely required to generate the two worst-case noise patterns. In the case of the timing margin and the logic noise margin, the program is apt to be considerably complicated and it will be very difficult to determine precisely what the program should consist of.

The rope module acceptance tests must be revised to provide these critical modules with a complete test. It is strongly recommended that the ropes be given a twofold test. The first should be a workmanship test which would prove that there are no bad solder joints or damaged wires in the assembly. This workmanship test should consist of a simultaneous vibration and thermal cycle while the windings of the rope modules are monitored for continuity. Assuming that the module passes the workmanship test, it should then be subjected to a realistic operating test over the temperature range with tests designed to guarantee adequte electrical operating margins. Adequate marginal testing will provide some assurance that each set of ropes will work in any computer.

#### 1.6.5 Design Tasks

The present computer contains several specific designs which have been rated as C - Inadequate. A list of those specific problem areas is contained in Section 3 of Appendix H. This paragraph discusses some of the more important design tasks.

The voltage failure alarms should be redesigned to cause an overvoltage condition to disconnect power from the computer when it is connected to the ground support equipment. The use of the voltage fail alarms to cause a program restart has been seriously questioned and should be examined from an operational standpoint. The alarms should be redesigned so that the undervoltage and overvoltage conditions at which the alarm is indicated are those conditions which are either dangerous to the reliability of the circuits or which will cause the circuits to operate improperly.

The committee recommends that the overloaded conditions in the computer logic be corrected. The committee also recommends that the wire-wrap program be revised to include electrical considerations of the wiring noise in addition to the present mechanical considerations. Introduction of these new constraints into the program should help to avoid conditions of bad noise generation or undue noise pickup.

The oscillator circuit presently uses parts which cannot be qualified to the flight environment. The oscillator could be redesigned to remove the troublesome parts without seriously affecting the performance of the oscillator.

The DSKY utilizes electroluminescent panels which presently exhibit serious quality problems and which require the use of relays, which also have serious quality problems. An investigation should be made of the possibility of substituting incandescent displays for the present electroluminescent panels.

If the electroluminescent panels are retained in the DSKY, the indicator driver modules which contain the latching relays should be redesigned to provide sufficient power to the relays under all conditions of temperature and input voltage level.

It is recommended that a relief valve or a bellows be provided to limit the overpressure to a value tolerable to a simple cover, thereby simplifying the mechanical design.

Counter failures should be detected and signalled to the computer program. The present logic design is also known to have a minor flaw (see Paragraph 2.1.1.8) and should be corrected.

The logic of the standby flip-flop should be redesigned to prevent its coming on in an arbitrary state. In addition, the indicator light should be operated from the relay which disconnects the power from the remainder of the computer.

#### 1.7 ORGANIZATION OF THIS REPORT

This report is organized along the general lines which the investigation took. There were some aspects of the computer design which significantly influenced several other areas and, therefore, are mentioned in more than one section of the report. This is primarily due to the specific organization or format chosen for the report, and is not intended to imply that those items mentioned more than once are more important than the other items. It is not possible, for example, to treat the Malco pin as just a piece part problem, since it affects the choice of interwiring techniques, the choice of construction processees, and the maintenance and logistics plan for the computer.

Section II contains the bulk of the material and discusses the computer; its mechanical; thermal, logic, and circuit problems.

Section III discusses the display and keyboard which provides the interface between the computer and the astronauts.

Section IV discusses the piece part problems and the flight processing techniques.

Section V discusses the qualification and acceptance tests.

Section VI treats the documents which should provide design definition and system integration information, as well as the documents which are used or are generated in manufacturing the computer.

Section VII discusses those computer programs which are pertinent to the testing of the computer as well as aspects of the mission programs which are intimately affected by the constraints imposed by the computer hardware design.

Section VIII discusses several miscellaneous topics which bear only indirectly on the adequacy of the computer itself. This section includes brief discussions of the GSE insofar as it affects the thoroughness of the testing of the computer and the safety of the computer during these tests. It also discusses the CDU blue nose problem and computer manufacturing techniques. Section IX contains MIT/IL comments on the content of the original report. Following Section IX there are several appendices. These, in general, contain the details of the specific design reviews which have been performed.

#### II BLOCK II APOLLO GUIDANCE COMPUTER (AGC)

#### 2.1 FUNCTIONAL ASPECTS

The operational criteria which the computer must fulfill for the lunar landing mission have not been documented to the extent that the acceptability of the computer design can be judged by a straightforward procedure. There is apparently no sample problem nor its functional equivalent which is explicitly specified and being imposed upon the designers of the computer by the customer. As a result, many of the characteristics of the computer have not been questioned. Even so, there are some functional aspects which have raised doubts in the minds of the review committee and these are discussed in the immediately following paragraphs.

#### 2.1.1 Alarms and Restart (B)

The alarm situation has been questioned beginning with the choice of the alarm parameters and extending all the way through the techniques used to guarantee a satisfactory restart of the computer program. Even if it is granted that the entire set of alarms is desirable, the disposition of each is inconsistent. In the first place, the identity of the alarm is not generally retained. This should be changed, since continuing use of the computer might depend on the failure mode. Furthermore, the storage of each failure should be unique, i.e., failures which imply impending shutdown can still allow memory access to store the failure data, while others implying loss of memory would require flip-flop storage. The program exit point at the time of the alarm should be saved if at all possible. The recovery routine following a restart can then review the failure type, as well as the locations involved. In the case of parity failure, it may be possible to reserve blocks of memory for scratch pad and blocks for mission data, and the recovery could be handled accordingly.

#### 2.1.1.1 Parity Alarm (B)

A parity failure is treated identically whether it occurs in fixed or erasable storage. This seems incorrect. First, a parity failure in the rope memory due to a transient may not be disastrous. Repeated trials (two or three) should be allowed to read the correct data. Second, parity failures in the erasable memory are allowed to regenerate good parity with bad data, which may act properly after a restart. This could lead to a dangerous condition. A better solution would be to identify the word in which the failure occurred and that the type of failure was parity. Obviously, this is of no use when the failure affects more than one word, such as a sense amplifier would. But in that case, the computer will not run anyway.

## 2.1.1.2 Transfer of Control (B)

This alarm guarantees that the program does not either run wild or lock up in a one word loop. If an instruction transfers control to itself continuously, the alarm will be indicated after some period of time. If there is as much as one other instruction in the loop the alarm will not be tripped. It is not absolutely known whether this alarm guards against a particularly likely mode of failure, or not. It presumably does not. Therefore, it will detect a small percentage of the possible failures of this kind, and can hardly be considered worth while. The alarm logic also checks to see that a transfer of control instruction is executed within some longer time period. This alarm needs additional study, but it does not seem to provide any high confidence that things are going well.

#### 2.1.1.3 Rupt Lock (B)

This alarm checks to see that the program services at least one new interrupt request within an interval of from 160 to 320 ms, and that no single interrupt servicing routine lasts longer than that same period of time. This alarm is considered marginal because it will detect only a gross malfunction of the computer hardware. There are many critical functions being carried out in the various interrupt subroutines during several phases of the mission, and these functions cannot be ignored as long as this alarm permits without serious degradation of system performance. By the same token, there are several phases of the mission during which the checking performed by this alarm is quite appropriate. The general question of interrupts is discussed in more detail in Paragraph 2.1.2.

#### 2.1.1.4 Night Watchman (A)

This logic checks to see that the executive program addresses memory cell "New Job" (0067)<sub>8</sub> at least once in .64 to 1.92 seconds. This is a sound alarm technique, but the sensitivity of this implementation is low due to the long sampling time.

#### 2.1.1.5 Oscillator Fail (D)

The computer oscillator provides the basic time and frequency reference to the entire spacecraft, yet its failure is not handled any differently from any other alarm condition. As far as the computer is concerned, when the clock stops the computer stops, and when the clock restarts the computer will restart with no knowledge that anything untoward had happened. If the clock stops intermittently at critical times, say during thrusting, the consequences could be quite severe. Yet this condition is not detected at all by the alarm circuit. It should at least trip a latching indicator and be telemetered on Down Link, assuming that is possible when the oscillator stops.

The oscillator failure alarm does provide a quarter of a second delay when the computer power is first applied. This is a useful function in that it allows the computer power supplies to stabilize and the logic to be initialized before the computer actually begins to run. The committee's investigation of this alarm has not been complete, and since several questions remain to be answered, this particular alarm must be placed in the indeterminate category.

#### 2.1.1.6 Voltage Failure (C)

All voltage failures (+28V input, +14V, +4V) are treated the same. When the +4 or +14 outputs of the power supply rise above their normal values, the alarm turns on the "Restart" light but no attempt is made to turn off the power to the computer, thereby preventing serious damage. It is argued that in flight it is more desirable to allow the computer to burn up than to include more equipment which can itself fail. Since the alarm circuits themselves already constitute a significant number of components, the few additional components for a safe shutdown circuit are easily justified. The additional arguments obtain that most of the computer's life is in ground operation and, even in flight, recovery might be effected from a temporary power excursion, if the computer does not burn up.

There is some question about the undervoltage alarm conditions as well as the overvoltage condition. At the present time the 28 volt alarm threshold is set at 21.6 volts. This appears to be a satisfactory compromise between the 23 volts guaranteed lower limit of the spacecraft power supply and the 18 volts at which the 4 and 14 volt power supplies begin to lose regulation. On the other hand, as indicated in Section III, there is a significant circuit problem associated with the relays in the DSKY. At high temperatures the relay will fail to operate at a voltage level which is higher than the 28 volt alarm threshold. Therefore, this alarm cannot be expected to indicate satisfactory DSKY operation. This is not considered to be an inadequacy of the alarm circuit, however, but an inadequacy of the DSKY circuit. If the DSKY relay circuit cannot be corrected, the alarm threshold should be raised to the value dictated by the circuit.

# 2.1.1.7 Restart (D)

Each of the above alarms causes the main computer program to restart and the restart light to be lit. The hardware provides no clues to the nature of the difficulty which created the restart and, therefore, the restart program has no knowledge of the particular difficulty from which it is trying to recover. Certainly, the restart procedures should be different if the restart were due to a parity failure in erasable memory or in rope memory. There is not sufficient information available with regard to the detailed nature of the restart program to allow us to judge whether this is a serious problem or not. It would appear to be a questionable approach for the

lunar landing, during which time the computer is providing direct control of the LEM. In addition, continuous restarts, with no clue as to reason, make checkout of the computer and its integration into the system much more time-consuming than it would be otherwise.

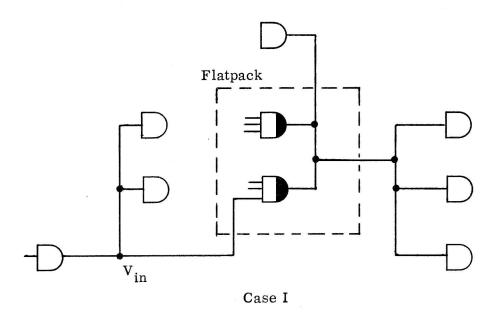

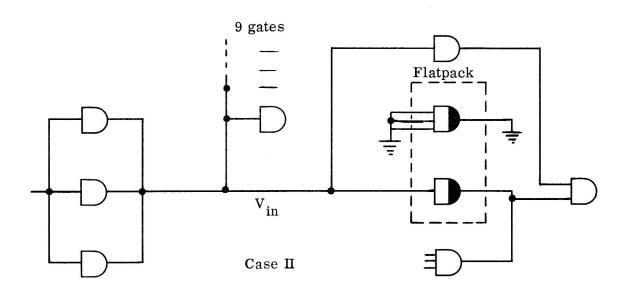

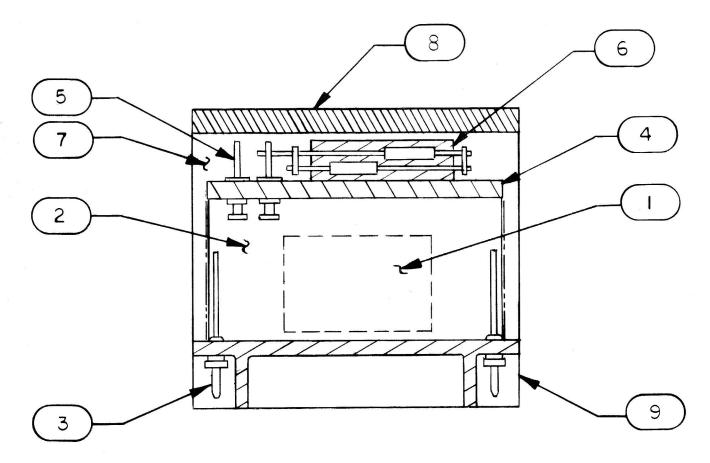

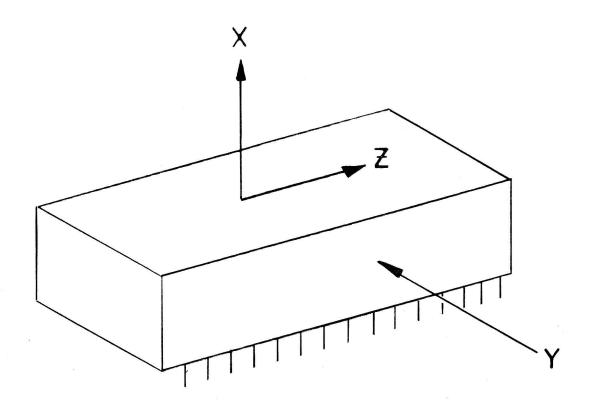

The restart also provides an input to the warning filter, and repeated restarts are necessary before the AGC Warning light will be turned on as a result of the output of the filter exceeding the circuit threshold. The rationale for this appears to be that the computer and its program are designed to tolerate restarts, since restarts happen even in the laboratory environment. As a result, restarts are treated quite casually, and diagnosis of an individual restart cause is not normally attempted.