E-1077

MASSACHUSETTS INSTITUTE OF TECHNOLOG

PRELIMINARY MOD 3C PROGRAMMERS MANUAL

by

R. Alonso J.H. Laning, Jr. H. Blair-Smith

November 1961

### ACKNOWLEDGMENT

This report was prepared under the auspices of DSR Project 55-191 sponsored by the Space Task Group of the National Aeronautics and Space Administration through Contract NAS9-153.

The publication of this report does not constitute approval by the National Aeronautics and Space Administration, of the findings or the conclusions contained therein. It is published only for the exchange and stimulation of ideas.

## TABLE OF CONTENTS

|                                       |                                                                                             | Page |

|---------------------------------------|---------------------------------------------------------------------------------------------|------|

| Preliminary Mod 3C Programmers Manual |                                                                                             |      |

| Introduction                          |                                                                                             |      |

| Machine                               | Organization                                                                                | 5    |

| Description of the Instructions       |                                                                                             |      |

| Additiona                             | l Special and Central Registers                                                             | 11   |

| Output Re                             | egisters                                                                                    | 13   |

| Input Registers                       |                                                                                             |      |

| Counter Incrementing                  |                                                                                             |      |

| Program Interruption                  |                                                                                             |      |

| Examples                              | 19                                                                                          |      |

| APPENDIX I                            | Complete List of Centrals and<br>Specials with Numerical Address<br>and Bit Transformations | 27   |

| APPENDIX II                           | List of Control Pulses                                                                      | 31   |

| APPENDIX III                          | 3C Instructions (H. Blair-Smith)                                                            | 33   |

| APPENDIX IV                           | Yul System for 3 C and Related<br>Computers (H. Blair-Smith)                                | 49   |

| APPENDIX V                            | Interpreted Instructions<br>(J. H. Laning, Jr.)                                             | 59   |

| APPENDIX VI                           | Illustrative 3C Program in<br>Yul Language (J. H. Laning, Jr.)                              | 75   |

#### PRELIMINARY MOD 3C PROGRAMMERS MANUAL

#### INTRODUCTION

This manual is intended for those people who have some familiarity with the type of computer of which the Mod 3C is an example. Although the 3C computer is like the one described in R-276, there are many differences of details and of nomenclature.

The material presented here neither is complete, nor is it entirely firmly established at the present date. It is meant to provide prospective 3C programmers with enough information to code representative programs, to make estimates of storage and speed requirements, and to aid the 3C designers by forcing commitments as to the nature of the IN-OUT system. Furthermore, it is hoped that this manual will bring about comments and questions by those who program. Despite the foregoing remarks which suggest that the design of 3C is still in a fluid state, it should be emphasized that there is no reason at present to suppose that the material described in this report will be changed in any respect in the final design.

A complete listing of all registers in Groups SC, IO, and C (Table 1) and their tentative address assignments is included in Appendix I. Appendix II contains a listing of control pulses, and Appendix III shows all the control pulse sequences. Appendices IV, V, and VI describe, respectively, the Yul system compiler for compilation of 3C programs and preparation of corresponding rope wiring diagrams, a set of interpreted instructions for extra precision arithmetic and vector operations, and finally a representative program in Yul system language for purposes of illustration.

#### MACHINE ORGANIZATION

For programming purposes, 3C may be outlined as in

Table I. Other relevant facts are:

- a. Bit positions in the 3C word are numbered 0 to 15, reading from right to left. Bit zero is always the parity bit whenever a parity bit exists. Bit 1 is the lowest order digit position and bit 15 the highest. Data words consist of a sign bit (15), 14 bits of data (bits 14-1), and parity bit 0.

- b. Number system is ONE's complement. This means that there are two representations of zero.

- c. Instruction format consists of 3 bits for instruction code (bits 15-13), and 12 bits for the relevant address (bits 12-1).

- d. List of Instructions:

| <br>тс | Transfer Control                           |

|--------|--------------------------------------------|

| CCS    | Count, Compare and Skip (a kind of branch) |

| INDEX  | Modify Next Instruction                    |

| ХСН    | Exchange                                   |

| CS     | Clear and Subtract                         |

| TS     | Transfer to Storage                        |

| AD     | Add and Count on Overflow                  |

| MP     | Multiply                                   |

- e. Additional Sequences:

- Increment Counters Interrupt Resume

Several other operations on a word are possible by the use of specially wired registers. The present content of a register, e.g. register A, is symbolized by

### c(A),

and it means "that which would be read out of A". It is sometimes

# TABLE I Programmer's View of 3C Organization

| Group<br>Name* |                                                                                                                                                    |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| F              | <u>Fixed:</u> 3584 Registers<br>Octal Addresses<br>7777 to 1000, inclusive                                                                         |

| E              | Normal Erasable: 460 Registers<br>Octal Addresses<br>0777 to 0064, inclusive                                                                       |

| С              | <u>Counters:</u> 20 Registers<br>Octal Addresses<br>0063 to 0040, inclusive                                                                        |

| Ю              | <u>IN-OUT:</u> 16 Registers<br>(6 Input, 4 Output, 4 Unassigned<br>Addresses, and Inhibit Interrupt)<br>Octal Addresses<br>0037 to 0020, inclusive |

| SC             | Specials and Centrals: 15 Registers<br>Octal Addresses<br>0017 to 0001, inclusive                                                                  |

| А.             | <u>Accummulator A:</u> l Register<br>Octal Address<br>0000                                                                                         |

| * Gro          | oup Name is for convenience in writing the text.                                                                                                   |

necessary to make a distinction between the present content of a register, and the content of a register before some action or operation. The "before" content is symbolized by

## b(A).

The registers mentioned in the description of instructions are:

| А  | The Accummulator             |

|----|------------------------------|

| Q  | The Return Address Register  |

| N  | The Uncorrected Sum Register |

| LP | The Low Order Product        |

These registers are all addressable as ordinary registers in storage and have addresses and properties as given in Appendix I.

## DESCRIPTION OF THE INSTRUCTIONS

When discussing an instruction, it is assumed that L is the location of that instruction.

## Code 0. TC x Transfer Control

| Action:    | Take the next instruction from location $x$ , instead of from location $L + 1$ . Set central register Q to                                                                                                                                 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | c (Q) = L + 1 = TC L + 1                                                                                                                                                                                                                   |

|            | The last equality holds because the numerical code for TC is 000.                                                                                                                                                                          |

| Comments : | The instruction TC Q is useful for exiting<br>subroutines. The instruction TC A<br>causes the single instruction in register<br>A to be executed. This action follows<br>because register A has address 0 and<br>register Q has address 1. |

| Code 1. CCS x. | Count, Compare and Skip                                                                                                                                           |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Action:        | If $c(x) > 0$ , set $c(A) = c(x) - 1$ ;<br>Take next instruction from L + 1.                                                                                      |

|                | If $c(x) = +0$ , set $c(A) = +0$ ;<br>Take next instruction from $L + 2$ .                                                                                        |

|                | If $c(x) < 0$ , set $c(A) = -c(x) - 1$ ;<br>Take next instruction from L + 3.                                                                                     |

|                | If $c(x) = -0$ , set $c(A) = +0$ ;<br>Take next instruction from $L + 4$ .                                                                                        |

| Comments:      | The instruction CCS A is permissible.<br>Note, however, that the original contents<br>of A are changed as per the actions<br>described above.                     |

| Code 2. INDEX  | x. Modify Next Instruction by Adding c(x)                                                                                                                         |

| Action:        | Take as the next instruction $c(L + 1) + c(x)$ .                                                                                                                  |

| Comments:      | If L + 1 is of Group E, its contents are <u>not</u><br>correctly restored. Address x may be of<br>Group E without ill effects.                                    |

|                | The sum $c(L + 1) + c(x)$ is the overflow-<br>corrected sum. (See Note 3 of Appendix I).                                                                          |

| Code 3. XCH x. | Exchange c(x)                                                                                                                                                     |

| Action:        | <pre>Set c(A) = b(x) Set c(x) = b(A) Exchange c(A) with c(x), unless x is of Group F. If it is, c(x) remains undisturbed. Take next instruction from L + 1.</pre> |

| Comments:      | There are implications to the use of XCH C,<br>where C is a counter of Group C. This<br>will be elaborated upon later.                                            |

| Code 4. CS x. | Clear and Subtract x                                                                                                                                                                                                                                                                                           |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Action:       | Set $c(A) = -c(x)$ ;<br>Restore x to the original $c(x)$ . $[c(x) = b(x)]$ .<br>Take next instruction from L + 1.                                                                                                                                                                                              |

| Comments:     | The instruction CS A complements c(A);<br>i.e., c(A) = - b(A)<br>Beware of CS x, where x is of Groups                                                                                                                                                                                                          |

|               | ID or SC; restoring the contents of a<br>register implies first clearing that<br>register, and then writing back into it.                                                                                                                                                                                      |

|               | If the register x is a shift register,<br>for example, its contents will be altered<br>in the process of restoration. This<br>warning applies to all instructions.                                                                                                                                             |

| Code 5. TS:x. | Transfer to Storage x                                                                                                                                                                                                                                                                                          |

| Action:       | Set c(x) = c(A);<br>Leave c(A) undisturbed.                                                                                                                                                                                                                                                                    |

| Code 6. AD x  | Add and Count Overflow                                                                                                                                                                                                                                                                                         |

| Action:       | Set c(A) = b(A) + c(x), corrected for<br>overflow. Superpose the uncorrected<br>sum onto c(N). N is of Group SC.<br>If overflow occurs, set a signal to<br>cause incrementing or decrementing<br>of the overflow counter (OVCTR) of<br>Group C, according to whether the<br>addends were positive or negative. |

|               | Superposing onto $c(N)$ means storing in<br>N the bit-by-bit OR of the sum $c(A) + c(x)$ ,<br>not corrected for overflow, and the previous<br>content of N, i. e., $c(N) = b(N) + \{c(A) + c(x)\}$ .<br>As will be shown later, N can be used                                                                  |

.

10

for editing purposes. The counter

incrementing feature is useful in double precision subroutines. TS N may be used to set N to some desired initial value. See Appendix I, Note 3 for definition of overflow correction.

#### Code 7. MP x. Multiply by x

Action: Set c(A) and c(LP) to b(A). c(x), with LP holding the low order part of the product, and A the high order part. Register x is restored. The quantity in LP has the same sign as that in A.

Comments: Multiplication requires 16 Instruction Times, versus 2 for CCS, and 1 for all others.

### ADDITIONAL SPECIAL & CENTRAL REGISTERS

There are 15 registers classified as Special or Central. The Special registers are those which perform some sort of transformation or manipulation of the incoming or outgoing bits. Shift and Cycle registers are of this sort, as well as the N register; the N register has its sign bit position connected to a special place in the Adder circuit, rather than to the normal sign bus. Nonspecial registers are those which are like erasable registers in that they do not modify the information transmitted through them in any way.

The category of Central registers - which is not mutually exclusive with that of Specials - refers to those registers which are addressed directly by the Sequence Generator, as well as by the regular addressing method. For example, register CYL, which cycles a word left by one bit position, is Central because it is used by the MP instruction, and clearly Special because of the tranformation it effects on a word. The programmer may use freely those Specials which are not Centrals; that is, those

special registers which are not committed to any particular sequence or instruction. These registers are:

| SR1 | Shift Right                                  |

|-----|----------------------------------------------|

| SLl | Shift Left                                   |

| CYR | Cycle Right                                  |

| EDH | An editing register described in Appendix I. |

|     | and meant for use in the Interpretive set    |

|     | of subroutines.                              |

The programmer may also use certain other of the special registers such as CYL, or LP, at his own discretion, provided not intervening instructions alter their contents. Other central registers, such as D or Z, should be used only by the programmer who has full knowledge of the specific effects of the control pulse sequences. These registers are discussed in detail in Appendices I and III.

Several Central registers, not Special, are worthy of note because of the use they are put to. These are:

- D Holds the data address of an instruction.Programmers stay away.

- Z At the point of beginning an instruction at

L, c(Z) = L + 1. Stay away.

- Q Holds P + 1, where P is the location of the TC instruction last executed. Used in exiting subroutines, as is shown in later examples.

- BI Holds a replica of what register B held at the time of an interruption. B is not an addressable register. BI should not be disturbed unless the programmer is trying to resume from an interrupting program to another program different from the original interrupted one. This sort of thing is to be done with extreme caution.

ZI Holds a replica of what Z held at the time of an interruption. Further comments as in BI.

#### OUTPUT REGISTERS

There are four addresses currently reserved for output registers. The output registers are OUT0, OUT1, OUT2, and OUT3. Each output register consists of 15 bistable latches corresponding to the 15 useful bit positions of the word length and are addressed by executing TS OUT<sub>x</sub>; those latches will be turned on which correspond to ONEs in the word originally in A. Hence, each latch is addressed by bit position within a word, as well as by word address.

Register OUT0 and OUT1 are such that their latches, once turned on, stay on until a new word is written into them. The useful output signal is a DC level. To turn off all the latches of, say, OUT1, execute TS OUT1, (or XCH OUT1), where c(A) = +0.

Register OUT2 is discussed after Register OUT3.

Register OUT3 is different from the previous two in that all of its latches are connected to the circuitry associated with the Group C registers (the Counters), so that a given latch within OUT3 may be turned on by the overflow of a specific counter, as well as by the execution of TS OUT3. Furthermore, these latches are turned off by every time pulse 6\*, so that these latches are never on for longer than a fraction of an Instruction Time; the time these latches remain on is  $30 \,\mu$ sec if they were turned on by an overflow; about  $10 \,\mu$ sec if turned on by a TS OUT3. The XCH instruction should not be used for addressing either OUT3 or OUT2.

The reason for the complicated arrangement for OUT3 is that the latches are meant to be primarily the overflow (underflow) indicators for counters. The feature of addressing these overflow \*The basic Instruction Time unit has 8 steps, called Time Pulses.

indicators by means of programming was tacked on as an afterthought. It is thought that the ability to simulate overflows will aid in systems and computer tests. The brief duration of these outputs is a logical requirement of the Counter Incrementing and Priority Interrupt systems.

Register OUT2 is like OUT0 and OUT1 in that the output latches can be turned on only by means of a TS instruction. For the most part, these latches will stay on until turned off by an instruction, as in OUT0 and OUT1. Some bit positions, however, may have connections which turn those latches off at every Time Pulse 6, exactly as in the case of OUT3 latches.

There are a total of 60 output latches in 3C. Attempts to read information from an OUTx register, e.g., by means of XCH OUTx or CS OUTx, will result in c(A) = 0; CS OUTx will also result in all the latches of OUTx being turned off.

### INPUT REGISTERS

There are six input registers in 3C, IN0 through IN5. These input registers are very like sampling and storing devices, and experience with Mod 1B has shown them to be a source of mild confusion.

Input registers consist of magnetic cores, each of which is tied to some DC source, e.g., a toggle switch, or an output latch. An instruction such as XCH INx first clears those cores to ZERO, sensing their contents into A, and then samples the state of the DC sources; the state of the cores of INx is known to be like the state of the sampled DC sources only after the execution of XCH INx. What this means is that the first XCH INx does not transfer into A the present state of the sampled DC sources, but the state those sources were in the previous time INx was addressed. Prudent practice, then, calls for interrogating input registers by means of two successive orders XCH INx, or equivalent.

Registers IN0, IN1, and IN2 are tied, one to one, with the output latches of registers OUT0, OUT1, and OUT2. In this way it is possible, by means of programs, to check on the state of output latches. The short duration of the outputs from Register OUT3 makes it impractical to tie an Input Register to it. OUT2 is connected to IN2 because it is anticipated that most of its latches will stay on as do those of OUT0 and OUT1, and hence it is desirable to be able to check the state of those latches.

The remaining registers IN3, IN4, and IN5 are to be connected to the outside world. The input convention is that a ONE is a grounded input line i.e., the DC source supplies a ground to indicate a ONE, and an open or -10v through high impedance when indicating ZERO.

INx registers may not be written into directly by way of programs; it is not possible to transfer c(A) into INx by means of TS INx or XCH INx. Those two instructions will, however, cause the state of the input lines to be sampled into INx.

#### COUNTER INCREMENTING

Mod 3C has 20 addressable registers which behave as counters. The inputs to those counters are things such as accelerometer pulses, or pulses from a clock, or overflows from other counters. Specification of the inputs to counters is a matter of wiring, not of program, and is one of the desired goals and a necessary condition for the full definition of 3C. Counter incrementing takes place between the end of one instruction and the beginning of the next one. This process requires one Instruction Time per increment executed; this is one reason why statements about time of execution of programs must be qualified.

As presently planned, positive or negative input into a counter position causes the action  $c(K) = b(K) \pm l(o)$ , where l(o) stands for low order ONE. Every input into a counter position specifies a counter. The overflow or underflow of counters may be used as outputs to be connected to the outside world; or

to serve as inputs to other counters; or to the Priority Interrupt circuits. It is part of the programmer's job to specify such connections when he needs them.

To interrogate a counter without risk of missing input pulses, use CS CTR and not XCH CTR. To preset a counter to a given value, and not miss pulses, use XCH CTR, not TS CTR. The subtleties which cause these recommendations will be explored later in examples.

| Counter<br>No. | Octal<br>Address | Name   | Comments                             |  |  |  |

|----------------|------------------|--------|--------------------------------------|--|--|--|

| 0              | 0040             | OVCTR  | Used in connection with AD x         |  |  |  |

| 1              | 0041             | Time l | Low order part of time               |  |  |  |

| 2              | 0042             | Time 2 | High order part of time              |  |  |  |

| 3              | 0043             | Time 3 | Presettable counter. See Example II. |  |  |  |

Table II Preliminary Counter List

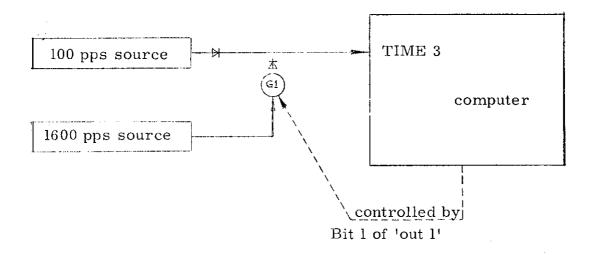

A list with a tentative assignment of the first four counters is shown in Table II. The inputs to TIME 1 are pulses from a clock. For the sake of definiteness, assume that these pulses appear at 10 m sec intervals. Counter TIME 1 can store  $2^{14}$  such pulses, or about 160 sec. The overflows from TIME 1 are the inputs to TIME 2. TIME 3 also has input pulses which appears once every 10 m sec. Overflows from TIME 3 cause automatic interruption of whatever program is then being executed, and transfer of control to another program. TIME 3 can be preset to any desired value, so that it may be used to mark off time intervals in multiples of 10 m sec; this method of marking time intervals, which may differ one from the next, is useful in that it avoids clumsy programs for finding out whether it is time to perform some action or not. See Example II.

### PROGRAM INTERRUPTION

In general, a program may be interrupted by the occurence of certain external signals. This means that the normal sequence of instructions of a program may be broken into at <u>any</u> point, and that control is transferred to some other program. There is a short subroutine which has the net effect of returning control to the original (interrupted) program, with no loss of information if certain precautions are taken. It would be expected, for example, that the signalling of the computer from the control console by manual intervention would take place through an interrupt operation. In other words, the depressing of the button or turning of the switch on the control console could signal the computer that information was to be read, and the information itself then taken from one of the input registers.

An interrupting program is prevented by interlock logic from itself being interrupted. It is the responsibility of the interrupting program to preserve the contents of registers Q and A, and to restore them to their original content. The content of register Z is preserved automatically. The interrupting program must also restore any other Central or Special register it uses back to its original state. Register A is mentioned specifically because it is necessarily used by an interrupting subroutine. Register Q must usually be preserved, since interrupting subroutines will usually have a TC instruction.

The specific point at which the interrupted program is resumed is when the instruction TS RIP is executed; the content of A may be anything at all; RIP is a specific address (octal 0036), and the mnemonic code stands for "Resume Interrupted Program".

A specific format has been decided upon for the Interrupt System. These are eight Interrupt options available; i.e., all signals which cause an Interrupt belong to one of eight categories,

OPTION 1 through OPTION 8. The first and immediate result of some such signal is to preserve B and Q, and to transfer control to one of eight subroutines named OPTION 1 through OPTION 8. These routines are located in octal addresses 1000 through 1037; for example:

| Mnemonic<br>Address | Absolute<br>Address |               |          |

|---------------------|---------------------|---------------|----------|

| OPTION 1            | 1000                | $\mathbf{TS}$ | AI       |

|                     | 1                   | ХСН           | Q        |

|                     | 2                   | TS            | QI       |

|                     | 1003                | тс            | INTPNG 1 |

| <b>OPTION 2</b>     | 1004                | TS            | AI       |

|                     | 3                   | ХСН           | Q        |

|                     | 4                   | TS            | QI       |

|                     | 1005                | TC            | INTPNG 2 |

|                     | etc.                |               |          |

These programs preserve c(A) and c(Q), and transfer control to the appropriate interrupting program INTPNG 1, 2, etc. Registers AI and QI are in E; since there can be no interruption of an interrupt, AI and QI are the same for all options.

The particular actions described above may seem roundabout, since it can be arranged for an interruption to transfer control directly to INTPNG X. The reason for first transferring control to an OPTION X is to make definite the wiring of the sequence generator, since each OPTION X now has a definite numerical address associated with it. These addresses are in F; the rope wiring is still left indefinite, of course.

The last act of the INTPNG X program is to transfer control to the RESUME subroutine.

| RESUME | XCH           | $\mathbf{QI}$ |

|--------|---------------|---------------|

|        | $\mathbf{TS}$ | Q             |

|        | XCH           | AI            |

|        | $\mathbf{TS}$ | RIP           |

The last instruction causes transfer of control back to the interrupted program.

It is sometimes necessary to guarantee that an interruption will not occur during a certain part of a program, as is shown in Example I. An address has been reserved for this purpose and the instruction TS INHINT, where c(A) < 0, will inhibit interrupt. Removal of the inhibition takes place by executing another TS INHINT, where c(A)>0. Address INHINT happens to be octal address 0037.

#### EXAMPLES OF PROGRAMS

Example I. Modification of a Single Bit of an Output Register

Let OUT1 (whose latches are turned ON and OFF by program) be in some uspecified state. Let it be desired to turn to ON bit 5 of OUT1. All other latches must be left in their original state. We may not assume that bit 5 was OFF to being with. Recall that IN1 is tied to OUT1, and the present state of OUT1 may be known by interrogating IN1. The logical problem is then simple: Transfer into OUT1 a word which has a ONE in bit position 5, and ONEs and ZEROs elsewhere as before. If it is known that bit 5 was OFF, then such a word could be obtained by the following program:

| XCH | IN1,       |               |     |     |     |     |     |  |

|-----|------------|---------------|-----|-----|-----|-----|-----|--|

| XCH | IN1,       |               |     |     |     |     |     |  |

| AD  | ''Bit 5'', | c ("Bit 5") = | 000 | 000 | 000 | 010 | 000 |  |

| TS  | OUT1.      |               |     |     |     |     |     |  |

If latch 5 of OUTl were ON, however, such a program would result in a ZERO sum in position 5, and a carry into the higher order bits. What is desired, then, is the OR operation, rather than AD. A particular way of doing this is to blank the content of A as per the content of some register Bk, where blanking means "make ZERO those bit positions of A which correspond to ONEs of Bk." Once a word is blanked in the desired hit positions, the OR operation

is achieved by the AD instruction.

A blanking subroutine can be as follows, making use of the special register N (see description of AD x).

| "Blank c(A) by c(Bk)" | CS            | А,   | Invert c(A) |

|-----------------------|---------------|------|-------------|

| +1                    | XCH           | N,   |             |

| +2                    | XCH           | ZERO | c(ZERO) = 0 |

| +3                    | $\mathbf{AD}$ | Bk   |             |

| +4                    | CS            | N,   |             |

| +5                    | TC            | Q    |             |

The first two instructions result in placing -b(A) in N. XCH ZERO clears A. AD Bk places c(Bk) on the word already in N. This word is the inverse of what is desired. Return of control to the calling subroutine is accomplished by TC Q. This subroutine is useful in turning output latches OFF as well as ON.

Turning on bit 5 of OUTI is then done as

follows:

| Latch ON | XCH           | IN1                 |                                                       |

|----------|---------------|---------------------|-------------------------------------------------------|

| +1       | ХСН           | INl                 |                                                       |

| +2       | тс            | Blank A by "Bit 5", | c(Bk) = all<br>ZEROs except<br>for a ONE in<br>bit 5. |

| +3       | AD            | "Bit 5",            |                                                       |

| +4       | $\mathbf{TS}$ | OUT1.               |                                                       |

If it is desired to check that all the latches are now in their proper state, the following program might be used.

Latch ON +5 TC CHECK OUT1,

and

| ХСН                    | Templ                                                 | Preserve c(A)                                             |

|------------------------|-------------------------------------------------------|-----------------------------------------------------------|

| XCH                    | INl                                                   |                                                           |

| XCH                    | INl                                                   |                                                           |

| CS                     | А                                                     |                                                           |

| AD                     | Temp 1                                                |                                                           |

| $\mathbf{TS}$          | Temp 2                                                | Preserve difference                                       |

| CCS                    | Temp 2                                                |                                                           |

| $\mathbf{TC}$          | WRONG                                                 | Too few latches ON.                                       |

| TC                     | Q                                                     | Ok exit                                                   |

| $\mathbf{TC}$          | WRONG                                                 | Too many latches ON.                                      |

| $\mathbf{T}\mathbf{C}$ | Q                                                     | Ok exit                                                   |

|                        | XCH<br>XCH<br>CS<br>AD<br>TS<br>CCS<br>TC<br>TC<br>TC | XCHIN1XCHIN1CSAADTemp 1TSTemp 2CCSTemp 2TCWRONGTCQTCWRONG |

Further routines, remedial or diagnostic, could follow a failure of the above check. If the check succeeds, TCQ causes control to be transferred to "Latch ON +6".

One cause for concern in the above programs might be if the program LATCH ON is interrupted, say after AD "Bit 5", and the interrupting program changes the state of some other latch of OUT1. Upon resumption of LATCH ON, the selection of latches to be turned ON (or OFF) with TS OUT1 is based on the sampling of OUT1 which occurred before the interruption. Thus, as far as OUT1 is concerned, the latches will all be restored to the state they were at before the interruption, excepting for bit 5. This situation can be remedied by inhibiting interruptions for a brief period. Interruptions may be inhibited by the instruction TS INHINT, where  $c(A) \le 0$  or c(A) = -0; i. e., the sign bit position of A contains a ONE. To again allow interruptions, it is necessary to do TS INHINT with the sign bit of A at ZERO. Hence, program LATCH ON should be preceded and succeeded as follows:

| LATCH ON    | -2      | CS PLUS   | Puts sign bit of A at ONE, if c (PLUS) <0 |

|-------------|---------|-----------|-------------------------------------------|

|             | -1      | TS INHINT |                                           |

| LATCH ON    |         | ETC.      |                                           |

| · · · · · · |         |           | c(MINUS) > 0                              |

|             | $\pm 7$ | TS INHINT |                                           |

|             |         | 01        |                                           |

There is no need for such precautions if the LATCH ON program is part of an interrupting program.

Example II. Use of Counters

Let the overflow of TIME 3 cause control to be transferred to INTPNG 1. For present purposes, let it be desired that this occur once per second. Since TIME 3 is incremented once every  $10^{-2}$  sec, it should overflow every 100 pulses (octal 144). The largest positive number a register can hold is, in octal, +37777; hence, if upon overflowing TIME 3 is set to +37634, it will overflow 144 (octal) pulses later. Let c (SET) = +37634; then part of the interrupting program is

| INTPNG 1 | XCH  | SET     |  |  |  |

|----------|------|---------|--|--|--|

| +1       | TS   | SET     |  |  |  |

| +2       | XCH  | TIME 3  |  |  |  |

|          | etc. |         |  |  |  |

| EXIT     | тС   | Resume. |  |  |  |

In this case the time elapsed between overflow and the execution of  $INTPNG^{2} 1 + 2$  is 8 instruction times, counted as follows:

| Interrupt Sequence    | $1 \ IT$        |

|-----------------------|-----------------|

| Option 1 Program      | $4 \mathrm{IT}$ |

| INTPNG to INTPNG: + 2 | 3 IT.           |

This time is 320  $\mu$ sec; hence, there is little fear  $\tilde{}$  of having missed a pulse between overflow and resetting. This, in turn, means that the next overflow will occur exactly 100 (decimal) pulses later, and not 101 pulses later. Upon overflow TIME 3 is left at ZERO.

There may be circumstances in which the time elapse between overflow and resetting of TIME 3 is so great as to make it possible to miss a count. This hazard may be avoided by the program shown below.

<sup>\*</sup>Assume there are few or none intervening counter increments being performed.

| INTPNG 1      |               |          | Some unspecified action               |

|---------------|---------------|----------|---------------------------------------|

|               |               |          |                                       |

|               |               |          |                                       |

| $+\mathbf{M}$ | XCH           | SET      |                                       |

|               | TS            | SET      |                                       |

|               | XCH           | TIME 3   |                                       |

|               | TS            | TEMP     | TEMP is in E                          |

|               | CCS           | А        |                                       |

|               | тс            | AD       | TIME 3 had counted something          |

|               |               |          | before being set.                     |

|               | тс            | CONTINUE | it had not; continue.                 |

|               | TC            | WRONG    | These two possibilities can only      |

|               |               |          | occur if there has been an error.     |

| AD            | XCH           | ZERO     | Clear A                               |

| +1            | XCH           | TIME 3   |                                       |

| +2            | AD            | TEMP     |                                       |

| +3            | XCH           | TIME 3   | Set TIME 3 again, and again bring     |

|               |               |          | its previous contents out for         |

|               |               |          | examination.                          |

| +4            | $\mathbf{TC}$ | M + 3    | Check again that no pulses have       |

|               |               |          | been missed.                          |

| CONTINUE      |               |          | Other actions of interrupting program |

|               |               |          |                                       |

| EXIT          | TC            | RESUME   |                                       |

The program checks if TIME 3 was incremented before being set. The XCH order is such that the actual exchange of c (A) and c (register) takes place between Time Pulses 4 and 5, while counter incrementing does not take place until Time Pulse 8. Thus the program guarantees that no pulses will be lost. Unfortunately, this guarantee may be at the expense of an endless loop, since the AD subroutine transfers control back to the start of the checking program to see if any pulses were added between AD + 1 and AD + 3; hence, a sufficiently fast input pulse rate could cause such an endless loop. This checking program

is probably most useful in circumstances where input pulse rates are slow, but where there is reason to think an initial pulse might have been missed.

One way to use the INTPNG programs is to have them execute a TC to register CHOICE, where CHOICE is in E. The content of CHOICE can be set by the INTPNG program itself or by some other program. In this way, INTPNG 1 does different things at different times. As an example, let it be required that TIME 3 overflows twice every 10 m sec: once at the 10 and once at the 10.625 m sec mark. Assume that a ONE in bit 1 of OUT1 connects to TIME 3 a pulse source which provides a pulse every .625 m sec, or 16 times faster than TIME 3's normal pulse source of one pulse per 10 m sec. This latter pulse source is not disconnected from TIME 3 since Gl(Fig.1) is ON but a small portion of the time, and never when the 100 pps source is active.

Fig. 1

The subroutines CHE 1 and CHE 2, shown below, are straight forward examples. The method of turning G1 ON and OFF is good only if the state of G2 is known, in the sense that being in CHE 1 implies that G1 is OFF, and being in CHE 2 implies G1 is ON.

| INTPNG 1          | тс            | CHOICE       |                           |

|-------------------|---------------|--------------|---------------------------|

|                   | тс            | ALARM        |                           |

| c(choice          | e) is guar    | anteed to be | either TC CHE1 or TC CHE2 |

| CHE 1             | XCH           | IN 1         |                           |

|                   | XCH           | IN 1         |                           |

|                   | AD            | BIT 1        | BIT l is a word in F      |

|                   | $\mathbf{TS}$ | OUT 1        | TURN ON G1                |

|                   | XCH           | SET 1        | SET 1 is a word in F      |

|                   | XCH           | TIME 3       |                           |

|                   | ХСН           | C 2          | C2 is a word in F         |

|                   | XCH           | CHOICE       |                           |

|                   | TC            | RESUME       |                           |

| CHE 2             | XCH           | IN 1         |                           |

|                   | CS            | IN 1         |                           |

|                   | AD            | BIT 1        |                           |

|                   | CS            | А            |                           |

|                   | TS            | OUT 1        | TURN OFF G1               |

|                   | XCH           | SET 2        | SET 2 is a word in F      |

|                   | XCH           | TIME 3       |                           |

|                   | XCH           | C 1          | Clis a word in F          |

|                   | XCH           | CHOICE       |                           |

|                   | TC            | RESUME       |                           |

| C(BIT1) = 000     | 001           |              |                           |

| C (SET 1) = + 377 | 777           |              |                           |

| C (SET 2) = + 376 | 534           |              |                           |

| C(C1) = TC        | C CHE 1       |              |                           |

| C(C2) = TC        | C CHE 2       |              |                           |

|                   |               |              |                           |

## APPENDIX I COMPLETE LIST OF CENTRALS & SPECIALS WITH NUMERICAL ADDRESS AND BIT TRANSFORMATIONS

### APPENDIX I COMPLETE LIST OF CENTRALS & SPECIALS WITH NUMERICAL ADDRESS AND BIT TRANSFORMATIONS

TRANSFORMATION (See Note 1) Register Bit Position vs Write Buss

|    | Register Bit Position vs Write Buss |                  |                                                    |    |    |    |    |    |    |    |   |   |   |    |    |    |    |    |         |         |

|----|-------------------------------------|------------------|----------------------------------------------------|----|----|----|----|----|----|----|---|---|---|----|----|----|----|----|---------|---------|

|    | NAME                                | Octal<br>Address | PURPOSE OR COMMENTS                                | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5  | 4  | 3  | 2  | 1  | Central | Special |

|    | Q                                   | 001              | Return Address                                     | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5  | 4  | 3  | 2  | 1  | x       |         |

|    | D                                   | 002              | Data Address                                       | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5  | 4  | 3  | 2  | 1  | x       |         |

| ſ  | Z                                   | 003              | Next Instruction Address                           | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5  | 4  | 3  | 2  | 1  | x       |         |

|    |                                     | 004              | Normal Register                                    | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5  | 4  | 3  | 2  | 1  |         |         |

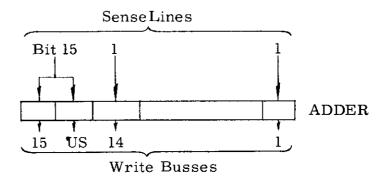

|    | N                                   | 005              | Overflow Detection and OR operation<br>Used in ADx | US | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5  | 4  | 3  | 2  | 1  | x       | x       |

|    | SR                                  | 006              | Shift Right                                        | 15 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6  | 5  | 4  | 3  | 2  |         | x       |

| 27 | SL                                  | 007              | Shift Left                                         | 15 | 13 | 12 | 11 | 10 | .9 | 8  | 7 | 6 | 5 | 4  | 3  | 2  | 1  | 15 |         | x       |

|    | BI                                  | 010              | Keep c(B) during Interrupts                        | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5  | 4  | 3  | 2  | 1  | x       |         |

|    | CYL                                 | 011              | Cycle Left                                         | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7 | 6 | 5 | 4  | 3  | 2  | 1  | 15 | x       | x       |

|    | EDH                                 | 013              | Edit - Used in Interpretive Sub-<br>routines       | 9  | -  | -  | -  | -  | -  | -  | - | - | - | 14 | 13 | 12 | 11 | 10 |         | x       |

|    | CYR                                 | 012              | Cycle Right                                        | 1  | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6  | 5  | 4  | 3  | 2  |         | x       |

|    | CLHP                                | 014              | See Note 2 for Comments                            | -  | 1  | -  | -  | -  | -  | -  | - | - | - | _  | -  | -  | -  | -  | x       | х       |

|    | HP                                  | 015              | High Order Register - Used in MPx                  | 15 | US | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6  | 5  | 4  | 3  | 2  | x       | x       |

|    | LP                                  | 016              | Low Order Product - Used in MPx                    | 1  | -  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6  | 5  | 4  | 3  | 2  | x       | x       |

|    | ZI                                  | 017              | Keep c(Z) During Interrupts                        | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5  | 4  | 3  | 2  | 1  | x       |         |

| NAME        | Octal<br>Address | PURPOSE OR COMMENTS                                                                                         | TRANSFORMATION (See Note 1)<br>Register Bit Position vs Write Buss |

|-------------|------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| IN O        | 0020             | Tied to OUT 0                                                                                               | (Addresses 20 and greater have                                     |

| <b>IN</b> 1 | 0021             | Tied to OUT 1                                                                                               | the standard one-to-one trans-<br>formation)                       |

| IN 2        | 22               | Tied to OUT 2                                                                                               |                                                                    |

| IN 3        | 23               | From outside the computer                                                                                   |                                                                    |

| IN 4        | 24               | From outside the computer                                                                                   |                                                                    |

| IN 5        | 25               | From outside the computer                                                                                   |                                                                    |

| OUT 0       | 26               |                                                                                                             |                                                                    |

| OUT 1       | 27               |                                                                                                             |                                                                    |

| OUT 2       | 0030             |                                                                                                             |                                                                    |

| OUT 3       | 31               | · · · · · · · · · · · · · · · · · · ·                                                                       |                                                                    |

|             | 32               | Spare addresses                                                                                             |                                                                    |

|             | 33               |                                                                                                             |                                                                    |

|             | 34               |                                                                                                             |                                                                    |

|             | 35               |                                                                                                             |                                                                    |

| RIP         | 0036             | Resume Interrupted Program                                                                                  |                                                                    |

| INHINT 7    | 0037             | Inhibit Interrupt if write a ONE into<br>this word, in sign position. Uninhibit<br>Interrupt if write ZERO. |                                                                    |

Notes for Appendix I:

1.

Register bit positions are named, as are the 3C word bit positions, 0 through 15. Bit position 0 is the parity position, bit position 14 is the most significant digit position, and 15 is the sign position.

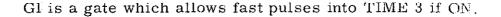

The Write Busses are 19 in number, named 0 through 15, US, OFW and UFW. Write Busses 0 through 15 correspond to the normal word bit arrangement. Write Buss US is for the Uncorrected Sign (i.e., the sign of an addition, not corrected for overflow; see AD x instruction). Write Buss OFW is for overflow and UFW for underflow. Both of these are part of the Counter Incrementing System, and are not connected to either Central or Special Registers. Buss US is connected to two such registers, as is shown in the accompanying table.

2. Addressing CLHP has the net effect of clearing register HP without restoring anything to it. The register which would normally be associated with CLHP is not connected to that address. It is called B14, and it is not independently addressable. B14 behaves as follows:

if LP is cleared, B14 is cleared;

if HP is written into, B14 is written into. Registers B14, HP and LP are used in MP x.

3.

Definition of overflow correction.

When two numbers are entered into the Adder circuits, the sign bit of each is repeated as shown below.

The addition performed is that of two 16 bit binary numbers, corresponding each to the original 15 bit binary number, with the sign bit repeated. The resulting sum is a 16 bit number. If the two higher order bits are alike, no overflow or underflow had occurred. If they are different, 01 represents an overflow and 10 an underflow. Positive sign is represented by ZERO in the ONE s complement, number system. The overflow corrected sign is the highest order bit; ZERO in the case of overflow, ONE in the case of underflow. This means that the sign of a sum which overflowed is the same as that of the two numbers summed. The Uncorrected Sign is the next to highest order bit, and the Write Buss associated with this sign is called US. (See Note 1).

## APPENDIX II LIST OF CONTROL PULSES

#### APPENDIX II

## LIST OF CONTROL PULSES

.

## Conventions

| CL    | means clear register to all ZEROS.                   |

|-------|------------------------------------------------------|

| W     | means write into register whatever is now present on |

|       | Write Busses.                                        |

| ALPHA | <b>s</b> amples sense lines of alpha side.           |

| BETA  | samples sense lines of beta side.                    |

## Control Pulses Having To Do With S & C Registers

| CL   | А,  | WA  |            |     | CL B, WB                         |

|------|-----|-----|------------|-----|----------------------------------|

| CL   | BI, | WBI | CLQ,       | WQ  | CLD , WD                         |

| CL   | Z,  | WZ  | (No CL N), | WN  | CLCYL, WCYL                      |

| CL   | HP, | WHP | CLLP ,     | WLP | CLZI, WZI                        |

| CL   | С,  | WC  | CLP1 ,     | WP1 | $\mathrm{CLP2}$ , $\mathrm{WP2}$ |

| CLSC | Ś,  | WSQ | CLS ,      | WS  | CLSUM,WX,WY                      |

## Other Control Pulses

| TP             | Test <b>P</b> arity.                         |  |  |  |  |  |

|----------------|----------------------------------------------|--|--|--|--|--|

| CLE            | Clear Memory, F, E, IO, C, or S & C.         |  |  |  |  |  |

| WE             | Write into memory register last cleared.     |  |  |  |  |  |

| CI             | Carry into bit 1 of adder.                   |  |  |  |  |  |

| CI 2           | Carry into bit 2 of adder.                   |  |  |  |  |  |

| BR 1, BR2, BR3 | Branching options for SQ.                    |  |  |  |  |  |

| II             | Inhibit interrupt for one instruction time.  |  |  |  |  |  |

| 000 <b>0</b> 1 | Read this number into Write Buss latches.    |  |  |  |  |  |

| All 1's        | Same                                         |  |  |  |  |  |

| 77776          | Same.                                        |  |  |  |  |  |

| CL SN          | Clear S, but allow no rope currents to flow. |  |  |  |  |  |

| INH            | Inhibit interrupt until further notice.      |  |  |  |  |  |

| ENI            | Enable interrupt.                            |  |  |  |  |  |

| CLI            | Advance priority.                            |  |  |  |  |  |

| CL CTR 1       | Clear counter, first time.                   |  |  |  |  |  |

| CL CTR 2       | Clear counter, second time.                  |  |  |  |  |  |

| W CTR          | Write counter.                               |  |  |  |  |  |

## APPENDIX III 3C INSTRUCTIONS

ī

#### APPENDIX III -- 3C INSTRUCTIONS

#### DESCRIPTION OF MODEL 3C INSTRUCTIONS

MODEL 3C HAS EIGHT INSTRUCTIONS... TRANSFER CONTROL, COUNT COMPARE AND SKIP, INDEX, EXCHANGE, CLEAR AND SUBTRACT, TRANSFER TO STORAGE, ADD, AND MULTIPLY. THE SEQUENCES ADD ONE TO COUNTER, SUB-TRACT ONE FROM COUNTER, INTERRUPT, AND RESUME ARE BUILT IN.

THE STANDARD QUANTUM OF TIME IS THE INSTRUCTION TIME, OR I-TIME. ONE I-TIME, OR 1 I, IS 8 PULSE TIMES, SINCE THE SHIFT REGISTER IS 8 STEPS LONG. ALL INSTRUCTIONS AND SEQUENCES TAKE 1 I, EXCEPT COUNT COMPARE AND SKIP, WHICH TAKES 2 I, AND MULTIPLY, WHICH TAKES 16 I.

SEQUENCES ARE SELECTED BY A DIODE DECODING MATRIX OPERATED BY THE SQ REGISTER. THE LATTER CONTAINS THE TOP THREE BITS OF AN IN-STRUCTION WORD AND THREE MORE BITS FOR BRANCHING WHICH ARE SET BY SOME COMBINATION OF THE PULSES BR1, BR2, AND BR3. THE PULSE CLSQ SELECTS AN INSTRUCTION OR ONE OF A PAIR OF BRANCH SEQUENCES DEPEND-ING ON THE BRANCH BITS IN THE SQ REGISTER.

MOST CONTROL PULSES CLEAR OR WRITE INTO REGISTERS. CLEARING A REGISTER SETS ITS ELEMENTS (CORES OR LATCHES) TO THE ZERO STATE, AND PLACES ITS INITIAL CONTENTS ON ITS ASSOCIATED SENSE LINES. THE ALPHA-SIDE REGISTERS, INCLUDING FIXED AND ERASABLE STORAGE, ARE MADE OF CORES AND FEED THE ALPHA SENSE LINES. THE EXCEPTIONS ARE THE OUTPUT REG-ISTERS, WHICH ARE MADE OF LATCHES AND HAVE NO SENSE LINE CONNECTIONS. THE BETA-SIDE REGISTERS ARE MADE OF CORES (THE SPECIAL CIRCUITRY IN THE PARITY REGISTERS AND THE ADDER DOES NOT AFFECT THIS DISCUSSION) AND FEED THE BETA SENSE LINES, EXCEPT FOR P1, WHICH FEEDS THE PARITY TEST CIRCUIT. THE GAMMA-SIDE REGISTERS ARE MADE OF CORES. S FEEDS THE MEMORY ROPE INHIBIT LINES, AND SQ FEEDS THE SEQUENCE SELECTION MATRIX INHIBIT LINES.

.

11-01-61 1

11-01-61 2

WRITING INTO A REGISTER CONDITIONS ITS ELEMENTS TO BE DRIVEN BY ITS ASSOCIATED WRITE BUSSES, WHICH ARE USUALLY THE SENSE AMPLIFIER OUT-PUTS. FIXED STORAGE HAS OF COURSE NO WRITE BUS CONNECTIONS, AND INPUT REGISTERS ARE DRIVEN BY DC LEVELS EITHER FROM OUTPUT LATCHES OR FROM EXTERNAL CONDITIONS.

OF THE CONTROL PULSES THAT MANIPULATE REGISTERS, SOME (CLE, WE CLCTR1, CLCTR2, WCTR, AND CLI) MANIPULATE WHICHEVER OF A SET OF REGIS-TERS WAS CHOSEN BY SOME PREVIOUS PROCESS. THE OTHERS REFER TO REGIS-TERS BY NAME, AND ANY REGISTER SO REFERENCED IS CALLED A CENTRAL REGIS-TER. THIS CLASS INCLUDES ALL THE BETA-SIDE AND GAMMA-SIDE REGISTERS, AND IS TABULATED BELOW.

| A<br>B | THE ACCUMULATOR REGISTER<br>THE BUFFER | (ALPHA)<br>(BETA) |

|--------|----------------------------------------|-------------------|

| BI     | BUFFER INTERRUPT STORAGE               | (ALPHA)           |

| B14    | THE PRODUCT TRANSFER REGISTER          | (ALPHA)           |

| С      | THE COMPLEMENTING REGISTER             | (BETA)            |

| CYL    | A CYCLE-LEFT-ONE REGISTER              | (ALPHA)           |

| D      | THE DATA ADDRESS REGISTER              | (ALPHA)           |

| HP     | THE HIGH-ORDER PRODUCT REGISTER        | (ALPHA)           |

| LP     | THE LOW-ORDER PRODUCT REGISTER         | (ALPHA)           |

| N      | THE NO-OVERFLOW SUM REGISTER           | (ALPHA)           |

| P1     | THE PARITY TESTING REGISTER            | (BETA)            |

| P2     | THE PARITY GENERATING REGISTER         | (BETA)            |

| Q      | THE RETURN ADDRESS REGISTER            | (ALPHA)           |

| 5      | THE MEMORY SELECTION REGISTER          | (GAMMA)           |

| SQ     | THE SEQUENCE SELECTION REGISTER        | (GAMMA)           |

| Z      | THE INSTRUCTION LOCATION COUNTER       | (ALPHA)           |

| ΖΙ·    | Z-REGISTER INTERRUPT STORAGE           | (ALPHA)           |

AND THE ADDER, (BETA), WITH INPUTS X AND Y AND OUTPUT DENOTED SUM. WITH NO X INPUT, THE CONTROL PULSES WY CI INCREMENT THE NUMBER TRANSFERRED BY INTRODUCING A CARRY INTO BIT POSITION 1. SIMILARLY, AN INCREMENT OF TWO IS OBTAINED BY WY CI2. MEMORY TRANSFERS FROM ALPHA TO BETA AND VICE VERSA DO NOT NEED TO ALTERNATE, SINCE THE SENSE AMPLIFIER GATES ARE OPERATED BY CONTROL PULSES. S AND SQ MAY BE WRITTEN INTO FROM EITHER SIDE.

ALL THE ALPHA-SIDE REGISTERS HAVE ADDRESSES IN ERASABLE STORAGE. THESE AND SOME MAJOR PROPERTIES ARE GIVEN BELOW.

|   | А   | 0000 | NORMAL WIRING.                            |

|---|-----|------|-------------------------------------------|

|   | Q   | 0001 | NORMAL WIRING.                            |

|   | D   | 0002 | NORMAL WIRING.                            |

|   | Z   | 0003 | NORMAL WIRING.                            |

| ¥ | N   | 0005 | SEE BELOW.                                |

|   | CYL | 0011 | CYCLES LEFT 1 BIT.                        |

|   | BI  | 0010 | NORMAL WIRING.                            |

|   | B14 | 0014 | BIT 14 ONLY. WHP IMPLIES WB14, CLLP       |

|   |     |      | IMPLIES CLB14.                            |

| ¥ | HP  | 0015 | SHIFTS RIGHT ONE, PLACING BIT 1 INTO B14. |

|   | LP  | 0016 | CYCLES RIGHT ONE, HAS NO BIT 14.          |

|   | ZI  | 0017 | NORMAL WIRING.                            |

THE ADDER CONTAINS AN EXTRA BIT (BIT 16). THE SIGN BIT (BIT 15) OF AN INPUT TO THE ADDER IS WRITTEN INTO ADDER BITS 16 AND 15. WHEN THE ADDER IS CLEARED, BIT 16 ACTIVATES WRITE BUS 15 SO THAT THE REGULAR WRITE BUSSES CONTAIN AN OVERFLOW-CORRECTED SUM. ADDER BIT 15 ACTIVATES A SPECIAL LINE WHICH GOES TO THE REGISTERS MARKED \* ABOVE. IT FEEDS BIT 15 OF N (WHICH IS NORMALLY WIRED OTHERWISE) AND BIT 14 OF HP.

3

11-01-61

11-01-61 4

THE OCTAL CODE, NAME, DURATION, MNEMONIC CODE, ACTION, AND PULSE SEQUENCE OF EACH INSTRUCTION IS GIVEN BELOW. THE FORMAT L \*\* X INDICATES THAT BITS 15-13 OF C(L) ARE INTERPRETED AS THE OPERATION \*\*, AND BITS 12-1 OF C(L) AS THE ADDRESS X. NOTE THAT IF THE PRECEDING INSTRUCTION WAS AN INDEX ORDER, THIS DESCRIPTION APPLIES NOT TO C(L), BUT TO THE SUM OF C(L) AND THE QUANTITY REFERENCED BY THE INDEX. THE APPEARANCE OF L IN THE DESCRIPTION OF THE ACTION OF EACH INSTRUCTION HAS ITS REGULAR MEANING IN THIS CASE, HOWEVER. THE INTERRUPT, RESUME, AND COUNTER INCREMENT/DECREMENT SEQUENCES ARE ALSO DESCRIBED IN THIS SECTION.

|   | CODE 0.  |                        |     | TRANSFER CONTROL |     |    |                       |     | 1 I |     |     |      |      |

|---|----------|------------------------|-----|------------------|-----|----|-----------------------|-----|-----|-----|-----|------|------|

| - | L        | Ţ                      | -   | x                |     |    | SET C(Q)<br>INSTRUCTI |     |     |     | AND | TAKE | NEXT |

|   | 2.<br>3. | ALPHA<br>ALPHA<br>BETA |     |                  | WP1 | WS | WSQ                   |     |     |     |     |      |      |

|   | 5.       | ALPHA<br>BETA          | CLD | WY               | CI  |    |                       |     |     |     |     |      |      |

|   | 8•       | BETA                   | CLB | CLP1             | ΤP  | WE | WD                    | CLS | c C | LSQ |     |      |      |

NOTE THAT TO Q WORKS BUT LEAVES C(Q) SET TO THE LOGICAL SUM OF TO L+1 AND THE ORIGINAL C(Q).

|    | APPENDIX II              | I 3C INSTR                  | UCTIONS           |                                                          | 11-01-61 5                                     |

|----|--------------------------|-----------------------------|-------------------|----------------------------------------------------------|------------------------------------------------|

|    | CODE 1.                  | COUNT CO                    | MPARE AND SI      | <ip< td=""><td>2 I</td></ip<>                            | 2 I                                            |

|    | L CC                     | S X                         | IF<br>TO C(X)-    | C(X) IS POSITIV<br>1 AND TAKE NEXT                       | (E NON-ZERO, SET C(A)<br>INSTRUCTION FROM L+1. |

|    | IF C(X) =                | +0, SET C(A)                | = +0 AND TAI      | <e instruc<="" next="" td=""><td>TION FROM L+2.</td></e> | TION FROM L+2.                                 |

|    |                          | NEGATIVE NON<br>N FROM L+3. | -ZERO, SET        | C(A) TO -C(X)-1                                          | AND TAKE NEXT                                  |

|    | IFC(X) =                 | -0, SET C(A)                | = +0 AND TAI      | KE NEXT INSTRUC                                          | TION FROM L+4.                                 |

|    | C(A) IS SE               | T TO +0 FOR C               | (X) = +1  OR      | C(X) = -1.                                               |                                                |

| 37 | 1 •<br>2 •<br>3 •        | ALPHA CLE                   | WB WP1<br>CLP1 TP | WSQ BR1<br>WE WD C                                       | LSQ                                            |

|    | 4+• ALPHA<br>5+• BETA    | +                           | CLA               | 4-• ALPHA CLZ<br>5-• BETA CLS                            |                                                |

|    | 6.<br>7.<br>8.           |                             | WY CI<br>WA WSQ   | BR2 II                                                   |                                                |

|    |                          | CLZ WY<br>CLSUM WZ          | CI<br>CLA         | 1 ALPHA CLA<br>2 BETA CLC                                |                                                |

|    | 3 •<br>4 •<br>5 •<br>6 • | ALPHA CLZ<br>BETA CLSUM     |                   | WS                                                       |                                                |

|    | 7.<br>8.                 | ALPHA CLE                   |                   | WS WSQ<br>WE WD C                                        | LS CLSQ                                        |

11-01-61 6

|                                                                                                                                                                                                            | Je mon                                 |                                                                  |                  |                  |           |                                                        | ` |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------|------------------|------------------|-----------|--------------------------------------------------------|---|

| CODE 2.                                                                                                                                                                                                    | MODIFY 1                               | NEXT INST                                                        | RUCTION          | ·                | 1 I       |                                                        |   |

| L INDEX                                                                                                                                                                                                    | Х -                                    |                                                                  | OVERFLOW C(X). I | -CORREC<br>F L+1 | IS IN ERA | CTION THE<br>OF C(L+1) AN<br>SABLE, ITS C<br>RESTORED. |   |

| <ol> <li>ALPHA CLZ</li> <li>ALPHA CLE</li> <li>BETA CLSUI</li> <li>BETA CLSUI</li> <li>BETA CLB</li> <li>ALPHA CLE</li> <li>ALPHA CLD</li> <li>BETA CLSUI</li> <li>BETA CLSUI</li> <li>BETA CLB</li> </ol> | WB<br>4 WZ<br>CLP1<br>WX<br>WY<br>4 WD | WP1<br>CLD CLS<br>TP WE<br>WP1<br>WS WSG                         | S<br>WD          | CLS              | CLSQ      |                                                        |   |

| CODE 3.                                                                                                                                                                                                    | EXCHANG                                | E                                                                |                  |                  | 1 1       |                                                        |   |

| L ХСН                                                                                                                                                                                                      | <b>X</b>                               |                                                                  | CODE CAF         | MAY B            | E USED WH | (X). THE OP<br>EN X IS IN<br>D ADD FIXED)              |   |

| <ol> <li>ALPHA CLA</li> <li>ALPHA CLZ</li> <li>BETA CLSUI</li> <li>ALPHA CLE</li> <li>BETA CLB</li> <li>BETA CLSUI</li> <li>7. ALPHA CLE</li> <li>8. BETA CLB</li> </ol>                                   | WY<br>WZ<br>WY<br>CLP2<br>M CLP1<br>WB | WP2<br>CI WS<br>CLD<br>WP1<br>WE CLS<br>TP WA<br>WP1 WS<br>TP WE |                  | CLS              | CLSQ      |                                                        |   |

| PPE                      | NDIX II                | I            | 3C INS           | TRUCTIO  | DNS            |          |     |       |      | 11-01-61                       |

|--------------------------|------------------------|--------------|------------------|----------|----------------|----------|-----|-------|------|--------------------------------|

| CODI                     | E 4.                   |              | CLEAR /          | AND SUE  | BTRA           | ACT.     |     |       | 1    | I                              |

| L                        | . cs                   | 5            | х                |          |                | SET C(A) | то  | THE C | DNES | COMPLEMENT OF C(X)             |

| 1 •<br>2 •<br>3 •<br>4 • | ALPHA<br>ALPHA<br>BETA | CLE          | WY<br>WB<br>CLP1 |          | WS<br>WC<br>WE |          |     |       |      |                                |

| 5 •<br>6 •<br>7 •        | BETA<br>BETA<br>ALPHA  | CLSUM<br>CLC | WZ<br>WA<br>WB   |          | CLD<br>WS      | )<br>WSQ |     |       |      | Ň                              |

| 7 •<br>8 •               | BETA                   |              | CLP1             | TP       | WE             | WD       | CLS | C۱    | SQ   |                                |

|                          | E 5.                   |              | TRANSF           | ER TO S  |                |          | ·   |       |      | I                              |

| L                        | Τι                     | S            | Х                |          |                |          | ΓHE | ADDEF | r so | RANSMISSION IS<br>THAT TS WILL |

| 1•<br>2•                 | ALPHA                  |              | WY               | WP2      | WB             |          |     |       |      |                                |

| 2 •<br>3 •<br>4 •        | BETA<br>ALPHA          | CLSUM        | 1 CLP2<br>WY     | WE<br>CI | WS             |          |     |       |      |                                |

| 5.<br>6.                 | BETA                   |              |                  | CLS      | CLE            | <b>)</b> |     |       |      |                                |

APPENDIX III -- 3C INSTRUCTIONS

11-01-61 8

| CODE 6. | ADD AND | COUNT ON | OVERFLOW | 1 I ' |

|---------|---------|----------|----------|-------|

|---------|---------|----------|----------|-------|

L AD X SET C(A) TO THE OVERFLOW-CORRECTED SUM OF C(A) AND C(X). SUPERPOSE ON C(N) THE UNCORRECTED SUM. IF OVERFLOW OCCURS, SET AN INTERRUPT SIGNAL TO CAUSE INCREMENTING OR DECREMENTING OF THE OVERFLOW COUNTER, ACCORDING AS THE ADDENDS WERE POSITIVE OR NEGATIVE.

| 1. | ALPHA | CLZ   | WY   | CI  | WS  |     |     |      |

|----|-------|-------|------|-----|-----|-----|-----|------|

| 2• | BETA  | CLSUM | WZ   | CLD |     |     |     |      |

| 3. | ALPHA | CLE   | WX   | WB  | WP1 |     |     |      |

| 4. | BETA  | CLB   | CLP1 | ТР  | WE  |     |     | •    |

| 5∙ | ALPHA | CLA   | WY   | CLS |     |     |     |      |

| 6. | BETA  | CLSUM | WA   | WN  |     |     |     |      |

| 7. | ALPHA | CLE   | WB   | WP1 | WS  | WSQ |     |      |

| 8. | BETA  | CLB   | CLP1 | ΤP  | WE  | WD  | CLS | CLSQ |

CODE 7. MULTIPLY

16 I

L MP X DELIVER THE PRODUCT OF C(A) AND C(X) TO A (HIGH-ORDER PART) AND LP (LOW-ORDER PART). THE SIGNS OF THE TWO PARTS AGREE AND ARE STRICTLY DETERMINED BY THE SIGNS OF THE OPERANDS. PULSE SEQUENCE IS ON THE NEXT PAGE. APPENDIX III -- 3C INSTRUCTIONS

11-01-61 9

PULSE SEQUENCE OF MULTIPLY INSTRUCTION.

1. ALPHA CLA WB WC WSQ BR1 BR2 2. CLLP CLSQ BETA CLB WLP CLD 3-. BETA CLC WLP CLD 3+• 4-. ALPHA CLE WY ALPHA CLE WY WP1 WB CLC 4+. WP1 WC CLB 5. BETA CLB CLC WD WSQ BR2 BR3 6. BETA CLSUM CLP1 TP WE CLCYL CLSQ CLHP II ALLIS WHP II 7+. 7~. 00001 WCYL 8+. 00001 WCYL 8~. 1. ALPHA CLLP WB WSQ BR1 BR3 2. BETA CLB WLP CLSQ 3+. 3-• ALPHA CLD WB WX. 4-. BETA CLB 4+. WD 5. ALPHA CLHP WY 6. BETA CLSUM WHP 7. ALPHA CLCYL WB WSQ BR3 ΙI 8. BETA CLB WCYL CLSQ 1. 2. 3. ALPHA CLHP WB ALPHA CLZ WS CI 4. WΥ BETA CLSUM WZ CLS 5. CLD 6. BETA CLB WA 7. ALPHA CLE WB WP1 WS WSQ 8. BETA CLB CLP1 TΡ WE. WD CLS CLSQ

00001 WY

### INCREMENT OR DECREMENT

## 1 I '

77776 WY

THIS SEQUENCE IS TRIGGERED BY A SUITABLE INTERRUPT SIGNAL AND FOLLOWS LINE 8 OF ANY SEQUENCE OR 8-LINE PORTION THEREOF, EXCEPT THE DUMMY LINE 8 THAT IMMEDIATELY PRECEDES INTERRUPT AND RESUME. ITS ACTION IS TO SET THE CONTENTS OF THE COUNTER SELECTED AS CTR (C(CTR)) TO C(CTR)+00001 (INCREMENT) OR TO C(CTR)+77776 (DECREMENT), CHECKING PARITY OF THE INITIAL C(CTR) AND GENERATING PARITY FOR THE SUM.

## 1. ALPHA CLCTR1 WX WP1

2+•

3. CLP1 TP

4. BETA CLSUM WCTR

5. ALPHA CLCTR2 WY WP2

6. BETA CLSUM CLP2 WCTR II

7.

8.

2-.

٠.

### INTERRUPT

1 I

THIS SEQUENCE IS TRIGGERED BY A SUITABLE INTERRUPT SIGNAL AND MAY FOLLOW ANY LINE 7 NOT INCLUDING THE CONTROL PULSE II. THE PULSE CLI SUPPLIES THE ADDRESS OF THE DESIRED INTERRUPT PROGRAM. THIS SEQUENCE IS PRECEDED BY A DUMMY LINE 8, AND IS FOLLOWED BY THE STAN-DARD LINE 8 WHICH WAS LEFT SET UP BY THE INTERRUPTIBLE SEQUENCE. THE PULSE INH INHIBITS ANY INTERRUPT UNTIL THE OCCURENCE OF THE PULSE ENI IN THE RESUME SEQUENCE.

| 1. | ALPHA | CLD   | WΒ   | CLSN | INH |     |

|----|-------|-------|------|------|-----|-----|

| 2• | BETA  | CLB   | CLP1 | TΡ   | WE  | WBI |

| 3• | ALPHA | CLZ   | WB   |      |     |     |

| 4. | ALPHA | CLI   | WY   | CI   | WS  |     |

| 5. | BETA  | CLSUM | WZ   | CLS  |     |     |

| 6. | BETA  | CLB   | WZI  |      |     |     |

| 7. | ALPHA | CLE   | WB   | WP1  | WS  | WSQ |

#### RESUME

1 I