N72-21205 CR115514

rinal Report

Volume II.

Contract NAS 9-11778

ADVANCED SOFTWARE TECHNIQUES FOR DATA MANAGEMENT SYSTEMS February 1972

# CASEFILE

## INTERMETRICS

OFFICE OF PRIME RESPONSIBILITY

ED5

N72-21203 CR 115514

Volume II.

Contract NAS 9-11778

ADVANCED SOFTWARE TECHNIQUES FOR DATA MANAGEMENT SYSTEMS February 1972

## INTERMETRICS

OFFICE OF PRIME RESPONSIBILITY

ED5

Final Report

Volume II.

Contract NAS 9-11778

ADVANCED SOFTWARE TECHNIQUES FOR DATA MANAGEMENT SYSTEMS February 1972

SPACE SHUTTLE FLIGHT EXECUTIVE SYSTEM: FUNCTIONAL DESIGN

Prepared by:

James T. Pepe

#### FOREWORD

This document is the final report on the functional design of a flight executive system for the Space Shuttle mission. The study was sponsored by the Manned Spacecraft Center, Houston, Texas, under Contract NAS-9-11778. It was performed by Intermetrics, Inc., Cambridge, Massachusetts, under the technical direction of Mr. Joseph A. Saponaro, to whom the author is indebted for his many helpful contributions to the design of this executive system and to the format of this report.

The study program covered the period from June 16, 1971 through February 16, 1972. The Technical Monitor for the Manned Spacecraft Center was Mr. Donald Barron.

The publication of this report does not constitute approval by the NASA of the findings or recommendations contained therein.

#### TABLE OF CONTENTS

| •   |      |                                              | <u>ruge</u> |

|-----|------|----------------------------------------------|-------------|

|     |      |                                              |             |

| • . |      |                                              |             |

|     |      |                                              |             |

| 1.  | INTR | ODUCTION                                     | . 1         |

|     | 1.1  | Scope                                        | 1           |

| •   | 1.2  | Executive System Overview                    | . 1         |

|     |      |                                              |             |

| 2.  | EXEC | UTIVE DESIGN FUNCTIONAL REQUIREMENTS         | · 7         |

| •   | 2.1  | Introduction                                 | 7           |

|     | 2.2  | Space Shuttle Avionics System                | 7           |

|     | 2.3  | Features of the IBM 4 Pi EP Computer System  | 13          |

|     | 2.4  | Executive Design Issues                      | 18          |

|     | 2.5  | Synchronous versus Asynchronous Task Control | 20          |

|     | 2.6  | Interrupt Handling and Task Dispatching      | 30          |

|     | 2.7  | Resource Allocation                          | 32          |

|     | 2.8  | Allocation of Specific Resources             | 34          |

|     |      |                                              |             |

| 3.  | EXEC | UTIVE SYSTEM ARCHITECTURE                    | 43          |

|     | 3.1  | Introduction                                 | 43          |

|     | 3.2  | Executive and Task Structures                | 44          |

|     | 3.3  | Definitions                                  | 48          |

|     | 3.4  | Subroutine Linkage                           | 54          |

|     | 3.5  | Task Priority Levels                         | 59          |

|     | 3.6  | Assignment of Core Memory                    | 60          |

|     | 3.7  | Events                                       | 61          |

|     | 3.8  | I/O Scheduling                               | 67          |

|     | 3.9  | I/O Considerations                           | 67          |

|     |      |                                              |             |

| 4.  | TASK | MANAGEMENT FUNCTIONS                         | 69          |

|     | 4.1  | Introduction                                 | 69          |

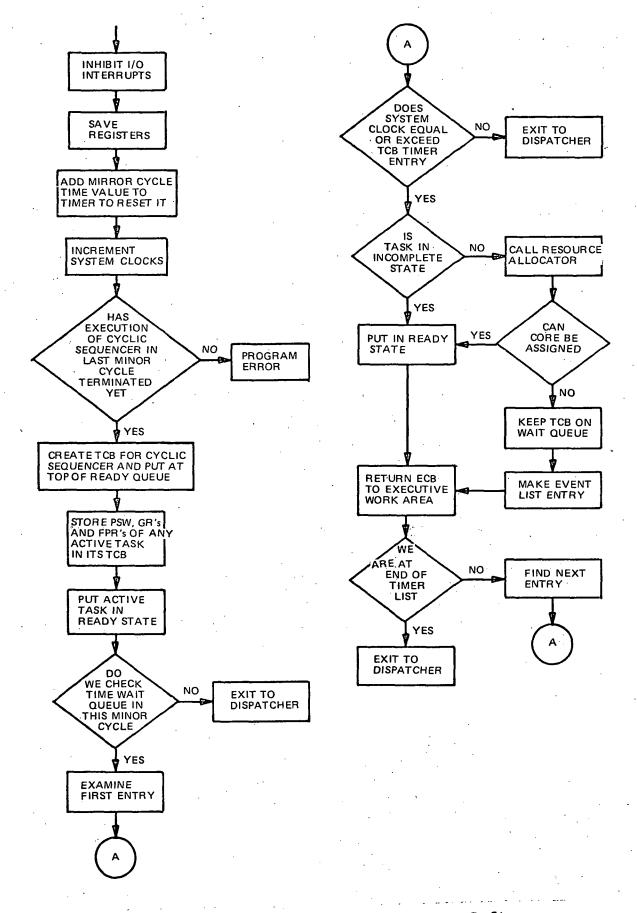

|     | 4.2  | Time Interrupt                               | 89          |

|    | 4.3  | Deadlock Detection                      | 90  |

|----|------|-----------------------------------------|-----|

| 5. | I/O  | MANAGEMENT FUNCTIONS                    | 103 |

|    | 5.1  | Introduction                            | 103 |

|    | 52   | Definition of I/O Management Functions  | 104 |

| •  | 5.3  | I/O Queues and Control Blocks           | 104 |

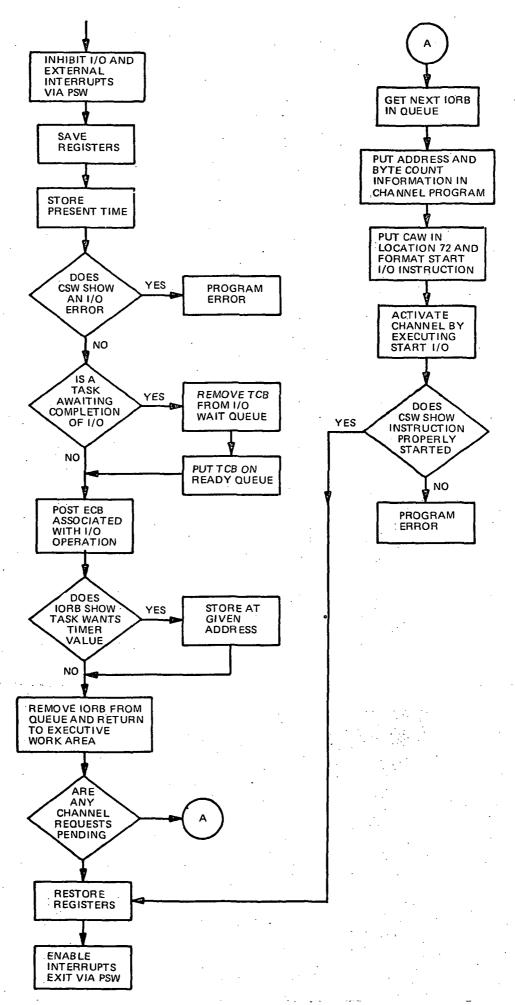

|    | 5.4  | The I/O Supervisor                      | 106 |

|    | 5.5  | I/O Service Routines                    | 107 |

|    | 5.6  | Cyclic and Non-Cyclic I/O               | 108 |

|    | 5.7  | Configuration Dependent Features        | 108 |

|    | 5.8  | I/O Error Correction                    | 109 |

|    |      |                                         |     |

| 6. | CONF | GURATION MANAGEMENT                     | 113 |

|    | 6.1  | Introduction                            | 113 |

|    | 6.2  | Initialization                          | 113 |

|    | 6.3  | Failure Detection and Error Recovery    | 115 |

|    | 6.4  | Failures in a Quad-Redundant System     | 120 |

|    | 6.5  | Mode Switching                          | 121 |

|    | 6.6  | Synchronization                         | 122 |

| •  |      |                                         |     |

| 7. | SECO | ONDARY STORAGE MANAGEMENT               | 127 |

|    | 7.1  | Introduction                            | 127 |

|    | 7.2  | Data Set Structure                      | 127 |

|    | 7.3  | The Secondary Storage Supervisor        | 127 |

|    |      |                                         |     |

| 8. | EXEC | CUTIVE DESIGN PARAMETERS                | 131 |

|    | 8.1  | Introduction                            | 131 |

| •  | 8.2  | Synchronous Versus Asynchronous Control | 131 |

|    | 8.3  | Executive Control Element Sizes         | 132 |

|    | 8.4  | Task Management Parameters              | 133 |

| •  | 8.5  | Supervisor Call Parameters              | 133 |

| 9. | APPLICATION TASK INTERFACES                                       | 135 |

|----|-------------------------------------------------------------------|-----|

| •  | 9.1 Introduction                                                  | 135 |

|    | 9.2 SVC Parameters                                                | 135 |

|    | APPENDIX A - OPERATION AND CONTROL OF THE DATA BUS                | 137 |

|    | APPENDIX B - DATA BUS ERROR CONTROL                               | 163 |

|    | APPENDIX C - LITERATURE REVIEW OF AVIONICS EXECU-<br>TIVE SYSTEMS | 175 |

Chapter 1

Introduction

#### 1.1 Scope

This document presents a top level functional design of a software executive system for the Space Shuttle avionics computer. The design task was accomplished as part of a study entitled Advanced Software Techniques for Data Management Systems. Three primary functions of the executive are emphasized in the design: task management, I/O management and configuration management.

The executive system organization is based on the applications software and configuration requirements established during the Phase B definition of the Space Shuttle program. Although the primary features of the executive system architecture were derived from Phase B requirements, it has been specified for implementation with the IBM 4 Pi EP aerospace computer and ultimately is expected to be incorporated into a breadboard data management computer system at NASA Manned Spacecraft Center's Information Systems Division. Accordingly, the executive system has been structured for internal operation on the IBM 4 Pi EP system with its external configuration and applications software assumed to be characteristic of the centralized quad-redundant avionics systems defined in Phase B.

#### 1.2 Executive System Overview

The major areas of the executive system designed during the course of this study are briefly summarized below with the major characteristics defined.

#### 1.2.1 Control Structure

The executive system is based on a combined synchronous/ asynchronous control structure with priority dispatching for processor allocation and task execution. Cyclic computations are operated at high priority in a synchronous mode under the supervision of a cyclic control executive function. It is initiated by a timer interrupt at a fixed frequency, currently 20 msec, with the scheduling and sequencing of each computation in a minor cycle predetermined and specified via control sequencing tables. The total running time of the synchronous mode or "foreground" is constrained to be at maximum less than a percentage of the minor cycle frequency, the percentage to be established during implementation. After completing the execution of the cyclic computations each minor cycle, the executive dispatches the processor to one of the "ready" tasks in the executive ready queue on the basis of priority. A total of three priority levels have been established for application programs.

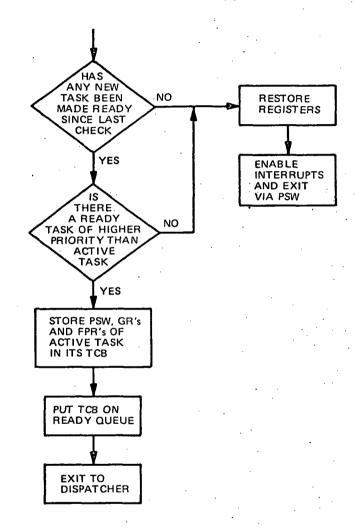

#### 1.2.2 Interrupt and Task Dispatching

All external interrupts within the configuration are fielded and serviced by the executive as in any real time system, allowing a multiprogrammed task environment in the The concept termed "segmented dispatching" is background. however employed for background tasks. That is, although interrupts are immediately serviced by the executive and entries are made in appropriate queues, the interrupted task is resumed and continued until it either ends or until it reaches a segment dispatch point. Only then is a higher priority background task activated by the executive dispatcher. In this way long duration tasks can be organized into reasonable execution segments with task swapping or interruption points more predictable. The dispatching of the cyclic task controller each minor cycle is however an exception and is executed immediately at the occurrence of the minor cycle clock interrupt. This exception is made as a reasonable tradeoff to provide the timing and response characteristics needed for cyclic computations ultimately assigned in the synchronous mode. This subject is discussed more fully in Chapter 2.

#### 1.2.3 Task and Event Scheduling

Any executing task may request the executive to schedule another task on the occurrence of an event or a specified time. Events are system defined in scope and may be posted or deposted by application tasks via the executive.

#### 1.2.4 Memory Organization and Allocation

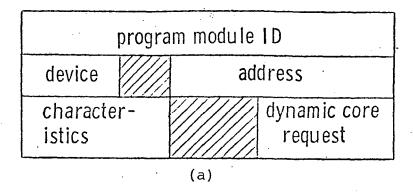

All application software program modules are known to the executive via a program module directory. Programs are defined as either total mission resident or mission phase resident. Phase resident programs are loaded from the secondary storage device into their assigned portion of the operating memory by the phase initiation function of the executive. Dynamic memory is allocated to each task by the executive, when a task is made ready for execution, out of a subpool of working memory established for each priority level. Dynamic memory requirements are preestablished and defined for each program in the directory. Memory is allocated in continuous blocks within the priority pool and addressing is accomplished via base registers on the EP computer.

A portion of the memory is dedicated to shared data. The common memory pool, the compool, is organized into mission dependent resident data and an overlaid area for phase dependent data. The phase dependent shared memory is initialized with the program load at phase initiation and statically assigned during the phase. All access to the common data is controlled through and by the executive. The executive prevents conflicts in memory utilization by placing the conflicting task in a wait state until the memory is properly released by the task to which it is presently assigned.

#### 1.2.5 I/O Control

Control and execution of all input and output operations are performed by the executive system. Input/output services are performed in two modes: on demand via request by an executing task, or table driven as in the case of cyclic computations in the synchronous mode. Secondary memory management is under the control of the executive. Limited use of the secondary storage device is assumed during any mission phase. The executive is responsible for the maintaining of tables of current status and communication paths to all redundant equipment within the system configuration.

#### 1.2.6 Configuration Management Error Recovery

The executive responds to all system hardware and software detected error conditions and supervises reconfiguration of the system. A standard system error recovery action is defined for each error class. Application tasks may invoke during execution local recovery for a class via specification of a task re-entry point.

#### 1.2.7 Executive Functions as a Summary

The specific functions that the executive performs within the scope of its design to insure the overall integrity and proper execution of application tasks are the following:

- a) control allocation of the processor by scheduling and dispatching both periodic and nonperiodic tasks;

- b) provide timing and event handling services to insure proper scheduling of tasks;

- c) supervise and control all I/O operations;

- d) allocate all resources to tasks and avoid conflicts; resources include dynamic memory, secondary storage and shared memory;

- e) provide methods for controlling conflicts over shared memory;

- f) maintain and update all system queues and tables;

- g) provide the means of hardware error recovery and system reconfiguration;

- h) provide linkage and common subroutines and executive services in application tasks via controlled simple interfaces.

#### 1.3 Task Objectives and Approach

The executive system design task was accomplished in conjunction with other major tasks of the study. Its primary objectives were threefold:

a) review the Phase B avionics configuration and software requirements and identify major functions of the executive system;

- b) analyze and determine key aspects of the executive structure such as: methods of task scheduling and control, external interrupt control techniques, task dispatching algorithms, allocation and sharing schemes, and application program interfaces;

- c) develop functional logic and algorithm design for the task management, I/O management and configuration management modules of the executive system. The design is to incorporate definition of application program interfaces to the executive.

The approach taken in this task was based upon several constraints and necessary assumptions about the nature of the Space Shuttle mission.

- 1) The application software is not completely defined. Hence, specific parameters, such as the amount of dynamic memory needed, can not now be decided. This topic is again discussed in Chapter 8.

- 2) The software system we are developing is a kernel executive system for use in the Space Shuttle Data Management computer. It is not an operating system for a ground based system.

- 3) The breadboard data management computer system at NASA Manned Spacecraft Center's Information Systems Division is not at present completely specified. Thus, several assumptions concerning the design are made and pointed out in later chapters.

- 4) The executive features incorporated in this design are those deemed necessary to execute the application software as far as it is defined in the Phase B Study Reports [1,2].

### Page Intentionally Left Blank

#### Chapter 2

#### Executive Design Functional Requirements

#### 2.1 Introduction

The fundamental features of an executive system must be based on the requirements of its environment and the application software it controls. Ideally, it should be efficiently tailored to meet the design objectives and operating environment of the total system. Prior to discussing the design chosen, the purpose of this chapter is to review major system requirements impacting on executive system architecture. These topics include: aspects of the avionics system configuration and applications software, and the organization of the host computer system. Finally, several key issues relative to the selection of a particular executive system structure (as it influences task control, resource allocation and interrupt handling) are discussed with respect to the appropriate design considerations.

#### 2.2 Space Shuttle Avionics System

#### 2.2.1 Configuration

The Phase B Space Shuttle avionics systems have been reviewed and are discussed in Volume 1 of this study. Although more than one Phase B design was reviewed, a hypothetical system configuration is briefly described incorporating the important features of the designs to the software executive.

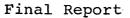

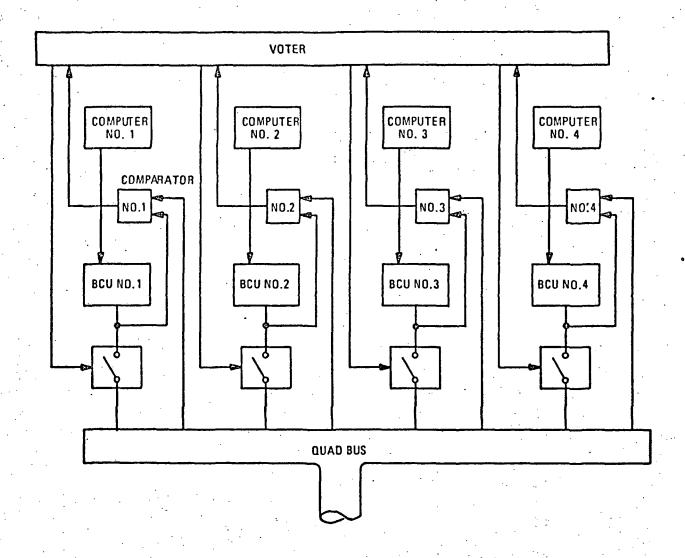

The avionics configuration assumed consists of a centralized data management computer system interfaced to all avionics subsystems via a high speed time multiplexed serial data bus system as illustrated in Figure 2.1. The data management computer system consists of quad redundant computers which operate in a simplex redundant mode.

During critical phases of the mission more than one computer is operating with one of them designated as the prime computer. The prime computer transmits and receives all commands and

and data over the data bus to the avionics subsystems. The standby computers are synchronized with the prime computer via external control and execute the identical software. Outputs from the prime computer are monitored by the standby computers and compared via hardware by its bus control unit in lieu of transmission. The results of the comparison are sent to external control unit and crew operator personnel for voting and switching.

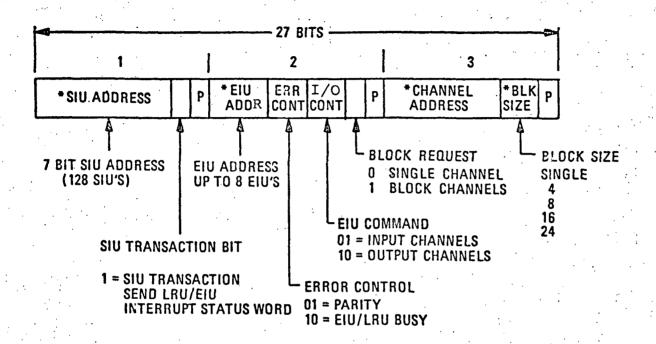

The data bus system consists of a bus control unit (BCU), 4 bus lines and remote interface units (IU) for equipment connection. The BCU functions as a peripheral under command from the computer and controls the transmission of information over the bus. It communicates with the IU which in turn acquires, converts and sends data to and from the subsystems. The bus system operates in a "command response" mode in which data is sent only when requested by the central computer. operation and control of the bus is described more fully in Appendix A. There is no provision for interrupts from the subsystems. Each bus line carries serial digital data at l MBPS. The bus system is quad redundant with each BCU capable of transmitting on each of the four buses; however, each computer interfaces with only one BCU. Redundant subsystems are interfaced to physically separate bus lines via the interface The computer system is also interfaced to redundant secondary storage units. These units contain additional programs and data tables for various mission phases. For the purpose of executive design it will be assumed to have limited use during a phase with restricted write access. Also for purposes of executive design, it will be assumed that other external units may be interfaced to the computer directly and not via the data bus such as display and control subsystems.

#### 2.2.2 Application Software

The total onboard software has been estimated (during Phase B) at requiring approximately 50,000 32 bit words of operating memory and a peak rate speed of approximately 200,000 equivalent adds operations per second. For purposes of this discussion the total flight software for the Space Shuttle central computer system may be broadly classified into two areas: the executive and mission applications software. The application software is under the control of the executive and supports all phases of the mission: boost, insertion, orbital operations, coast and powered flight, rendezvous, docking, undocking, entry and landing. The applications software to support these phases comprises the following functional areas:

- a) flight control and stabilization

- b) guidance

- c) navigation

Figure 2.1 Avionics Computer Configuration

- d) trajectory targeting

- e) crew displays and control

- f) onboard checkout and systems monitoring

- g) avionics subsystem management and support.

Estimates of size, data requirements and frequency of operation of this software have been estimated during Phase B. The flight control and stabilization function place the highest respond time demands on the system and have been estimated at basic frequency of approximately 20 msec. Subsystem and status monitoring rates are significantly less at 1 sample/sec being the average although the number of such samples and processing loads are greater. Targeting, navigation and guidance schemes are characteristic of more lengthy, iterative mathematical calculations, requiring large CPU utilization.

The full impact of crew interaction via display and control is not completely determined. It is evident however, they will require the capability to interact through the display to: load programs and data, select major program modes for execution, terminate execution, request displays, select control options, configure and reconfigure equipment, and monitor the status of avionics subsystems. The crew will also interact with the computer through other controls such as the rotational hand controller when flying under pilot control.

These requirements indicate the Shuttle software environment to include three types of tasks:

- a) cyclic tasks: Tasks which are performed on a periodic basis at varying frequencies.

- b) response/request tasks. These are tasks which are performed in response to a pre-selected mode such as the rendezvous mission mode. Generally these tasks are major sequences or functions initiated throughout the mission by the crew.

- c) demand tasks: These are tasks which must be performed at the occurrence of a system event or certain time.

#### 2.2.3 Data Rates

In the Phase B avionics design concept, the data bus system provides a communication path between the avionics equipment and the prime computer complex. No general requirement for terminal to terminal communication which cannot, or should not be routed through the computer complex was identified. The exact number and type of subsystems has been continually changing. A representative list provided below is presented to indicate the scope of the system.

- Primary propulsion subsystem: this system consists of two orbital insertion engines and one orbital maneuvering engine.

- 2) Reaction control subsystem: at least 20 RCS jets located in the nose, wings and tail for effecting rotation and translation in space.

- 3) Hydraulic system: hydraulic power generation, distribution, control, and conversion of mechanical energy. It consists of supply lines, gimbals, pumps, aerodynamic surfaces, flaps, wheel controls, etc.

- 4) Electrical power generation and distribution system: fuel cells and battery, and the auxiliary power units located throughout the Shuttle.

- 5) Navigation aids/air data: a collection of equipment providing navigation and landing capabilities (ALS, radar altimeter, TACAN, DME, etc.).

- 6) Environmental control system: the environmental control system provides temperature, pressure, and humidity control of equipment, equipment bays, and personnel compartments.

- 7) Cryogenic system: contains the hydrogen and oxygen for the primary propulsion, the reaction control system, the fuel cells and the auxiliary power units.

- 8) Displays and controls: this system is assumed to have local processing capability and accepts dynamic data through the bus for updating of display parameters.

- 9) Telecommunication: this system consists of various transmitters and receivers including S-band, C-band, VHF, telemetry encoder, EVA communications, air traffic control communications, etc.

- 10) Guidance, navigation and control: this subsystem is composed of elements necessary to control, stabilize and navigate the Shuttle vehicle during all phases of the mission. It interfaces to the reaction control system, jet engines, aerodynamic control surfaces, and landing gear, etc. It has access to sensors which include the

inertial subsystem, horizon and star trackers, approach landing aids, rendezvous radar, radar altimeter, etc.

Although this list of subsystems may not be complete for the final organization of the avionics system it is meant to be representative. It is estimated that approximately 150 to 250 LRU's are associated with the subsystems listed above.

#### 2.2.4 Data Requirements

The following is a summary of the data requirements abstracted from the various studies of Phase B contractors.

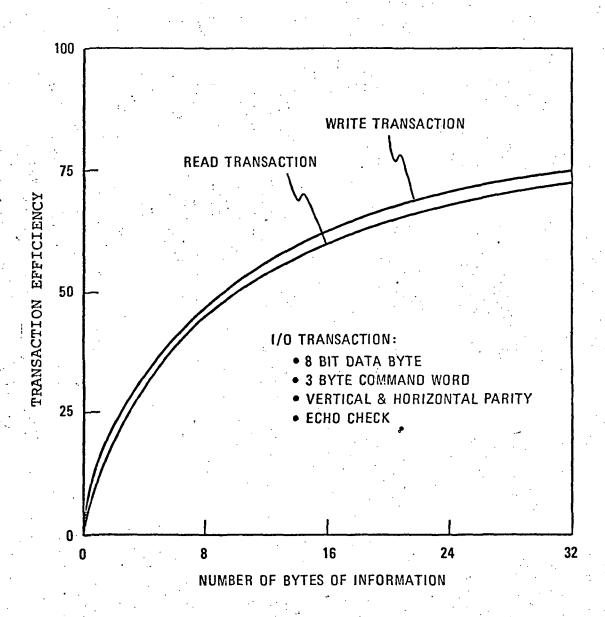

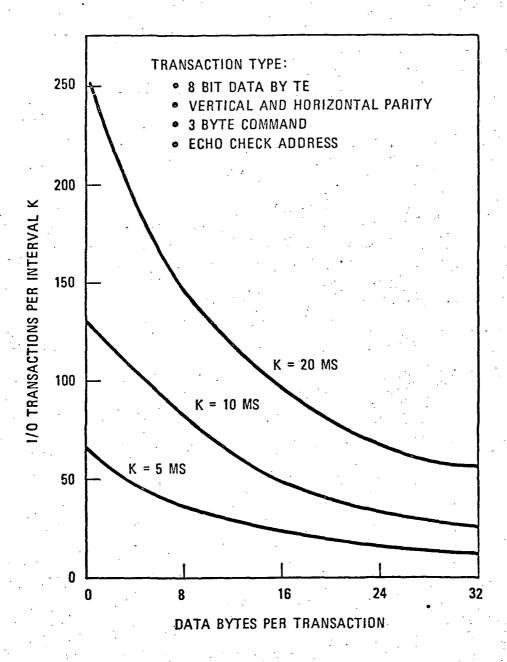

- 1) Speed. Peak load estimates of data rate for both the Shuttle and orbiter have ranged between 100,000 and 250,000 bits per second, including overhead. Considering an average overhead of approximately 50% for each bus transaction and allowing for a minimum of 100% expansion to the maximum speed, a capability of 106 bits per second has been assumed to be an adequate requirement. This speed should allow the computer to acquire data at a rate of approximately 10,000 average transactions per second.

- 2) Measurements. Estimates have ranged between 4000 and 6500 unique data points to be sampled from the total complement of avionics equipment by the central computer. Data types include:

digital parallel digital serial analog discrete

The majority of these data points are measurements input to the computer, and are estimated at approximately 60% to 70% of the traffic on the data bus.

Response time/sampling frequency. The maximum sampling frequency of measurements is estimated at fifty samples per second. The average sampling frequency for status information is between two and five samples per second. Very little information was made available on response requirements and load distribution of subsystems.

#### 2.3 Features of the IBM 4 Pi EP Computer System

The hardware features of the computer can directly influence the executive system software design. In this section the most pertinent features of the IBM 4 Pi EP computer assumed in the executive design are presented for review. 4 Pi EP hardware is documented in detail in the IBM Programming Manual for System 4 Pi Model EP [3].

#### 2.3.1 Computer Organization

The EP is a byte addressable computer with two bytes constituting a half word, four bytes a full word, and eight bytes a double word. The EP memory size for the computer in the ISD breadboard is assumed at 24K 32 bit words. An additional 16K multiport buffer memory may be incorporated; yet its status is unknown at this time.

There are 16 general registers (GR) of full word size used for high speed fixed point and logical operations and four floating point registers of (FPR) of double word size used for floating point operations.

The instructions are organized into four classes: register to register (RR), register to indexed storage (RX), register to storage (RS), and storage and immediate operand (SI). A complete list of all instructions may be found in reference [3].

All addressing of core storage within instructions is done relative to a base address stored in one of the general registers, designated the base register. Many instructions' address fields can reference up to 4K bytes beyond a base address by adding a 12 bit displacement to the contents of a base register. RX instructions further extend this addressing capability by also allowing indexed addressing.

#### 2.3.2 Interrupts

There are five classes of interrupts in the EP.

- a) I/O interruptions allow the CPU to respond to conditions in the channels and I/O units.

- b) Program interruptions signal unusual conditions encountered in a program, e.g., incorrect operands and operand specifications. This class of interrupt may be subdivided into nine subclasses identified by the interruption code generated by the EP. The subclasses are:

- 1) Operation Exception: operation code unassigned

- 2) Privileged-Operation Exception: a privileged operation is encountered in the problem state

- 3) Specification Exception: incorrect operand specification

- 4) Fixed Point Overflow Exception

- 5) Fixed Point Divide Exception

- 6) Exponent Overflow Exception

- 7) Exponent Underflow Exception

- 8) Significance Exception: the result of a floating point add or subtract has an all zero fraction

- 9) Floating Point Divide Exception

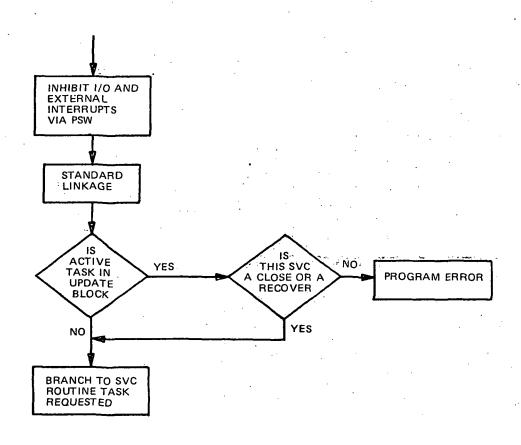

- c) Supervisor call interruptions result from the execution of a SVC opcode. This interrupt is used to switch from the problem state to the supervisor state in which privileged instructions can be executed.

- d) External interruptions allow the CPU to respond to signals from the interruption key on the system control panel and the timer. The timer is a full word in main storage location 80. An external interrupt is generated when the value of the timer goes from positive to negative. A timer is essential to the executive system. The exact details of the timer in the breadboard are not known as of this time.

- e) The machine check interruption occurs when a hardware error is encountered. A diagnostic procedure is automatically initiated.

Should several interrupts occur simultaneously they are honored in the following order:

- 1) machine check;

- 2) program or supervisor call (mutually exclusive interrupts);

- 3) external:

- 4) I/O.

Each of the five interrupts described above has two related program status words (PSW) associated with them in unique main storage locations (see Figure 2.2). An interrupt causes the current PSW to be stored in the "old" position and the PSW in the "new" position to become the current PSW. The old PSW contains all the information necessary to resume the problem program again at the point of interruption, and the new PSW allows executing a routine associated with the interrupt.

As mentioned above the supervisor state (as distinct from the problem state) allows a class of privileged instructions to be executed. The executive uses these instructions to maintain the integrity of the system. Examples of privileged instructions include direct I/O operations, setting system masks, and setting PSWs. To prevent their use by application tasks a program interruption is generated when a privileged instruction is encountered in the problem state.

The supervisor state can also be used to protect the executive from invalid access by application tasks. Hence, SVC operations provide the means for application tasks to correctly use the executive, and they help insure that an application task does not alter the executive.

#### 2.3.3 4 Pi Input/Output Via Standard Channel

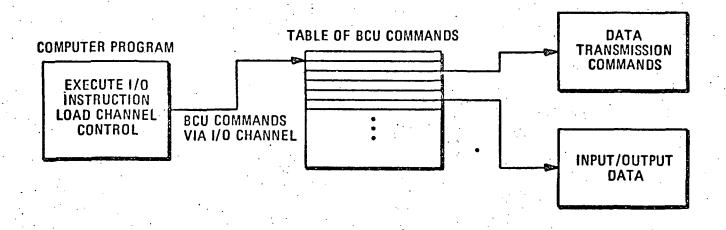

Another important EP hardware feature is the structure of the I/O control system. Since the structure of I/O operations depends heavily upon the channel control structure and its operation, I/O management will be one of the most configuration sensitive areas of the executive software. Hence, a clear understanding of the EP's I/O system is necessary.

All I/O operations are initiated by a START I/O instruction. If the channel is free, this instruction is executed, and the CPU continues processing its program. Then the channel, independent of the CPU, selects the I/O device the instruction specifies.

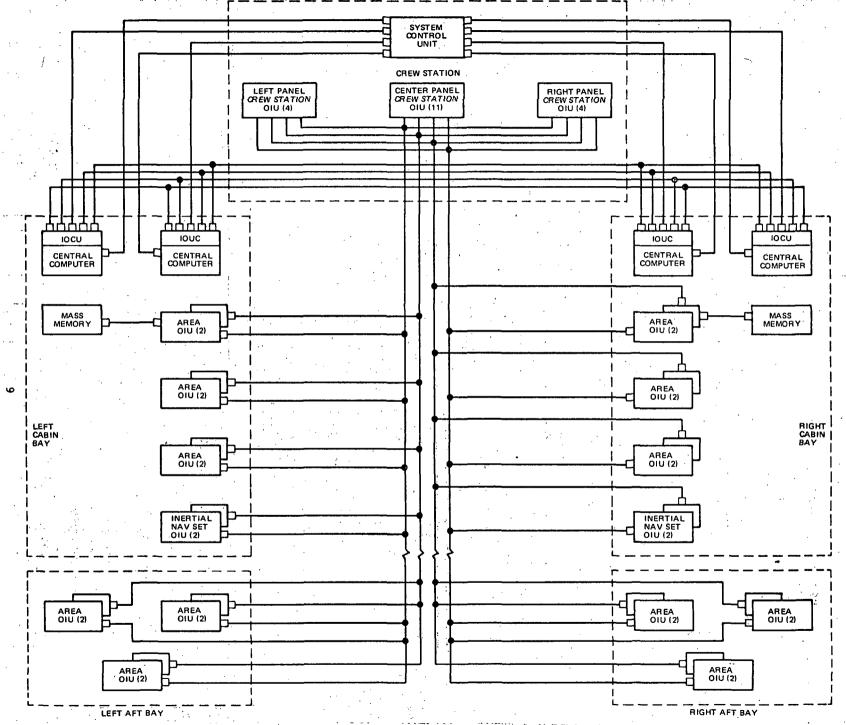

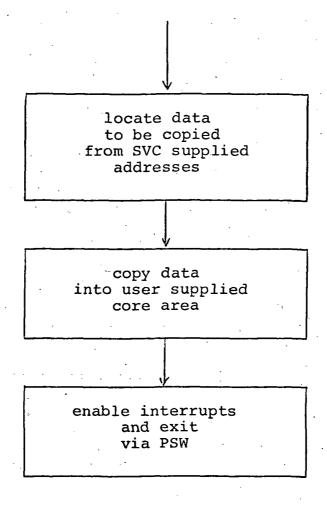

START I/O causes the channel to fetch a channel address word (CAW) from main storage location 72. This word points to the main storage location where the channel program begins. The channel program is a series of chained channel command words (CCW), each of which contains a command code to the channel as well as main memory data addresses and byte counts. See Figures 2.3 and 2.4 for the CAW and CCW formats.

Should an I/O command be rejected during execution of a START I/O (by a program check, busy condition, etc.), the command rejection is indicated in the PSW. The details of the conditions that prevented I/O initiation are given in the channel status word (CSW) which is stored in main storage location 64 when the command is rejected (see Figure 2.5). The CSW is formed or reformed by START I/O, TEST I/O, or an I/O interruption. This word contains information about the termination of an I/O instruction. An error recovery program that is initiated because of an I/O error will depend heavily upon the CSW to determine the cause of the error and whether a system reconfiguration is necessary.

| System<br>Mask | Key | AMWP            | Interruption<br>Code   |

|----------------|-----|-----------------|------------------------|

| ILC            | CC  | Program<br>Mask | Instruction<br>Address |

Figure 2.2 Program Status Word Format

| Key 0000 Command Address |

|--------------------------|

|--------------------------|

Figure 2.3 Channel Address Word Format

Figure 2.4 Channel Command Word Format

| Кеу 0000 |        | Command Address |       |

|----------|--------|-----------------|-------|

|          | Status |                 | Count |

Figure 2.5 Channel Status Word Format

#### 2.3.4 4 Pi EP Data Bus Input/Output

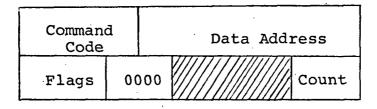

The 4 Pi computer in the DMS breadboard (Figure 2.6) will be interfaced to a bus system via a stored program data processor (SPDP). The details of this interface and method of operation are currently not known. Accordingly, by direction, the executive design has been based upon interfacing to a Phase B type of bus system described previously. It is anticipated that the functional organization of executive I/O management will remain the same.

#### 2.4 Executive Design Issues

In conjunction with the review of the avionics system requirements, several factors of the basic executive system structure were evaluated. The purpose of this and succeeding sections is to discuss these issues.

Prior to performing the analysis several design goals were established to be used as guidance in selecting an ultimate design approach. Primary considerations of the executive structure analyzed are:

- a) synchronous versus asynchronous task control;

- b) interrupt handling and task dispatching;

- c) resource allocation;

- d) shared data;

- e) secondary storage management.

The primary objective or goal usually adapted by most executive system designers is the achievement of an "efficient" executive where efficiency is some measure of throughput. Efficiency may be defined by either the fraction of executive overhead time spent doing nonproductive work or in terms of response time. In performing analyses of these issues, efficiency was considered a necessary but not primary factor since it often tends to lead towards complex design resulting in complex testing and verification of software. Ideally, flight software should not only be tailored to meet operational mission requirements but should be structured to enhance software verification and flexibility to adjust to changing needs. Therefore, the following design criteria were used as evaluation of the executive structure.

Figure 2.6 ISD Breadboard Data Management System

- a) To provide an executive system which will control and allocate resources of the system to satisfy operational mission requirements (i.e., one that does the job).

- b) To establish an executive organization which facilitates verification of application software and reliability of code.

- c) To structure an executive enabling flexibility and modularity in incorporation of application software changes over long term maintenance periods.

- d) To define simple and well defined application program interfaces to the executive system. It should be structured as a virtual machine to the applications programmer.

- e) To develop an executive structure which is both simple and efficient but consistent with other objectives.

#### 2.5 Synchronous versus Asynchronous Task Control

A primary function of the task management portion of the executive is the scheduling, dispatching and control of the allocation of processor to task in the job stream. It is a fundamental feature of the executive system. Most large ground based computer systems incorporate very flexible and general task scheduling and dispatching algorithms to accommodate a varied number and type of users. The Shuttle software on the other hand, is more tailored to its environment. Although Phase B contractors have specified synchronous structured executives, shuttle software requirements do not allow task scheduling to be completely planned in advance. Furthermore, it is our contention that a pure synchronous structure would ultimately be modified to accommodate priority based event handling since it is necessary as a Shuttle software feature. We have chosen a design which accommodates the best features from each control structure. following presents the advantages and disadvantages of synchronous versus asynchronous control.

#### 2.5.1 Synchronous Structure

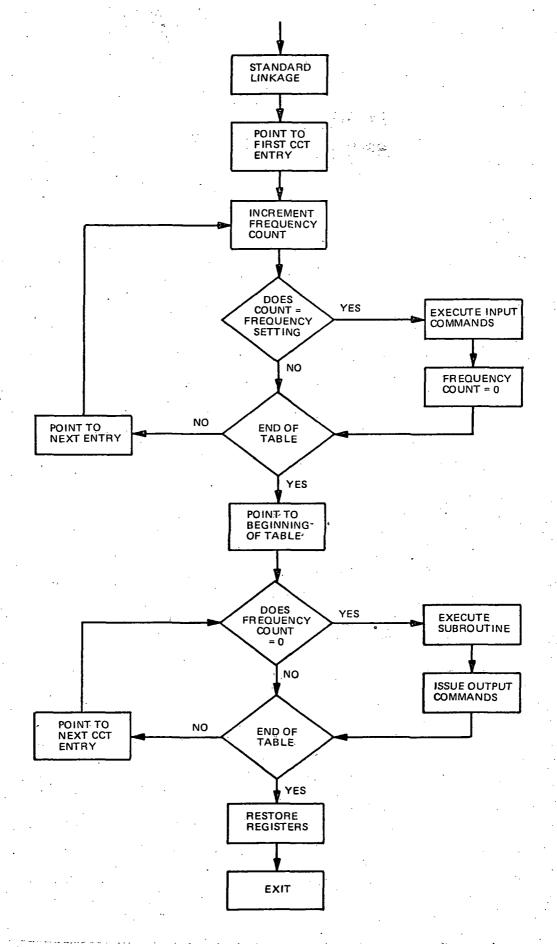

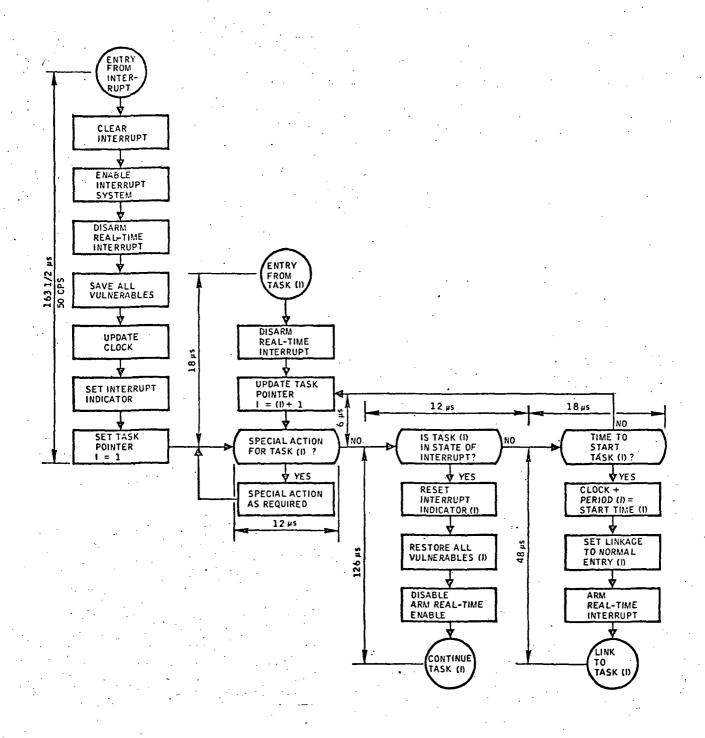

A synchronous structured executive is based on a timer-interrupt, fixed schedule, time slice mode of operation. For example, Shuttle baseline designs use a 20 msec interval as a basic reference frame for the system, providing a minor cycle sampling rate of 50 cps. Under this concept jobs are organized by the designer into short routines, and when the executive detects a timer interrupt (i.e., every 20 msec) it

examines the "task schedule tables" to determine which set of routines is to be operated during the next program interval. Each 20 msec interval contains all 50/sec tasks and a selection of other lower frequency tasks. The minor cycle is operated every 20 msec, and a percentage of that time is distributed among the tasks that are assigned to each minor cycle. A background job may be run in the slack time before the next minor cycle. Each task is statically structured as a subroutine such that it can be dynamically called and returned to the executive.

Using a command response data bus control concept, scheduling I/O in a synchronous structure is similar to the scheduling of tasks. The I/O requirements for each mission phase or major cycle are predetermined and synchronized with the structure of tasks operated in the major cycle. The I/O request list is assumed to be fixed. Since the I/O requirements will have different frequencies, they are incorporated in each minor cycle in correspondence to load balancing of the processing tasks.

For example, assume all I/O requirements for a particular mission phase are organized into three categories of frequencies: 50 times/sec, 5/sec, and 1/sec. Assume that X, Y, and Z are the number of commands in each category. Assume further that a minor cycle occurs every 20 ms and that a BCU is commanded with a list of I/O requests each minor cycle. The averaged number of I/O operations required to be scheduled each minor cycle are: all of the 50/sec requests, 1/10 of the 5/sec requests, and 1/50 of the 1/sec signals. In a synchronous structure tables of predetermined I/O requests are organized according to sampling frequencies. The appropriate number of I/O entries to command each minor cycle are selected from these tables. The synchronized concept attempts to avoid non-deterministic behavior of I/O, I/O queues, and I/O backlog.

Several types of I/O activity cannot be determined in advance; for example, the command of jets on and off. The I/O scheduler may accomplish this by providing a place for the command in the appropriate list and then causing the BCU to skip the command or incorporate it, depending on the results of the stabilization and control tasks.

#### 2.5.2 Example of a Synchronous Executive

For purposes of illustration the basic functions performed by a synchronously controlled executive include:

a) managing data bus I/O by issuing all I/O requests for the minor cycle; b) managing task execution by executing all high frequency tasks; deciding what tasks executed at a less frequent rate must now be done and executing these; and doing background and/or housekeeping functions in any slack time.

To enable the executive to perform these tasks with the least amount of overhead, judiciously organized system tables must be used. A description of the contents of the types of tables is presented below.

A cyclic command table (CCT) lists all tasks and the frequency they are to be done in a given mission phase. In other mission phases a different table is used, which can be stored on a mass storage device until it is needed. For example, a typical entry would be

| frequency | program module<br>ID | core<br>address |

|-----------|----------------------|-----------------|

|           |                      |                 |

It must also contain pointers to the I/O requests for every minor cycle. That is, in a particular minor cycle all I/O requests are known in advance since a synchronous structure is deterministic. Thus, the executive can issue all I/O requests at once. For example, consider the following CCT entries:

| Frequency                     | Module | Address      |

|-------------------------------|--------|--------------|

| every                         | A      | 1000         |

| minor                         | B      | 2000         |

| cycle                         | C      | 3000         |

| every<br>other minor<br>cycle | D<br>E | 4000<br>5000 |

| every                         | F      | 6000         |

| four minor                    | G      | 7000         |

| cycles                        | H      | 10000        |

The order of execution of these program modules every four minor cycles would be the following

| Minor Cycles | Modules  |

|--------------|----------|

| N            | A B C    |

| N+1          | ABCDE    |

| N+2          | A B C    |

| N+3          | ABCDEFGH |

Should D take an abnormal exit during the (N+1)st minor cycle, and deschedule E, the order then becomes:

|    | Minor Cycles | Modules  |

|----|--------------|----------|

|    | N            | АВС      |

|    | N+1          | ABCD     |

| ٠, | N+2          | ABC      |

|    | N+3          | ABCDEFGH |

A flowchart of a synchronous executive structure is presented in Chapter 4.

#### 2.5.3 Advantages of Synchronous Structure

- a) There is minimal overhead for scheduling and dispatching because all tasks are known to the system in advance, and hence, are prescheduled. The executive knows which fixed set of code to execute in each time slice.

- b) The executive design is simple and thus easy to program.

- c) The system is not multiprogrammed so no queues of ready and waiting tasks have to be maintained. In other words, more than one task is never in contention at any time for the processor. One fixed set of code is executed in each time slice. Memory conflict problems are also eliminated since core and word areas for all programmers are pre-allocated.

- d) The system is deterministic which makes the task of software verification easier. A programmer must divide a long program into segments to evenly distribute over several time slices. The break points can occur at places at which he knows no interrupting program can interfere with his program or data.

- e) The computational and I/O load will be balanced over a major loop. Thus, no degraded response can occur

because of computational or I/O overload. Response is predictable.

f) The predictability of the system eliminates sharing problems. Programs can be put together in time slices so that no data sharing problems result. This fact eliminates the need for a central update routine for data. Also, the need for reentrant coding, and hence, dynamic storage allocation, is eliminated.

#### 2.5.4 Disadvantages of Synchronous Structure

- a) Application programming is more difficult especially for long programs. The programmer must break such a program into segments so that between segments any running program cannot interfere with his program or data. Also, fitting his program segments into time slices with other program segments is difficult. Timing requirements of each segment must be known before these can be fitted together in a time slice. Thus, the programmer has a second constraint, namely, time bounding his segments.

- b) Changing application programs or mission programming requirements can be a major redesign. Such a change can require rebalancing of the entire computational load. New requirements can mean having to spread the existing application programs more thinly over the time slices of a major loop, so that the new programs can also be fit. That is, each existing program segment might be restricted to a smaller time bound, and hence, reprogramming will result.

- c) Each time slice must accommodate the worst case computational requirement. For example, if the crew is provided the option to display a parameter during a particular mission phase, then the calculation of that parameter will have to be incorporated into the sequence whether or not the crew ever requests it.

This situation is particularly bad if more tasks are added to the system. If in the worst case 80% of the computer's time is being used, a task having a worst case requirement of 25% cannot be accommodated. If it were accommodated, some time slice would have a worst case requirement of over 100%. This situation is unacceptable in a synchronous structure.

d) A synchronous structure does not allow tasks to be run on a time or event basis. In particular, this type of fixed-sequence executive organization does not provide a structure which allows for external interaction by the crew, or which copes with a random job stream. Jobs must be predetermined and assigned to slots in a sequence and must operate within the basic reference framework. It is not clear at this point whether all Shuttle requirements can be so predetermined.

Both Phase B executive designs allow tasks to be scheduled on an event basis. That is, when an event occurs a task can then be scheduled. A scheduler is used to fit the newly scheduled task into the time slices and to deschedule lower priority tasks when necessary. Such an executive cannot be fully synchronous, as defined and described above.

#### 2.5.5 Asynchronous Structure

In an asynchronous control structure scheduling and allocation of the processor are accomplished in real time according to the needs of the operating environment. Under this concept processing tasks are assigned a priority which establishes their relative importance to each other. A task with a given priority runs until a wait is encountered, or the existence of a higher priority task is established.

The distinction between synchronous and asynchronous control structure can be illustrated by the "states" in which a task will exist while operating under each structure. In a synchronous structure, tasks are in one of two states: actively running or not running. At any instant of time only one task is in the running state and all others are not running. The transition to the running state occurs when a task's scheduled time slot arrives.

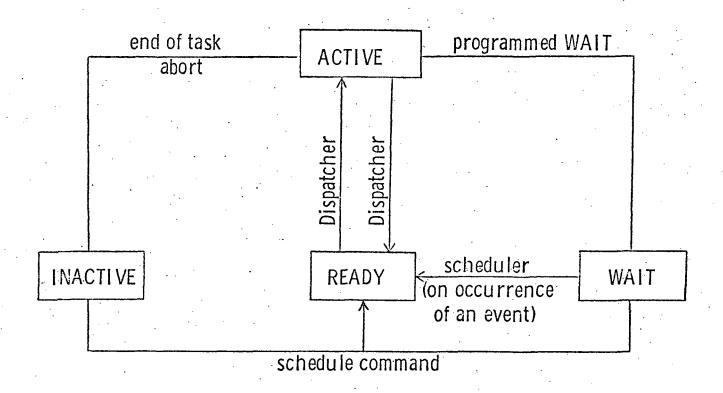

In an asynchronous structure, a task, while present in the system, will exist in one of four states: running, waiting, ready, or inactive. The executive insures the proper transition of states depending upon either internal or external stimuli. The running state definition is obvious. Note that the running state can only be entered from the ready to run state. This unifies the dispatcher functions. The waiting state is either a voluntary or involuntary state, depending upon its cause. A voluntary wait would be a wait for completion of I/O, or perhaps some external time stimulus. An involuntary wait would be awaiting resources (e.g., memory) to become available. The inactive state occurs when the task is neither running, waiting, or ready.

The ready state can be entered from all other states and indicates that a job has all the facilities available to it to run. The function of the dispatcher is to pick the most appropriate task from the ready queue and start it running.

State changes from wait to ready would occur when the awaited stimulus has occurred. The change from limbo to ready state occurs when a schedule request is issued by some task. The switch from running to ready occurs when a task is preempted by a higher priority task or interrupt.

In summary, an asynchronous structure is one in which one or more tasks may be in the ready state awaiting allocation of the processor. In a simplex computer system this is termed multprogramming, i.e., the concurrent operation of more than one task.

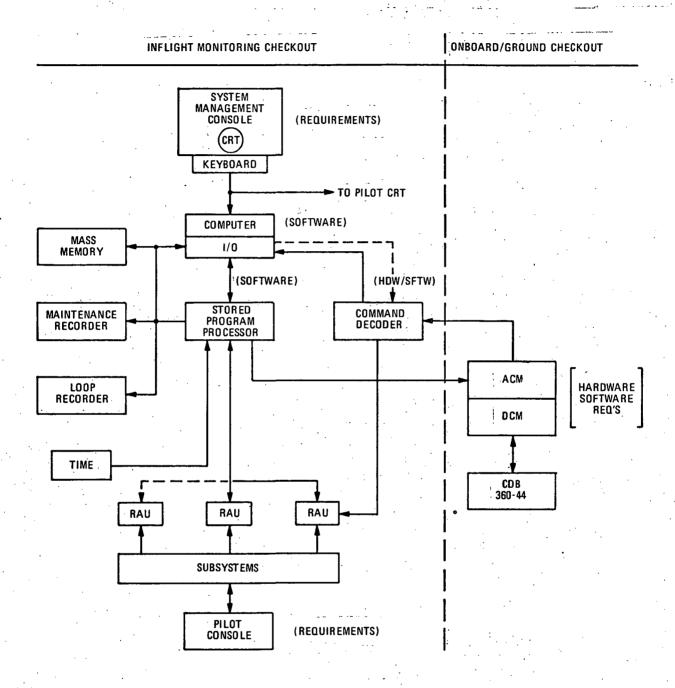

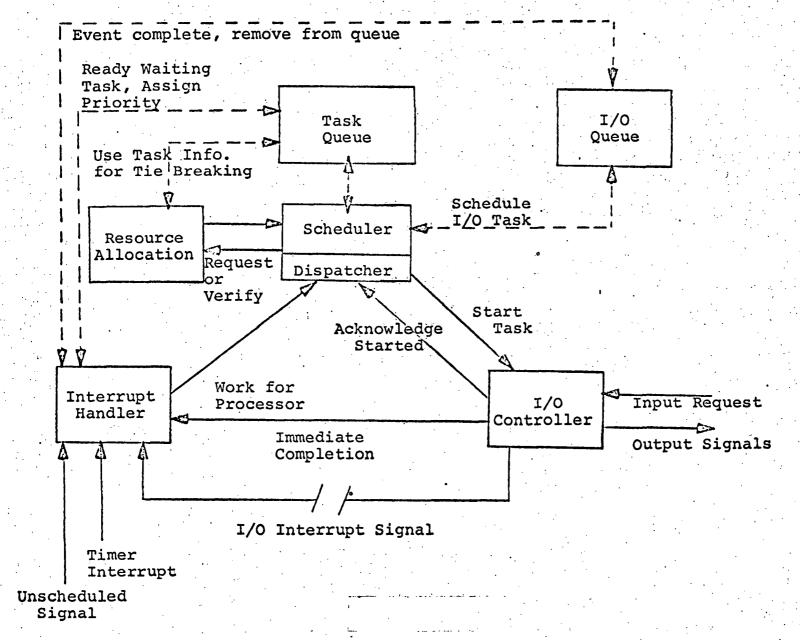

An overview of the operation of a general asynchronous executive is illustrated in Figure 2.7. The scheduler and dispatcher, once in control, should be able to pick a task and run with it. The scheduler assigns or reassigns task priorities, verifies that all the task resources are available, and maintains the overall view of real time events. All task starting is done through the dispatcher.

The scheduling function in a broad sense consists of making appropriate entries in task blocks and priority queues so that the dispatcher need only select jobs from the top of the ready list. If there is a number of tasks to be scheduled, the scheduler treats some as more important than others and executes them first. If the dispatch function occurs at some time other than at the end of a program, then a multiprogrammed environment is a direct result.

The interrupt handler "posts" the event complete, makes the task ready if possible, and then passes control to the scheduler to act on the information it has provided.

The resource allocator is invoked as an executive function by the scheduler to test readiness to run, and if not ready, will inform the scheduler of the requirements for readiness. It may also be invoked to test availability of contention items.

I/O in an asynchronous structure is generally scheduled on a demand basis. An active task requiring I/O schedules its request via an I/O queue. The task is placed into the wait state until completion of the I/O request. The I/O

control routines operate on the I/O queue and interface the I/O peripheral (i.e., the bus system) to perform the request. I/O is performed asynchronously with other processing tasks in the system. After acknowledging receipt, initiation or completion of the I/O request, the scheduler is informed via a simulated or actual interrupt. The task awaiting the I/O request is then placed into the ready state and awaits processor assignment. However, demand scheduling may not be easily implemented in the Shuttle software due to the high speed of the BCU as a peripheral and the intended block scheduling.

#### 2.5.6 Advantages of Asynchronous Structure

- a) It is able to adapt to a random job stream; i.e., it does not require rebalancing of a computational load, and it can tolerate periodic overload and backlog since it is designed to cope with this problem. Time and event scheduling can easily be accommodated.

- b) It is more adaptive to a real time environment. If a task of high priority must be scheduled, it is not necessary to deschedule a lower priority task. The task dispatcher selects this high priority task for execution while lower priority tasks remain in the ready state. Lower overhead results.

- c) Application programming is easier. An asynchronous structure does not require long program sequences such as targeting, etc. to be arbitrarily organized into fixed segments to fit in some fixed cycle or sequence.

- d) Since it is able to adapt to a random job stream, interface with the crew is easier. If the crew schedules a program of high priority, they can be sure this program will not be spread out over small portions of many time slices but will be executed quickly.

- e) It has a greater flexibility for incorporating changes than the fixed sequence approach. A change in mission requirements is not a major programming change for existing programs.

#### 2.5.7 Disadvantages of Asynchronous Structure

a) The multiprograming environment resulting from this type of scheduling is more complex and difficult to test and verify. Programmers no longer know where their programs

will be interrupted. Thus, the executive must guarantee data integrity, handle sharing of data, and allow for reentrant coding. It can be made more predictable, however, particularly on the Shuttle where no external interrupts exist.

b) Since all tasks are run through the scheduler and dispatcher, there is an increased overhead for running these programs, queueing ready and waiting tasks, and handling the queues. However, this overhead can be minimized by combining the features of synchronous and as will be explained later.

#### 2.5.8 Need for Asynchronous Features

Since the nature of the Space Shuttle mission requires the computer to respond to unpredictable events, such as the crew altering the job stream, handling emergency situations, reconfiguring because of failed equipment, etc., a fully synchronous executive is insufficient. As mentioned above, both contractors see the need for scheduling tasks on an event basis. Since this fact is a step toward asynchronous structure, the question arises to what degree the executive organization should be asynchronous. Because of the simplicity of a synchronous structure, as many of its advantages as possible must be kept. It is the disadvantages that must be eliminated by allowing some asynchronous features.

The following structure obtains the best features Tasks will be organized into foreground and background categories. The foreground tasks are those tasks run at a fixed frequency by the scheduler in a synchronous manner, as described above. The time needed to execute each of these tasks must be small, i.e., less than a minor cycle. By definition all foreground tasks (synchronously) scheduled in a minor cycle must be totally executed in that The remainder of the time of the minor cycle can be devoted to executing background tasks. Background tasks have They can be operated on a priority basis; several features. they can be long (i.e., require more than one minor cycle to execute); and they can be scheduled on a time or event basis. The nature of background tasks makes a queue structure necessary. Hence, in a minor cycle there are now two types of scheduling: synchronous and asynchronous. By making as many tasks foreground as possible we eliminate much overhead in scheduling/ dispatching background tasks.

The advantages of this structure are:

a) it eases the incorporation of event and time dependent rescheduling of tasks;

Figure 2.7 System Flow of General Asynchronous Structured Executive

- asynchronous structure data integrity problem avoided, i.e., programmer control of where interrupts will be serviced;

- c) tasks for which precise timing analysis is unnecessary or impossible, or which require extreme timing safety factors can be executed on a priority basis rather than on a time slice basis.

Thus, in general, the proposed structure can handle the Shuttle software in a way advantageous to either completely synchronous or completely asynchronous structure.

## 2.6 Interrupt Handling and Task Dispatching

The interruption of a running program in response to an external signal was introduced into the computer technology to serve two purposes:

- a) provide rapid response-time to asynchronous events;

- b) eliminate the necessity of polling (and its overhead) to discover whether an awaited event has yet occurred.

In single-processor systems, particularly dedicated systems where most or all of the computation is devoted to a single application, the introduction of interrupt-mode computation raises the hazards associated with multiprocessing: at arbitrary times, an interruption can introduce what appears to be a parallel task which is at least conceivably capable of disrupting the progress of the interrupted task by altering its variables. Thus, methods for masking or inhibiting interruptions were added, and the nature of the functions allowed in interrupt-mode was restricted. Properly and thoroughly applied, these fixes allowed programs to perform properly, although no truly thorough method has been found of proving that the system was actually properly programmed.

There exist therefore, two relevant negative aspects of interruptions: timing response uncertainties, and potential data disruption and conflict. Both can be minimized by causing interrupts to schedule tasks whenever possible, as opposed to performing them. This provision reduces the multiplicity of possible timing situations, since job swapping occurs only at specified intervals.

Accordingly, it is considered desirable to utilize hardware interrupts such that tasks are scheduled and the interrupted task is rapidly resumed. The primary consideration becomes when to dispatch a higher priority task resulting from an interrupt, such that respond time requirements can be satisfied.

When an active task is dispatched into the wait state, another higher priority task is dispatched (made active) from the ready queue. When else does the executive dispatch? The following summarizes various approaches considered.

- a) If the executive dispatches at no other time, system response time to high priority tasks cannot be guaranteed since long duration tasks would execute to their end. This appears unacceptable in the Space Shuttle mission unless all lengthy tasks were broken down into separate, sufficiently short, independent tasks.

- b) The executive can dispatch whenever a task of higher priority than the active task is scheduled. In this case, interruption of the active task will occur at a random point in the coding and a higher priority task given the CPU. This uncertainty can lead to a program verification problem due to its random nature and non-repeatability.

- c) Alternatively, a programmer can inhibit dispatching at dangerous points in his program. Tasks of higher priority would be dispatched when permitted. However, this method does not completely solve the verification problem or prevent a higher priority task being delayed from execution for an unacceptable amount of time. By introducing an onboard "watchdog" timer, it is possible to guarantee a maximum time in which dispatching is inhibited. If a programmer exceeds this maximum time in inhibiting dispatching, the CPU is taken from his program. However, the dispatch will now occur at a random point.

- d) Another approach is to require the application task to be organized into short segments in which the dispatcher is requested at the end of each segment. If these segments were fixed at short intervals it would enable system response time to be maintained.

Furthermore, the segment organization of a lengthy program provides visible and controllable evidence to the programmer of the possible points that alternate control paths can occur. Conversely, he is assured that once the segment begins it is non-interruptable until it ends other than by the executive servicing of an interrupt or the task placing itself into a wait state. Similar arguments could be used for the previous approach.

The chosen method involves a modification to approach (d). First, high priority cyclic tasks, operating in a synchronous mode in the foreground, will always be dispatched at the occurrence of the clock interrupt. All other tasks will only be dispatched at the segment points. This will guarantee response time where it is needed and loosen the requirement for segment operating limits.

Secondly, the establishment of segments for lengthy programs can be aided by an assembler or compiler. Given that a procedure oriented higher order language is used for application programming, it can often suggest segment points and make them visible to the programmer. Tentative examples of compiler based segment points are:

- a) on all forward GO TO statements;

- b) entry or exit from a block;

- c) maximum time allowed in a segment exceeded.

The programmer must have a compiler override capability.

## 2.7 Resource Allocation

A resource may be defined as a facility of a computing system that can be temporarily assigned to tasks to enable them to perform their computations. Examples of resources pertinent to the Shuttle software are core storage, shared data, and data sets on mass memory units. Resource allocation is that function of a computer's operating system that assigns resources, when possible, to the tasks requesting them. In a multiprogrammed system, several tasks can request the exclusive use of a single resource. Since only one task at a given time can be granted its request, the others must wait until these resources are freed. Care must be exercised in resource allocation to minimize the number of transitions of a task from the active to the wait state and to avoid allocation conflicts.

To be specific, several conflicts can result from inefficient resource allocation. These are:

- a) deadlock,

- b) memory fragmentation,

- c) priority conflict...

We will define each of these conditions in the following paragraphs.

#### 2.7.1 Deadlock

Deadlock is a condition in which two (or more) tasks are each waiting for a resource held by the other before either can proceed. Neither task can release the resource it holds, so neither can be taken out of the wait state [16]. For example, suppose task A holds resource Rl and needs R2, but task B holds R2 and needs R1. Since neither task can release its resource, neither can proceed and deadlock results.

Deadlock detection algorithms can be included in an operating system to enable the task performing resource allocation to recognize potentially hazardous situations, and hence, to avoid them. This topic has been discussed extensively by several authors [9-10,13-16]. However, such an algorithm can cost a high overhead in execution time. The Space Shuttle executive should have an alternate way of avoiding deadlock.

Deadlock is the result of incremental resource allocation. That is, it is the result of tasks requesting resources sequentially during execution. By avoiding incremental allocation we can avoid deadlock without costly detection algorithms. More will be said about this topic later as it relates to the Space Shuttle computer.

## 2.7.2 Memory Fragmentation

Memory fragmentation is a condition in which a task cannot be granted its request for a large block of contiguous core because all available core for dynamic allocation is in small noncontiguous blocks.

When this situation arises in a large ground based computing system having a large secondary memory, part of the contents of core are rolled out temporarily to create a large enough

contiguous area of main memory to satisfy dynamic allocation requests. However, on the Space Shuttle computer we seek to minimize the use of any MMU because of its inherent complexity. Thus, most data will be maintained in main memory so that programs can operate at maximum speed. Programs and data are only reloaded into the operating memory at low frequency during the mission, such as at the start of a new mission phase.

## 2.7.3 Priority Conflict

Finally, an allocation conflict can arise when a low priority task holds a resource that a high priority task requests. Often the resource cannot be released by the former task as in the case of temporary work areas of core storage. Unfortunately, the high priority task must now be placed in the wait state until the low priority task can safely release the resource. The result of this situation is a degradation in the system's response time for high priority computations. For a sufficiently large degradation the effects upon the overall mission can be very serious.

Each of these hazardous situations must be avoided in designing a resource allocation algorithm for the Space Shuttle computer. The following section will present methods of avoiding these problems.

## 2.8 Allocation of Specific Resources

In the Space Shuttle computer there will be three categories of resource allocation for which provisions must be made. These are:

- a) dynamic memory allocation,

- b) common data sharing,

- c) data set management.

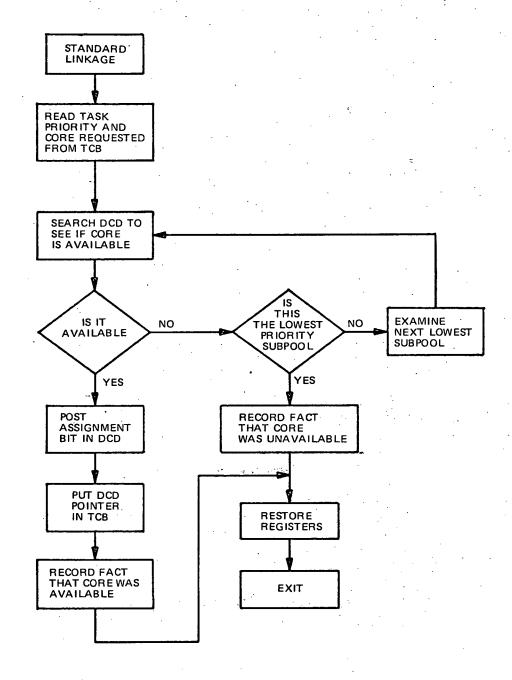

#### 2.8.1 Dynamic Memory Allocation

Dynamic memory allocation occurs when the executive temporarily assigns blocks of core storage to a task requesting this resource. This core is returned to the dynamic core pool either by the task during its execution or by the executive at the end of the task. To avoid deadlock we require that all core requests of a task be satisfied when the task is placed in the ready state. That is, to avoid incremental allocation a task makes all core requests known to the

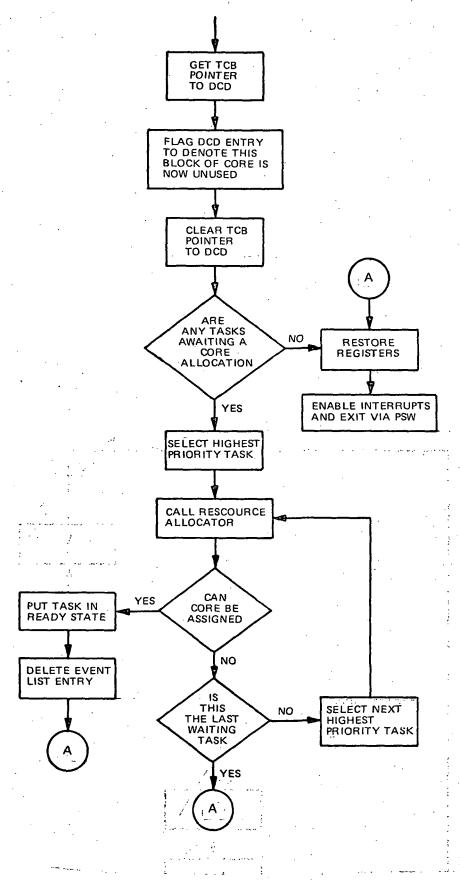

executive via its TCB at schedule time. If the request can be satisfied, the task can be placed in the ready state provided it is not awaiting the allocation of any other resource. If not, the task is placed in the wait state, awaiting the release of a sufficient amount of dynamic core to satisfy its needs. When this core becomes available, the task can be placed in the ready state. Eventually when the task becomes active, it has all the core it will ever need and will not have to be placed back in the wait state during execution for lack of this resource. Hence, deadlock cannot occur because of a conflict in dynamic core allocation.

Although we have avoided deadlock fairly easily, the problem of memory fragmentation is not as readily solved. The reason for this increased difficulty is that several alternative methods of avoiding this problem are available to us, and the specific method chosen depends upon the computational requirements of the mission application programs. So far these requirements are not known in any detail. Hence, we will examine four methods of memory allocation and determine which is optimal with respect to our present knowledge of the program requirements.

2.8.1.1 Fully Static. This method would avoid dynamic storage allocation by permanently assigning to each task all the core storage it needs for the duration of the mission. Memory conflicts are obviously avoided.

If the total amount of core so assigned is small, e.g., lK bytes, then avoiding the problems of dynamic storage allocation is advantageous since the executive design will be simpler. However, the amount of core needed is likely to be higher than our lK example above, so the extra cost in the amount of memory needed for static allocation becomes uneconomical.

This is not to say that no task should have its work areas permanently assigned. For example, a computation executed every minor cycle will utilizes its work area for a large percentage of every major cycle. In this case it could be economical to statically assign this task's work area to it. However, for the large amount of tasks run on a less frequent basis the percentage of a major cycle that they utilize their work areas is small. Hence, static storage allocation cannot be the only method of storage allocation in the Space Shuttle computer.

Note that any task having a static work area allocation is by its very nature non-reentrant.

2.8.1.2 Fully Dynamic. A frequently used method of dynamic storage allocation in large scale computing systems is to allow all tasks to compete with each other for all available core. A task can request a block of any size provided it does not exceed the amount of core available. If this block is available, it will be allocated to the task [4].

The disadvantage of fully dynamic allocation is that it does not solve the problem of memory fragmentation.

2.8.1.3 <u>Semi-dynamic</u>. Let dynamic core be divided into blocks of several specific sizes, e.g., 50 bytes, 100 bytes, .5K bytes and lK bytes. Tasks which request core must be structured so that their request conforms to one of these sizes. Although this method imposes a restriction upon the tasks, the problem of memory fragmentation is now solved.

There still remains the problem of low priority tasks holding core and preventing high priority tasks from executing. The problem can be partially solved by allowing several blocks of each size in dynamic core. This will reduce the probability of all blocks of a given size being simultaneously allocated. However, the number of blocks of each size cannot be too large since this would be as uneconomical as static memory allocation. Program requirements will of course determine how many blocks and what sizes to allow.

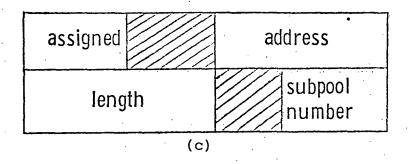

2.8.1.4 Priority Subpool Allocation. Dynamic core will be divided into sections called subpools, one corresponding to each possible task priority level. A task requesting core will then receive its allocation only from the subpool corresponding to its priority level. Within a subpool core can be allocated on a fully dynamic or semi-dynamic basis.

If the fully dynamic method were used, fragmentation would occur within each subpool. To avoid this problem we will use semi-dynamic memory allocation (as explained above) within subpools. Each subpool will have several blocks of core of several different sizes. A task is then allocated a block of its requested size when it is placed on the ready queue.

Should a task request a block of core that is unavailable within its subpool because of existing allocations, a block from a lower priority level can be used for allocation. This will prevent a high priority task from having to wait

for the release of core while low priority tasks can be scheduled. In addition, tasks of the highest priority will not have to share their subpool with any other tasks. These tasks will have the least interference from other tasks in competing for core.

The sizes of the blocks and the number of each size are determined by the number of tasks and their requirements at the given priority level. Once this algorithm has been implemented size and quantity parameters can be varied for optimization. This is the method selected in the design structure.

## 2.8.2 Common Data Sharing

In any multiprogramming system a resource allocation problem arises when data in core memory can be simultaneously used by two (or more) tasks. If two tasks only want to read the data, no conflict exists. However, if one of the tasks wants to update before the other has finished reading, a conflict arises.

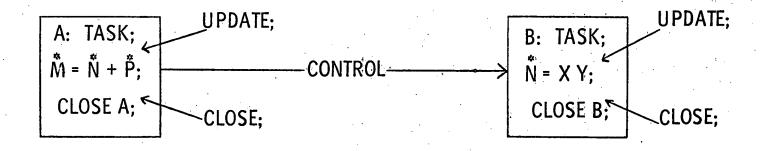

To illustrate this, consider the examples shown in Figure 2.8. In both examples TASK B interrupts TASK A during the execution of a statement. In Example 1, presume that the interruption occurred while the matrix N was being read. When TASK A resumes, the computation of M will continue using some "old" N data and the "new" N data assigned in TASK B. In order to prevent this conflict, initiation of TASK B would have to be stalled until the reading of N in TASK A is completed.

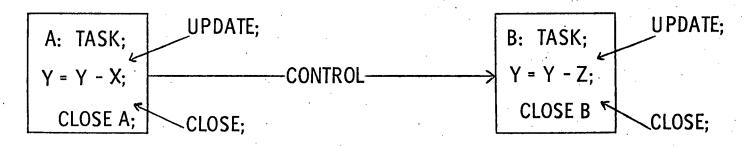

In Example 2, presume that the interruption occurs just after the current value of Y is loaded into the accumulator. When TASK A resumes, the "old" value of Y (i.e., not reflecting the update of Y in TASK B) is restored into the accumulator, X is subtracted and the result assigned to Y. In order to prevent this conflict, the initiation of TASK B would have to be stalled until the value of Y is updated in TASK A.

These examples illustrate the fact that accesses to shared data must be controlled to prevent conflicts. One possible way of doing this is by preventing task dispatching at critical times. This method is too restrictive however, especially for high priority tasks needing fast system response. We will investigate alternative approaches to this problem.

- a) OS/360 uses the ENQ and DEQ macros to grant tasks access rights to shared data. ENQ will grant a task access rights as long as no other task is using the data. In the latter case, the task requesting access rights is put in the wait state, awaiting the release of this data (DEQ). Upon this release, the next task enqueued for access rights is taken out of the wait state and allowed to proceed. For two tasks that only want to read shared data, this method imposes a needless wait for one while the other has the data enqueued.

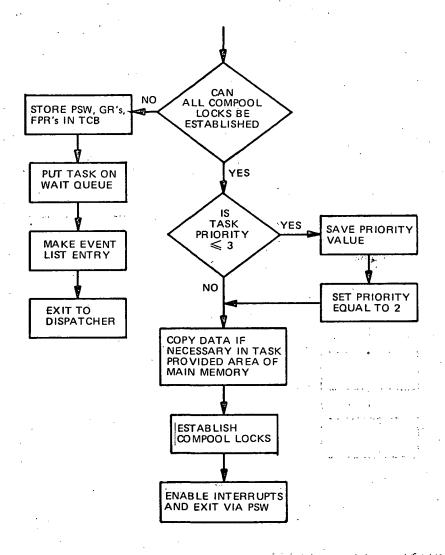

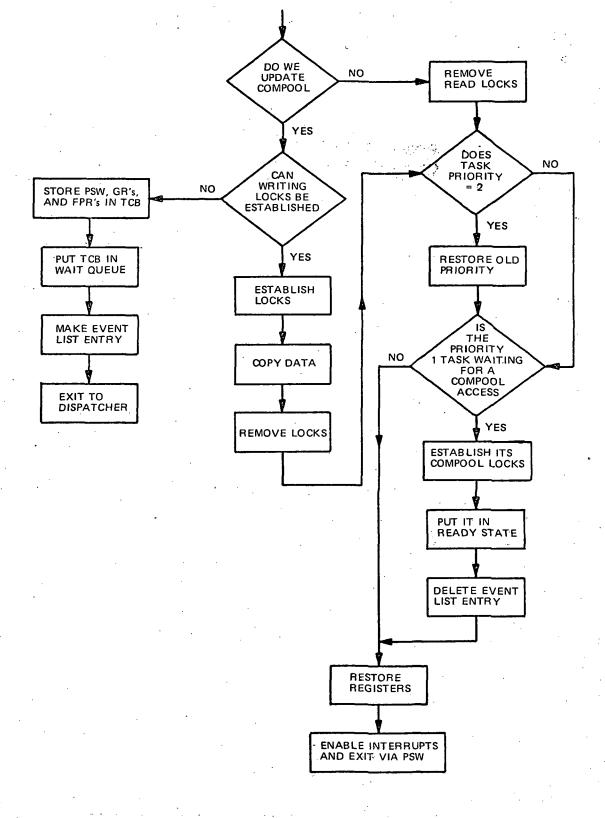

- b) A second approach to avoid common data sharing conflicts is to use UPDATE blocks as is done in the HAL compiler [6,7]. An UPDATE block is a group of statements within a program providing a controlled environment for the reading and writing of shared data variables. Upon entry into the UPDATE block, read or write locks are established around parts of the compool containing the variables to be referenced. There need not be an individual lock for each variable nor should there be only one lock around the the entire compool. How the compool is organized can be decided at a later time depending upon the programs to be executed and their requirements.

Should a part of the compool needed by a task be unavailable for locking, the task is placed in the wait state. Any other parts of the compool it has locked are now unlocked so that they can be used by nonwaiting tasks. The requesting task can be placed in the ready state when the scheduler determines that all parts of the compool requested now can be allocated to this task. At this time read or write locks are established around these parts of the compool.

Three types of locks can be established: read, write, and writing. We say that unlocked data is in state 0 and locked data can be in states 1-3 corresponding to the three types of locks respectively.

A read lock will enable another task that also wishes to read lock this data to do so. If a write lock is established around a piece of data, a copy of the data is made for the updating task. Upon closing the UPDATE block, the compool is updated as long as no other locks exist around the data to be undated. No writing locks can be put on a given part of the compool, until any read locks already there are removed by all tasks reading this data. If the locks exist, the updating task must wait until the locks are removed.

Consider the first example above and suppose that the statements in question (in TASKS A and B) were enclosed within UPDATE blocks. In TASK A a read-lock is established for N, because it will be read only. After the interruption, a write-lock is established for N and TASK B proceeds toward completion using copy-data for N rather than active data. At the end of the update block in TASK B, the process stalls because of the read-lock imposed in TASK A. As a result, TASK A is allowed to continue with consistent "old" N data. After completion of TASK A, a copy-cycle is effected in TASK B and N is updated. All conflicts are eliminated. A table of compool state transitions follows.

| Present<br>State<br>Desired<br>State | Free                   | Read<br>Locked | Write<br>Locked        | Writing<br>Locked      |

|--------------------------------------|------------------------|----------------|------------------------|------------------------|

| Free                                 | O.K.                   | О.К.           | not<br>appli-<br>cable | O.K.                   |

| Read Locked                          | о.к.                   | О.К.           | O.K.                   | Wait                   |

| Write Locked                         | о.к.                   | о.к.           | Wait                   | Wait                   |

| Writing Locked                       | not<br>appli-<br>cable | Wait           | O.K.                   | not<br>appli-<br>cable |

To prevent any task from locking a part of the composed any longer than necessary, no I/O statements and no programmed WAIT statements will be allowed in an UPDATE block. This requirement will prevent a high priority task from having to wait for long time intervals while a lower priority task has data locked.

To economize on the amount of core needed for the compool, part of the compool can be overlaid on transitions to different mission phases. If two tasks that are only executed during a particular mission phase use part of the compool, it is needless to keep this part of the compool in core as long as no other task in another phase will ever again use the data. In this case as new program modules are read into core during a mission phase transition, this part of the compool can be overlaid.

## **EXAMPLE 2: UPDATE CONFLICTS**

NOTES: 1. B "INTERRUPTS" A IN BOTH CASES

- 2. #1 TASK A RESUMES USING OLD AND NEW VALUES FOR N

- 3. #2 TASK RESUMES "CLOBBERING" THE VALUE FOR Y SET BY TASK B

40

#### 2.8.3 Data Set Management

Data set management is heavily dependent upon the type of mass storage unit used on the Space Shuttle. If a tape drive is used, as in the MDC/TRW study, very little data management capability will be necessary. However, if a random access unit is used, as in the NR/IBM study, more extensive data management facilities will be necessary.

In this report we will assume a random access unit, especially since the ASIL configuration includes an IBM 2311 disk drive. However, the data management system we will present is not as general purpose as in the System/360, for example. It is designed to meet the needs of the Space Shuttle mission. One of the criteria used in designing this part of the executive is the desirability of minimizing use of the random access unit during the Space Shuttle mission. The major anticipated uses of the storage unit are to record flight data, to update the programs in core memory on a per mission phase basis, and to retrieve display skeletons for the visual display application programs. More frequent use of the mass storage unit is unnecessary, based upon the two Phase B study reports [1,2].

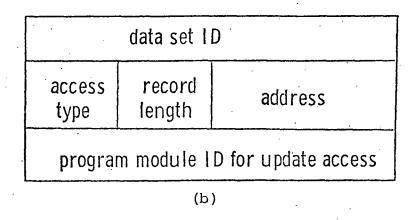

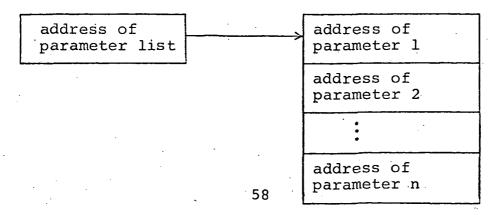

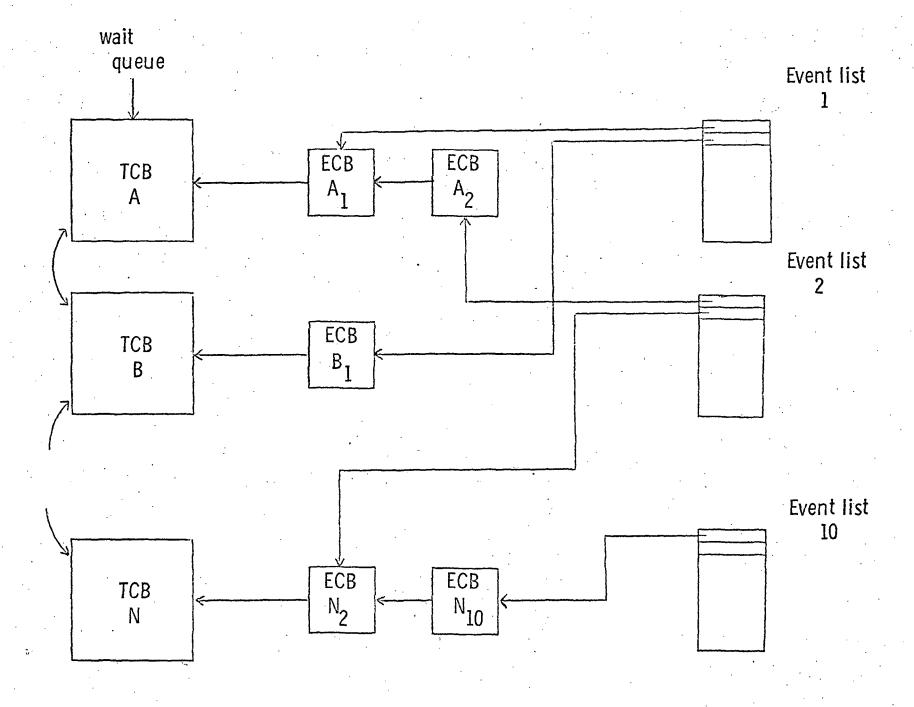

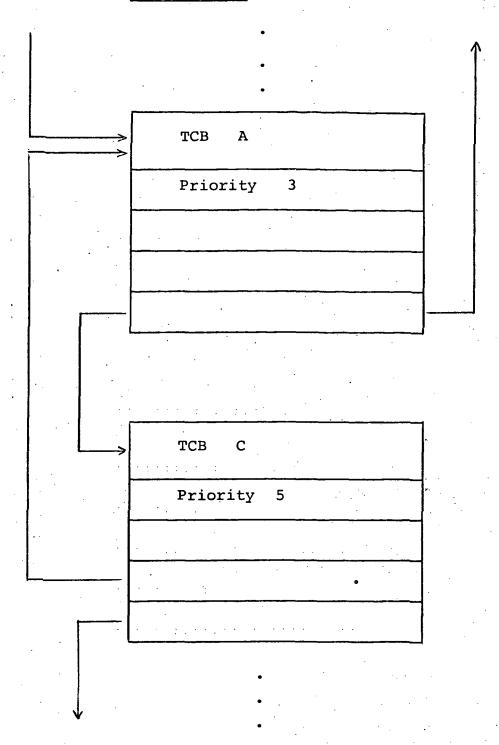

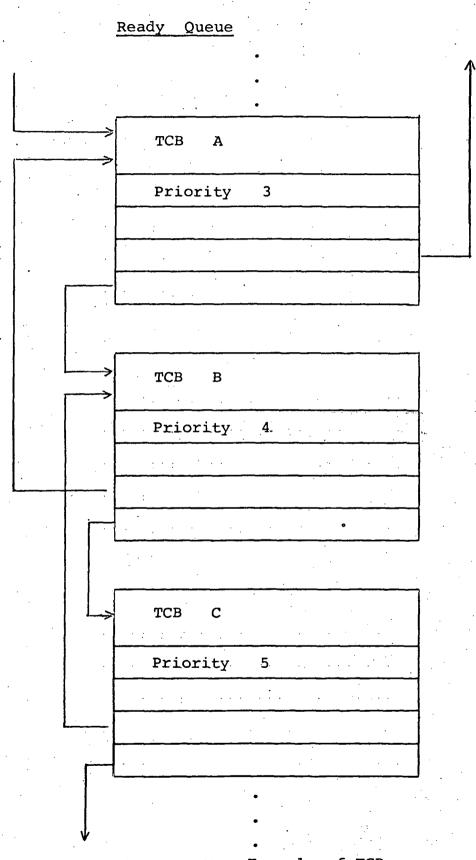

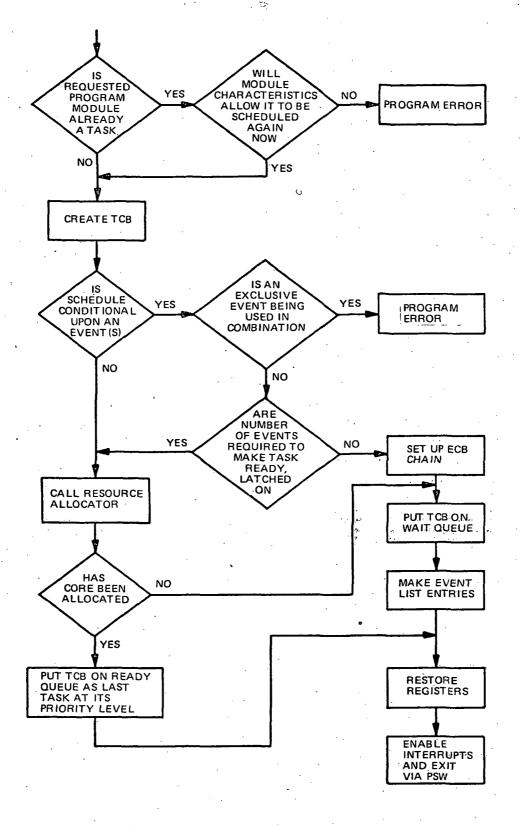

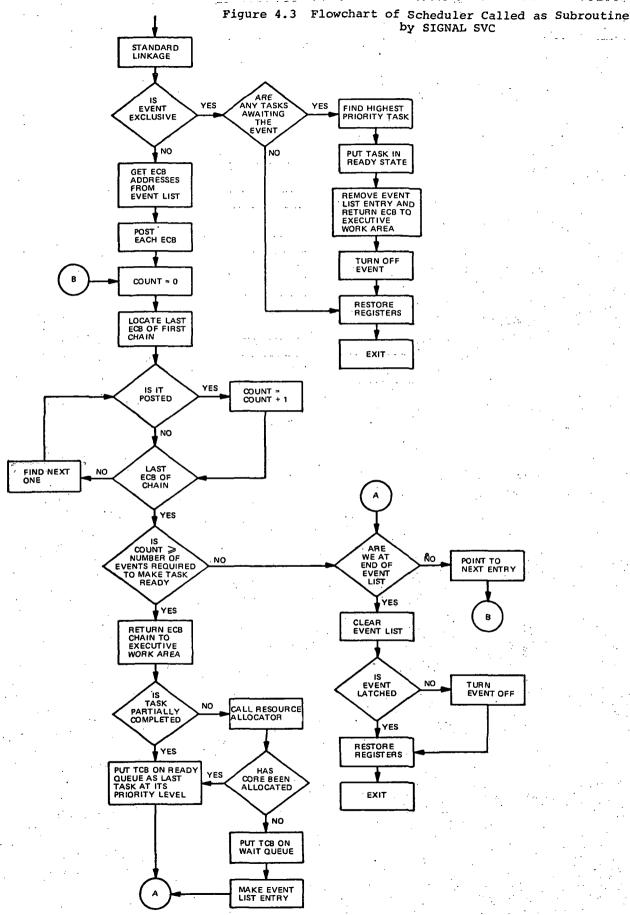

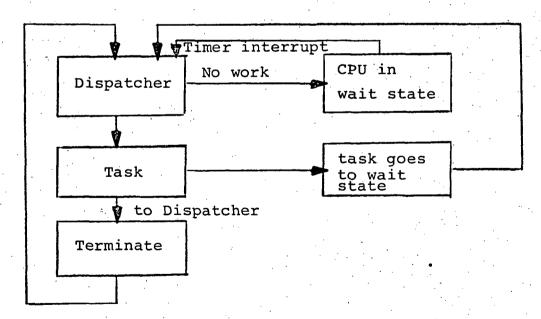

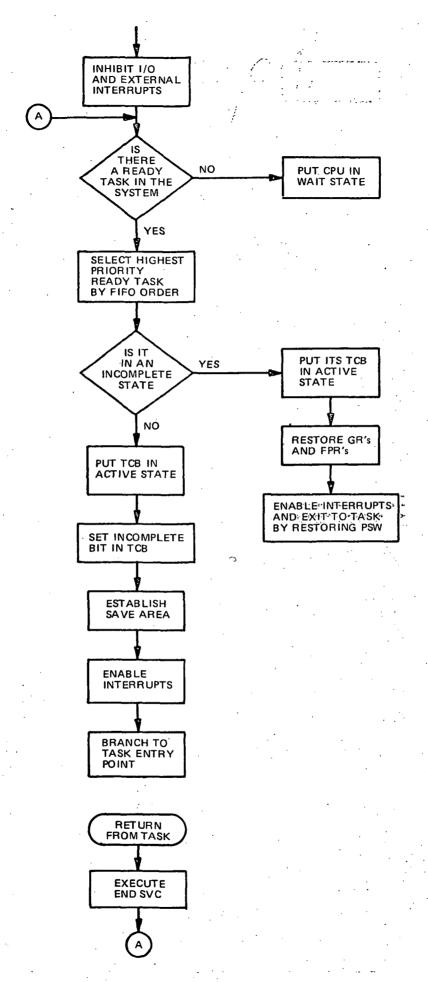

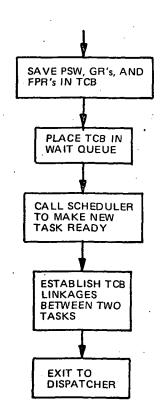

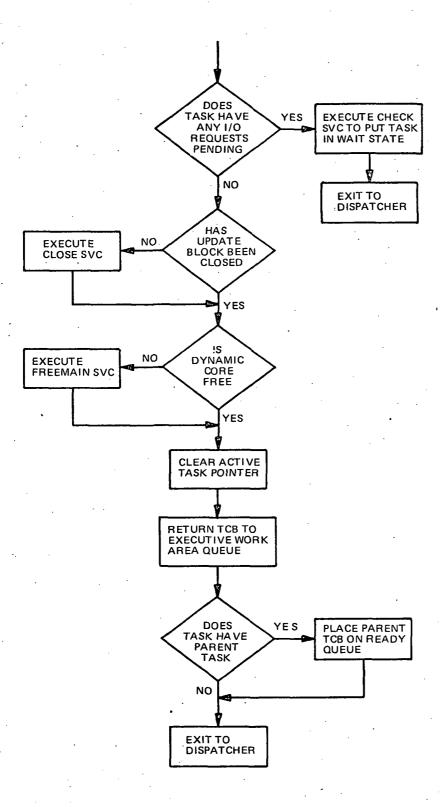

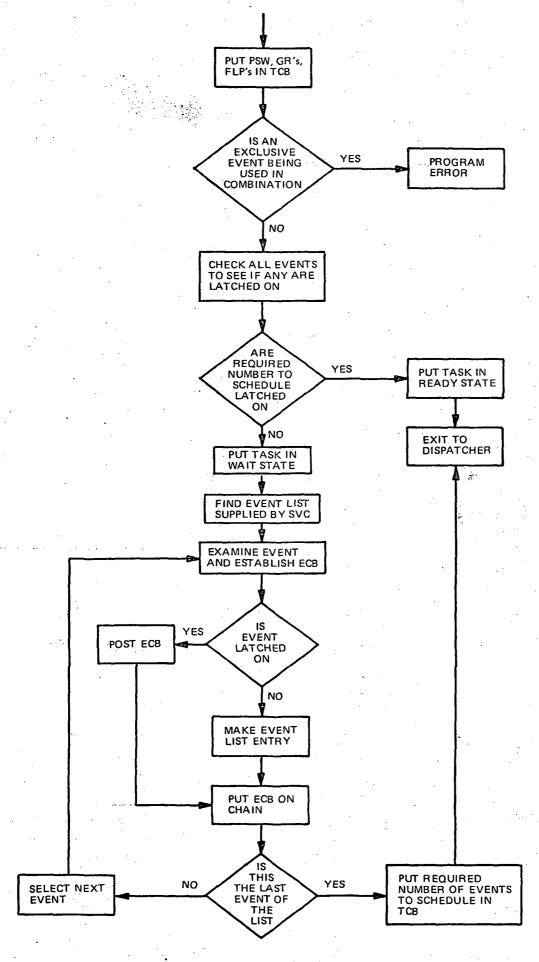

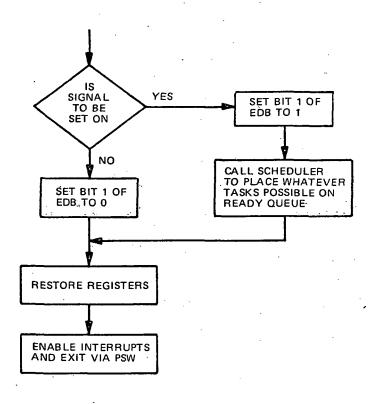

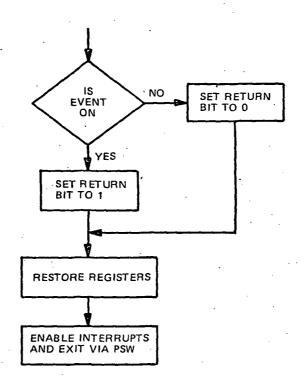

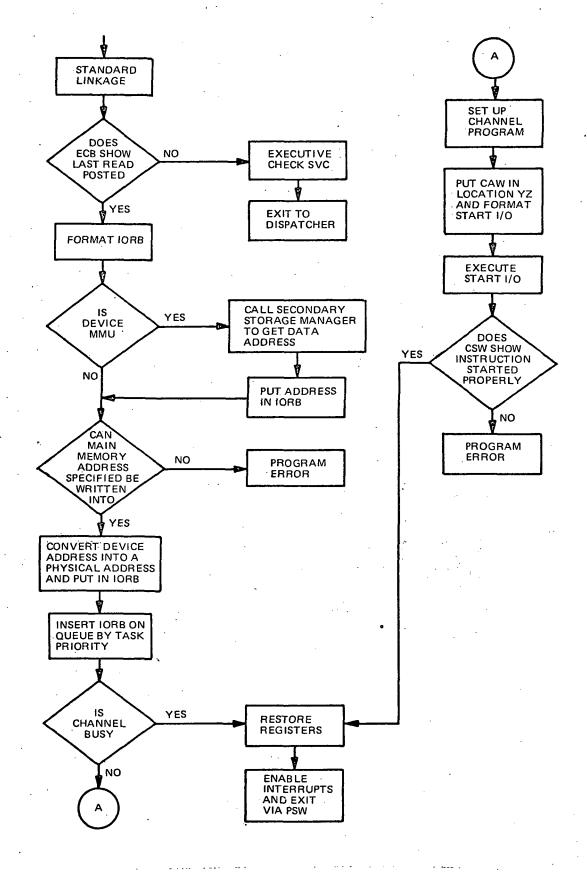

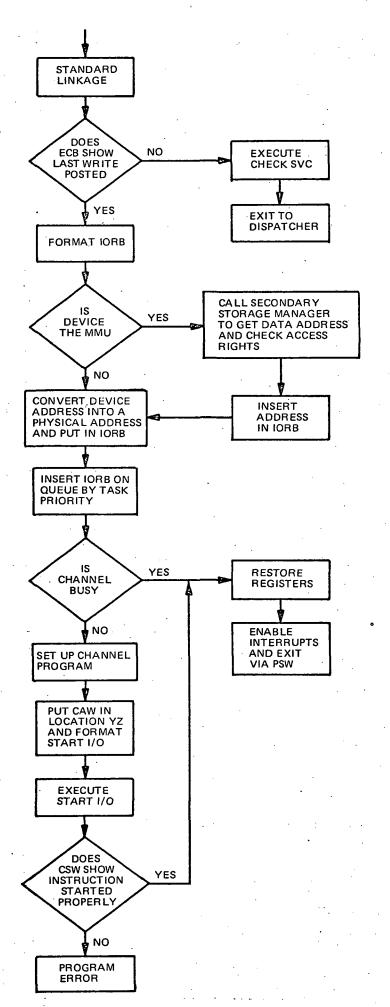

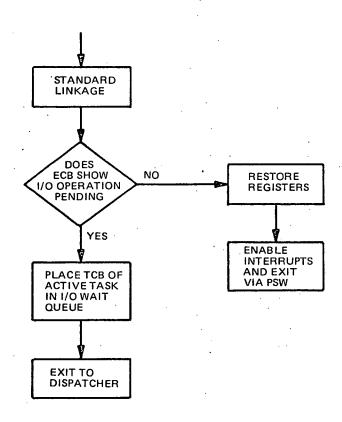

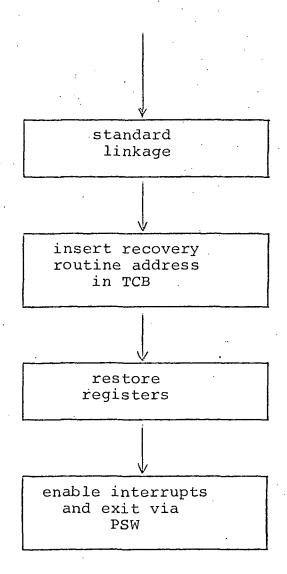

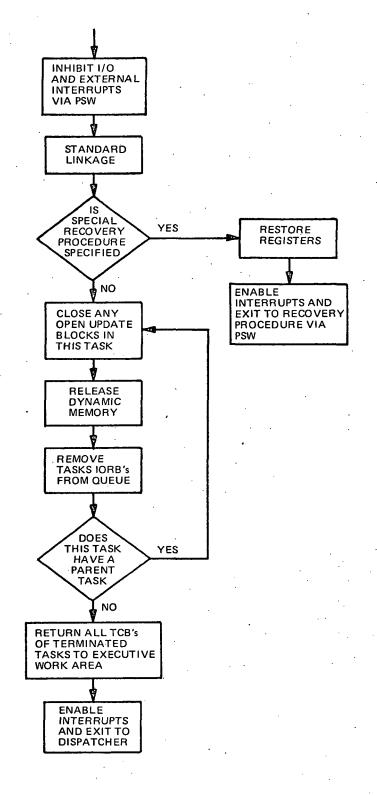

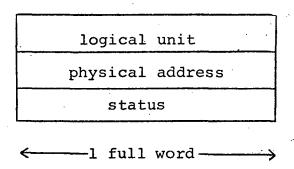

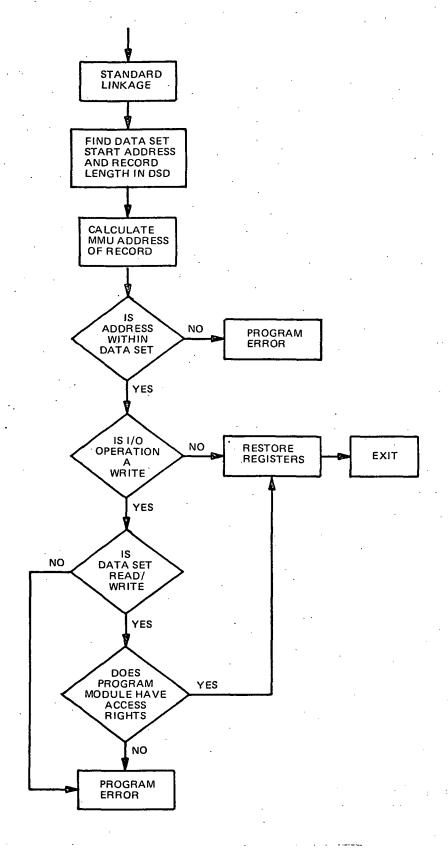

There will be two classes of data sets on the random access storage unit, read only and read/write. The former category may be read at any time by any number of tasks without conflict. The latter category, however, can cause access conflicts, and hence, some protection mechanism is necessary.