Section 1

### INTRODUCTION

### AP-101S WITH SHUTTLE INSTRUCTION SET

The AP-101S is a high-speed general-purpose computer intended primarily for real-time applications such as guidance, navigation, control, and data processing. The AP-101S is a member of the advanced System/4 Pi family of digital computers, and is software compatible with AP-101C/M, described in IBM No. 6246156B, 30 Jan. 1979. This family shares and is unified by extensive design experience, proven technology base, and common manufacturing processes.

This Principles of Operation manual provides a direct comprehensive description of the system structure; the arithmetic, logical, branching, and status switching; and the interruption system. This publication defines and describes features common to all AP-101 computers. These features are the basis for IBM-developed support software and are compatible with compiler development efforts now in process.

Execution times and nonstandard features and functions are described in separate documents. This is because aerospace computers characteristically include user defined features such as unique input/output channels, and special discretes. These will be incorporated into the AP-101S as pluggable options. Furthermore, the AP-101S is microprogrammed and is designed to permit incorporation of additional instructions and operations without redesign and requalification. Such extensions are also described separately.

Note: This document is also applicable to the APIOIS/G, the ground version of the APIOIS computer.

Section 2

**AP-101S STRUCTURE**

correction bits and three voted

### SHUTTLE INSTRUCTION SET

The AP-101S system structure encompasses the functional operation of main storage, the central processing unit (CPU), and program-controlled I/O facilities. The overall definition is open ended and includes all the basic facilities necessary to accommodate additional specialized and/or application-dependent I/O channels and features.

The modular AP-101S system structure can support configuration alternatives ranging from a self-contained single processor to a full symmetrical shared-storage multiprocessing system.

### MAIN STORAGE

The functional operation of main storage is unrelated to the physical width of the information paths or cycle time.

Six

INFORMATION FORMATS

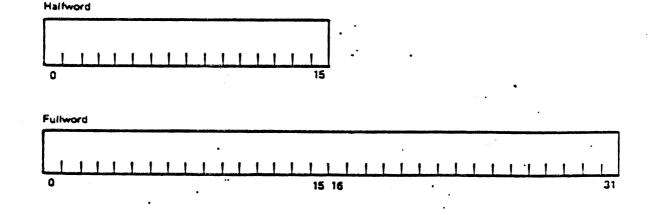

The system transmits information between main storage and the CPU in units of 16 bits, or in integer multiple of 16 bits. Each 16-bit unit of information is called a halfword. A parity bit and a storage protection bits are also associated with each halfword, but later references in this manual to the size of data fields exclude these bits.

Halfwords may be handled separately or in pairs. A fullword is a group of two consecutive halfwords. Both halfword and fullword instructions and operands are used. Their location is always specified by the address of the leftmost halfword. The instruction length is designated implicitly in every instruction; the operand length is also implicit.

Within any instruction and operand format, the bits making up the format are consecutively numbered from left to right, starting with the number 0, as shown in Figure 2-1.

#### ADDRESSING

Halfword locations in storage are consecutively numbered starting with 0. Each number is considered the address of the corresponding halfword. The addressing technique uses a 19-bit binary address to accommodate a maximum of 2<sup>19</sup> halfword addresses. This set of main storage addresses includes some locations reserved for special purposes, such as program status words; consequently, these special locations should not be used for any purpose not implicitly defined.

Fullword

0 15 16 31

Figure 2-1. Instruction and Operand Bit Numbering

### INFORMATION POSITIONING

Fullword operands must be located in main storage on even halfword boundaries. That is, the least significant bit of the operand address, when expressed in binary, must always be zero. Fullword instructions may begin at any address.

### CENTRAL PROCESSING UNIT

The central processing unit (CPU) contains facilities for addressing main storage, for fetching or storing information, for arithmetic and logical processing of data, for sequencing instructions in the desired order, and for initiating the communication between storage and external devices.

The control section guides the CPU through the functions necessary to execute the program.

### PROGRAM ADDRESSABLE REGISTERS

Two sets of eight fixed-point general registers and one set of eight floating-point registers are under explicit program control. The contents of one or more of these registers (32 bits) participate in most CPU operations.

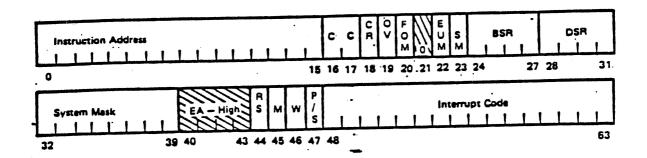

Conceptually, an additional doubleword status register, called the program status word (PSW), is the focal point for machine status. The contents of the PSW are updated during each instruction. Consequently, the PSW reflects current machine status following every instruction. The PSW participates implicitly in status switching, branching operations, and address calculations.

審

In addition to the PSW and the general and floating-point registers, the CPU also contains working registers used for storage addressing, storage buffering, shift and iteration counting, and operand storage. These registers are of no direct concern to the programmer and are not described herein.

The contents of the PSW specify which of the two sets of general registers is in current use. Only the contents of the selected general register set can participate in arithmetic operations and the contents of unselected sets of general registers can not be altered by a program. An alternate set of general registers can be selected by changing the PSW. Only one set of the fixed-point, general-purpose registers and the floating-point registers are available to the program at any one time.

General register contents can be used interchangeably as operands for arithmetic, logical, and shifting operations, or as base and index registers for relative addressing. Each set of general registers is numbered from 0 through 7 and is addressed as shown in Figure 2-2.

| General            | Register Function |            |       |  |

|--------------------|-------------------|------------|-------|--|

| Register<br>Number | Operand Base      |            | Index |  |

| 0                  | 000               | 00         | None  |  |

| 1                  | 001               | 01         | 001   |  |

| 2                  | 010               | 10         | 010   |  |

| 3                  | 011               | 11 or None | 011   |  |

| 4                  | 100               |            | 100   |  |

| 5                  | 101               |            | 101   |  |

| 6                  | 110               |            | 110   |  |

| 7                  | 111               |            | 111   |  |

Figure 2-2. General Register Addresses

Note that general registers 4 through 7 cannot contain base addresses and that general register 0 cannot contain an index.

For some operations, an even/odd pair of general registers are linked to form a 64-bit doubleword register. The most significant half of a doubleword operand is contained in the even-numbered register; the least significant half of the doubleword in the next higher odd-numbered register. Doubleword operands are addressed by specifying the even numbered address of the register containing the most significant portion of the operand.

For addressing data, general registers 0-3 can be augmented by 4 bit Data Sector Extension (DSE) registers or by the DSR in the PSW to address beyond 16 bit capabilities. There are 16 DSE's, one for each of the 8 general purpose registers in each of the two sets of general registers. This feature shall not be used by program<sup>of</sup>less. than 128K full words.

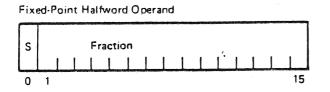

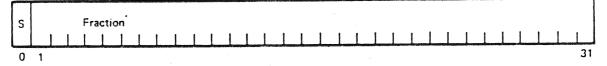

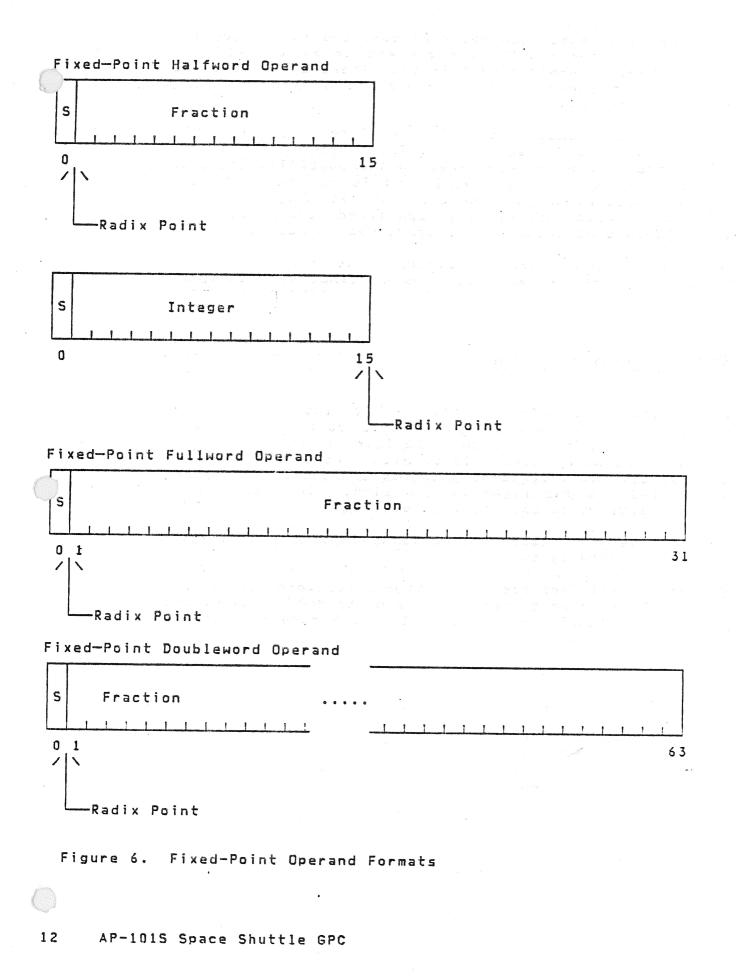

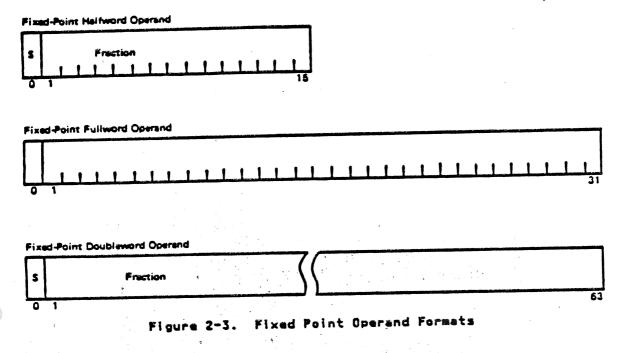

### FIXED POINT DATA REPRESENTATION

Data representation is fractional, with negative numbers represented in two's complement form. A halfword operand is 15 bits plus sign; a fullword operand is 31 bits plus sign, as shown in Figure 2-3.

In fractional data representation, the binary point is immediately to the right of the sign.

Fixed-Point Fullword Operand

### Figure 2-3. Fixed-Point Operand Formats

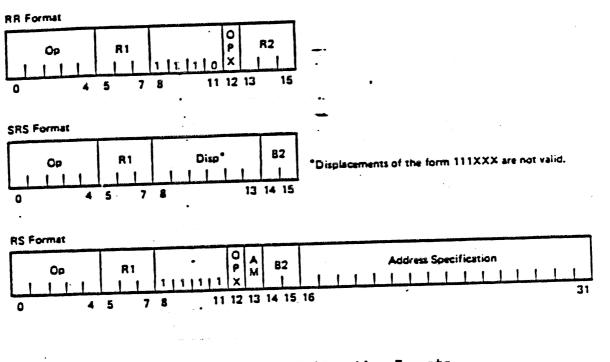

### INSTRUCTION FORMATS

The length of an instruction format can be either one or two halfwords. Long format instructions provide maximum range and extended flexibility for addressing storage operands. Short instructions are used to (1) specify register-to-register operations, and (2) specify storage operands in cases where a small displacement is sufficient and complete address modification capability is not required.

Instruction formats overlap. Programs are written so that in many instances any given operation can be coded using either a halfword or a fullword instruction. In such cases, maximum use of halfword instructions results in increased storage efficiency and performance.

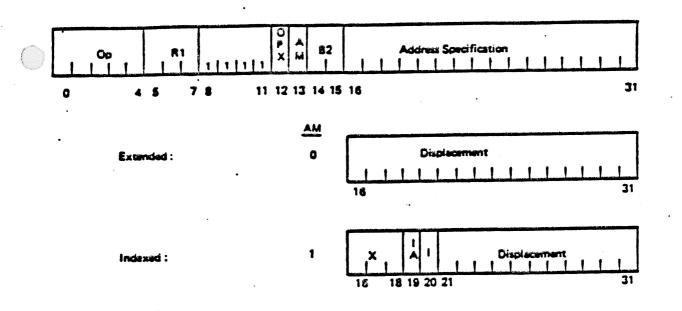

The three basic instruction formats are as shown in Figure 2-4. Halfword instructions are automatically selected by the assembler unless otherwise specified by the programmer.

2-4

### 4.0 HI3H LEVEL FUNCTIONAL DESCRIPTION

### 4.1 GENERAL SYSTEM OPERATION

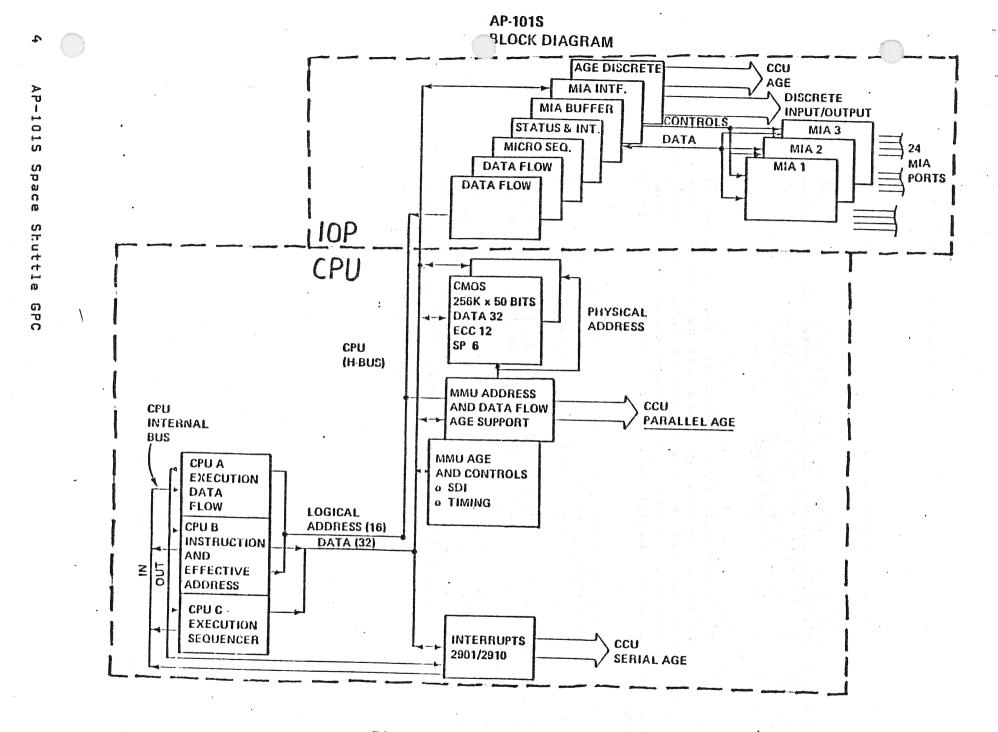

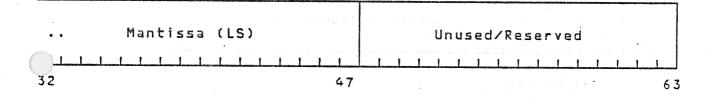

The AP-101S was formed by the integration of a redesigned B1-B AP-101F processor and a repackaged Input/Output Processor (IOP) from the existing Shuttle computer. Redesign and repackaging permits both of these elements to be housed in a single structure. Figure 2 on page 4 shows the AP-101S Block Diagram.

The elements utilized from the AP-101F are the CPU, MMU (Memory Management Unit), and Interrupt sections. The microcode has been modified so existing shuttle software can be used on the AP-101S. The Timing page, SDI (Software Development Interface) page and the SIB bus have been eliminated. The unused circuitry in the MMU has been removed to permit integration of the timing and SDI functions into the MMU.

The IOP has been repackaged using medium scale integration to reduce the number of pages from fourteen to seven. The IOP has maintained the same timing as the original processor.

All of the pages use Modular Computer System (MCS) page technology. The repackaging allows the AP-101S to be housed in a single box.

The CPU performs the functions of computation, storage and communication of data for the Shuttle Orbiter. The CPU executes instructions from main store. Main store is controlled by the MMU, which handles all memory access requests from the CPU and IOP.

Figure 2. AP-101S Block Diagram

The IOP functions as a programmable, time-shared processor that transmits and receives Shuttle Orbiter subsystems data under control of the CPU.

The CPU communicates with the IOP by means of Program Controlled Input/Output (PCIO) instructions. PCIO transmissions involve a command word and data from either the CPU or IOP.

The Shuttle Orbiter subsystems are connected to the IOP by 24 serial, 1-MHz data buses. Data bus-to-IOP interface is accomplished by 24 Multiplexer Interface Adapters (MIAs) located in the IOP. The MIAs perform such functions as parallel/serial conversion, Manchester encode and decode, parity generation and detection, and bit count detection. The IOP handles the processing required to service the 24 data buses.

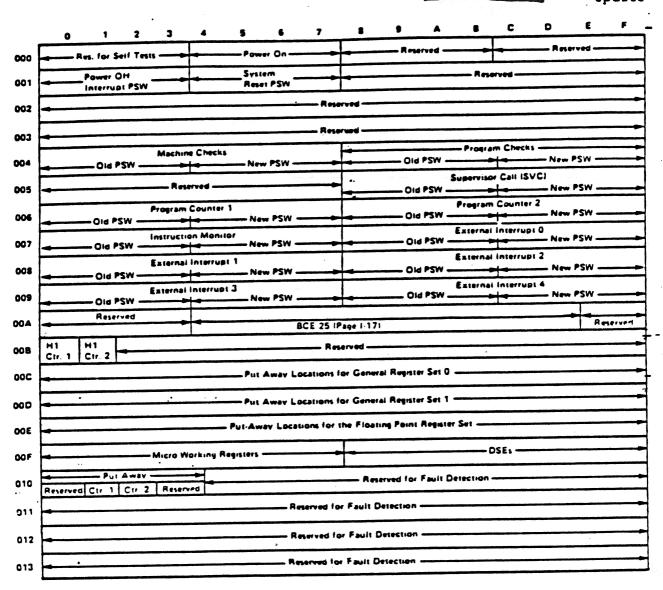

The 24 data buses each have a Bus Control Element (BCE). The BCEs are given instructions by the Master Sequence Controller (MSC) on how to handle data. The MSC executes instructions from main store as directed by PCIO instructions from the CPU. The MSC/BCE instructions and data are fetched from main store through Direct Memory Access requests. The MSC has a set of programmable registers in Local Store. These registers include a PCIO register, index register and program counter.

The BCEs execute programs from main store specified by MSC instructions. Each BCE also has a set of programmable registers in Local Store and can read or write I/O data into main memory via Direct Memory Access (DMA). Included in the registers is an indicator register which contains one bit for each BCE. This bit is set and reset by a BCE to communicate with the MSC.

Each BCE is sequenced by a timing 'wheel' which allows one microinstruction from each BCE to be executed at a time. The MSC is also in this timing sequence, but it gets eight slots in a complete turn of the 'wheel' while each BCE gets only one. One MSC microinstruction is executed after three BCE microinstructions. Some MSC and BCE instructions may take more than one rotation of the 'wheel' to be executed.

The Interrupt page contains a processor to handle interrupts. The interrupt processor prioritizes, masks, categorizes and performs any other processing that is necessary before giving informaticn to the CPU. A one byte word is generated to inform the CPU into which category the interrupt falls. Additional information allows the CPU to formulate a six bit address for a PSW swap and begin processing the interrupt.

Each of the three major components of a GPC (CPU, IOP, and Interrupt Page) is controlled by independent microcode. The CPU microarchitecture is described in detail in "Microcontrol Implementation For CPU" on page 113, the Interrupt microarchitecture is described in "Microcontrol Implementation For INT" on page 191, and the IOP microarchitecture is described in "Microcontrol Implementation For IOP" on page 211.

### 4.2 AP-101S CENTRAL PROCESSING UNIT

The AP-101S central processor unit is optimized for both MMP and MIL-STD-1750A Notice 2 architectures and is comprised of these functional units:

- Instruction Unit (I-unit).

- Effective Address Unit (EA-unit)

- Execution Unit (EX-unit)

- Fractional Data Flow

- Exponential Data Flow

- Sequencer

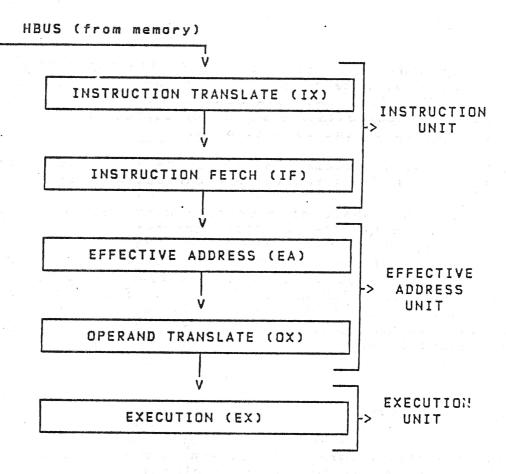

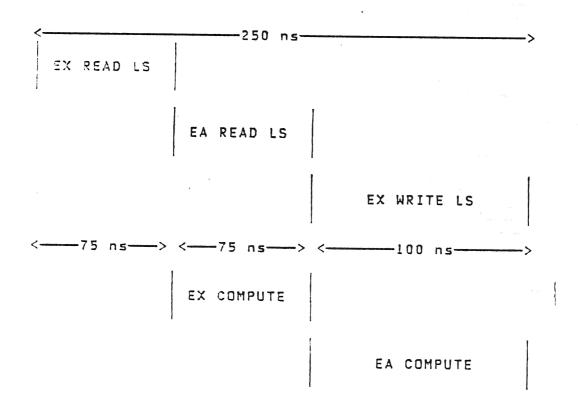

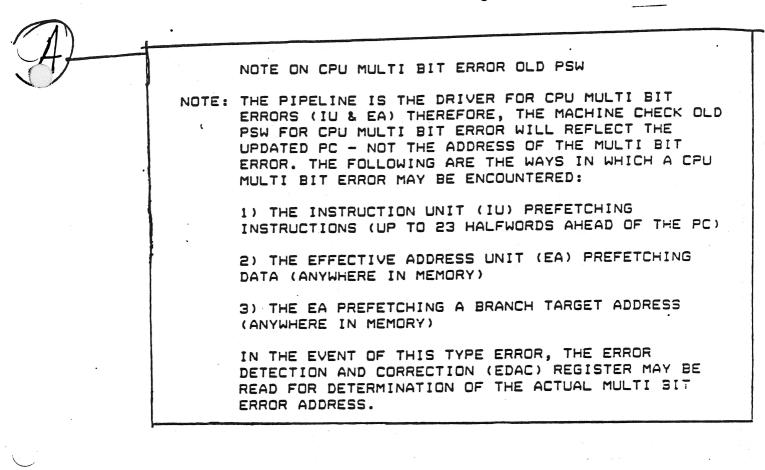

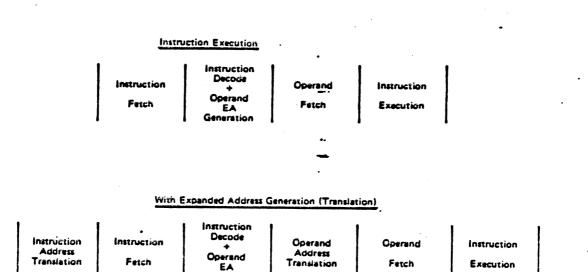

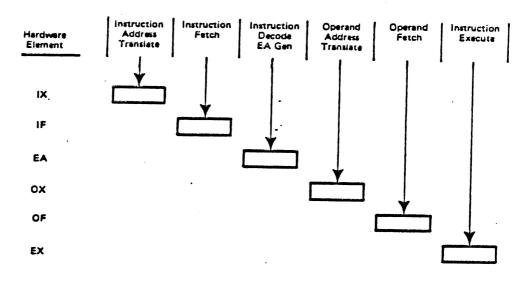

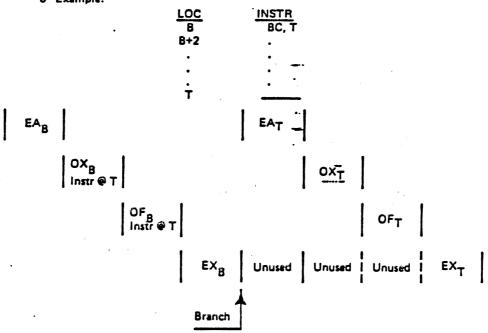

These units are organized to execute instructions in a pipeline fashion designed to provide results at a rate of one per machine cycle (250 ns) when operating on simple instructions (with the pipe full). The pipeline is shown in Figure 3 on page 7.

The Instruction unit is responsible for prefetching instructions. It provides a logical instruction address to the Memory Management Unit, which then translates this to a physical address before fetching the instruction. The EA-unit decodes the instruction to determine what type of addressing the instruction specifies, and uses its data flow to calculate (if necessary) the effective (logical) address of the operand. This logical address is translated to a physical address in the MMU, and the operand is fetched. The EA-unit provides the operand and decoded instruction to the Execution unit and selects the general registers specified by the instruction.

The EX-unit performs the actual execution of the instruction via microprogramming (i.e., microcode provides the signals that control the data flow through the hardware). Each macroinstruction corresponds to one or more microinstructions. At the end of a microcode routine which implements a macroinstruction, a 1:256-way branch in the microcode is executed in order to access the section of microcode required for execution of the following macroinstruction.

The CPU machine cycle is 250 ns and is the time required to read, compute, and write the result of a simple register to register operation such as add (RA = RA + RB). Each pipeline operation is completed in one machine cycle and data can be passed from one stage of the pipe to the next at this rate when the EX-unit is operating at its maximum rate. Three additional cycle times for the EX-unit are

AP-101S Space Shuttle GPC

### Figure 3. CPU Pipeline

provided to speed up the execution of multicycle instructions: 125 ns and 150 ns are for microcoded operations which do not require a full machine cycle to execute, and 100 ns is used for high-speed iterations typical in operations such as multiplication, division, and shifting.

Synchronization of the pipeline is accomplished by means of the ENDOP command which is issued at the end of each macroinstruction by the microprogram. The ENDOP command signals each stage of the pipeline to output its results (pass them on to the next stage) and to begin working on its new input (the output from the previous stage) at the beginning of the next machine cycle. When the EX-unit is operating on simple instructions, the ENDOP command may be issued every 250 ns, one machine cycle. When the EX-unit requires more than 250 ns for the execution of an instruction, the operation of all other stages in the pipeline is suspended (no ENDOP is issued) except for the prefetching of instructions by the I-unit (which continues independently until the 16 x 16-bit instruction file is full). When the EX unit has completed its operation the microprogram issues an ENDOP and all stages of the pipeline restart at the beginning of the following machine cycle. The ENDOP signal also signifies the end of a microcode routine, causing the EX-unit to branch (1:256-way branch) to the start of a new routine based on the next macroinstruction.

7

### 4.3 MAIN STORAGE

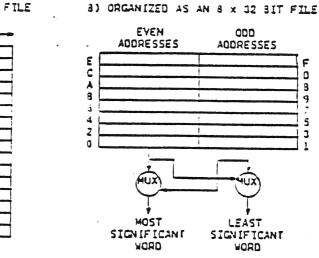

The AP-101S contains two battery-backed Static RAM CMOS pages, each containing 128K X 32 bits plus store protect bits and Error Correction Code (ECC) bits. Associated with each main memory halfword are three store protect bits and six Error Correction Code (ECC) bits which are determined by the 16 data bits.

The CMOS memory has an access time of 250 ns and a cycle time of 250 ns. This includes error detection and correction (EDC).

The AP-101S is also capable of operation with dynamic memory pages of the type found in the B1-B AP-101F computer. A signal indicating the type of memory in use is generated on the memory page, and this signal is used to configure the interface portion of the MMU. Both memory pages in use must be of the same type. The dynamic memory configuration provides 128K words of memory. Except for the difference in memory size, the type of memory in use is transparent to the software. Dynamic memory is not battery-backed and will not retain data in the event of power loss.

### 4.4 INFORMATION FORMATS

The system transmits information between main storage and the CPU in hits of 16 bits, or in integer multiples of 16 bits. Each 16-bit unit of information is called a halfword. Six error correction bits and three voted storage protection bits are also associated with each halfword for the AP-101S, but later references in this workbook to the size of the data fields exclude these bits.

Halfwords may be handled separately or in pairs. A fullword is a group of two consecutive halfwords. Both halfword and fullword instructions are used. Their location is always specified by the address of the most significant halfword. The instruction length is designated implicitly in every instruction. The operand length is also implicit.

Within any instruction and operand format, the bits making up the format are consecutively numbered from left to right, starting with the number zero, as shown in Figure 4 on page 9.

### Halfword

### Fullword

| U |                 | e l'égéné de la |  | 21                |

|---|-----------------|-----------------------------------------------------|--|-------------------|

| n |                 |                                                     |  |                   |

|   |                 |                                                     |  |                   |

|   |                 |                                                     |  |                   |

|   | - 106 a 100 k - | di di Angli altanti                                 |  | and the all all a |

| 1 |                 |                                                     |  |                   |

Figure 4. Instruction and Operand Bit Numbering

### 4.5 ADDRESSING

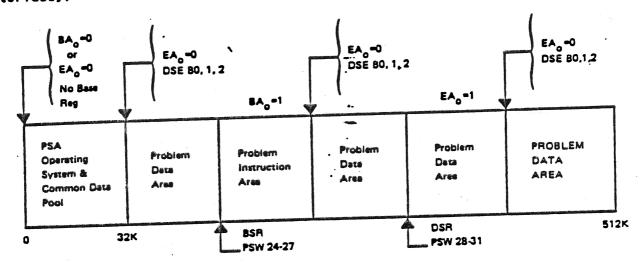

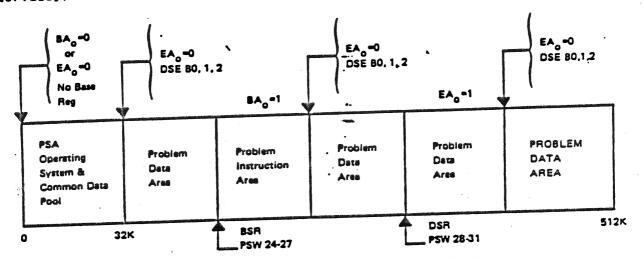

Halfword locations in storage are consecutively numbered starting with zero. Each number is considered the address of the corresponding halfword. The addressing technique uses a 19-bit binary address to accommodate a maximum of 512K halfword addresses. This set of main storage addresses includes some locations reserved for special purposes, such as program status words. Consequently, these special locations should not be used for any purpose not explicitly defined.

### 4.6 INFORMATION POSITIONING

Unlike previous versions of the AP-101 computer, the AP-101S does not require either fullword instructions or fullword/doubleword operands to be located in main storage on even boundaries.

### 4.7 PROGRAM ADDRESSABLE REGISTERS

Two sets of eight fixed-point general registers and one set of eight floating-point registers are under explicit program control. The contents of one or more of these registers (32 bits each) participate in most CPU operations. Associated with each of the general purpose registers is a 4-bit addressing extension register (Data Sector Extension or DSE), the use of which is described below in Extended Addressing.

onceptually, an additional doubleword status register, called the Program Status Word (PSW), is the focal point for machine status. The contents of the PSW are updated during each instruction. Consequently, the PSW reflects current machine status following every instruction. The PSW participates implicitly in status switching, branching operations, and address calculations. Condition codes resulting from an instruction are also part of the PSW.

In addition to the PSW and the general and floating-point registers, the CPU also contains working registers used for storage addressing, storage buffering, shift and iteration counting, and operand storage.

The contents of the PSW specify which of the two sets of general registers is in current use. Only the contents of the selected general register set can participate in arithmetic operations and the contents of unselected sets of general registers cannot be altered by a program. An alternate set of general registers can be selected by changing the PSN. Only one set of the fixed point, general purpose registers and the floating-point registers are available to the program at any one time.

General register contents can be used interchangeably as operands for arithmetic, logical and shifting operations, or as base and index registers for relative addressing. Each of the general registers is numbered from 0 through 7 and is addressed as shown in Figure 5.

| General<br>Register | Register Function |             |     |      |

|---------------------|-------------------|-------------|-----|------|

| Number              | Operand           | Base        | Ind | e x  |

| 0                   | 000               | 00          | Not | Used |

| . 1                 | 001               | 01          | 001 |      |

| 2                   | 010               | 10          | 010 |      |

| 3                   | 011               | 11 or none* | 011 |      |

| 4                   | 100               |             | 100 |      |

| 5                   | 101               |             | 101 |      |

| 6                   | 110 .             |             | 110 |      |

| 7                   | 111               |             | 111 |      |

\*11 = Register 3 for SRS; none for RS

Figure 5. General Register Addresses

Note that general registers 4 through 7 cannot contain base addresses and that general register O cannot contain an index.

in the second spectrum is a second

AP-1015 Space Shuttle GPC

10

For addressing data, general registers 0-3 can be augmented by 4-bit Data Sector Extension (DSE) registers or by the DSR in the PSW to address beyond 16-bit capabilities. There are 16 DSEs, one for each of the eight general-purpose registers in each of the two sets of general registers.

For some operations, a pair of general registers is linked to form a 64-bit doubleword register. The most significant half of a doubleword operand is contained in the specified register; the least significant half of the doubleword is in the next higher-numbered register (determined by modulo 8 addition of one (1) to the specified register). Note: If Reg 7 is specified, the least significant half of the double word operand is contained in Reg. 0.

One set of eight 32-bit floating-point registers is provided and these registers are separate and distinct from the general-purpose registers.

### 4.8 DATA REPRESENTATION

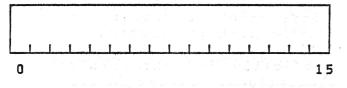

Fixed-point data representation is both integer and fractional, with negative numbers represented in twos complement form. A halfword operand is 15 bits plus sign, a fullword operand is 31 bits plus sign, and a doubleword operand is 63 bits plus sign, as shown in Figure 6 on page 12. In fractional data representation, the binary point is immediately to the right of the sign. In integer arithmetic, the binary point is to the right of bit 15.

Unless otherwise stated, fixed-point arithmetic operations assume a fractional data type.

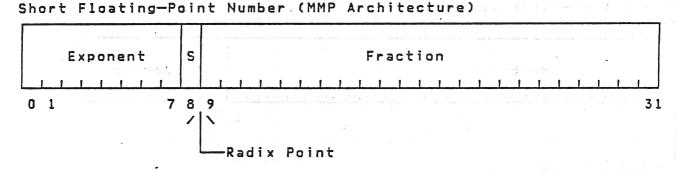

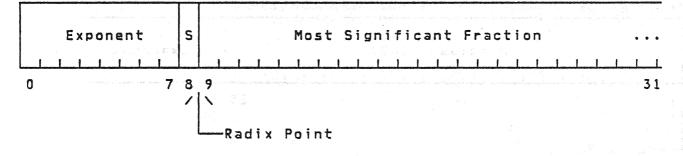

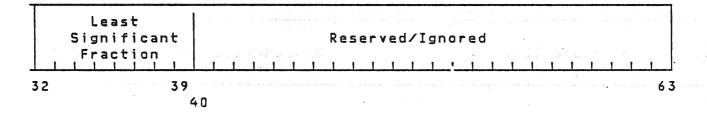

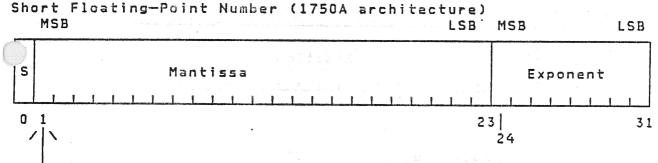

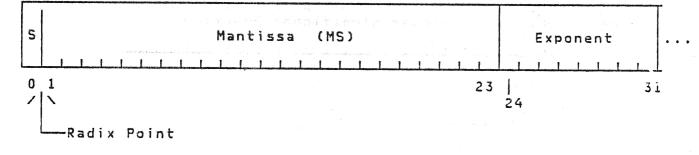

Floating point data occupies either a fullword format or a doubleword format. These formats differ between the MMP and 1750A architectures, as depicted in Figure 7 on page 13 and Figure 8 on page 14.

Long Floating-Point Number (MMP Architecture)

High Level Functional Description 13

이 아이는 것은 사람이 많이 가 없는 것은

and a second state of the second s

-Radix Point

Long Floating-Point Number (1750A Architecture)

Figure 8. Floating-Point Operand Formats (1750 Architecture)

### 4.9 INSTRUCTION FORMATS

The length of an instruction format can be either one or two 16-bit words. In contrast with 16-bit (halfword) instructions, 32-bit (fullword) instructions provide increased addressing, permit the specification of additional address modification, and make possible the designation of special conditions to test for in Jump instructions. Halfword instructions are used to (1) specify register-to-register operations, and (2) specify storage operands in cases where a small displacement is sufficient and complete address modification is not required.

Instruction formats overlap. Programs are written so that, in many instances, any given operation can be coded using either a halfword a fullword instruction. In such cases, maximum use of halfword

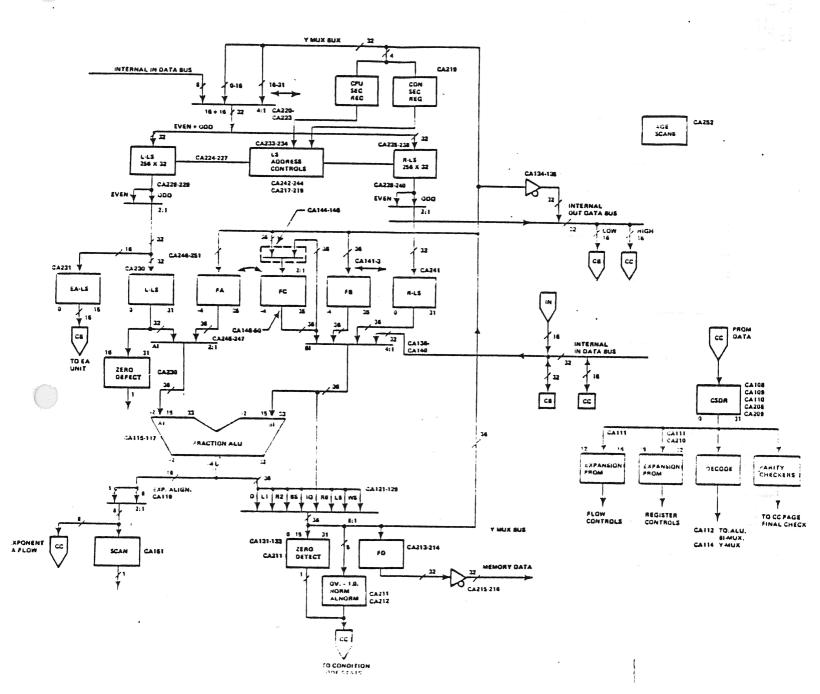

# 11.1 BACKPANEL FUNCTIONAL DESCRIPTION

The Backpanel provides the means of connecting all the pages in the AP101S Computer to each other and the outside world. It is a Multilayer Interconnection Board (MIB) with connectors for each page, the Power Converters, and the Input/Output (I/O) Wiring Harness. Figure 130 on page 256 gives a side view of the AP101S Computer showing the Backpanel and which page is in each connector.

# 11.1.1.1 Backpanel Layout

SLOT

There are 23 slots or places for connectors in the backpanel as defined below. The input voltages available to each slot are also listed.

| SLOT           | DESCRIPTION                                | INPUT VOLTAGES     |

|----------------|--------------------------------------------|--------------------|

| A 0 1<br>A 0 2 | I/O Harness<br>AD Page (Age and Discretes) | +5 MEMORY          |

| A 0 3          | MIA Page (Manchester Tata (                | +5V,+12V,+5_MEMORY |

| A04            | MIA Page (Manchester Interface Adapter)    | +5V,+12V,-12V      |

| A05            | MIA Page (Manchester Interface Adapter)    | +5V,+12V,-12V      |

| A06            | MIA Page (Manchester Interface Adapter)    | +5V,+12V,-12V      |

|                | MC Page (Master Sequencer Controller)      | +5V                |

| A07            | IB Page (I/O Buffer)                       | +5V                |

| A08            | SI Page (Status and Interrupt              | ÷5V                |

| A O 9          | FT Page (Flow Top)                         | +5V                |

| A10            | Spare Slot                                 | + 5 V              |

| A11            | Spare Slot                                 | + 5 V              |

| A12            | FB Page (Flow Bottom)                      | +5V                |

| A13            | IM Page (Interface and MIA Control)        |                    |

| A14            | CC Page (CPU 3)                            | +5V                |

| A15            | CB Page (CPU 2)                            | +5V                |

| A16            | CA Page (CPU 1)                            | +5V                |

| A17            | IN Page (Interrupt)                        | +5V                |

| A18            | MB Page (MMU 2)                            | + 5 V              |

| A19            |                                            | + 5 V              |

|                | MA Page (MMU 1)                            | +5V                |

| A20            | CMOS Memory Page                           | +5 MEMORY          |

| A21            | CMOS Memory Page                           | +5 MEMORY          |

| A22            | +5 Volt Converter (Power Supply)           | 28 VDC -           |

| A23            | 12 Volt Converter (Power Supply)           | 28 VDC             |

Figure 129. Backpanel Slot Input Voltages

All the connectors have 296 pins except the I/O Harness connector (A01) which has 300 pins and the +5 Volt and 12 Volt Power Converters (A22 and A23) which have 125 pins.

AP-101S Space Shuttle GPC

256

### BACKPANEL

# 11.1.1.2 Backpanel Stackup

The Backpanel consists of 23 layers as shown in Figure 131 on page 257. These include the "O" top and "O" bottom, eleven signal layers, and various voltage and ground layers. One signal layer is divided to provide straight runs for the MIA channels without any interference from other signals. This divider separates A01 through A05 from the other backpanel slots. Some of the voltage layers are also divided.

| LAYER<br>NUMBER                                                                                                               | COPPER<br>Thickness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DESCRIPTION                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23 | 1       OZ         2       OZ         2       OZ         1       OZ         2       OZ         2 | "O" TOP, FOIL<br>28V, +5V<br>SIG 1<br>SIG 2<br>+12V, 28V RETN<br>-12V, 28V<br>SIG 3<br>SIG 4<br>+5V, 28V RETN<br>BATTERY, +10V CHARGE 1 & 2<br>SIG 5<br>SIG 6<br>CMOS +5V, CHAS GND<br>GND, 28V<br>SIG 7<br>SIG 3<br>GND, 28V RETN<br>+5V, 28V RETN<br>SIG 9<br>SIG 10<br>GND<br>SIG 11, MIA<br>"O" BOTTOM |

|                                                                                                                               | and and any                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                            |

Figure 131. Backpanel Stackup

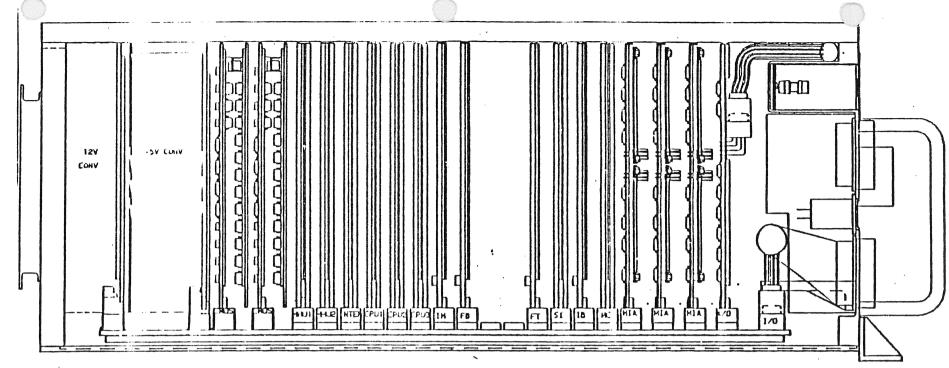

### 11.2 CPU PAGES

# 11.2.1 CPU Functional Description

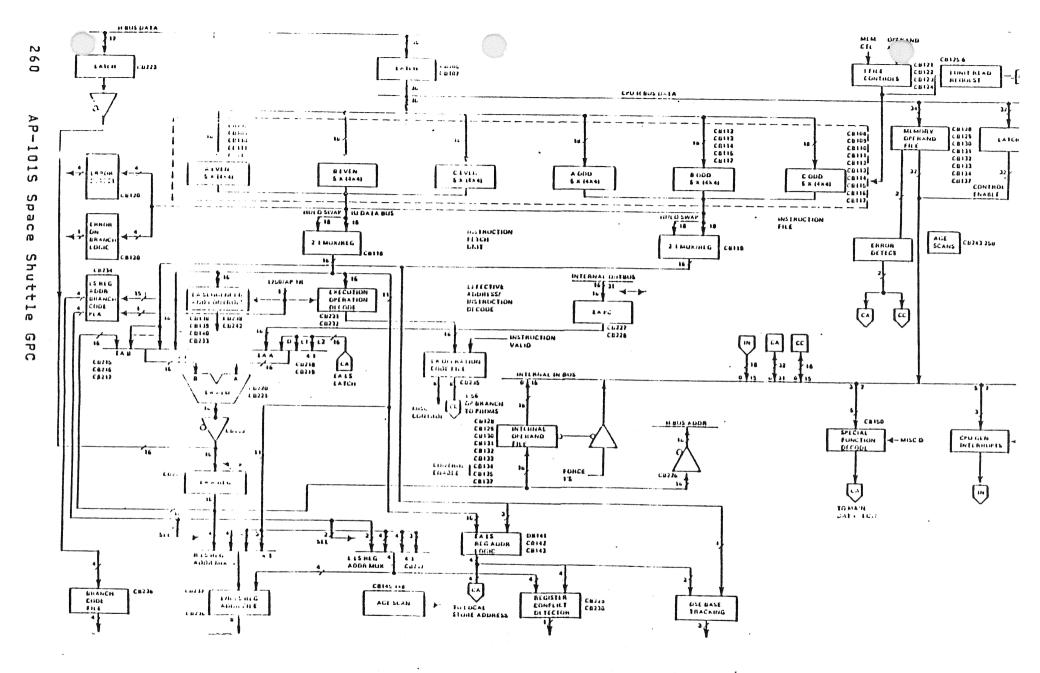

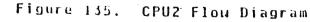

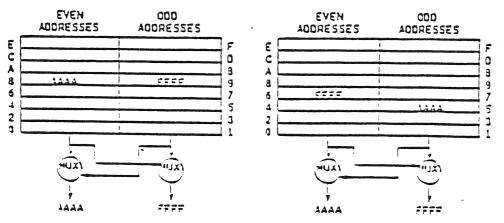

The AP-101S Central Processor Unit is optimized for both MMP and MIL-STD-1750A Notice 2 architectures, although the 1750A architecture is not implemented in the standard AP-101S configuration. The AP-101SG/1750, a special groundbase development configuration of the AP-101S, implements the 1750A architecture and shares with the AP-101S a common Central Processor Unit. The CPU flow diagrams are shown in Figure 132 on page 259, Figure 133 on page 260, and Figure 134 on page 261.

# 11.2.1.1 Instruction Unit

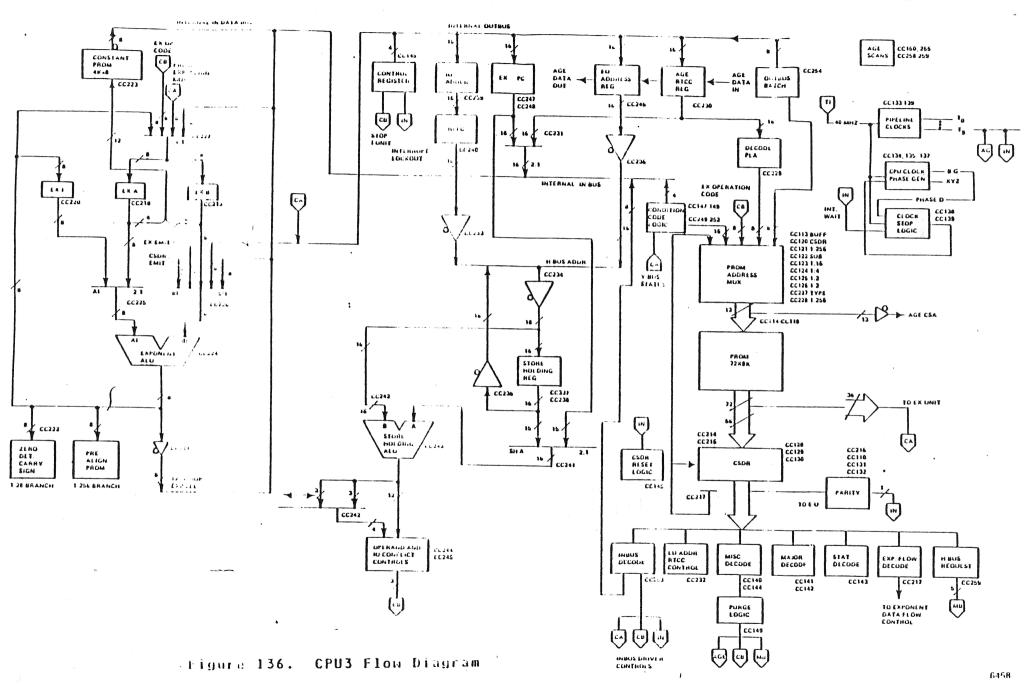

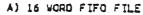

The Instruction unit uses its own instruction counter (IU-PC) to prefetch instructions from memory during unused memory cycles. Instructions are fetched two words (16 bits each) at a time and are put into a 16 x 16-bit FIFO instruction file, shown in Figure 135 on page 262.

The 16 word instruction file is organized as two 8 x 16-bit buffers. The most significant 16-bit instruction word is placed in the even address portion, and the least significant is placed in the odd address portion. The file is further divided between the higher order dresses (A) and the lower order addresses (B) so that it is accessed as shown in Figure 135 on page 262.

In addition to the A and B sets of Suffers, the instruction file also has a C set of buffers to minimize delays when a branch is taken. When a branch instruction is encountered, the EA-unit generates the branch address, prefetches two words from that location, and places them in the C set of buffers. If the branch is not taken, the instruction file continues to fill up the A and B sets of buffers as before. However, when the Execution unit determines that a branch is taken, it directs the instruction file to switch from the A and B buffers to the A and C buffers and to start fetching instructions from the location following the branch address (branch address plus two, since the EA-unit has already fetched the two words located at the branch address and placed them in the C Euffer). The A and C buffers are now the sources of instructions for the EA-unit, and no time has been lost by the switch. The next branch taken will cause the instruction file to switch from buffers A and C back to buffers A and 3 again, and so forth.

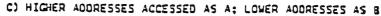

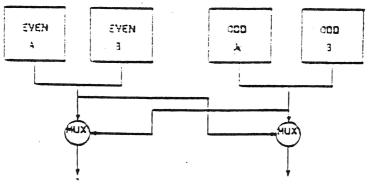

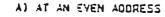

Instructions can be either one or two 16-bit words long, so two alignment multiplexers (muxes) at the output of the file ensure that a 16-bit instruction or the most significant word of a 32-bit instruction is always output from the left mux. To correctly output a 16-bit instruction at an even or odd address, the left mux'chooses s even or odd input, respectively. For 52-bit instructions start-

Figure 132. CPU1 Flow Diagram

# Figure 135. Instruction File

ing at an even or odd address, the left mux again chooses its even or odd input, respectively, and the right mux the complementary input, odd or even, respectively. Figure 136 on page 264 shows how the 16-bit instruction AAFF is output from even and odd locations, and Figure 137 on page 264 shows the 32-bit instruction AAAA FFFF being output from even and odd locations.

# 11.2.1.2 Effective Address Unit

The EA-unit decodes the instruction and provides this decoded version to the Execution unit. The EA-unit also handles the generation of the operand addresses and prefetches the operands for the EX-unit. Operands or addresses can be provided by the instruction as immediate data, or may need to be calculated by adding any combination of the following:

1. Immediate data

- 2. Contents of a base register or memory location

- 3. Contents of an index register

- 4. Displacement.

The EA-unit and I-unit data flows are shown in Figure 138 on page 265. Instructions sent from the I-unit enter two logic sections in the EA-unit. In the Execution Operation Decode section, the instruction is decoded, converted into an 8-bit code, and sent to the EX Operation Code File for the EX-unit to access when executing an ENDOP 1:256-way branch issued by the microcode. The EA Sequencer and Controls section generates the control signals needed for the EA-ALU and its associated logic to compute the loyical addresses of the operands and to prefetch those operands when necessary.

To compute operand addresses, the EA Sequencer and Controls section first determines what type of addressing is used in the instruction. The EA-unit then fetches the contents of any base or index register or memory location (indirect addressing) specified and selects from the instruction any displacement or immediate data for input to the EA-ALU. The EA-unit calculates the address of the operands by summing register or memory contents, immediate data and displacement as indicated by the type of addressing.

The EA-unit places the results of its calculations into the EA-A register, then sends them to the Internal Operand File. General register addresses are set up by the EA-unit for use by the EX-unit as required for the instruction. If an instruction requires an operand from memory, that operand is fetched and placed in the Memory Operand File by the EA-unit. The operands for the instruction have thus been prefetched into one of two files (internal or memory), and the EA-unit controls which of these files will be provided to the EX-unit.

Figure 136. Accessing a 16-Bit Instruction

3) AT AN ODD ADDRESS

Figure 137. Accessing a 32-Bit Instruction

Description 26

S

L o u

Leve

-

Functiona

-

## 11.2.1.3 Execution Unit

The Execution unit contains all the logic needed to perform 16- or 2-bit fixed point operations and 32-, 40-, or 48-bit floating point operations. Microcode provides the control signals for the hardware in this unit and is contained in an 8K x 72 Programmable Read Only Memory (PROM). Thirty-two x 8-bit Expansion PROMs are used to minimize the width of the microword while still allowing multiple control signals to the hardware. Five bits in the microword address one of the 32 locations in one or more of the Expansion PROMs to provide a 16- or 24-bit field of control signals.

The CPU local store (LS) consists of two duplicate 256 x 16-bit banks of registers which are organized as 32 sectors (16 CPU, 16 constant) of 16 registers each. The general purpose registers are located in one (1750) or two (MMP) of these sectors, and in MMP another sector is used for the floating-point register set. The remaining sectors are used for temporary storage of partial results or contain constants which are loaded from the constant prom during machine reset and are accessed by the microcode for certain computations. There are two identical LS banks, a left LS and a right LS arranged as a dual-port local store. To the macroprogrammer, the local store appears as one set of general purpose registers; but the two halves may be read independently by the microcoder so that the contents of two independent registers may be used in the same machine cycle. This allows simple operations, such as add or subtract, involving two registers to be completed in one 250 ns machine cycle. When writing to local store, both the left and right halves are written into at he same locations to keep the contents of the two sides identical.

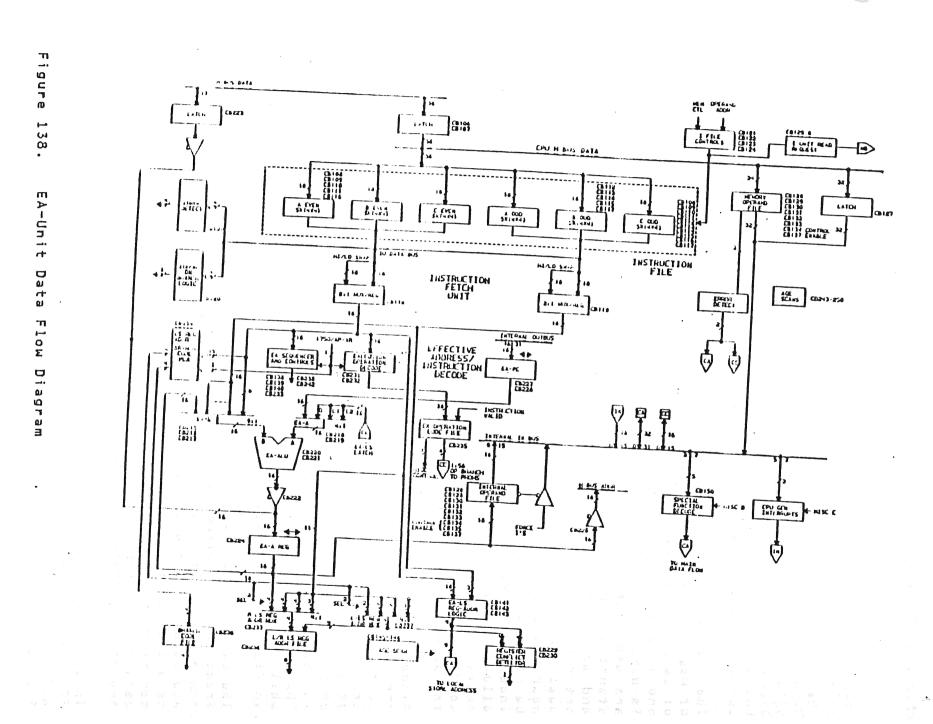

Since both the EX and EA-units may need to access local store during the same machine cycle, provision has been made for local store to be time-shared. In a 250 ns machine cycle, the EX-unit reads local store during the first 75 ns, the EA-unit reads LS during the second 75 ns, and the EX-unit writes to local store during the last 100 ns of the cycle. This requires the EX-unit to perform its computations in the second 75 ns period while the EA is accessing local store. The EA-unit performs its computations in the last 100 ns of the cycle while the EX-unit is writing to local store. This timing is shown in Figure 139 on page 267.

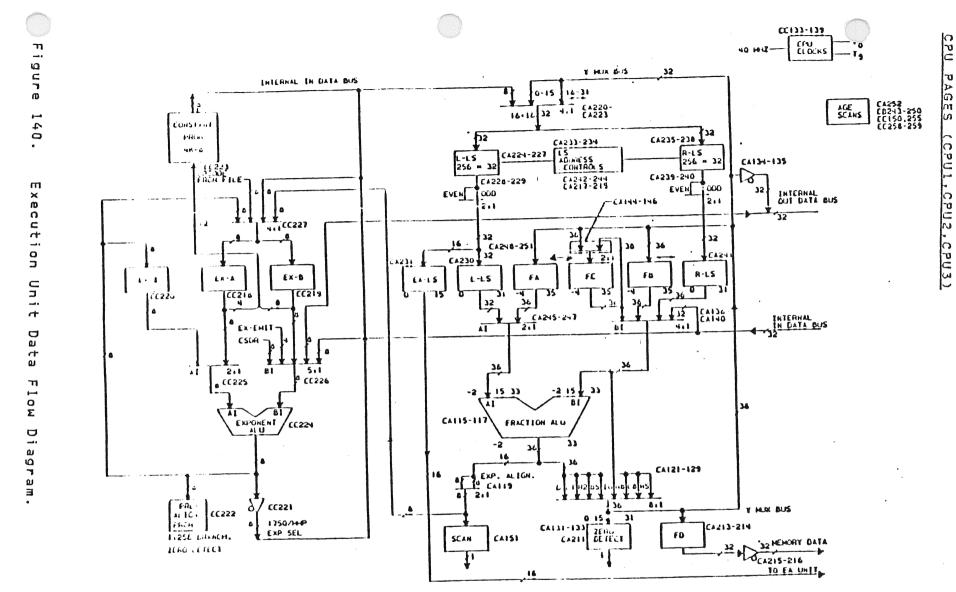

The EX-unit data flow is shown in Figure 140 on page 268. A 36-bit Fraction ALU handles computations involving fixed point numbers and the mantissa portion of floating point numbers. The 3-bit Exponent ALU calculates the exponent in floating point operations and is used as a counter in iterative operations. In addition, the Exponent ALU can be used as an extension of the Fraction ALU to provide an expanded data flow (40 bits) for some Extended Floating Point operations in the MIL-STD-1750A architecture.

Input to the Fraction ALU can come from local store, the FA, FB, or FC registers, and the internal data bus where data from the Internal and Memory Operand Files and from EX-unit memory reads is placed. ovision is made for ALU results to be shifted. At the output of

the ALU, the Y Mux is capable of passing data directly or shifting left 1, right 2, left 8, right 8, 16-bit word swaps, 8-bit byte swaps, or setting up for I/O. Data from the output bus may be sent to local store, the FA, FB, and FC input registers, and the FD register. The FD register is dedicated to holding data which will be stored in memory.

# 11.2.1.4 Typical Instruction Execution

The following example will illustrate the roles of the EA and EX-units in the execution of a typical instruction. The instruction A (add) of MMP is a 32-bit integer add using the base-relative indexed addressing mode (contents of base register + the displacement (bits 21 - 31 of the instruction) + contents of index register (shifted left 1 for a fullword alignment) = address of the second operand). R1 is the register containing the first operand, D2 is the displacement, X2 is the index register, and B2 is the base register. The result of the add is stored in R1.

Figure 139. Time-Sharing of Local Store

268 AP-1015 sp ۵J 0 n Shut rt n GPC

CPU

PAGE

S

Instruction: A R1,D2(X2,B2)

### <u>EA-Unit</u>

- Decodes instruction and places an 8-bit value of x'AO' in the EX Operation Code File to be used as a vector for the 1:256-way branch by the EX at ENDOP. This is because the RS format add instruction begins at microcode location x'O2AO'.

- Fetches the contents of B2 and adds this to D2, storing the result (the Preliminary Effective Addres;) in the EA-A register.

- Fetches the contents of X2, shifts these contents left 1 and adds them to the contents of the EA-A register, storing the result (the Effective Address) in the EA-A register.

- Fetches the second operand from the memory address given by the contents of the EA-A reg and places it in the Memory Operand File

- Selects R1 (instruction bits 5-7) as the left local store register ter address and selects the contents of the Memory Operand file rather than the Internal Operand file to be placed on the Internal In Data Bus, or INBUS, when the ENABLE OPERAND signal from the EX-unit goes high.

### EX-Unit

- Selects the left local store input for the fraction AI mux and the INBUS input for the fraction ALU BI mux. The INBUS contains contents of Memory Operand file by default (statb3 must be zero).

- Adds operands

- Outputs operands directly (no shifting) at Y Mux to Y-Bus

- Writes data from Y-Bus to both left and right local store using R1 as the address of the register to be written into.

# 11.2.1.5 Conflicts and Hazards

Several faults are associated with the operation of a pipelined machine:

- 1. Register Conflicts

- 2. Operand Conflicts

- 3. I-Unit Hazard (Store Within Range)

The CPU contains the logic necessary to detect these conflicts and take appropriate action while minimizing any performance impacts. These conflicts are explained below.

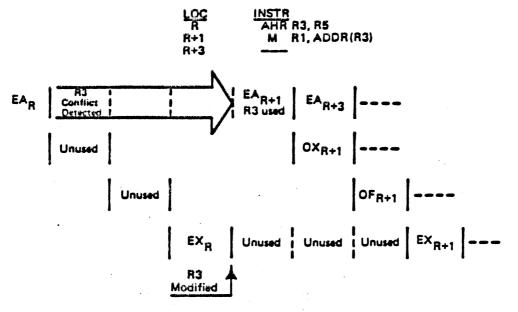

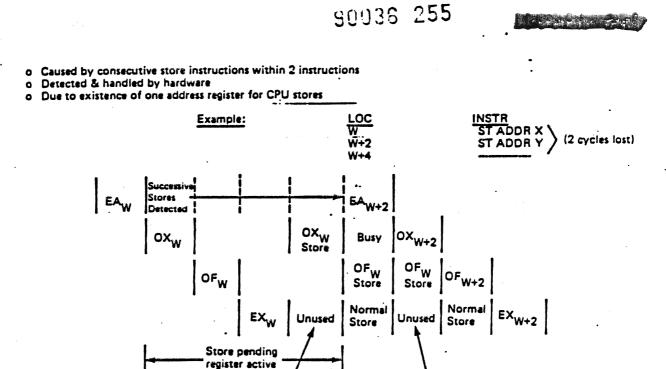

Degister Conflicts: A register conflict occurs when the EX-unit modifies the contents of a register which will be used in the EA calculation of any of the next three instructions. When a register conflict is detected, the EA must wait until the EX-unit has completed its register store, then start again using the new contents of the register.

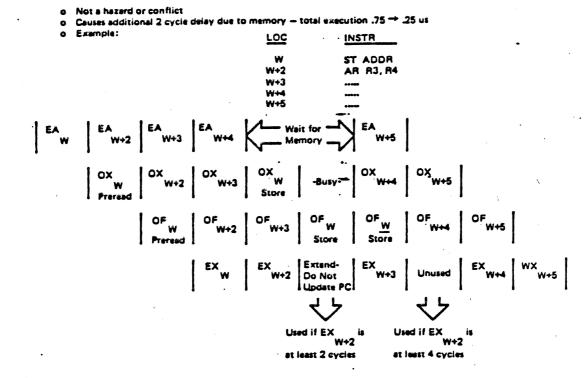

Operand Conflicts: An operand conflict occurs when the EX-unit will modify the contents of a memory location whose contents will be prefetched for any of the next three instructions. When an operand conflict is detected, the EA-unit must wait until the EX-unit has completed storing into the memory location before it can access that location.

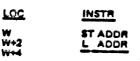

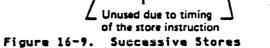

I-Unit Hazard (Store Within Range): An I-unit hazard occurs when the EX-unit modifies a memory location which may have been prefetched by the Instruction unit. When this occurs, the entire pipeline must be purged and restarted with the instruction following the store. The AP-101S contains a two page Memory Management Unit (MMU) which incorporates numerous functions in addition to management of main memory. The MMU flow diagrams are shown in Figure 141 on Fage 272 and Figure 142 on page 273. Included among the diverse tasks performed by the MMU are the following functions:

- The MMU arbitrates and controls the timing and sequencing of the HBUS.

- 2. The MMU controls all timing and sequencing to the mainstore in the AP-101S computer.

- 3. The MMU contains the address expansion logic for the system. The address expansion mechanisms are architecturally defined and are different for each architecture. The MMU accommodates either under external control.

- 4. The MMU is responsible for detecting, capturing and posting memory related faults. These faults vary according to architecture, system configuration and memory requestor.

- 5. The MMU directs I/O commands to the proper system element via designate generation.

- 6. The MMU supports testability by:

- a. Providing various diagnostic modes of operation under control of the MMU mode register.

- b. Providing several serial scan paths.

- c. Providing several IIO (Internal I/O) commands which make various MMU registers accessible to the diagnostic programmer.

- d. Further identifying faults detected by the MMU Memory Fault Extension Register (MFER).

- e. Providing an HBUS arbiter port for the tester.

# 11.2.2.1 MMU Clock Generation

The MMU generates a 40 MHz clock common to all the pages that are attached to the HBUS and receives a time 9 sync pulse from the CPU-3 page. From these two signals, a series of 10 pulses, each 50 ns in width is created. The 10 clocks are labeled T0 through T9 with the newly created T9 corresponding to the sync time 9. The MMU clocks are illustrated in Figure 143 on page 274.

Figure 141. MMUA Flow figure

272 AP-101S Space Shuttle GPC

# MEMORY MANAGEMENT UNIT PAGES ( MMU1, MMU2)

÷

- DA CREEKE ENDING VERME

forthroom show S.S. Self

O. T. W.

61%

合于 安

STUDIA

1

Figure 142. MMUB Flow Diagram

### MEMORY MANAGEMENT UNIT PAGES ( MMU1, MMU2)

The MMU also contains a 24 MHZ oscillator for the 1553 page in the 1750 mode. The oscillator is used to generate 12 MHZ and 24 MHZ clock for the 1553 page.

11.2.2.2 MMU Reset Logic

When an Inhibit Main Store (IMS) is generated, a system reset is issued on the MMU. The Interrupt page generates an IMS pending signal shortly before issuing an IMS. When this signal is active, the MMU stops all HBUS activity. When IMS becomes active, the MMU resets itself and 250 ns later starts all activity again. At this point, any request to the arbiters will be acknowledged.

### 11.2.2.3 Mode Control

The MMU supports several different modes of operation. To change these modes, the user must issue the internal I/O (IIO) command of

| +40 MHz |   |

|---------|---|

| SYNC T9 |   |

|         | < |

| + T O   |   |

| +71     |   |

| + T 2   |   |

| + T 3   |   |

| + T 4   |   |

| + T 5   |   |

| + T 6   |   |

| +77     | · |

| +78     |   |

| +T9     |   |

|         |   |

Figure 143. MMU Clocks

## MEMORY MANAGEMENT UNIT PAGES ( MMU1, MMU2)

X'9407'. To read the current mode of operation, The IIO code of X'140B' can be used. There are 10 functions defined by the mode register (Figure 144 on page 275).

Figure 144. MMU Mode Register

| FUNCTION                | WRITE<br>BIT | READ<br>BIT |

|-------------------------|--------------|-------------|

| INHIBIT DMA'S           | 06           | 22          |

| DISABLE STORAGE ERRORS  | 07           | 23          |

| BCE DISABLE             | 08           | 24          |

| SPECIAL STORE PROTECT   | 09           | 25          |

| TRANSMIT DISABLE        | 10           | 26          |

| SYSTEM IPL              | 11           | 27          |

| PASSTHRU CMOS           | 12           | 28          |

| SYNDROME/CHECK BIT MODE | 13           | 29          |

| CODE IDO                | 14           | 30          |

| SCRUB DISABLE           | 15           | 31          |

### 11.2.2.4 Bus Protocol

The Memory Management Unit (MMU) transfers data between the central processor and the IOP through the HBUS. This is a high-speed synchronous bus developed to transfer memory data at high rates of speed.

# 11.2.2.5 Memory Address Expansion

The MMU handles all memory address expansion requirements for the AP-101S computer. The general functions performed by the MMU address expansion logic are:

- A 20-bit Advanced Programmable Tester (APT) address is accommodated on the 16-bit HBUS address bus

- 2. Memory addressing for 512K halfwords (20-bit) is provided.

- Either halfword (16-bit) or fullword (32-bit) accesses are permitted during a single memory cycle.

- 4. No boundary constraints are imposed on fullword accesses, toba

. EUSH and no seemble

040 S.e.S.<u>9</u>.11

icol tidoli a sesse UHO sol iconotecuper ile bog sectors da UGO cos giones 2005 i vo benimereo el secordo

tour the implanees the UNN and

isillulia adj zaslovi zasloba is lik-216-21 z jo sjutostinoja

and politic state bandeds

64 14 7

orist southethe istas and and

The Heus Staulator resistor of

## MEMORY MANAGEMENT UNIT PAGES ( MMU1, MMU2)

- 5. The ability to bypass the address expansion logic is provided.

- 6. Separate address expansion mechanisms are provided for each ar-

11.2.2.6 Address Interfaces

11.2.2.6.1 IOP Interface

The IOP in the AP-101S computer always provides a physical 18-bit address on the HBUS.

11.2.2.6.2 CPU

The CPU passes a 16-bit logical address to the MMU via the HBUS. This address and all requestor generated HBUS tag bits are passed on the HBUS during any CPU acknowledge cycle. The CPU unit sourcing this address is determined by the particular acknowledge that was granted. During the address cycle, the 16-bit logical address is selected into the MMU address flow, and must be expanded into a 20-bit physical address (unless the operation type bits specify "no map") in the 1750 architecture or a 19-bit physical address in the MMP architecture.

# 1.2.2.6.3 Avionics Programmable Tester (APT)

When an SDI (APT) acknowledge is granted, a 20-bit physical address is passed to the MMU. The low order 16 bits are passed over the HBUS via normal HBUS protocol. The high order four bits are serially scanned into a holding register on MMU1 at the same time that the testers serial interface logic (refer to the SDI description) scans in the HBUS Simulator register on the interrupt page. During the SDI ACK, the high four bits and the low 16 bits are concatenated and selected into the MMU address flow. This 20-bit physical address always bypasses the address expansion logic.

11.2.2.7 Address Expansion Logic

The requirement to support single cycle memory accesses for doublewords on any boundary based on a single address that is passed to the MMU dictates the following MMU hardware support:

Address adder 🗠

276 AP-101S Space Shuttle GPC

•

e "

|                   |                               | ·                               |                                   |

|-------------------|-------------------------------|---------------------------------|-----------------------------------|

| POWER             | 560 WATTS                     | 780 WATTS                       | SAVE 1100 WATTS                   |

| WEIGHT            | 64 LBS                        | 117 LBS                         | SLEEP MODE: 56 WATTS              |

|                   |                               |                                 | EAVE 318 LBS                      |

| MEMORY            | CMOS: 256K FW'S               | CORE: 104K FW'S                 | OI20 G3 ARCHIVE                   |

| HALF WORD         | 6 EDAC BITS                   | 16 DATA BITS                    |                                   |

|                   | 3 STORE PROTECT               | 1 PARITY BIT<br>1 STORE PROTECT | ERROR DETECTION<br>AND CORRECTION |

| •                 |                               | • •                             | MEMORY SCRUB                      |

| SPEED             | > 1000 Kops                   | 420 KOPS .                      | 018F 1.7 TO 1                     |

| BATTERY<br>BACKUP | 6 RECHARGEABLE<br>NICADS      | •••••                           | REMOVABLE SRU                     |

| BITE              | TEMPERATURE<br>CHARGER        | •••••                           |                                   |

|                   | BATTERY<br>SOFT ERROR COUNTER |                                 |                                   |

| MTBF              | DESIGN: 6,000 HRS             | 5250 HRS                        | · ·                               |

| 45× • * . ,       | OUTLOOK: 10,000 HRS           |                                 | CURRENT AP101S: 24,000 HRS        |

|                   |                               |                                 |                                   |

1 68 C

2.0 AP-1015 STRUCTURE

#### 2.1 SHUTTLE INSTRUCTION SET

The AP-101S system structure encompasses the functional operation of main storage, the central processing unit (CPU), and program-controlled I/O facilities.

#### 2.1.1 Information Formats

The system transmits information between main storage and the CPU in units of 16 bits, or in integer multiple of 16 bits. Each 16-bit unit of information is called a halfword. Six error correction bits and three voted storage protection bits are also associated with each halfword for the AP-101S but later references in this manual to the size of data fields exclude these bits. The AP-101S/G has two storage protect bits per halfword.

Halfwords may be handled separately or in pairs. A fullword is a group of two consecutive halfwords. Both halfword and fullword instructions and operands are used. Their location is always specified by the address of the leftmost halfword (leftmost halfword is the numerically smallest address). The instruction length is designated implicitly in every instruction; the operand length is also implicit.

Within any instruction and operand format, the bits making up the format are consecutively numbered from left to right, starting with the number 0, as shown in Figure 2-1.

2-1

. Addressing

- BERGER

Halfword locations in storage are consecutively numbered starting with 0. Each number is considered the address of the corresponding halfword. The addressing technique uses a 19-bit binary address to a maximum of 2<sup>19</sup> halfword addresses. This set of main storage addresses includes some locations reserved for special purposes, such as program status words; consequently, these special locations should not be used for any purpose not implicitly defined.

### 2.1.3 Information Positioning

Unlike previous versions of the AP-101 computer, the AP-1015 does not require either fullword instructions or fullword/doubleword operands to be located in main storage on even boundaries.

#### 2.2 CENTRAL PROCESSING UNIT

The central processing unit (CPU) contains facilities for addressing main "torage, fetching or storing information, for arithmetic and logical processing of data, to. sequencing instructions in the desired order, and for initiating the con initiation between storage and external devices.

The control section guides the CPU through the functions necessary to execute the program.

#### 2.2.1 Program Addressable Registers

Two sets of eight fixed point general registers and one set of eight floating point registers are under explicit program control. The contents of one or more of these registers (32 bits) participate in most CPU operations. Associated with each of the fixed point registers is a 4-bit addressing extension register (Data Sactor Extension or DSE), the use of which is described below in Extended Addressing.

Conceptually, an additional doubleword status register, called the program status word (PSW), is the focal point for machine status. The contents of the PSW are updated during each instruction. Consequently, the PSW reflacts current machine status following every instruction. The PSW participates implicitly in status switching, branching operations, and address calculations. Condition codes resulting from an instruction are also part of the PSW.

In addition to the PSW and the general and floating point registers, the CPU also c tains working registers used for storage addressing, storage buffering, shift and . .ration counting, and operand storage. These registers are of no direct concern to the programmer and are not described herein.

2-2

STATES TO BE SHOLD

The contents of the PSW specify which of the two sets of general registers is in current use. Only the contents of the selected general register set can participate in arithmetic operations and the contents of unselected sets of general registers cannot be altered by a program. An alternate set of general registers can be selected by changing the PSW. Only one set of the fixed point, general-purpose registers and the floating point registers are available to the program at any one time.

General register contents can be used interchangeably as operands for arithmetic, logical, and shifting operations, or as base and index registers for relative addressing. Each set of general registers is numbered from 0 through 7 and is addressed as shown in Figure 2-2.

| General<br>Register<br>Number        | Register Function                                    |                              |                                                       |  |  |  |  |

|--------------------------------------|------------------------------------------------------|------------------------------|-------------------------------------------------------|--|--|--|--|

|                                      | Operand                                              | Base                         | Index                                                 |  |  |  |  |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 00<br>01<br>10<br>11 or None | None<br>001<br>010<br>011<br>100<br>101<br>110<br>111 |  |  |  |  |

# ¥11 = Register 3 for SRS; none for RS

# Figure 2-2. General Register Addresses

Note that general registers 4 through 7 cannot contain base addresses and that general register 0 cannot contain an index.

For addressing data, general registers 0-3 can be augmented by 4-bit Data Sector Extension (DSE) registers or by the DSR in the PSW to address beyond 16-bit capabilities. There are 16 DSEs, one for each of the eight general-purpose registers in each of the two sets of general registers.

For some operations, a pair of general registers is linked to form a 64-bit doubleword register. The most significant half of a doubleword operand is contained in the specified register; the least significant half of the doubleword is in the next higher-numbered register (determined by Modulo 8 addition of one (1) to the specified register). Note: If Reg 7 is specified, the least significant half of the double word operand is contained in Reg. 0.

#### Surface and the second

# 2.2 Fixed Point Data Representation

Data representation is fractional, with negative numbers represented in twos complement form. A helfword operand is 15 bits plus sign, a fullword operand is 31 bits plus sign, and a doubleword operand is 63 bits plus sign, as shown in Figure 2-3.

In fractional data representation, the binary point is immediately to the right of the sign.

### 2.2.3 Instruction Formats

The length of an instruction format can be either one or two halfwords. Long format instructions provide maximum range and extended flexibility for addressing storage operands. Short instructions are used to (1) specify register-to-register operations, and (2) specify storage operands in cases where a small displacement is sufficient and complete address modification capability is not required.

Instruction formats overlap. Programs are written so that, in many instances, any given operation can be coded using either a halfword or a fullword instruction. In such cases, maximum use of halfword instructions results in increased storage efficiency and performance.

The three basic instruction formats are as shown in Figure 2-4. Kalfword # structions are automatically selected by the assembler unless otherwise specified the programmer.

2-4

Figure 2-4. Basic Instruction Formats

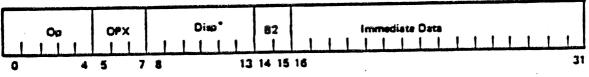

The fields within the instruction formats usually are used as described below. The exceptions are described in conjunction with the individual formats and instructions.

- Op This 5-bit field defines an operation, or the class of operation, to be performed by the SPU.

- R1 This 3-bit field designates the register containing the first operand. Except for operations which alter main storage, the result usually replaces the first operand.

- R2 This 3-bit field appears only in the RR format. It is used to specify a general register containing either the second operand or the address of the second operand.

- B2 This 2-bit field specifies the register containing the base address.

- Disp In halfword SRS format instructions, this 6-bit field is called the displacement. For the SRS format, the displacement is added to the base address specified by the B field to obtain a storage address.

- OPX This bit is an extension of the OP field.

AM This field designates one of two fullword format addressing options.

2-5

the second s

Address The second halfword of a fullword instruction is specified as either pecifi- extended or indexed addressing. cation

See the Effective Address Generation Summary Chart, page 11-1.

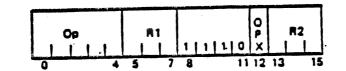

### 2.2.4 RR Format Instructions

The RR format instructions (Figure 2-5) permit the specification of operations that use two general registers.

Figure 2-5. The RR Instruction Formats

The operation normally uses as operands the contents of two general registers. The R2 field specifies the second operand while the R1 specifies the first operand. The jult of the operation usually replaces the first operand.

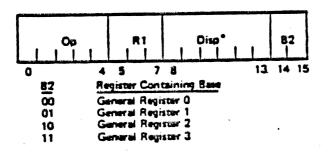

### 2.2.5 SRS Format Instructions

The SRS instruction format (Figure 2-6) is a compression of the RS format. It provides base plus displacement storage addressing.

Displacements of the form 111XXX are not valid.

Figure 2-4. SRS Instruction Format

.

The R1 field specifies the first operand register address. The 19-bit effective address (EA) of the second operand is developed as follows:

Step 1 First the positive integer contained in the displacement field is added to the contents of the base contained in the general register specified by B2.

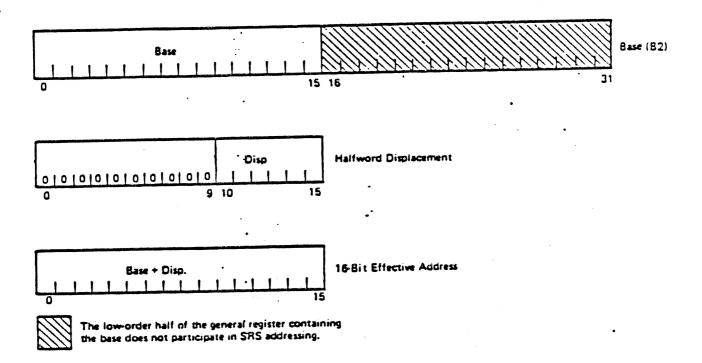

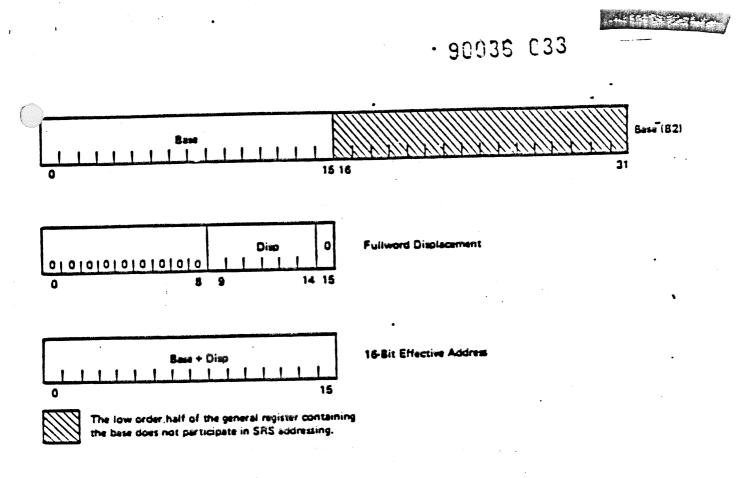

When addressing halfword operands, the least significant bit of the displacement field (instruction bit 13) is aligned with base register bit 15. The 16-bit result is the sum of the base and the displacement, aligned as shown in Figure 2-7.

When addressing fullword operands using the SRS format, the least significant bit of the displacement field is aligned with base register bit 14 as shown in Figure 2-8.

Unlike previous versions of this architecture, bit 15 of a base register is significant when addressing fullword data. Fullword storage operands may now be located on odd address boundaries. Programs which utilize this feature will not be downward compatible.

Step 2 The 16-bit result of the addition of the base and displacement is expanded (see Expanded Addressing) to a 19-bit effective address (EA), and this is the address of the second operand.

Figure 2-7. SRS Halfword Addressing

### Figure 2-8. SRS Fullword Addressing

Except for store instructions, the result of operation between the first operand (the contents of general register R1) and the second operand (the contents of the EA) replaces the first operand for SRS format operations. The first operand replaces the second operand for store instructions.

#### 2.2.6 SI Instructions

Direct initialization, modification, and testing of main storage is possible through the use of an immediate data halfword appended to an SRS instruction. See Figure 2-9.

\*Displacements of the form 111XXX are not valid.

Figure 2-9. SI Instructions

a address of the halfword second operand is developed in the normal manner for SRS instructions using halfword addressing. Except for test instructions, the result of operation between the halfword second operand and the immediate data replaces

SALAS -

the second operand. The second operand is not altered for test instructions. The first operand is never altered for SI instructions.

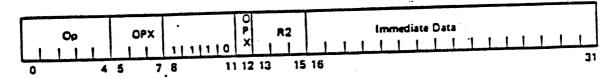

### 2.2.7 RI Instructions

Using an immediate data halfword appended to an RR instruction (Figure 2-10) permits direct initialization, modification, and testing of the most significant 16 bits contained in a general register.

Figure 2-10. RI Instructions

Except for test instructions, the result of the operation between the second operand and the immediate data replaces the second operand. The second operand is not altered for test instructions. The immediate data first operand is never altered for RI instructions.

### 2.2.8 <u>R5 Format Instructions</u>

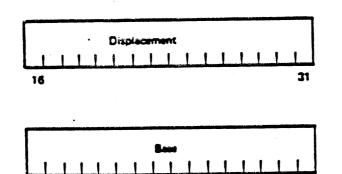

There are two major classes of RS instructions, extended and indexed addressing modes, differing in the techniques used to specify the second operand. See Figure 2-11.

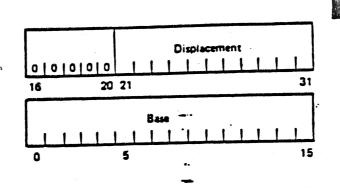

Extended addressing is specified when RS format bit 13 (AM) equals 0. This / Tressing wode provides a full 16-bit halfword displacement. The base and L splacement are aligned as shown in Figure 2-12 when base addressing is performed.

Figure 2-12. Displacement Alignment for Extended Addressing

Aside from the size and alignment of the displacement, RS extended addressing differs from SRS addressing in two other respects:

- 1. The alignment of the displacement is the same whether addressing doubleword, fullword or halfword operands.

- 2. When B2 equals 11, base addressing is not performed. In this case, the displacement is instead used directly as the effective address.

2-10

####

This

Indexed addressing is specified by RS format bit 13 (AM) equal to 1. This addressing mode contains three additional fields. Normally, they contribute to the effective address generation as follows:

X

I

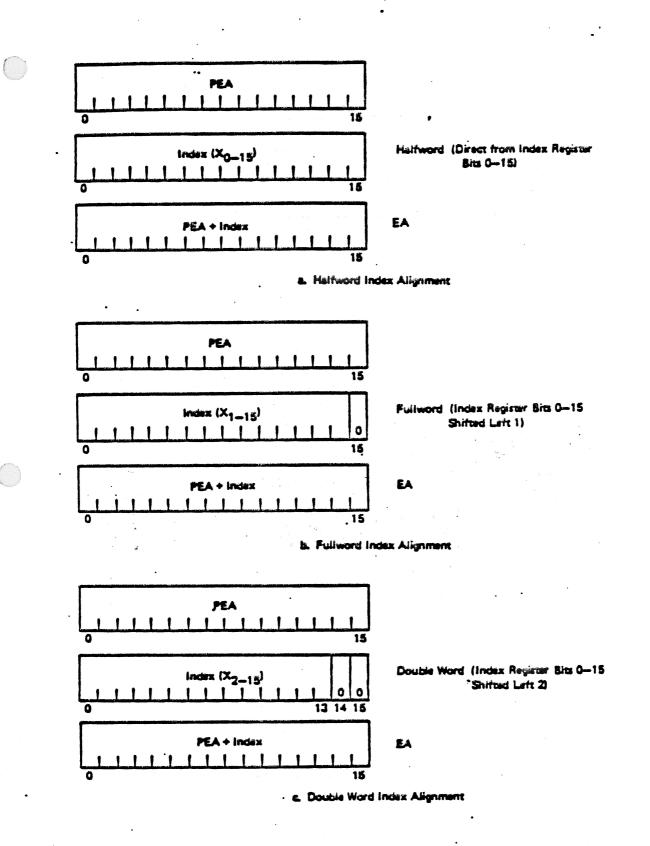

- This 3-bit field specifies one of seven general registers containing the index. Indexing is not performed when X is equal to 000. An index is contained in the upper halfword of a general register. index is automatically aligned as illustrated in Figure 2-13. For additional information on index-alignment, see Section 14. Consistent with the restrictions that apply to register usage and indirect addressing, general register contents can be used interchangeably as When indirect addressing is either a base or an index or both. specified, indexing follows indirect addressing (postindexing).

- This format bit, when a one, specifies indirect addressing. Indirect addressing is not performed when this bit is zero. In the instruction IA descriptions, the symbol 2 denotes IA for the assembler.

- This format bit, in conjunction with X and IA, specifies various In the instruction address modes which are explained below. descriptions, the symbol # denotes I for the assembler.

The development of the EA for the indexed mode (including IC relative) of operand addressing is explained in detail in the subsequent steps:

Indexed addressing is specified by RS format bit 13 (AM) equal to 1. This addressing mode provides an 11-bit displacement. 1. displacement are aligned as shown in Figure 2-14 when indexed addressing is performed.

The displacement is aligned so that bit 31 corresponds to base or index bit 15 and displacement bit 21 corresponds to base or index bit 5. displacement is expanded to 16 bits by appending five leading zeros.

If B2 is not equal to 11, the 16-bit base, contained in the higher order half of the specified register, is added to the aligned displacement. 2. This results in a preliminary effective address (PEA) whereby the PEA = (B) + Displacement.

If B2 is equal to 11, the aligned displacement is added to zero. result is the preliminary effactive address (PEA) whereby the PEA=Displacement.

- If the X field is all zeros, IA (bit 19) is a zero and I (bit 20) is a zero, then the 16-bit result of Step 2 is added to the contents of the 3. updated instruction counter (IC) to form the 16-bit EA whereby EA=(updated) IC + PEA. (This EA is then expanded to a 19-bit EA, as explained in the Expanded Addressing section, with the exception that the Branch Sector Register (BSR) bits are used instead of the Data Sector Register (DSR bits).

- 'If the X field is all zeros, IA (bit 19) is a zero and I (bit 20) is a one, the 16-bit result of Step 2 is subtracted from the contents of the updated IC to form the 16-bit EA whereby EA = (updated) IC - PEA. (This

The second second second

C

Figure 2-13. Automatic Index Alignment

90035 038

Figure 2-14. Displacement Alignment for Indexed Addressing

EA is then expanded to a 19-bit EA, as explained in the Expanded Addressing section with the exception that the Branch Sector Register (BSR) bits are used instead of the Data Sector Register (DSR) bits.)

5. If the X field is all zeros, IA (bit 19) is a one and I (bit 20) is a zero, then Indirect Addressing is performed. The 16-bit result of Step 2 is expanded to a 19-bit address and is used as the address of a main storage halfword. This halfword is then fetched and expanded to 19 bits by using expanded addressing to form the EA. EA=MS (PEA). Functional equivalency to preindexing capability can be obtained through modification of the base.

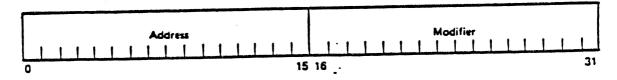

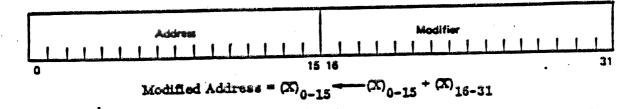

6. If the X field is all zeros, IA (bit 19) is a one and I (bit 20) is a one, Indirect Addressing is performed as described in Step 5 with a fullword main storage pointer. Then, after the EA has been formed, storage modification is automatically performed. The indirect address is contained in a fullword. A modifier is contained in bits 16 through 31. An address is contained in bits 0 through 15. The modifier is added to the address and the resulting modified address replaces bits 0 through 15 of the indirect address word (see Figure 2-15).

Modified Address = MS (PEA) - MS (PEA) + MS (PEA + 1)

Figure 2-15. The Contents of Indirect Address Storage Modification Word

7. If the X field is not zeros, IA (bit 19) is a zero and I (bit 20) is a zero, the most significant 16 bits of the general register specified by the X field are aligned, and then added to the 16-bit result of Step 2 (PEA) to form the 16-bit EA (See Figure 2-13). (This EA is then expanded to a 19-bit EA, as explained in the Expanded Addressing section.)

TEPT

• If the X field is not all zeros, IA (bit 19) is a zero and I (bit 20) is a one, the most significant 16 bits of the general register specified by the X field are aligned, and then added to the 16-bit result of Step 2 (PEA) to form the 16-bit EA (see Figure 2-13). (This EA is then expanded to a 19-bit EA, as explained in the Expanded Addressing section.) (The modifier is added to the address and the resulting modified address replaces bits 0 through 15 of the index register after the EA is determined.) Figure 2-16 illustrates the address and modifier format in the index register.

- 9. If the X field is not all zeros, IA (bit 19) is a one and I (bit 20) is a zero, Indirect Addressing (IA) with postindexing is performed. The 16-bit result of Step 2 is expanded to a 19-bit address and is used to fetch a main storage halfword. The index contained in the general register specified by X is aligned and then added to the fatched halfword to form the 16-bit EA (see Figure 2-13). This EA is then expanded to a 19-bit EA by using expanded addressing. Functional equivalency to preindexing capability can be obtained through modification of the base.

- 10. If the X field is not all zeros, IA (bit 19) is a one and I (bit 20) is a one, an indirect addressing mode is defined using a 32-bit fullword indirect address pointer as follows:

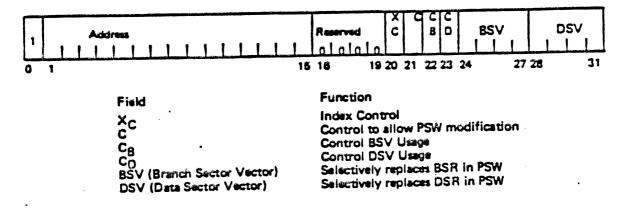

- a. First, the PEA from Step 2 must locate a fullword indirect address pointer, with the format as illustrated in Figure 2-17.

### Figure 2-17. Fullword Indirect Address Pointer

2-14

If C (bit 21) equals 0, XC (bit 20) equals 1, and the instruction is not a branch type instruction, the 19-bit EA equals the 4-bit DSV with the 15-bit address field appended. When C (bit 21) equals 0, XC (bit 20) equals 0, and the instruction is not a branch type instruction, the 19-bit EA equals the 15-bit address field added to the index value in indexing-register X with the result appended to the DSV. The current PSW's DSR is not changed.

If C (bit 21) equals 0 and the instruction is a branch type instruction, the current PSW's BSR in conjunction with bits 0 through 15 of the fullword indirect address pointer will be used to form the branch address (BA). If XC=0, postindexing will occur. When C (bit 21) equals zero, CB and CD are reserved and should be set to zero.

c. If C (bit 21) equals 1 and the instruction is a branch type instruction and the branch is taken, the BSV and DSV fields selectively replace the BSR and DSR fields in the current PSW, based on the CB and CD bit values as follows:

| CB | CD | Result                                                                                                                           |

|----|----|----------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0  | Use current PSW's BSR form the BA.                                                                                               |

| 0  | 1  | Replace the current PSW's DSR with the DSV. Form the BA normally.                                                                |

| 1  | 0  | Replace the current PSW's BSR with the<br>BSV before forming the BA.                                                             |

| 1  | 1  | First, replace the current PSW's DSR with<br>the DSV. Then, replace the current PSW's<br>BSR with the BSV before forming the BA. |

d. When C (bit 21) equals 1 and XC (bit 20) equals 1, postindexing is not performed. When C (bit 21) equals 1 and XC (bit 20) equals 0, the BA calculation includes a final addition of the index value in index registers X.

If C (bit 21) equals 1, XC equals 1, and the instruction is not a branch, the 19-bit EA equals. the current PSW's DSR and the 15-bit field appended. If XC=0, postindexing will occur.

The results of indexed mode RS operations normally replace the first operand except for store operation where the first operand replaces the second operand. The second operand is unaltered for nonstore operations, and the first operand is unaltered for store operation.

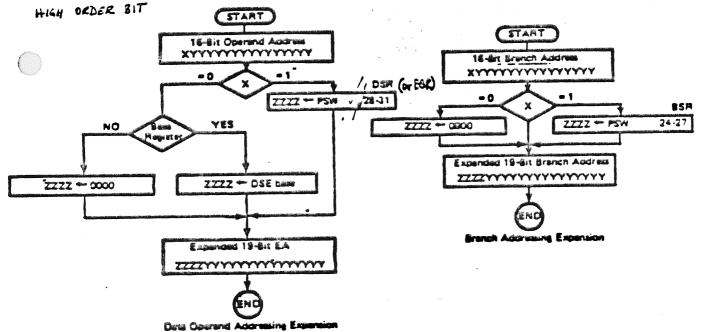

#### 2.2.9 Expanded Addressing

ь.

The addressing philosophy accommodates 64K halfword addresses since a full 16-bit address is provided. Extending the addressing range beyond 64K halfword locations

ANE REAL PROPERTY

Note: I'C relative data ofther & councils

¢

t 1

ころ シブ フシーシ

um to 512K halfword locations is provided by utilizing PSW bits and Data Sector Ext( ion (DSE) registers.