# <u>PART III</u>

# Space Shuttle Advanced System/4 Pi Input/Output Processor (IOP)

Principles of Operation for the Bus Control Element

Prepared for

Rockwell International Corporation Space Division 12214 Lakewood Blvd. Downey, CA 90241

26 April 1976

Under Purchase Order No. MAJ7XMA-483019

IBM No. 6246556A

Federal Systems Division, Owego, New York 13827

FOR RESEARCH USE ONLY THIS MATERIAL MAY BE PROTECTED BY COPYRIGHT LAW (TITLE 17 U.S. CODE). COPY PROVIDED BY WICHITA STATE UNIVERSITY LIBRARIES SPECIAL COLLECTIONS SPECIAL COLLECTIONS MITHOUT WRITTEN PERMISSION THIS MATERIAL MAY NOT BE COPIED OF

Dr. James E. Tomayko Collection of NASA Documents Wichita State University Libraries, Special Collections and University Archives

SM

87-08

Box

L J

뀨

# BCE POO

# 6246556A

# TABLE OF CONTENTS

- Section

- FOR RESEARCH USE ONLY THIS MATERIAL MAY BE PROTECTED BY COPYRIGHT LAW (TITLE 17 U.S. CODE). COPY PROVIDED BY WICHITA STATE UNIVERSITY LIBRARIES SPECIAL COLLECTIONS SPECIAL COLLECTIONS MITHOUT WRITTEN PERMISSION THIS MATERIAL MAY PREDICT OF MATERIAL MATERIAL MAY PREDICT OF MATERIAL MAY PREDICT OF MATERIAL MAY PREDICT OF MATERIAL MAY PREDICT OF MATERIAL MATERIAL MATERIAL MATERIAL MAY PREDICT OF MATERIAL  $\begin{array}{c} 1.0\\ 1.1\\ 1.1.2\\ 1.2.1\\ 1.2.2\\ 1.2.2\\ 1.2.2\\ 2.3.3\\ 2.12\\ 2.3.3\\ 2.3.3\\ 3.3.3\\ 3.3.3\\ 3.3.3\\ 3.3.3\\ 3.3.4\\ 4.2\\ 3.4.4\\ 4.5\\ 3.4.4\\ 3.5\\ 3.4.4\\ 4.5\\ 3.4.4\\ 4.2\\ 4.3\\ \end{array}$

|    |                                         | Page     |

|----|-----------------------------------------|----------|

|    | BUS CONTROL ELEMENT                     | 1        |

|    | FORMATSBUS FORMATS                      | 4        |

|    | BUS FURMAIS                             | 4        |

| 9. | ADDRESSING AND INSTRUCTION FORMATS      | 7        |

|    | BCE REGISTERS                           | 12       |

|    | BCE PROGRAMMABLE REGISTER               | 12       |

|    | BCE STATUS REGISTERS                    | 13       |

|    | BCE IMPLEMENTATION                      | 17       |

|    | GENERAL BCE OPERATION                   | 19       |

|    | WAIT STATE                              | 19       |

|    | BUSY STATE                              | 22       |

|    | BUSY STATE OPERATING MODES              | 23       |

|    |                                         | 24       |

|    | SUMMARY OF ERROR MODESBCE INSTRUCTIONS  | 24       |

|    | BCE REGISTER INSTRUCTIONS               | 28       |

|    | BCE BRANCHING                           | 29       |

|    | BCE TRANSMISSION INSTRUCTIONS           | 36       |

|    | TRANSMIT COMMAND INSTRUCTIONS           | 42       |

|    | TRANSMIT DATA INSTRUCTIONS              | 42       |

|    | TYPICAL BUS TIMING-GAPS BETWEEN OUTPUTS | 42       |

|    | ЕСНО ВАСК                               | 43       |

|    | ERROR MODES-DISABLED MIA                | 44<br>47 |

|    | ERROR MODES-EXCESSIVE CONCURRENCY       | 47       |

|    | BCE RECEIVE DATA INSTRUCTIONS           | 58       |

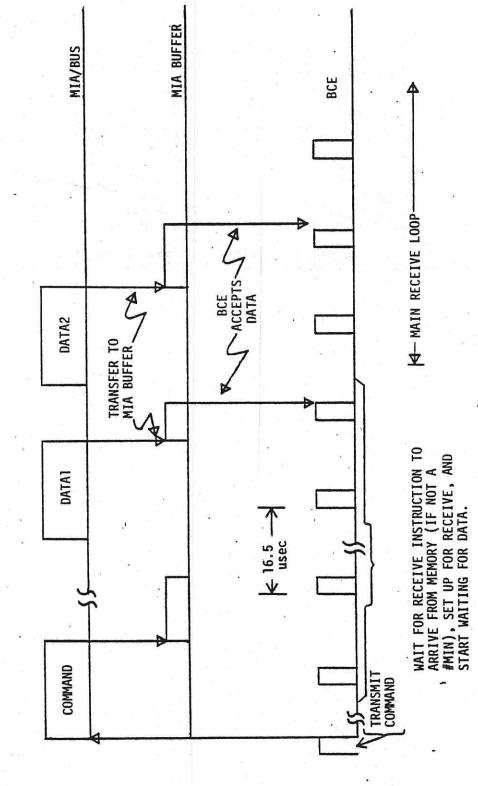

|    | MIA-MIA BUFFER-BCE OPERATION            | 58       |

|    | RECEIVE DATA SETUP                      | 65       |

|    | ACCEPTANCE OF FIRST INPUT               | 66       |

|    | ERROR CHECKS                            | 68       |

|    | HANDLING OF GOOD INPUTS                 | 68       |

|    | ERROR TERMINATION-FAULTY INPUT          | 69       |

|    | ERROR TERMINATION-TIME OUT              | 69       |

|    | RECEPTION OF INTERMEDIATE WORDS         | 70       |

|    | SPECIAL INSTRUCTIONS                    | 77       |

|    | LISTEN MODE                             | 81       |

|    | SAMPLE OPERATION IN LISTEN MODE         | 81       |

|    | INITIALIZATION INTO LISTEN MODE         | 85       |

|    | DIFFERENCES IN INSTRUCTION EXECUTION    | 85       |

|    |                                         |          |

# Appendix A

| IOP | BCE | INSTRUCTION | REPERTOIRE | 88 |

|-----|-----|-------------|------------|----|

|-----|-----|-------------|------------|----|

Dr. James E. Tomayko Collection of NASA Documents Wichita State University Libraries, Special Collections and University Archives SW 87-08 Box 42 П 50

ij

BCE POQ

(D)

# LIST OF FIGURES

|                                                                    | Figure |                                      | Page |

|--------------------------------------------------------------------|--------|--------------------------------------|------|

| 9)                                                                 | 1.1    | BUS Message Formats                  | 6    |

| WIT                                                                | 1.2    | BCE-Computed Main Memory Addresses   | 8    |

| REAL                                                               | 1,3    | Basic BCE Short Instructions Formats | 8    |

| PH PH                                                              | 1.4    | BCE Instructions-Long Formats        | 9    |

|                                                                    | 1.5    | BCE Local Store Usage                | 18   |

| INVERTITIE CORDECTED                                               | 2.1    | BCE States                           | 21   |

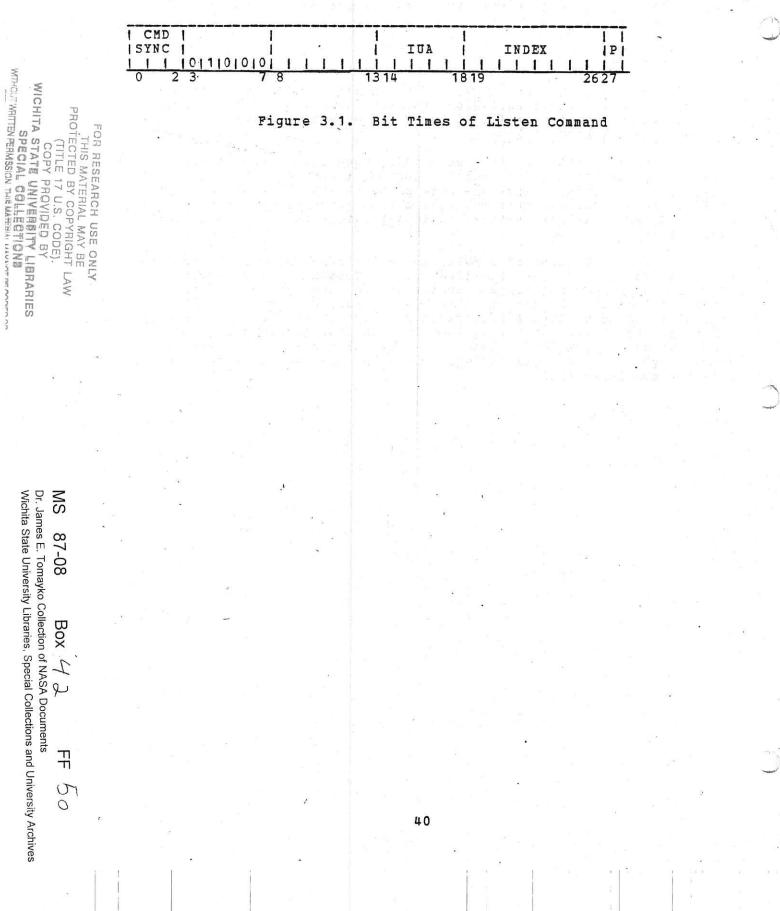

| AL DAL                                                             | 3.1    | Bit Times of Listen Command          | 40   |

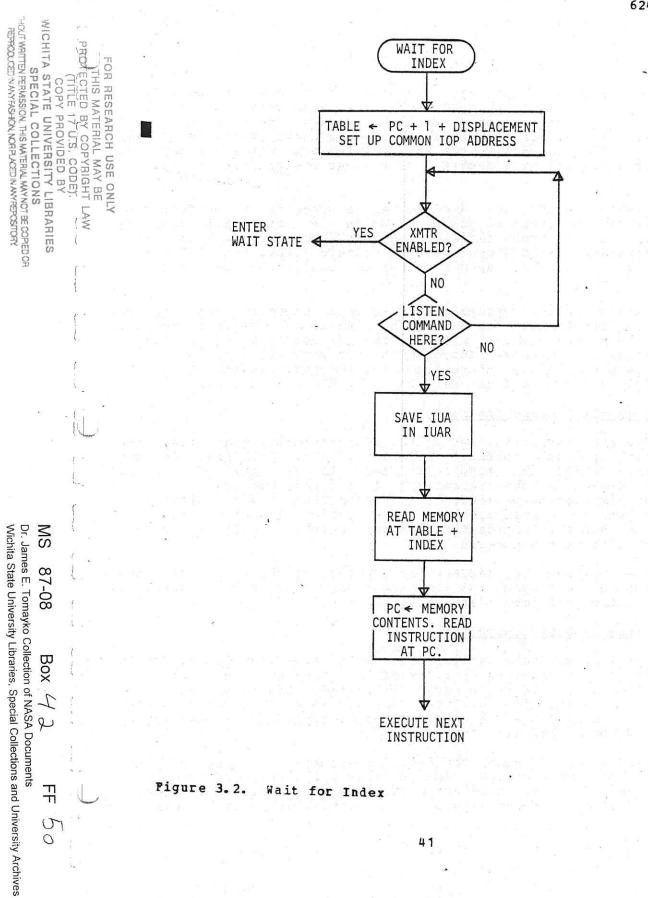

| ARC<br>ARC<br>ARC<br>ARC<br>ARC<br>ARC<br>ARC<br>ARC<br>ARC<br>ARC | 3.2    | Wait For Index                       | 41   |

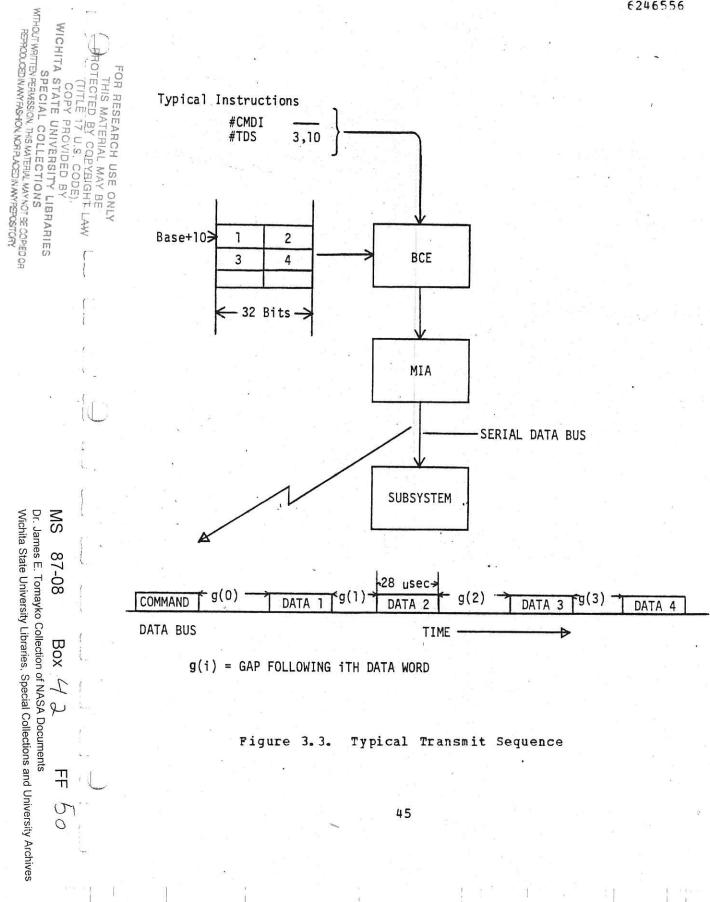

| ANDERS OPLAL                                                       | 3.3    | Typical Transmit Sequence            | 45   |

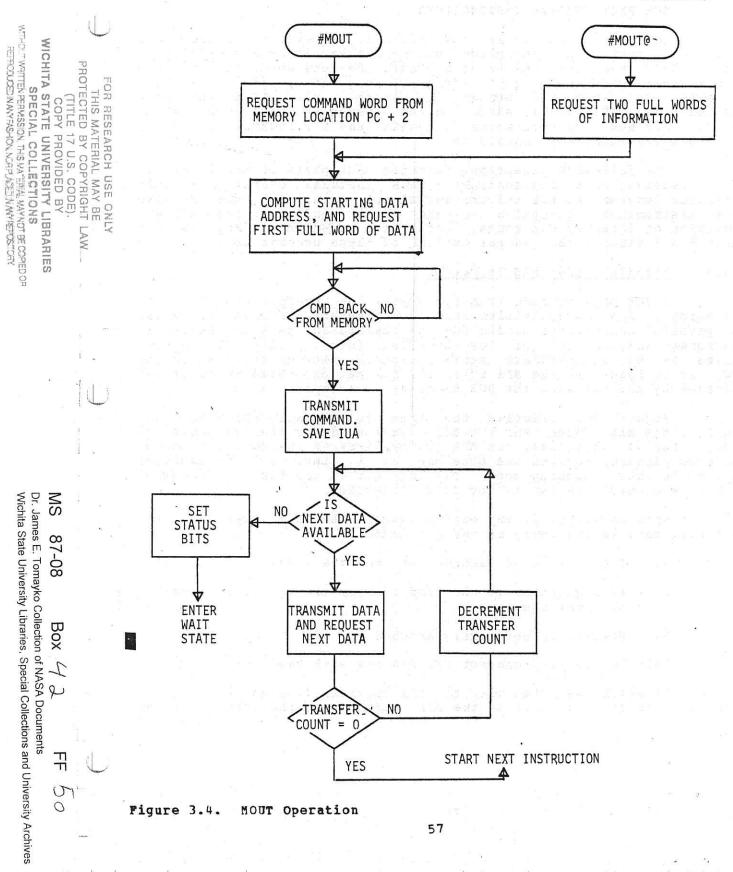

| 回避 AMAY                                                            | 3.4    | MOUT Operation                       | 57   |

| AAVNO                                                              | 3.5    | MIA-MIA-Buffer-BCE Operation         | 60   |

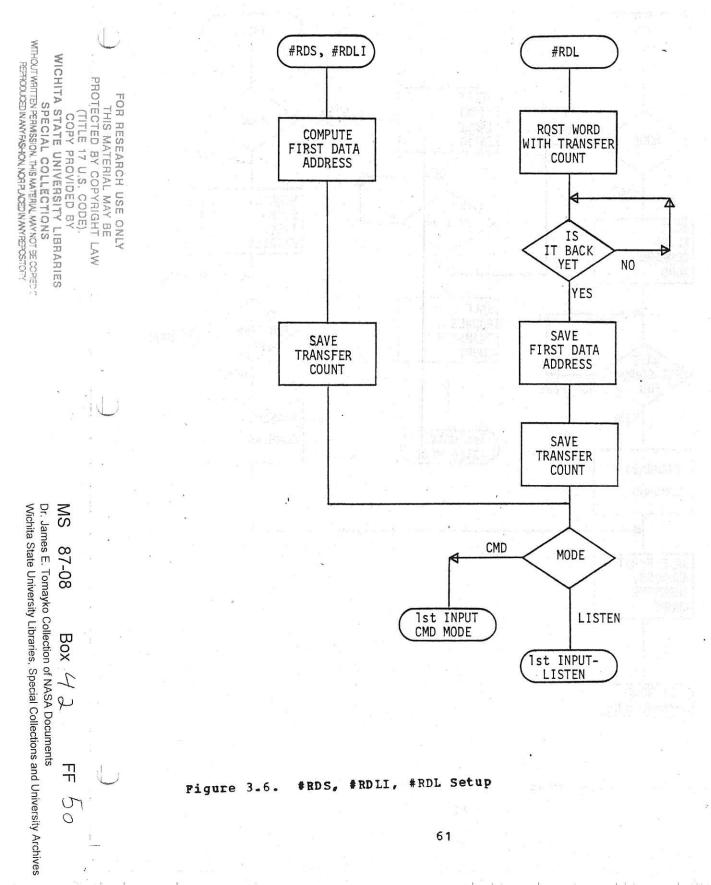

| LAW<br>LAW                                                         | 3.6    | <pre>#RDS, #RDLI, #RDL Setup</pre>   | 61   |

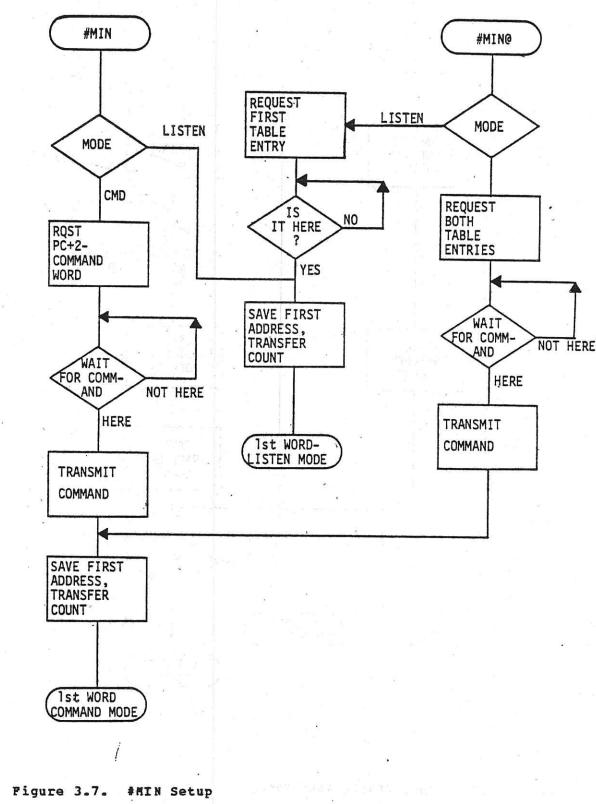

| RIES .                                                             | 3.7    | #MIN Setup                           | 62   |

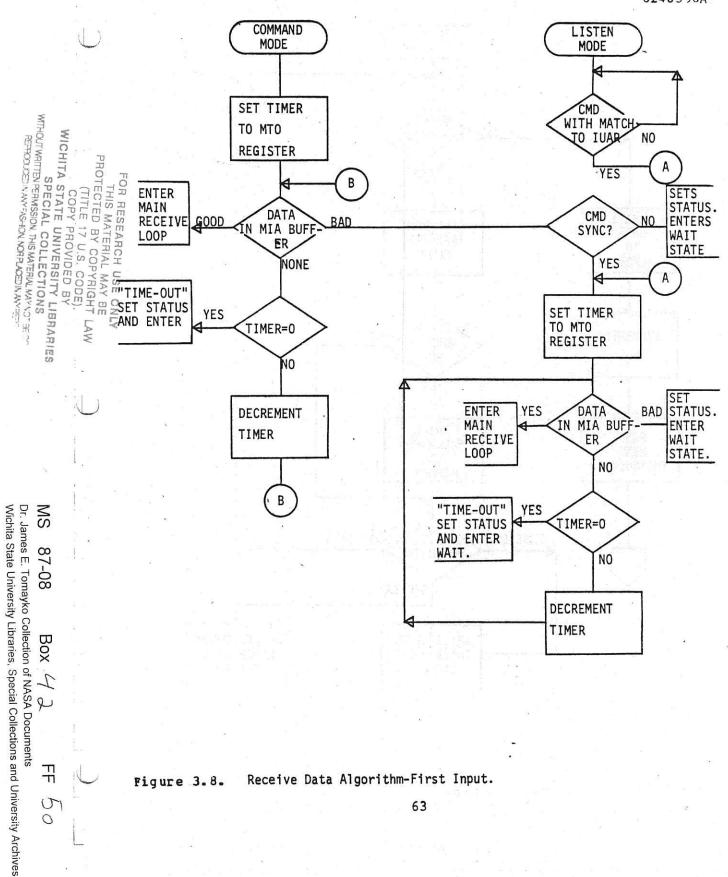

| OP .                                                               | 3.8    | Receive Data Algorithm-First Input   | 63   |

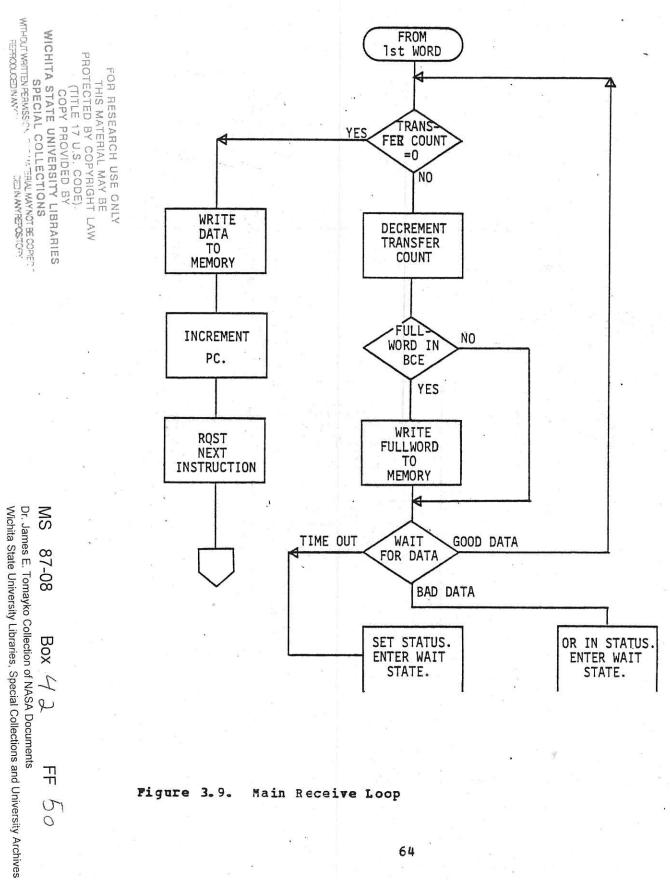

| · ( )                                                              | 3.9    | Main Receive Loop                    | 64   |

|                                                                    | 4.1    | Listen Mode Configuration            | 83   |

|                                                                    |        |                                      |      |

Dr. James E. Tomayko Collection of NASA Documents Wichita State University Libraries, Special Collections and University Archives MS 87-08 Box 42 П 0

# LIST OF TABLES

# Table

# Page

| 1.1 | BCE Characteristics                                   | 3  |

|-----|-------------------------------------------------------|----|

| 1.2 | BCE Status Register                                   | 14 |

| 2.1 | Summary of BCE-Related Errors                         | 25 |

| 3.1 | Typical Gaps Between Command and Data Word            | 46 |

| 3.2 | Time To First Look At Data                            | 67 |

| 4.1 | Differences in Instruction Executions Due to BCE Mode | 87 |

Dr. James E. Tomayko Collection of NASA Documents Wichita State University Libraries, Special Collections and University Archives SW 87-08 Box 42 0

FOR RESEARCH USE ONLY THIS MATERIAL MAY BE PROTECTED BY COPYRIGHT LAW (TITLE 17 U.S. CODE). COPY PROVIDED BY WICHITA STATE UNIVERSITY LIBRARIES SPECIAL COLLECTIONS SPECIAL COLLECTIONS MITHOUT WATTER DERMASSION THIS MATERIAL MAY PERSON THE PREMOVICED IN ANY PROVINCE ACED IN ANY PERSON OF

### BUS CONTROL ELEMENT

The Bus Control Element (BCE) is a microprogrammed controller specifically tailored for management of I/O traffic on one of the Shuttle system busses. Within each IOP there is one BCE for Space each system bus, for a total of 24 BCE's. Each of these BCE's is independent program execution, data buffering to and from capable of memory, and communication with the MSC. Further, each BCE is connected to its own bus via its own Multiplexer Interface Adapter (MIA), which performs all parallel to serial and serial to parallel conversions. Table 1.1 summarizes the basic characteristics of a BCE.

- The major purpose of a BCE is threefold:

- (1)Initiate transmission of commands to subsystems on the bus.

- (2)Handle data coming back from a commanded subsystem.

- (3) Fetch data to be sent to a commanded subsystem.

To handle these tasks there are two classes of instructions (transmit and receive), and two special operating modes (Command, and Listen ) that are unique to the BCE.

The transmit instructions allow transmission of both commands and data to a subsystem. When transmitting data a BCE/MIA pair performs:

- (1) Update of main memory buffer addresses.

- (2)Conversion between 32 bit main memory data format and 25 + Sync bit bus data format.

- (3) Check on number of words to be transferred.

The receive commands allow a BCE to accept a stream of input data from a subsystem through its MIA. When receiving data a BCE performs:

- (1) Time outs on data arrival.

- (2)Error checks on incoming data.

- (3) Assembly into main memory 32 bit data format.

- (4)Maintenance of main memory buffer addresses.

1

- (5) Transferral of data to main memory.

- Check on number of words to be received. (6)

THIS MATERIAL PROTECTED BY COP (TITLE 17 U.S.

D BY COPYRIGHT L E 17 U.S. CODEN

LAW

COPY PROVIDED

THIS

RESEARCH

USE

ONLY

WICHITA STATE UNIVERSITY LIBRARIES , SPECIAL COLLECTIONS WITHOUT WAITTEN PERMASSION, THIS MATERIAL MAY NOT BE COPIED OF REPROCUCED IN MAY HIGH YOU, NOR PLACED IN MAY REPORT FOR

Wichita State University Libraries, Special Collections and University Archives

Dr. James E. Tomayko Collection of NASA Documents

SW

87-08

Box

2

2

T U

0

1.0

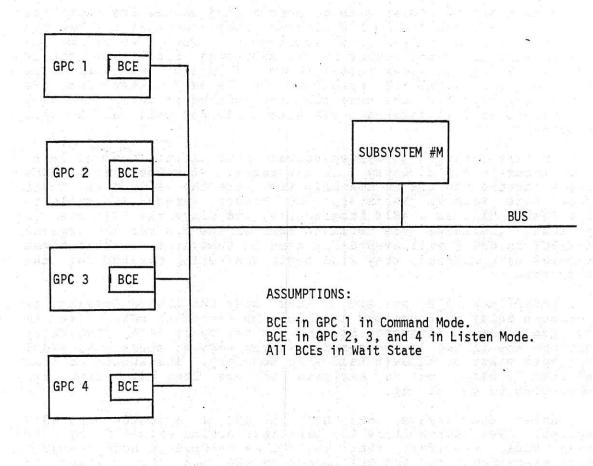

The two operating modes that a BCE may be in influence the BCE way the uses its bus. In Command mode, a BCE is master of its bus, and is free to transmit both commands and data. This allows a BCE to command a subsystem, receive data from it, or transmit data to it. In Listen mode a BCE monitors its bus for directions on how to handle any data that might appear on the bus. In this mode a BCE may only receive data, and may not transmit either commands or data. This handles the common situation in the Space Shuttle where several IOP's several BCE's and thus may be connected to one bus. In such a situation only one BCE is allowed to issue subsystem commands, but all BCE's on that bus wish to receive copies of the resulting data. The listening mode allows the command BCE to tell the others what data to expect, and when to expect it.

FOR RESEARCH USE ONLY THIS MATERIAL MAY BE PROTECTED BY COPYRIGHT LAW (TITLE 17 U.S. CODE). COPY PROVIDED BY WICHITA STATE UNIVERSITY LIBRARIES SPECIAL COLLECTIONS BPECIAL COLLECTIONS MTHOUTWRITTEN MERNSION, THIS MATERIAL MAY NEW SETTORY

Dr. James E. Tomayko Collection of NASA Documents Wichita State University Libraries, Special Collections and University Archives SW 87-08 Box 4 R П 00

### TABLE 1.1

### BCE CHARACTERISTICS

FOR RESEARCH USE THIS MATERIAL MAY BE PROTECTED BY COPYRIGHT L (TITLE 17 U.S. CODE). CONV PROVIDED BY Type -- Programmable I/O traffic controller Number -- One per bus, 24 BCE's per IOP Control Structure -- Microprogrammed Programmable Registers (per BCE) 18 Bit Base Register (BASE) 18 Bit Program Counter (PC) 18 Bit Maximum Time Out Register (MTO) 5 Bit Interface Unit Address Register (IUAR) 1 Bit BCE/MSC Indicator Bit ONLY Other BCE Registers (per BCE) 32 Bit Status Register Bit Program Exception Register (part of STAT 1) 1 1 Bit Busy/Wait Bit (part of STAT 4) 1 Bit MIA Transmitter Enable 1 Bit MIA Receiver Enable 6 Bit Identify Register Instruction Formats : 16 Bit Short/32 Bit Long/ 64 Bit Extended Instruction Repertoire: 10 Short/5 Long/ 2 Extended Addressing Space: 131,072 32 Bit Fullwords/262,144 16 Bit Halfwords Addressing Modes:, Immediate, PC relative, Base relative, Absolute Special Operating Modes: Command, Listen

3

Bus Data Format: 25 + Sync Bit serial

WITHOUT WRITTEN PERMISSION, THIS MATERIAL MAY NOT BE COPED S-RIDPRODUCED IN ANY FASHION, MOR PLACED IN MAY REPOSITORY WICHITA STATE UNIVERSITY LIBRARIES SPECIAL COLLECTIONS

Wichita State University Libraries, Special Collections and University Archives

Dr. James E. Tomayko Collection of NASA Documents

SM

87-08

Box

1 Q

뀨

5

0

LAW

#### 1.1 FORMATS

MITHOUT WRITTEN PERMISSION THIS WATER ALL COLLECTIONS REPRODUCED IN MATERIAL AND ALL COLLECTIONS

Wichita State University Libraries, Special Collections and University Archives

Dr. James E. Tomayko Collection of NASA Documents

$\leq$ 5

87

-08

ω ŠX

L

2

Π U 0

NCHITA

SPECIAL

COPY

PROVIDED

DE

LAW

PROT

HL.

FOR RESEARCH USE ONL THIS MATERIAL MAY BE DTECTED BY COPYRIGHT L (TITLE 17 U.S. CODE)

#### 1.1.1 Bus Formats

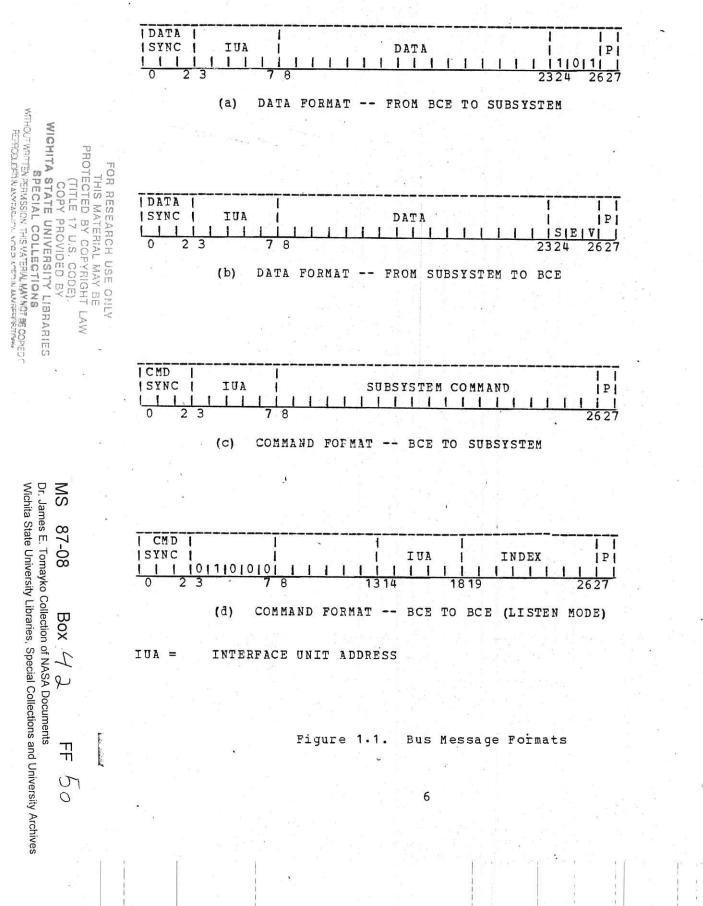

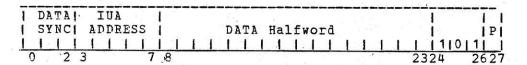

There are four basic formats for data or commands carried system bus in serial form. These are pictured in Figure 1.1. over a They are all 28 bits long, with 3 bit times for sync, 24 bits of information, and 1 bit for word parity. These 28 bits are transmitted at a serial rate of 1 bit per microsecond.

On transmission from an IOP to a subsystem, a BCE provides the middle 24 bits of information and an indication of the type of sync to use -- either command or data sync. Command sync is used when the 24 bits of information are to be treated as a command to be obeyed by some subsystem. Data sync is used when a BCE has previously conditioned a device, via a command, to accept a stream of data, and the word being put on the bus is a member of this stream.

Conversely, there are situations where a BCE may accept, through its MIA, words with either command or data sync. In such cases the MIA simply provides the type of sync that a word had, the 24 bits of information present in the word, and appropriate error signals. sync is recognized when a BCE is in the "Listening Mode" and Command is expecting a command from another BCE connected to the same bus. Data sync is accepted when a BCE is expecting to receive a stream of data from a subsystem on the bus. This subsystem was previously commanded to send this data by a message with command sync from some BCE on the bus.

The contents of the 24 bits of information in a bus word depends both on the sync type and the direction of transfer -- from a BCE or to a BCE. In all cases the upper 5 bits contain an interface (IUA) . When used in data words unit address or commands to subsystems, these 5 bits identify the subsystem on the bus who either originated the data or is to accept the command or data. In Listen Mode commands, the BCE in one IOP sends to all other BCE's in the IOP's connected to this bus a command that has a "Common IOP other This special pattern is not used by any subsystem. address". and a listening BCE to distinguish between listen commands and allows commands to subsystems.

In data transfers the remaining 19 bits consist of 16 bits of data (one half of a standard 32 bit main memory fullword) and 3 .bits nominally containing the pattern 101. In BCE to subsystem data transfers, this pattern never changes. However, in subsystem to BCE transfers, any variation in the 101 pattern indicates to the BCE data that the sending subsystem has encountered a problem, such as power surge, invalid commands, etc.

In commands sent by a BCE to a subsystem, the format of the lower 19 bits of information is subsystem dependent, and not discussed further here.

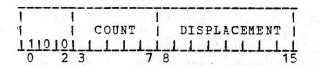

In Listen Mode commands sent from one IOP to another, the 18 bits of the information contain a 5 bit number representing a terminal or subsystem on the BCE's bus and an 8 bit index into a table of BCE branch addresses.

COPY PROVIDED BY WICHITA STATE UNIVERSITY LIBRARIE SPECIAL COLLECTIONS MITHOUT WRITTEN PERMISSION THIS MATERIAL WAY NOT BE COPIE PERPODUCED IN MY FASHER WATER AGED IN ANY TOTAL . Dr. James E. Tomayko Collection of NASA Documents Wichita State University Libraries, Special Collections and University Archives SM 87-08 Box 4 ۶. T 50

FOR RESEARCH USE ONLY THIS MATERIAL MAY BE PROTECTED BY COPYRIGHT LAW (TITLE 17 U.S. CODE).

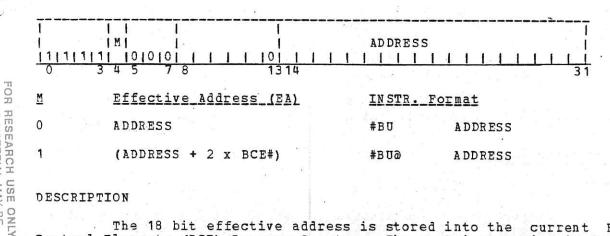

#### 1.1.2 Addressing and Instruction Formats

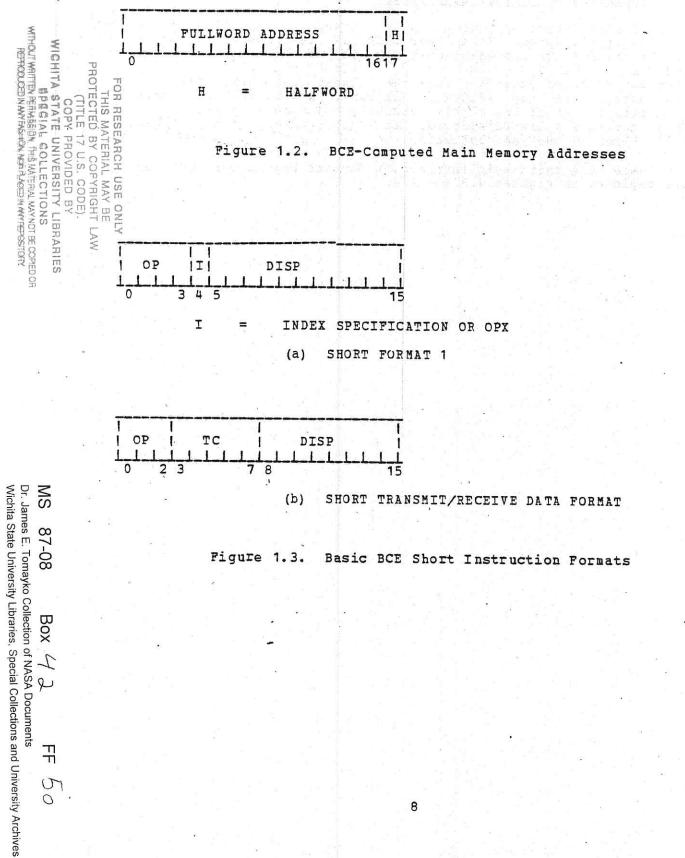

A BCE may directly address up to 262,132 16-bit halfwords or 32-bit fullwords. To achieve this, all main memory addresses 131,071 computed by the BCE are represented as 18-bit absolute numbers, as pictured in Figure 1.2. The upper 17-bits (bits 0 through 16) represent the fullword location, and the lowest halfword portion of the addressed fullword. A (bit bit 17) the A 0 in this lower bit refers to bits 0 - 15 of the 32-bit fullword; a 1 refers to bits 16 -When used as a fullword address, bit 17 is ignored. 31. Thus, H'276' and H'277' refer to the same fullword.

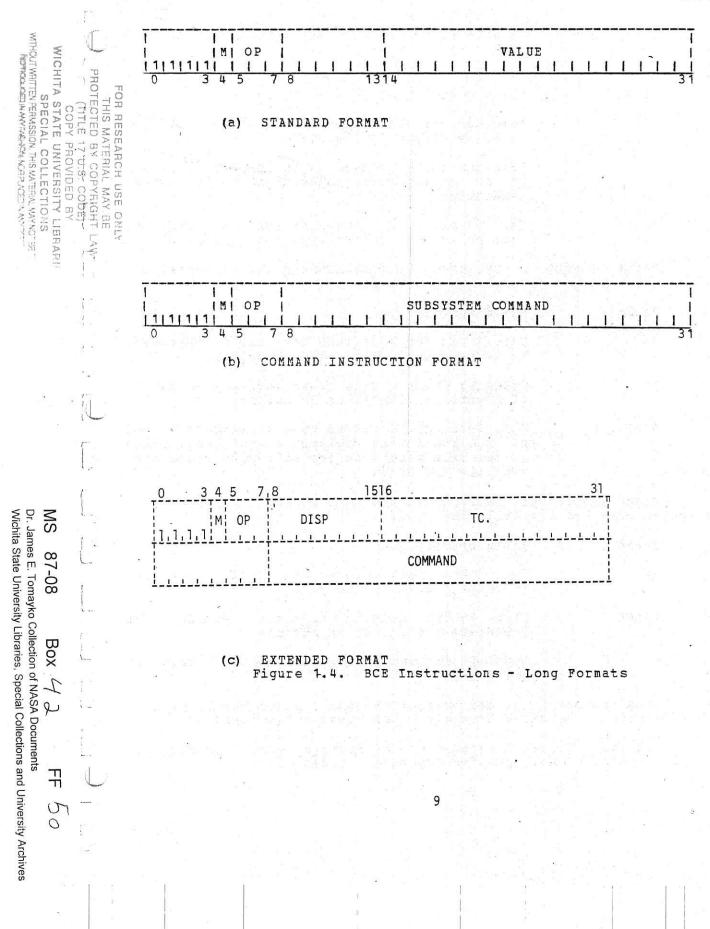

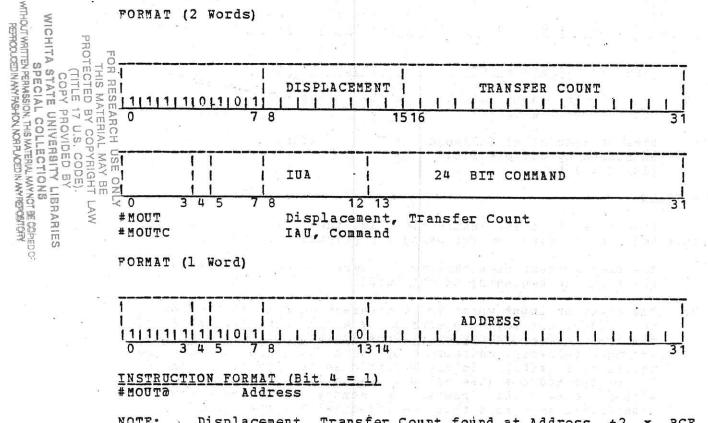

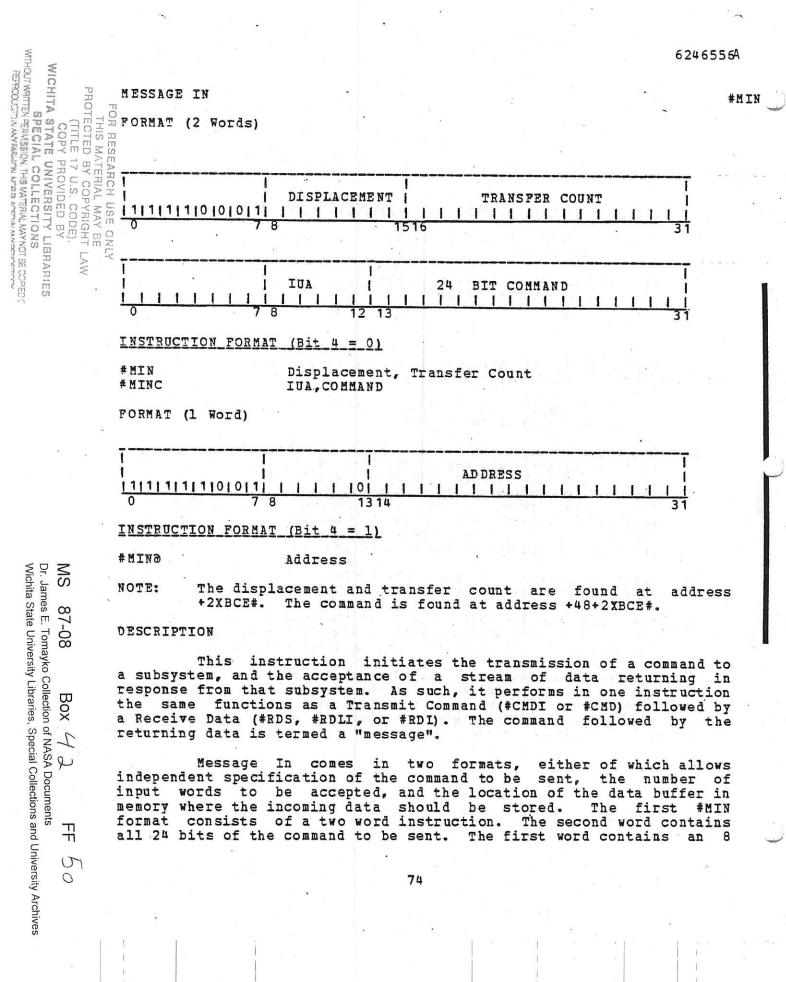

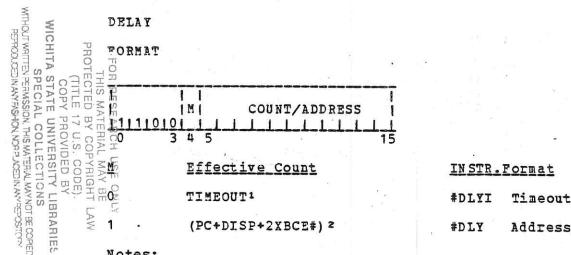

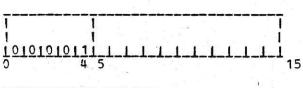

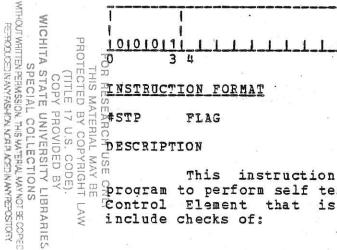

There are four basic instruction formats used by the BCE and they are depicted in Figures 1.3 and 1.4.

1 Q

> Т T

U 0 FOR RESEARCH USE ONLY

LAW ١...,

1

Short format 1 is used primarily by instructions dealing with the BCE register. It has the following fields:

| WIHO                                                                                   |                          | Field                              | Field Description                                                                                                                                                      |

|----------------------------------------------------------------------------------------|--------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                        | FOR<br>TH<br>PROTE:      | OP                                 | This 4-bit field defines the basic operation to be performed by the BCE.                                                                                               |

| COPY PRO<br>STATE UNISTATE UNISTATE UNISTATE UNISTICAL CO                              | OR RESEARC<br>THIS MATER | I                                  | This bit serves either as an opcode extension<br>or as an index mode specification in address<br>generation.                                                           |

| VIDED B<br>VIDED B<br>VERSITY<br>LLECTIO                                               | COPYRIC                  | DISP                               | This 11-bit field serves either as immediate<br>data or as a PC relative address displacement.                                                                         |

| T).                                                                                    | HT Y receive             | Short format<br>data. It has t     | 2 is used by instructions that transmit and the following fields:                                                                                                      |

| ARIES<br>COPIED OP                                                                     |                          | Field                              | Field Description                                                                                                                                                      |

| O.B.                                                                                   |                          | OP                                 | This 3-bit field defines the basic operation to be performed (data read or write).                                                                                     |

| ία.<br>La                                                                              |                          | TC                                 | Transfer Count. This field defines the number<br>of inputs or outputs to be handled.                                                                                   |

|                                                                                        |                          | DISP                               | This 8-bit field serves as a displacement off<br>of the BCE's base register in the computation<br>of the main memory buffer addresses associated<br>with the I/O data. |

| MS 87.<br>Dr. James E.<br>Wichita State                                                | Long for                 | most long form<br>rmat provides th | at instructions use long format 1 (Figure 1.4).<br>e following fields:                                                                                                 |

| mes<br>Ia Sta                                                                          | 200 - 10<br>10<br>10     | Field                              | Field Description                                                                                                                                                      |

| 7-08<br>E. Toma<br>ate Unive                                                           |                          | OP                                 | This 3-bit field defines the basic operation to be performed by the BCE.                                                                                               |

| MS 87-08 Box<br>Dr. James E. Tomayko Collection<br>Wichita State University Libraries. |                          | VALUE                              | This 18-bit address is used either for immediate data or as an address.                                                                                                |

| - <u>-</u>                                                                             |                          | M                                  | This bit influences how the Value field is used.                                                                                                                       |

| H J FF 50<br>of NASA Documents<br>Special Collections and University Archives          | proviđe                  | Long format 2<br>24 bits to be g   | is used by the Transmit Command instruction to<br>iven to the MIA for command transmission.                                                                            |

| F<br>cuments<br>ections a                                                              | to speci                 | Extended form                      | at 3 is used by the Message In/Out instructions<br>, Transfer Counts and Commands.                                                                                     |

|                                                                                        |                          |                                    | 승규는 승규는 방송을 가지 않는 것이 없는 것이 없다.                                                                                                                                         |

| 5 o                                                                                    |                          |                                    | 그렇는 방법은 것을 가지 않는 것이라. 그 것들 것이다.                                                                                                                                        |

| )<br>ity Ar                                                                            |                          |                                    | 10                                                                                                                                                                     |

| chives                                                                                 |                          |                                    | 이 같은 것 이상에서 이 것에 있는 것이 가격하는 것 같아요. 이상에 있는 것이 같아.<br>그 같은 것이 같아요. 이상에 있는 것이가 가격하는 것이 있는 것이 같아. 이상에 있는 것이 같아.                                                            |

| 0                                                                                      | a 22 bit interface       |                                    |                                                                                                                                                                        |

In many BCE instructions the direct addressing mode includes automatic indexing by twice the BCE's number. This allows BCE programs to be written in a table driven fashion, where the same BCE program can be used by many different BCE's, and yet each BCE will use a separate set of parameters in the programs execution.

WICHITA STATE UNIVERSITY LIBRARIES

Dr. James E. Tomayko Collection of NASA Documents Wichita State University Libraries, Special Collections and University Archives

SW

87-08

Box

4 J

뀨

00

FOR RESEARCH USE ONLY THIS MATERIAL MAY BE PROTECTED BY COPYRIGHT LAW (TITLE 17 U.S. CODE).

BCE REGISTERS 1.2

WICHITA

ABTATE

COLLECTIONS THIS MATERIAL WAY NOT BE

WAYNOT BE LIBRARI

YOPY

A DHOVIDED BY

177

SW

87-08

ω

ŠX

1

Q

뀨

U 0

Dr. James E. Tomayko Collection of NASA Documents

Wichita State University Libraries, Special Collections and University Archives

DED E

ROT

THIS MATERIAL THIS MATERIAL TECTED BY CC TITLE 17 U.S

PEPRODUCED IN NIV PARTON

#### 1.2.1 BCE Programmable Register

Each BCE contains several registers under direct program control. They are:

> BASE --An 18-bit Base Register PC --An 18-bit Program Counter MTO --An 18-bit Maximum Time Out Register IUAR --A 5-bit Interface Unit Address Register Indicator --A 1-bit indicator bit in the BCE/MSC Indicator Register.

S. CON The BASE is used in locating I/O buffers in main memory. A11 such buffers are base-relative, allowing the same BCE program to be with different buffers by simply changing the Base before used entering the common program segment.

The Program Counter is an 18-bit register indicating the main memory halfword or fullword location of the BCE instruction being It should be emphasized that there is a executed by this BCE. separate PC for each BCE, and that the contents of one PC need not have any relation to the contents of a different PC in another BCE.

The Maximum Time Out Register is used primarily during the reception of data to indicate the maximum time a BCE should wait for a subsystem to respond to a command with the beginning of a stream of input data. This time is defined as the "latency" of the subsystem. Failure of a subsystem to respond within this period of time results in a BCE declared error condition.

The Interface Unit Address Register contains the 5-bit subsystem address of the subsystem presently in communication with the This address is derived when a command is issued by a BCE BCE. (Figure 1.1(c) ), and is used in the construction of data words to be sent to a subsystem (Figure 1.1(a)), and in checking for proper subsystem response when data words from a subsystem are being received (Figure 1.1(b)).

The BCE/MSC Indicator Register has 1 bit associated with each BCE. A BCE is free to set or clear this bit under program control. The MSC can read all such bits and monitor when various BCE's have set OT cleared their bits. The MSC may also reset a BCE's Indicator bit via an ORBI instruction. This provides a means for BCE's to signal to the MSC the occurrence of various events such as execution of listening mode programs.

The detection of various errors will also set a BCE's Indicator bit to 1 (See Paragraph 2.2).

#### 1.2.2 BCE\_Status\_Registers\*

The modes and status of each BCE is recorded in the following registers:

- (1) BCE Busy/Wait Bit -- For BCE i this is bit i of the Busy/ Wait Register (STAT 4). A 1 in this bit indicates that the BCE is busy executing a program located in main A 0 indicates it is not busy. memory.

- BCE Program Exception Bit -- For BCE i this is bit i of (2) the Program Exception Register (STAT 1). A 0 indicates that the BCE has encountered some problem in the execution of a BCE program. A 1 indicates that no problem was encountered. The Status Register associated with that BCE contains a description of the cause of the problem.

- (3)Transmitter Enable Bit -- For BCE/MIA i this is bit i of the MIA Transmitter Enable Register. A 0 in this bit prevents the BCE from issuing a command or transmitting data over the bus to which its MIA is connected. This bit may be changed only by a PCO from the CPU.

- (4) Receiver Enable Bit -- For BCE/MIA i this is bit i of the MIA Receiver Enable Register. A 0 in this bit prevents the MIA from transferring any data or commands it receives on the bus to the BCE. This bit may be changed only by a PCO from the CPU.

- (5) BCE Status Register. Each BCE maintains a unique 32-bit status register describing what, if any, errors the BCE has encountered during the execution of a program. Table 1.2 describes the format used in these registers.

- BCE Identity Register. Each BCE maintains (6)a register that contains twice its own BCE number. This register is used in computing addresses during direct mode BCE instruction. The register is set while the BCE is leaving the Halt state and entering the Wait state, and is not altered by the BCE at any other time.

\* PROGRAMMING NOTE

COPY PROVIDED BY WICHITA STATE UNIVERSITY LIBRARIE: SPECIAL COLLECTIONS WITHOUT WATTER FEMALON IN MATERIAL MAY NOT SE COPE RETROLOGINANT PARTINI MOTIFICATION MATTERISTICATION

LIBRARIES

MS

87-08

Box

2

T

U 0 ι,

Wichita State University Libraries, Special Collections and University Archives

Dr. James E. Tomayko Collection of NASA Documents

BE COPIED OF

THIS MATERIAL MAY BE PROJECTED BY COPYRIGHT LAW (TITLE 17 U.S. CODE). COPY PROVINES

The BCE Status Registers should not be changed via PCO commands while the BCE is busy.

1

#### TABLE 1.2

# BCE STATUS REGISTER

|                                                                                                                                                                                       | м | P  | s  | E              | ۷  |           | I | U | A   |      |       |             | S   |      | · · · · · |                  |                                      | G<br>A<br>P      | S<br>T                 | X<br>M<br>T    |                        | I<br>T<br>O     | T<br>O            | B<br>T<br>O    | B<br>A    | I                    |    | L  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|----|----------------|----|-----------|---|---|-----|------|-------|-------------|-----|------|-----------|------------------|--------------------------------------|------------------|------------------------|----------------|------------------------|-----------------|-------------------|----------------|-----------|----------------------|----|----|

| 0 2                                                                                                                                                                                   | 3 | 4  | 5  | e y sê<br>alet | 7  | 8         |   |   |     | 12   | 13    | 14          | 15  | 16   |           |                  |                                      | 21               | 22                     | 23             | 24                     | 25              | 26                | 27             | 28        | 29                   | 30 | 31 |

| WIC                                                                                                                                                                                   |   |    | B  | IT             |    |           |   |   |     |      |       |             |     |      |           |                  |                                      |                  |                        |                |                        |                 |                   |                |           |                      |    | 1  |

| FO<br>PROTI                                                                                                                                                                           |   |    | 3  | 1 -            | 3  | 0         |   |   | R   | ese  | TV    | eđ          |     |      |           | l gata           |                                      |                  |                        |                |                        |                 |                   |                |           |                      |    |    |

| FOR RESEARCH<br>THIS MATERIAL<br>ROTECTED BY COD<br>(TITLE 17 U.S.<br>COPY PROVIE<br>IITA STATE UNIVER<br>SPECIAL COLL                                                                |   |    | 29 | 9 -            | I  |           |   |   | 1   | :11¢ | eg al | 10          | рс  | ode  |           |                  | his<br>110<br>xec                    | ega              | BCI<br>1 j<br>ion      | ns             | tri                    | ict             | nte<br>ior<br>rog | ı i            | n t       | an<br>he             |    | 2  |

| FOR RESEARCH USE ONLY<br>THIS MATERIAL MAY BE<br>PROTECTED BY COPYRIGHT LAW<br>(TITLE 17 U.S. CODE).<br>COPY PROVIDED BY<br>WICHITA STATE UNIVERSITY LIBRARIES<br>SPECIAL COLLECTIONS |   |    | 28 | 3 -            | В  | A         |   |   | B   | lour | nd a: | гy          |     | Ali  | gnm (     | e<br>i           | nco<br>nst<br>ali                    | ru               | ter<br>cti             | on             | C                      | i.l             |                   |                | OLI       | CE<br>at<br>dd       |    |    |

| LAW<br>BRARIES                                                                                                                                                                        |   |    | 27 | 7 -            | B  | ro        |   |   | B   | loc  | k :   | <b>ri</b> m | e   | Ou   | t1        | t<br>f           | ece<br>ime<br>or<br>nd.              | an an            | ou                     |                | wh                     | il              |                   |                | iti       |                      |    |    |

| MS 87-08 Box 42 F                                                                                                                                                                     |   |    | 26 | 5 -            | T  | <b>)</b>  |   |   | T   | 'ine | e Ot  | ıt          |     | A 1  | Recie     | o<br>d<br>t<br>i | Da<br>ut<br>ata<br>ime<br>npu<br>irs | W<br>W<br>O<br>O | hil<br>ord             | e<br>t         | wa<br>o a              | it<br>rr<br>re  | d c               | ۲<br>۹.        | da        |                      |    |    |

| Box                                                                                                                                                                                   |   |    | 25 | ; -            | I  | ro        |   |   | . I | nit  | ia:   | L T         | ine | e Oi | ıt -      | t<br>f           | ime                                  | t t              | ou<br>he               | t<br>f         | wh                     | il              | e                 | wa             | iti       |                      |    |    |

| 1                                                                                                                                                                                     |   | 25 | 24 | ţ              |    |           |   |   | R   | ese  | I Ve  | ∋đ          |     |      |           |                  | . *                                  |                  |                        |                |                        |                 |                   |                |           |                      |    |    |

| FF<br>FF                                                                                                                                                                              |   |    | 23 | 3 -            | XI | IT        |   |   | Т   | ran  | s ni  | Ltt         | er  | Di   | sabl      | e<br>D<br>a<br>h | ata<br>ssc<br>ad                     | ut:<br>i:<br>ci: | ion<br>nst<br>ate<br>s | ru<br>d<br>tra | of<br>cti<br>wi<br>ans | a<br>.on<br>.th | T<br>t            | ra<br>he<br>hi | s B<br>di | it<br>IA<br>CE<br>s- |    |    |

| 50                                                                                                                                                                                    |   |    |    |                |    | 1 43<br>5 |   |   |     | ľ    |       |             | 14  |      |           |                  |                                      |                  |                        |                |                        |                 |                   |                | 0         |                      |    |    |

Wichita State University Libraries, Special Collections and University Archives

| 2010                                                                                                                                                                |              |                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WITHO                                                                                                                                                               |              | set if the MIA was found<br>busy when it was time to<br>initiate transmission of<br>a new data word.                                                                                                                                                                                                          |

| FOR RES<br>THIS M<br>PROIECTED<br>(TITLE<br>COPY<br>WICHITA STATE<br>SPECIA<br>SPECIA                                                                               | 22 - ST      | Self Test Error A BCE Self Test Instruction<br>has detected a fault in<br>the BCE.                                                                                                                                                                                                                            |

| R RESEARCH<br>HIS MATERIA<br>COTED_BY CC<br>TITLE 17 U.S.<br>TITLE 17 U.S.<br>TATE UNIVE<br>STATE UNIVE<br>STATE UNIVE<br>STATE UNIVE<br>STATE UNIVE<br>STATE UNIVE | 21 - GAP     | Gap of greater than 20 usec. occurred during<br>execution of a transmit<br>data instruction, or 5<br>usec during a MOUT.                                                                                                                                                                                      |

| L MAY<br>DED I<br>COED I<br>RSIT                                                                                                                                    | 20 - 16      | Reserved.                                                                                                                                                                                                                                                                                                     |

| E ONLY<br>AY BE<br>UGHT-LAW<br>IBP<br>IBP<br>TY LIBBARIES<br>TIONS<br>UNAWIEDOSTORY                                                                                 | 15 - s       | Sync Error While executing a Receive Data<br>Instruction, an input word<br>with command sync was<br>received. (See #RDS<br>Instruction)                                                                                                                                                                       |

|                                                                                                                                                                     | 14 - 13      | Reserved                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                     | 12 - 8       | Subsystem Address This field is the logical<br>"OR" of the received sub-<br>system addresses of all<br>input words that were de-<br>tected to have errors<br>during execution of<br>previous Receive Data<br>Instrs.                                                                                          |

| MS 87-08 E<br>Dr. James E. Tomayko Colle<br>Wichita State University Libra                                                                                          | 7 - 5        | SEV This field is the logical "OR" of the<br>SEV bits of all input<br>words that were detected<br>to have errors during<br>execution of previous<br>Receive Data Instruction.<br>The S and V bits were<br>inverted before the "OR".<br>Thus, any pattern other<br>than 101 will be recorded<br>in these bits. |

| Box <i>H</i> J F<br>ko Collection of NASA Documents<br>rsity Libraries, Special Collections a                                                                       | 4 <b>-</b> P | Parity While executing a Receive Data<br>Instruction, an input word<br>with bad parity was<br>detected.                                                                                                                                                                                                       |

| Box $\mathcal{H}_{\mathcal{A}}$ FF $\mathcal{S}_{\mathcal{A}}$ ko Collection of NASA Documents rsity Libraries, Special Collections and Unive                       | 3 - M        | Signature Mismatch While executing a<br>Receive Data Instruction,<br>a · mismatch between the                                                                                                                                                                                                                 |

| nive                                                                                                                                                                |              | 15                                                                                                                                                                                                                                                                                                            |

Dr. James E. Tomayko Collection of NASA Documents Wichita State University Libraries, Special Collections and University Archives

00

input's IUA and the BCE's IUAR. The input IUA was simultaneously 'OR'ed into bits 8 - 12 of the status word.

FOR RESEARCH USE ONLY THIS MATERIAL MAY BE PROTECTED BY COPYRIGHT LAW (TITLE 17 U.S. CODE). COPY PROVIDED BY WICHITA STATE UNIVERSITY LIBRARIES SPECIAL COLLECTIONS SPECIAL COLLECTIONS MITHOUT WRITTEN PERMISSION, THIS MATERIAL MAY NEEDOSTORY

Dr. James E. Tomayko Collection of NASA Documents Wichita State University Libraries, Special Collections and University Archives

SW

87-08

Box 42

뀨

50

2

C

Reserved.

1.3

FOR RESEARCH USE ONLY THIS MATERIAL MAY BE PROTECTED BY COPYRIGHT LAW

MITHOUT WRITTEN PERMISSION. THIS MATERIAL MAY NOT BE COPIED OF REFROCUCED IN ANY FASHION, NOR PLACED IN MY FETOSITISTY

Wichita State University Libraries, Special Collections and University Archives

Dr. James E. Tomayko Collection of NASA Documents

SM

87-08

Box

С Д

뀌

00

(TITLE 17 U.S. CODE). COPY PROVIDED BY WICHITA STATE UNIVERSITY LIBRARIES SPECIAL COLLECTIONS

### BCE IMPLEMENTATION

- Any BCE implemented within an IOP consists of:

- A segment of Local Store. This consists of 4 words from each of Banks A and B, and 8 words from Bank C.

- (2) A bit in the IOP Busy/Wait Register.

- (3) A bit in the IOP Program Exception Register.

- (4) A bit in the IOP Halt Register.

- (5) A bit in the BCE-MSC Indicator Register.

- (6) The associated MIA.

- (7) A buffer location in the MIA Buffer.

- (8) A bit in the MIA Transmitter Enable Register.

- (9) A bit in the MIA Receiver Enable Register.

- (10) One of the Microprogram Counters. This contains the ROM address of the next micro instruction to be executed for this BCE.

As described in the IOP Functional Description (IBM No. 74-A31-016;), the operation of all BCE's and the MSC is time-shared. Each BCE executes its next microinstruction from ROS at intervals of one every 16.5 microseconds. During other periods of time the only carried on are previously requested BCE-related operations still operations, memory MIA reception/transmission of data, an d CPU directed PCI/0.

The general makeup of a BCE's Local Store segment is shown in Figure 1.5. All unlabelled words are used as temporary or working registers during instruction execution.

Figure 1.5. BCE Local Store Usage

Wichita State University Libraries, Special Collections and University Archives Dr. James E. Tomayko Collection of NASA Documents SW 87-08 Box 1 Q 귀 00

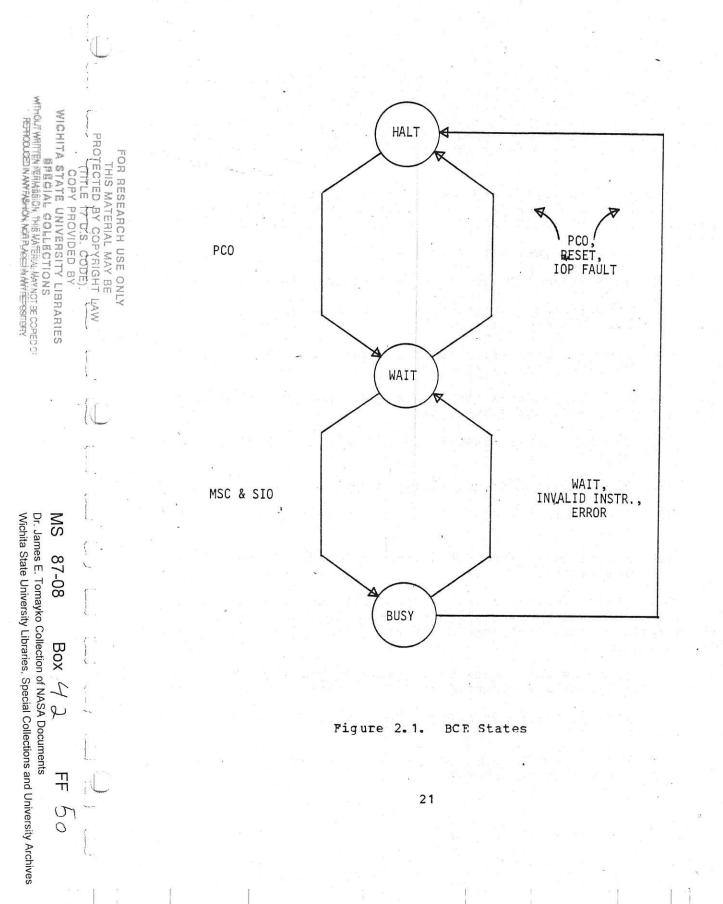

#### 2.0 GENERAL BCE OPERATION

During normal operation a BCE can be in one of three, states: Wait and Busy. In the Halt state the BCE is physically Halt, THE AWAITING A COMMAND AND A SIGNAL FOR THE AWAY OF TH restrained from performing any operations; in the Wait state the BCE is awaiting a command to execute a program; and in the Busy state the Figure 2.1 summarizes

Typical state transitions are as follows:

- During any system or CPU-directed BCE reset, the BCE is

- Upon release from the Halt state, the BCE enters the

- A signal from the MSC initializes a BCE, and places it

- In the Busy state, the BCE is executing a program located in main memory. It exits the Busy state only (4) upon execution of a Wait instruction, detection of an invalid instruction or operating error, or some reset In all but the latter case, the BCE re-enters signal. the Wait state; in the latter case it is forced to the Halt state.

The two bits that indicate the current state of BCE i are its Halt bit (Bit i of the IOP Halt Register) and its Busy/Wait bit (Bit IOP Busy/Wait Register). i of the In addition, the BCE Program Exception bit indicates if the BCE has found an error during its last time in the Busy state. If it has found an error, the BCE period of Status Register contains a record of the 'exact error.

The following sections describe each state in detail.

2.1 HALT STATE

WITHOUT WRITTEN PERMISSION, THIS MATERIAL MAY NOT BE COPI REPRODUCED IN MAY FASHON, NOR PLACED IN MAY PERGENCERY

WICHITA

MS

87-08

Box

1

Q

뀨

U 0

Wichita State University Libraries, Special Collections and University Archives

Dr. James E. Tomayko Collection of NASA Documents

PRO.

- The primary purpose of the Halt state is two-fold:

- Allow the external world to reset BCE operation to (1)a known condition.

- Upon the detection of very serious IOP faults (such as . (2) failure in the microstore) to isolate the BCE and prevent it from performing potentially erroneous operations.

Entry and exit from the Halt state are controlled by the value of a single "BCE Halt" status bit which is part of the IOP Halt Register. There is one such bit for each BCE. As long as this bit is set, the BCE microprogram counter is forced to point to a micro-

instruction that performs no operation other than clear the BCE The Halt bit may be set to 0 at any time, and Busy/Wait bit. effectively terminates anything that the BCE is doing.

The signals that set a BCE Halt bit to 0 (Halt) include:

- BCE/MSC disable discrete, Discrete Input 0, or a Master (1) Reset PCO from the CPU.

- Setting of the Fail Latch for this GPC by (2) either the Redundancy Management voting logic or IOP detected serious errors such as ROS parity error.

- A "Halt Processor" PCO from the CPU with a 1 (3) in bit position i (when BCE i is to be halted).

The first two signal classes halt all BCE's.

from this state to the Wait state occurs only when the Exit following occurs:

- BCE Disable Discrete is reset. (1)

- (2)Fail Latch is reset.

THOUT WRITTEN PEHMSSION, THIS MATERIAL MAY NOT BE COPIED OF ROPADCUCED IN ANY FASHORN NOT PLACED IN MY HED SETTERY

NICHITA

SPECI

≥ m

UNIVERSI

DROVIDED BY UNIVERSITY LIBRARIES COLLECTIONS

SM

87

$\widetilde{\infty}$

ω

2

1

Q

П TI U 0

Dr.

James

Ē 6

Wichita State University Libraries, Special Collections and University Archives

Tomayko Collection of NASA Documents

PRO

TH

J II ES

m

ARCH

ONLY

OTECTED BY C.

COPYRIGHT RIAL ŝ

LAW

CODE

a CPU "Enable Processors" PCO with bit i (for BCE i) set to 1 and is The PC I/O manual (IBM No. 6246556) describes the PCO that present. set/reset the Halt register.

Upon any exit from the Halt state, the BCE Program Exception is set to one (no errors). The BCE Status Register is cleared to bit all zeroes, and the BCE Identity Register is set to twice the BCE's number.

Although a BCE's Halt bit may be changed at any time, it does not affect the BCE's operation until the next time that the BCE executes a microinstruction. Consequently, to guarantee that a BCE has been halted, the BCE's Halt bit should be at 0 (halted) for a minimum of 18 usec. before being reset to 1 (enabled). This will guarantee that the BCE has truly been forced to the halt state for at least one BCE microcycle.

For similar reasons, a BCE should not be considered released from the Halt state and in the Wait state the instant its Halt bit is set to 1 (enabled). Release from the Halt state does not begin until the first BCE microcycle after the Halt bit has been reset, and continues for several BCE microcycles (about 100 usec.) as the BCE its internal registers and prepares to enter the Wait state. resets After this transition, the BCE will be in the Wait state, and will perform as described in the next section.

#### 2.2 WAIT STATE

WICHITA

SPE

SPECIAL

COPY

E 17 U.S. CODE). Y PROVIDED BY E UNIVERSITY LIBRARIES AL COLLECTIONS

FOR RESEARCH USE O THIS MATERIAL MAY E PROTECTED BY COPYRIGH (TITLE 17 U.S. CODE)

D BY COPYRIGHT I

LAW

MS

87

-08

ω 2

2

2

뀨

J 0

Dr. James E. Tomayko Collection of NASA Documents

Wichita State University Libraries, Special Collections and University Archives

In the Wait state, a BCE is prepared to be told to perform а This wait loop is implemented by a micro-routine that BCE program. monitors the status of the BCE's Busy/Wait bit. The BCE remains in Wait state as long as its bit is reset to the "Wait" value (0). the When the MSC (via an @SIO) sets this bit to busy, the BCE transits to Busy state. This transition consists of using the present value of the BCE's Program Counter as the starting address of a BCE program in main store.

Entry to the Wait state occurs either upon exit from the Halt as described above, or by a transition from the Busy state. state, A BCE performs this latter transition when any of the following occurs:

- (1) A "Wait" instruction is executed.

- (2)An instruction with an illegal opcode is encountered.

- A valid long format instruction is found starting on (3) an odd halfword boundary.

- (4) A significant error occurs. (such as in transmit OI receive data instruction) .

the final three cases, Tn a BCE performs the following actions before entering the Wait state:

- It sets its bit in the Program Exception Register (1)(STAT 1) to 0.

- It sets its BCE-MSC Indicator bit to 1. (2)

- It records the cause of the error in its own BCE (3) status register.

- (4) It leaves the Program Counter pointing to the offending instruction.

BCE's Indicator bit is set, upon detection of an error, The to aid in handling Listen mode programs where this bit is used to signal completion of some operation to the MSC (via a Repeat on Indicator instruction).

Exit from the Wait state is normally to the Busy state. This is done, by the MSC, via a sequence of MSC instructions that include:

- A "Load BCE Base" instruction 1) to set the BCE's Base register.

- 2) A "Load BCE Program Counter" instruction to set the BCE's Program Counter.

3) A "Start I/O" instruction to set the BCE's Busy Wait bit.

Note that the CPU can perform the equivalent of the first two via PCO's to the BCE's Local Store. Also, via PCO's, the functions CPU can reset the BCE's Status Register and Program Exception bit. The CPU cannot, however, directly set a BCE's Busy/Wait bit.

Note also that a BCE's Program Counter need not always be set the MSC sets the BCE to busy, since the BCE Wait instruction before (#WAT) when executed, leaves the PC pointing to the next sequential instruction. This next instruction may be programmed as a simple instruction. branch to the beginning of the next BCE program segment. In this case, the MSC need only execute an SIO instruction to restart the BCE at the next segment.

While a BCE is in the Wait state, the CPU may perform PCI/O activity without disturbing the BCE.

2.3 BUSY STATE

0

0

WITHOUT WRITTEN PERMISSION, THIS MATERIAL WAY NOT BE COPPORED IN MY FERMINICAL WAY REPORTORY

THIS MATERIAL WAY NOT BE COPE

ICHITA

COPY P A STATE L SPECIAL

E UNIVERSITY LI

BP

PARIE

MS

87-08

Box

1

T

U 0

Wichita State University Libraries, Special Collections and University Archives

Dr. James E. Tomayko Collection of NASA Documents

FOR RESEARCH USE ONLY THIS MATERIAL MAY BE PROTECTED B& COPYRIGHT L (TITLE 17 U.S. CODE).

LAW

In the Busy state, BCE i is in the process of executing a program out of main store. A value of 1 in the ith bit of the IOP Busy/ Wait Register indicates this condition.

The Busy state may be entered only from the Wait state, as described in the previous section. When the transition occurs, the BCE uses the value in its Program Counter to mory and start executing it. to fetch the first instruction from memory The BCE continues executing instructions until either a Wait instruction or some kind of invalid instruction is encountered. In either case, the BCE transitions back to the Wait state, again as described in the previous section.

an MSC @SIO instruction will set a BCE's Busy/Wait Although bit to busy within the time frame of the instruction's execution on the MSC, the BCE will not necessarily begin immediate execution of the first instruction. The possible delays include:

- The time required for the BCE to recognize that its Busy/Wait bit is set (up to 16.5 usec.)

- The time required to bring out the PC and request 0 the instruction word from memory (up to 33 usec) and,

- Any time required for the memory read request to reach the DMA channels, be read from memory, and be returned to the BCE.

23

The memory read request time delays the BCE setup only when handling time exceeds 16 usec. This situation can occur when several BCE/MSC processors have requested memory reads simultaneously.

While the BCE is in the Busy state, the CPU may execute any PCI without problem. However, all PCO's that write into BCE Local should be carefully controlled since the MSC is not aware that Store this action has occurred, and the resulting BCE program execution may be unpredictable.

#### 2.3.1 Busy State Operating Modes

WITHOUT WRITTEN PERMISSION.

ICHITA

STATE L

AL COLLECTIC

SW

87-08

E Š

I

Π U 0

Wichita State University Libraries, Special Collections and University Archives

Dr. James E. Tomayko Collection of NASA Documents

REPRODUCED IN ANY FASHION, INCR PLACED IN ANY REPOSITORY

FOR Once in the Busy state a BCE may operate in one of two mouse, OTHER Once in the Busy state a BCE may operate in one of two mouse, Science of the Busy state a BCE may operate in one of two mouse, Science of the Busy state a BCE may operate in one of two mouse, Science of the Busy state a BCE may operate in one of two mouse, Science of the BCE's MIA transmitter is disabled. In Command mode

COPYRIG AL MAY O free to t rel The BCE Mode affects the way certain BCE instructions are In the Command Mode, a BCE is in command of its bus and is free to transmit commands and data over the bus. A BCE in the Listen relies on a BCE in another IOP to indicate the operations to be performed and to issue the appropriate commands to subsystems the on bus to perform the operations. Consequently, a BCE in Listen mode will handle instructions that transmit commands in a different manner BCE executing the same program in the command than a mode. Additionally, a BCE in the Listen mode uses a Wait for Index as an instruction to wait for some other BCE in another instruction IOP to provide a signal as to what it should do. This signal is used by the Listening BCE in a table-look up process to determine an appropriate BCE program for execution.

Section 4 describes the differences between Command Mode and Receive Mode in greater detail.

#### 2.3.2 -Summary of Error Modes

Table 2.1 summarizes all the errors detectable during a BCE and the resulting actions. Separate columns indicate which, program if any status bits are set, and whether or not the BCE enters the wait state. If any status bits are set, the BCE Program Exception bit is also assumed set to 0, and the BCE/MSC Indicator bit is set to 1.

### TABLE 2.1

## SUMMARY OF BCE-RELATED ERRORS

Action WITHOUT WRITTEN PERMISSION, THIS MATERIAL MAY NOT BE COPIE REPROJUCED IN ANY FASHON NOR PLACED IN ANY REPOSITORY Status Bit Wait State Other FOR RESEARCH USE ONLY THIS MATERIAL MAY BE COPY PROVIDED BY COPY PROVIDED BY COPY PROVIDED BY COPY PROVIDED BY WICHITA STATE UNIVERSITY LIE SPECIAL COLLECTIONS FIIOI Detected By \_\_\_\_Set? Entered? Action Illegal BCE Microcode Bit 29 Yes Instruction Long Format Microcode Bit 28 Yes BCE Instruction on Odd Boundary Bad Command Microcode/ None No Command Received in MIA ignored. #WIX Wait continued. DMA (see Illegal Instruction) Channel Logic Write all Parity Error 0's into on Instruc-Instruction tion Read register (illegal opcode) CPU interrupt. DMA Channel Logic 21 Yes CPU Inter-Parity Error, Microcode rupt DMA Timeout, or Time Out Wichita State University Libraries, Special Collections and University Archives Dr. James E. Tomayko Collection of NASA Documents SN Queue Overflow on Data read for Transmit 87-08 Data Instruction DMA Channel Logic None NO CPU Inter-Parity Error, rupt. BCE DMA Timeout, or ãoes not Box Queue Overflow receive on other data data. reads 1 ROS Parity IOP Hardware No No BCE Reset to 2 Error, Clock halt. CPU Failure, Interrupt Termination Latch Set

25

U 0

Î

1.1

| ×                                                                                          | Self Test<br>Detected<br>BCE Fault                    | Bce Self Test<br>Instructi | Bit 22<br>on | No  | BCE Loops                            | - magelow |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------|--------------|-----|--------------------------------------|-----------|

| PROTECTE<br>(TITL<br>COP<br>WICHITA STAT<br>WICHITA STAT<br>SPECI<br>WITHOUT WRITTEN REAMS | - * -                                                 |                            |              |     |                                      |           |

| PROTECTED<br>(TITLE<br>COPY<br>VICHITA STATE<br>SPECIAL<br>OUT WAITTEN PERMASSIO           | Excessive<br>Concurrency<br>Iesulting                 | Microcode<br>Time out      | 21           | Yes |                                      |           |

|                                                                                            | gap in<br>Transmit                                    |                            |              |     |                                      |           |

| DEC DEC                                                                                    | Aata, or 5<br>Usec in MOUT<br>Transmitter<br>Disabled |                            |              |     |                                      |           |

| HIGHT LAW<br>ODE)<br>D BY<br>ITY LIBRARIE<br>TIONS                                         | Transmitter<br>Disabled<br>during                     | Microcode<br>Test          | 23           | Yes |                                      |           |

| LAM<br>FARIE                                                                               | transmit<br>data                                      |                            |              |     |                                      | *         |

|                                                                                            | Transmitter<br>Busy too                               | Microcode<br>Test          | 23           | Yes |                                      |           |

| 1                                                                                          | long                                                  |                            |              |     |                                      |           |

|                                                                                            | Parity<br>Error on<br>input data                      | MIA                        | 4            | Yes | Save IUA<br>from data.               | ( )       |

| 9                                                                                          | Input uata                                            |                            |              |     | Data not<br>stored in<br>MIA Buffer. |           |

| MS                                                                                         | Wrong SEV<br>bits                                     | Microcode/<br>Hardware     | 5,6,7        | Yes | 0 11                                 |           |

| Jame .                                                                                     | Command                                               | Microcode                  | 15           | Yes | 11 11                                |           |

| 87-08<br>% E. Tom                                                                          | Sync in<br>Receive<br>Data                            |                            |              |     | (See #RDS)                           |           |

| nayko Co                                                                                   | Wrong IUA<br>in incoming                              | Microcode/<br>Hardware     | 3            | Yes | <b>II</b> II                         |           |

| Box                                                                                        | data                                                  |                            |              |     |                                      | Ś.        |

| MS 87-08 Box 4 J FF 50<br>Dr. James E. Tomayko Collection of NASA Documents                | Failure of<br>Subsystem<br>to respond                 | Microcode<br>time-out      | 25           | Yes |                                      | 2<br>1    |

| A Docum                                                                                    | with data<br>(1st word)                               |                            |              |     |                                      |           |

| FF                                                                                         | н<br>, 1                                              |                            |              |     | a a a                                |           |

| 50                                                                                         | ы<br>ж.<br>3823 — т.                                  |                            |              |     | 3                                    |           |

| 2                                                                                          |                                                       |                            | 26           |     | 1 - 40<br>                           |           |

|                                                                                                                                                                                       | X.                        |       |     | 6246556A                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------|-----|--------------------------------------------------------------|

| Excessive<br>interword<br>gap in<br>incoming<br>data                                                                                                                                  | Microcode<br>time out     | 26,27 | Yes |                                                              |

| WITHOUT WRITTEN PERFORMED BY<br>PERFORMED BY<br>MITHOUT WRITTEN PERMISSION THIS MATERIAL MAY BE<br>COPY PROVIDED BY<br>COPY PROVIDED BY<br>SPECIAL COLLECTIONS<br>SPECIAL COLLECTIONS | MIA/Microcode<br>time-out | 26    | Yes | Data is not<br>stored in<br>MIA Buffer.<br>BCE will time out |

| SE ONLY<br>NAY BE<br>RIGHT LAW<br>ODE)<br>D BY<br>TTY LIBRARIE<br>TTONS                                                                                                               |                           |       |     |                                                              |

|                                                                                                                                                                                       |                           |       |     |                                                              |

| MS 87-08<br>Dr. James E. Tome<br>Wichita State Univ                                                                                                                                   |                           |       |     |                                                              |

| 08<br>mayko Coll                                                                                                                                                                      |                           |       |     |                                                              |

| Box 4 J<br>Ilection of NASA Docu<br>braries, Special Collec                                                                                                                           |                           |       |     |                                                              |

| MS 87-08 Box 4 2 FF 50<br>Dr. James E. Tomayko Collection of NASA Documents<br>Wichtha State University Libraries, Special Collections and University Archives                        |                           | 27    |     |                                                              |

| Archives                                                                                                                                                                              |                           |       |     |                                                              |

MS

87-08

Box

1 Q

귀

U 0

Dr. James E. Tomayko Collection of NASA Documents

Wichita State University Libraries, Special Collections and University Archives

BCE\_INSTRUCTIONS The following pages in presently supported by each presently supported by each presently supported by each instruction is as follows: Performed by each THIS MATERIAL MAY BE SPECIAL COLLECTIONS O The general name upper left instructior A STATE UNIVERSION HIS MATERIAL MAY BE NAMESON HIS MATERIAL MAY BE NA The following pages include descriptions of the instructions presently supported by each BCE. The format for the description of

- The general name of each instruction appears in the the first page describing that

- The assembler abbreviation appears in the upper right

- The format of the instruction, including binary opcode assignments and field designations.

- A table (where appropriate) relating addressing mode their effect on parameters used in the instruction execution, and how these addressing modes are signalled to the assembler.

- 0 A textual description of the instruction and its uses.

- 0 The minimum instruction execution time will not be presented here as it is supplied in Document No. 74-A31-00009A.

Since the IOP is a multiprocesser with up to 24 BCEs and the MSC requesting memory access independently of each other, it is possible that a memory request from a BCE can be delayed due to the servicing of earlier requests from other IOP processors. If these delays become significant (become greater than about 16.5 usec) then the BCE will be forced to wait for the memory operation to complete in increments of 16.5 usec. This will of course increase the instruction times.

These descriptions of instructions are grouped into several separate classes with a short prologue at the beginning of each class. These classes include:

| Paragraph | 3.1 |   | BCE Register Operations |

|-----------|-----|---|-------------------------|

| Paragraph | 3.2 |   | Branching Instructions  |

| Paragraph | 3.3 | - | Transmit Instructions   |

| Paragraph | 3.4 | - | Receive Instructions    |

| Paragraph | 3.5 | - | Special Instructions    |

# 3.1 BCE REGISTER INSTRUCTIONS

COPY PROVIDED BY WICHITA STATE UNIVERSITY LIBRARIES SPECIAL COLLECTIONS WITHOUT WRITTEN REMAINSION, THIS MATERIAL MAY NOT BE COPIED OF

MS

87-08

Box

1

뀨

U 0

Wichita State University Libraries, Special Collections and University Archives

Dr. James E. Tomayko Collection of NASA Documents

PROTECTED

OR RESEARCH USE ONLY THIS MATERIAL MAY BE NEETED BY GOPKHIGHT LA (TITLE 17 U.S. CODE).

FAX-

FOR N.

REPHOQUCED IN ANY FASHON, NOR PLACED IN ANY REPOSITORY

The BCE instruction set has several instructions that allow to modify or store many of its registers. it These registers include the Maximum Time Out register, the BCE-MSC Indicator bit, the Base register, and the Status register. In each case, the register referred to by the instruction is the one owned by the BCE executing that instruction.

The formats for these instructions are primarily 16 bits of the form of Figure 1.3, with the exception of the Load Base, which is a long format instruction (Figure 1.4). The Load Time Out and Load Base instructions use instruction bit 4 to indicate whether the addressing of the data to be loaded into the appropriate register is immediate or direct. In the first case, the data to be loaded is present in the instruction itself; in the latter, the instruction determines the address of the word containing data.

The Store Status instructions allow the specification of by the current BCE number in the computation of the memory indexing address to contain the status words. This permits the same instruction to be used by many BCE's since the index by processor number will construct a table of status words.

This group includes instructions to set or reset the BCE-MSC indicator bits. These bits have no meaning to the hardware, but can be read by MSC instructions, allowing them to be used as generalpurpose flags by the BCE and MSC programs.

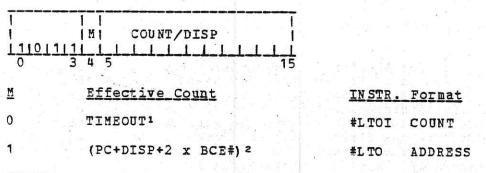

#LTOI, #LTO

## LOAD TIME OUT REGISTER

### FORMAT :

### NOTES:

SPECIAL COLLECTIONS

WICHITA

STATE

UNIVERSITY LIBRARIES

PROTECTED

(TITL COPY

m

C

ŝ

CODE

MS

87-08

ω

X

1

R

开

5 0

Dr. James E. Tomayko Collection of NASA Documents

Wichita State University Libraries, Special Collections and University Archives

LAW

THIS MATERIAL MAY

ATERIAL MAY BE

Any value between 0 and 2047. This corresponds to time outs from 0 to 33.78 millisec.

The lower 18-bits of the fullword addressed by PC (updated) + 2. displacement + 2 x BCE#. This allows any count between 0 and 262143, or 0 to 4.325 sec.

### DESCRIPTION

1.

instruction loads the Maximum Time Out Register (MTO) This with the Effective Count. This register is used by the Receive Data instructions to determine how long a BCE will wait for the first input word to arrive from a previously commanded subsystem. The resolution of this timeout count is 16.5 microseconds.

After loading the Maximum Time Out register, the BCE increments its program counter by 1 and begins execution of the next sequential instruction.

### PROGRAMMING NOTE

In direct mode, the computation of the effective address includes the number of the BCE executing the instruction. This allows many BCE's to execute the same BCE program, but, each one uses a timeout parameter best suited for the subsystem with which they are communicating. Note that two times the BCE number gives a fullword index.

#### RESET INDICATOR BIT

6246556A

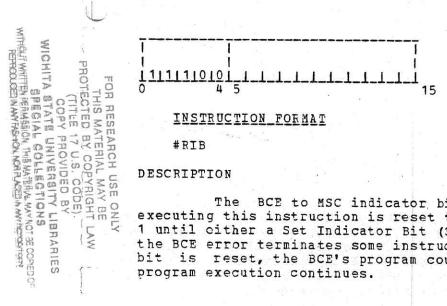

<u>#RIB</u>

FORMAT INSTRUCTION

### #RIB

### DESCRIPTION

5

The BCE to MSC indicator bit associated with the BCE that executing this instruction is reset to 0. This bit will not change is This bit will not change to until either a Set Indicator Bit (SIB) instruction is executed 1 or, the BCE error terminates some instruction at a later time. After this reset, the BCE's program counter is incremented by 1, and BCE bit is program execution continues.

Π

U 0

#### SET INDICATOR BIT

6246556A

#SIB

INSTRUCTION FORMAT

#SIB

## DESCRIPTION

BCE to MSC indicator bit associated with the BCE that is The executing this instruction is set to 1. This bit will not change to either the BCE executes a Reset Indicator (#RIB) instruction 0 until or the MSC executes a Reset BCE Indicator (@RBI) instruction with this BCE's number. After this bit is set, the BCE's program counter is incremented by 1, and BCE program execution continues.

### PROGRAMMING NOTE

In indexing mode the computation of the effective address includes the number of the BCE that is executing this instruction. This allows many BCE's to use the same BCE program, and yet store the status from each BCE in a different location. Note that the BCE number is multiplied by 2 to give a fullword index.

Dr. James E. Tomayko Collection of NASA Documents SW Wichita State University Libraries, Special Collections and University Archives 87-08 Box 1 2 귀 U 0

WICHITA STATE UNIVERSITY LIBRARIES PROTECTED BY COPYRIGHT LAW (TITLE 17 U.S. CODE).

TH DERMARION THIS MATERIAL MAY NOT BE COPIED OR

SPECIAL COLLECTIONS

FOR RESEARCH USE ONLY THIS MATERIAL MAY BE

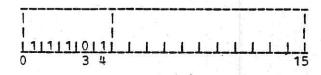

<u>#SSC</u>

STORE STATUS AND CLEAR

IMI DISPLACEMENT 101110101 1\_1 L 3 0 4 5 15 Effective Address (EA) M IN STR.Format 0 PC + DISP. #SSC ADDRESS 1 PC + DISP + 2XBCENO #SSC ADDRESS(1)

NOTES: 1. PC is the updated Bus Control Element (BCE) Program Counter, i.e. the address of the next sequential instruction.

### DESCRIPTION

This instruction stores the BCE's status register in the fullword location addressed by the Effective Address. The least significant bit of EA (the halfword address) is ignored. After initiating the store operation the BCE will then clear its status register and set its program execution bit (from STAT1) to 1 (GO). It will then increment its program counter by 1 and continue with execution of the next sequential instruction.

### PROGRAMMING NOTE

In indexing mode the computation of the effective address includes the number of the BCE that is executing this instruction. This allows many BCE's to use the same BCE program, and yet store the status from each BCE in a different location. Note that the BCE number is multiplied by 2 to give a fullword index.

FOR RESEARCH USE ONLY THIS MATERIAL MAY BE PROTECTED BY COPYRIGHT LAW (TITLE 17 U.S. CODE). COPY PROVIDED BY WICHITA STATE UNIVERSITY LIBRARIES SPECIAL COLLECTIONS SPECIAL COLLECTIONS MITHOUT WRITTEN PERMISSION THIS MATERIAL MAY MOTIVE COPPEDOF

MS

87-08

Box

L J

П

00

Wichita State University Libraries, Special Collections and University Archives

Dr. James E. Tomayko Collection of NASA Documents

#SST

### STORE STATUS