STORES

# Space Shuttle Advanced System/4 Pi Model AP-101 Central Processor Unit

**Technical Description**

Illinilli

interned is from Box 42,

O

752

INS: MAT

ERIAL MASEBONLY H USE ONLY **OPYRVGHTBEAW** YORGHT LAW

WICHITA ST

SUTY LIBRARIES

MS

87-08

---

Box to 2 \*

Π

15

1. 1.

Wichita State University Libraries, Special Collections and University Archives

Dr. James E. Tomayko Collection of NASA Documents

# Space Shuttle Advanced System/4 Pi Model AP-101 Central Processor Unit

2

SEARCH USE ONLY

LAW

N9-04

LIBRARIES

AS S

87-08.

Box 10 42

뀌

せい

Dr. James E. Tomayko Collection of NASA Documents

**Technical Description**

Prepared for

Rockwell International Corporation Space Division 12214 Lakewood Blvd Downey, CA 90241

31 March 1975

Under

Space Shuttle GPC M4J7XMA-483019

IBM File No. 75-A97-001

### TABLE OF CONTENTS

### Section

IBRARTES

SW

87-08

--- Box toya

FFJ45

AY B

### Title

|       |                                               | 1-1                       |

|-------|-----------------------------------------------|---------------------------|

| 1     | STIMMARY OF CHARACTERISTICS                   | 1-1                       |

| 1.1   | SUMMARY OF CHARACTERISTICS                    | 2-1                       |

| 2     | ARCHITECTURE                                  | 2-1                       |

| 2.1   | ADDRESSING                                    | 2-2                       |

| 2.2   | DATA FORMATS                                  | Contraction of the second |

| 1 2.3 | INSTRUCTION FORMATS                           | 2-4                       |

| o 2.4 |                                               | 2-8<br>2-14               |

| 0 2.5 | SYSTEM STATUS AND PROGRAM STATES              |                           |

| N.2.6 | CDU INTERBUPT STRUCTURES                      | 2-16                      |

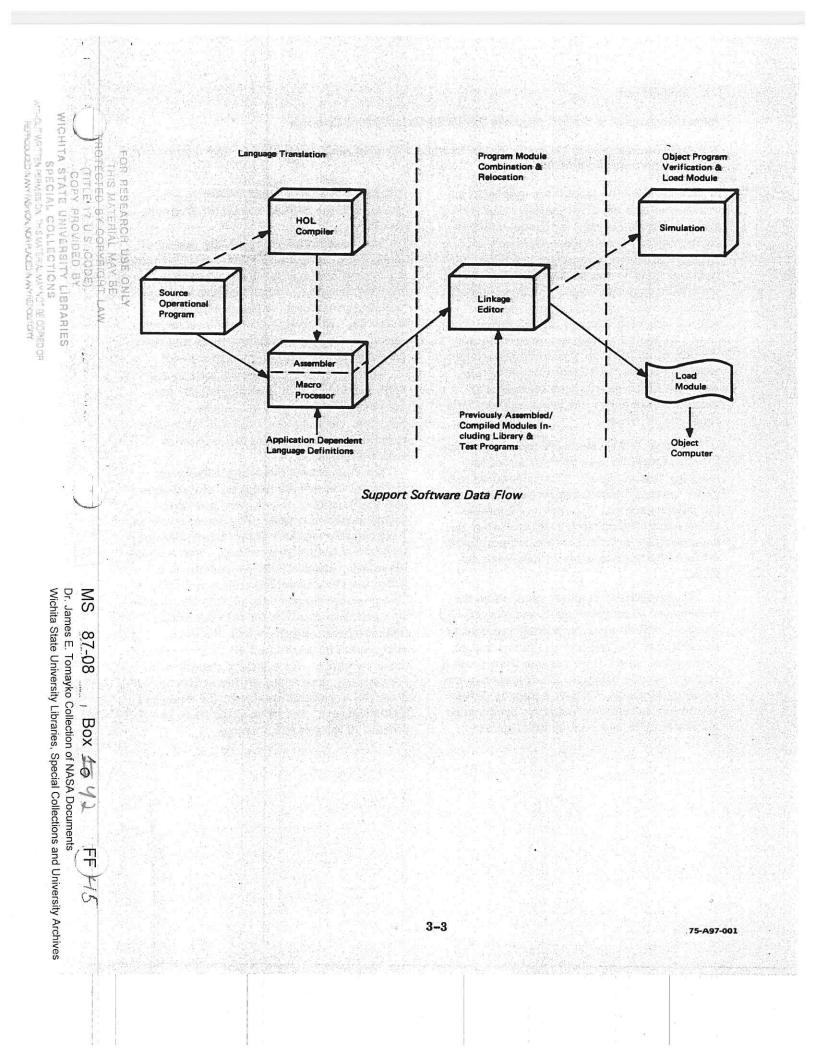

| 3     | CURRENT SOFTWARE                              | 3-1                       |

| 3.1   | SYSTEM 360/370 SUPPORT PROGRAMMING SYSTEM     | 3-2                       |

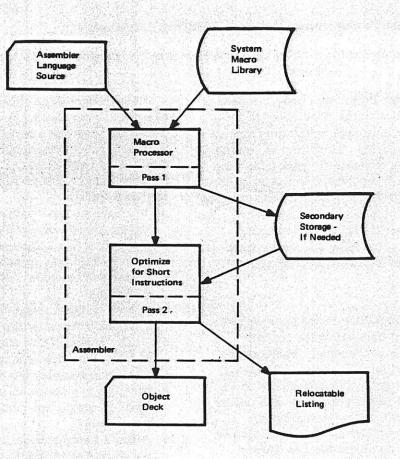

| 3.2   | ASSEMBLER                                     | 3-4                       |

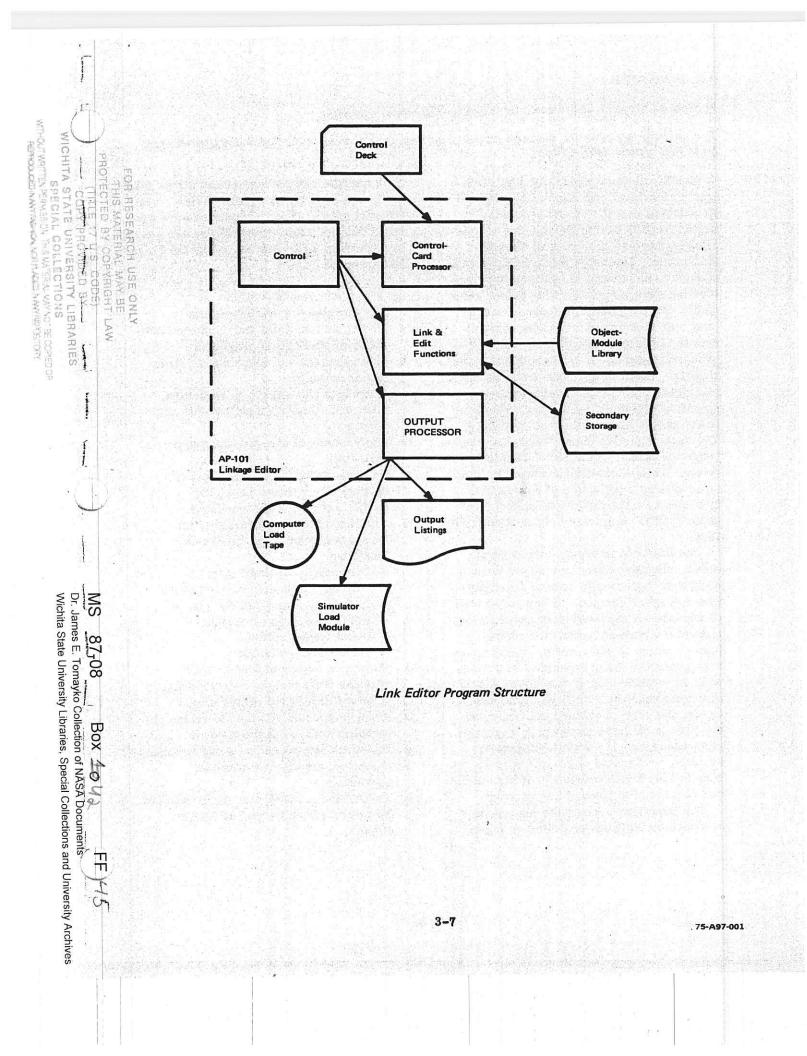

| 3.3   | LINKAGE EDITOR                                | 3-0                       |

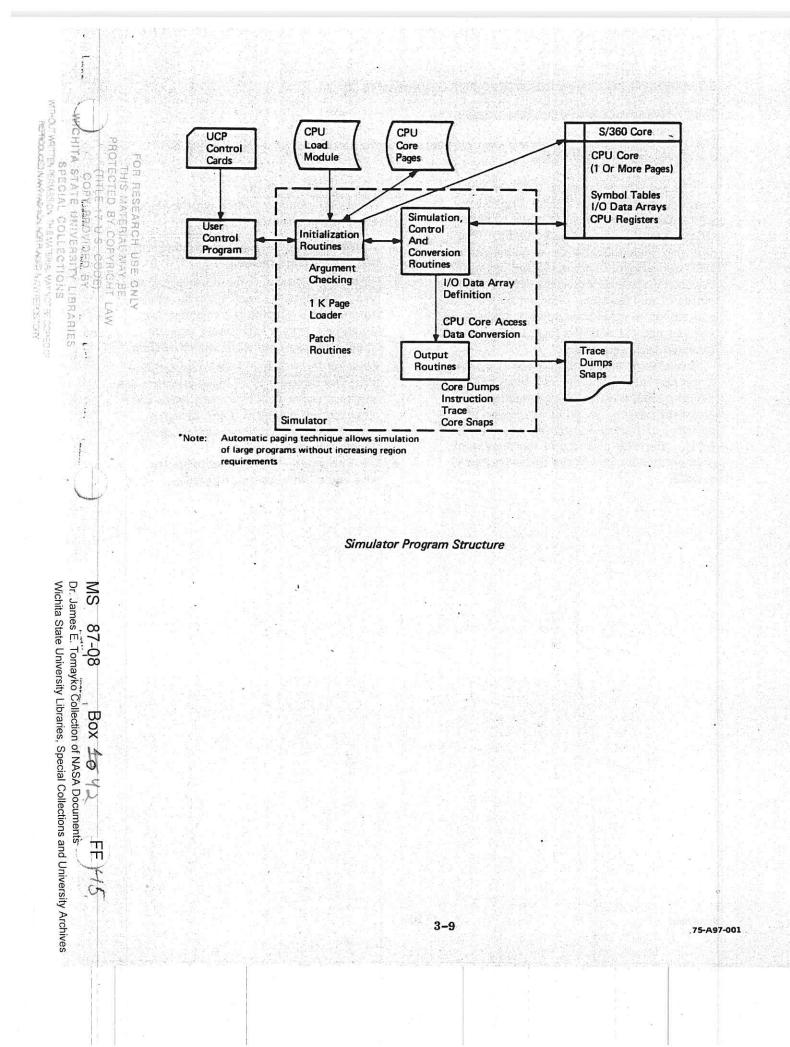

| 3.4   |                                               | 3-8                       |

| 3.5   | OPERATIONAL READINESS SELF-TEST PROGRAM (STP) | 3-10                      |

| 3.6   | FUNCTIONAL TEST PROGRAM (FTP)                 | 3-11                      |

| 4     | TUNCTIONAL DESCRIPTION                        | 4-1                       |

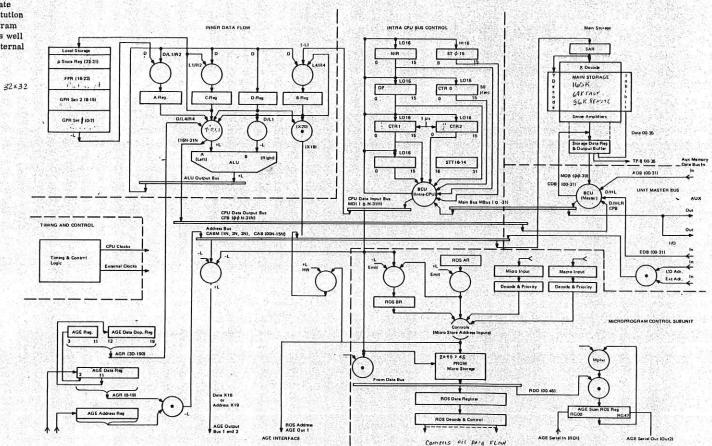

| 4.1   | CDU FUNCTIONAL OPERATION                      | 4-2                       |

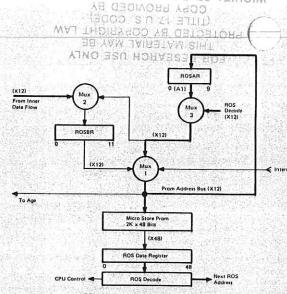

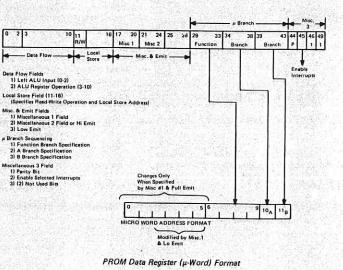

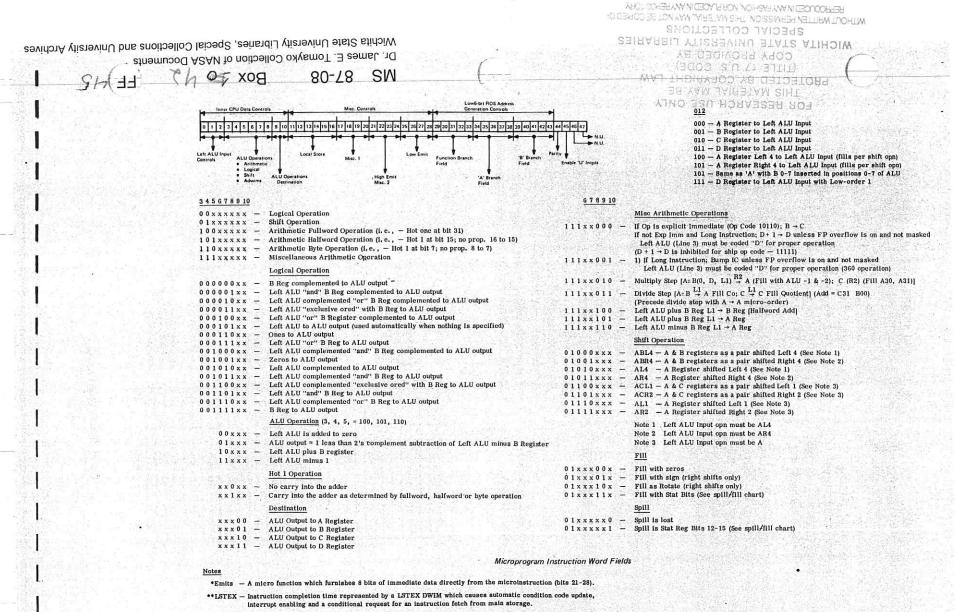

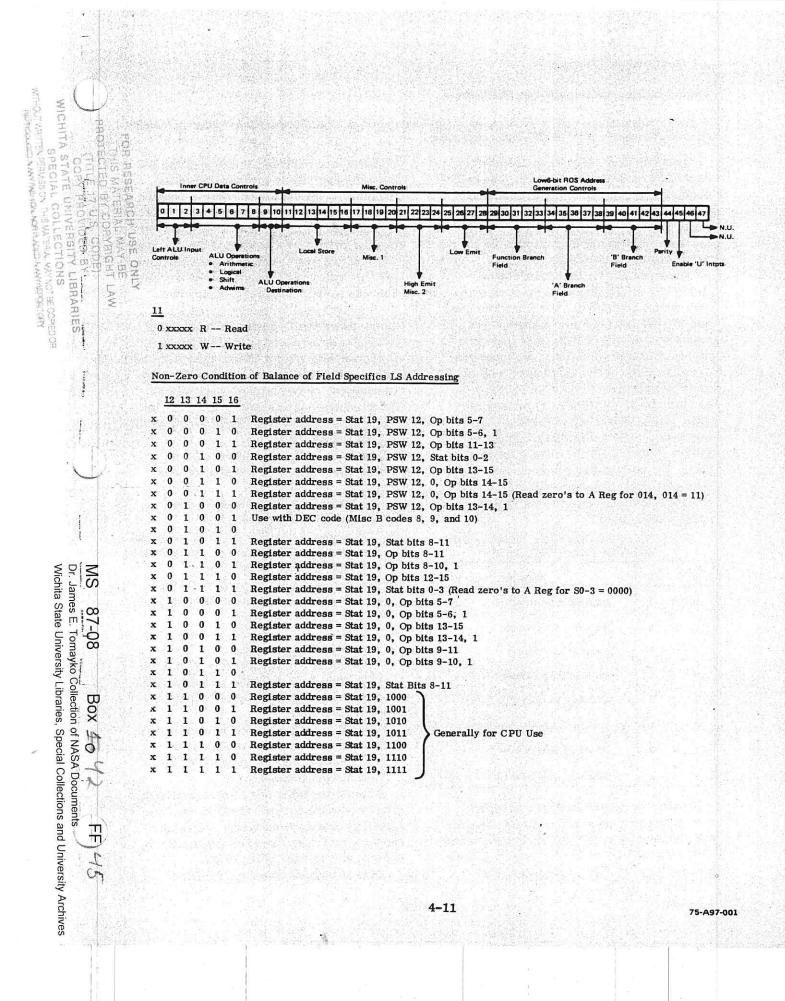

| 4.2   | MICROPROGRAM CONTROL                          | 4-4                       |

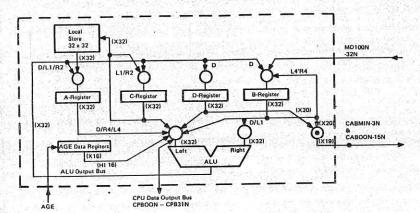

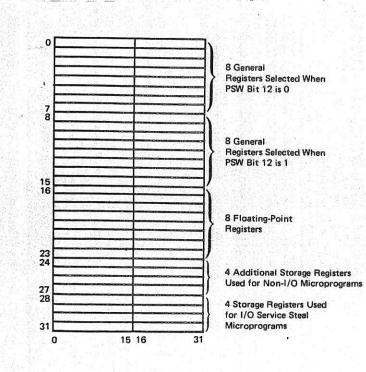

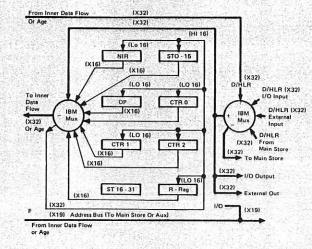

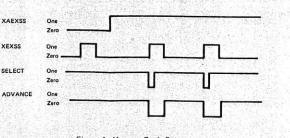

| 4.3   | INNER DATA FLOW                               | 4-0                       |

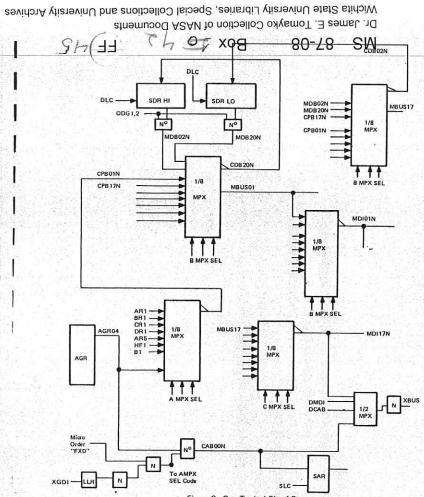

| 4.4   | DATA BUS CONTROL                              | 4-14                      |

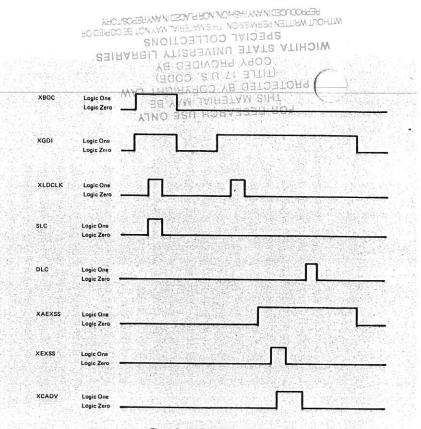

| 4.5   | TIMING AND CONTROL                            | 4-14                      |

| 4.6   | MAIN STOPACE                                  | 4-18                      |

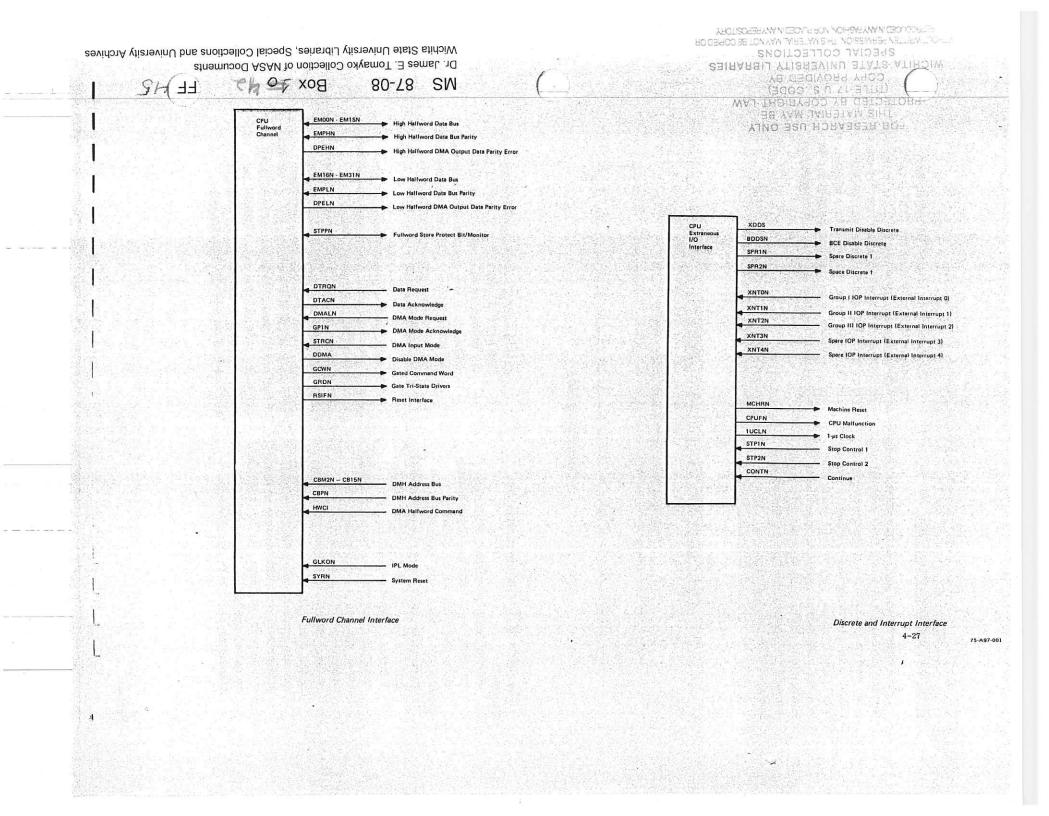

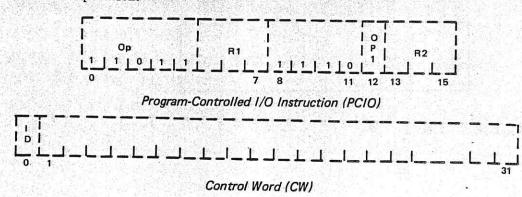

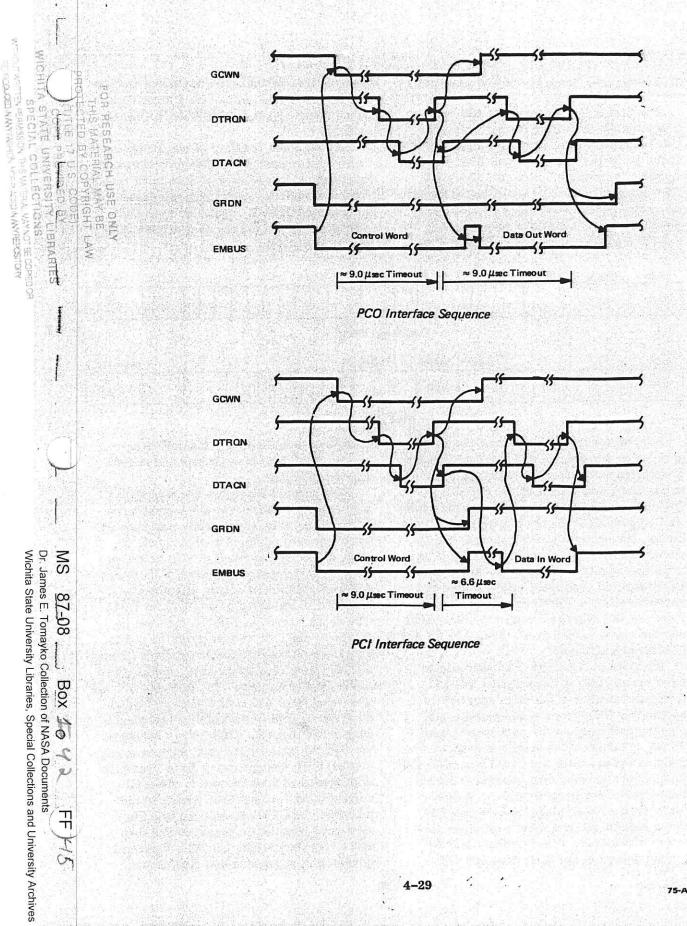

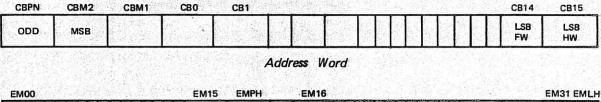

| 4.7   |                                               | 4-26                      |

| 4.8   | FAILT DETECTION                               | 4-30                      |

| 4.9   | ACE INTERFACE                                 | 4-38                      |

| 4,10  | DOWER SUPPLY                                  | 4-62                      |

| 4.11  | LOCIC TECHNOLOGY                              | 4-64                      |

| 5     | CDU MICROCODE OPERATIONS                      | 5-1                       |

| 5.1   | CDU MICBOCODE OPERATIONS                      | 5-4                       |

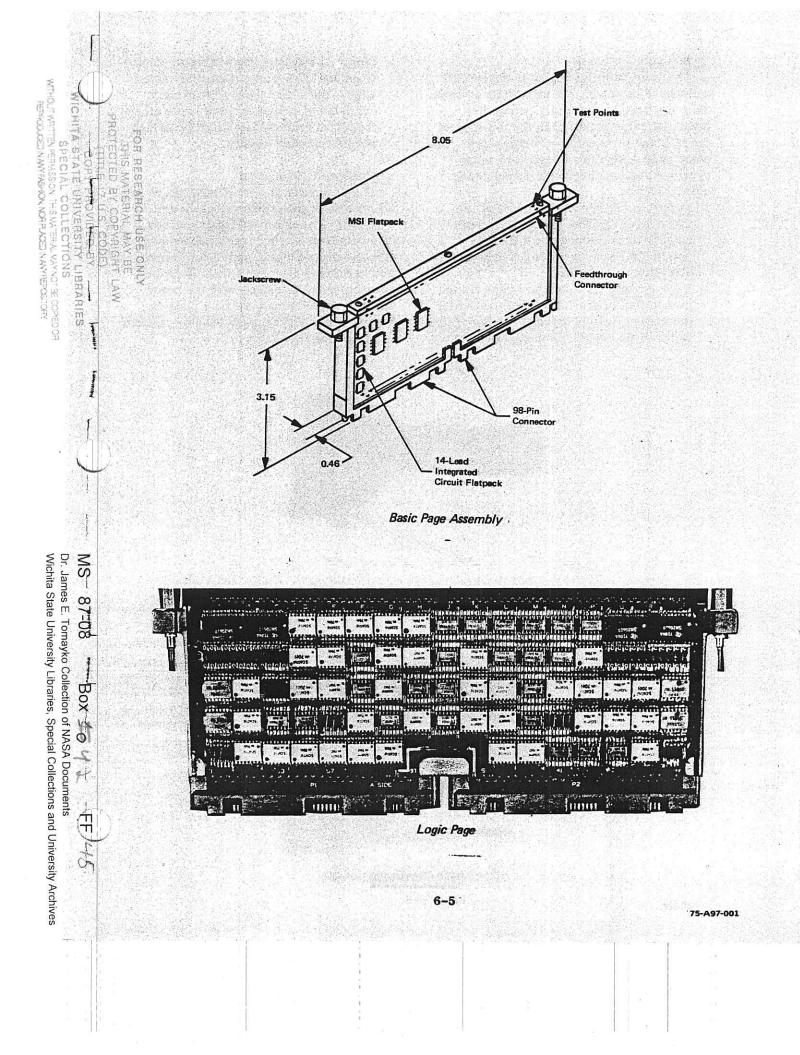

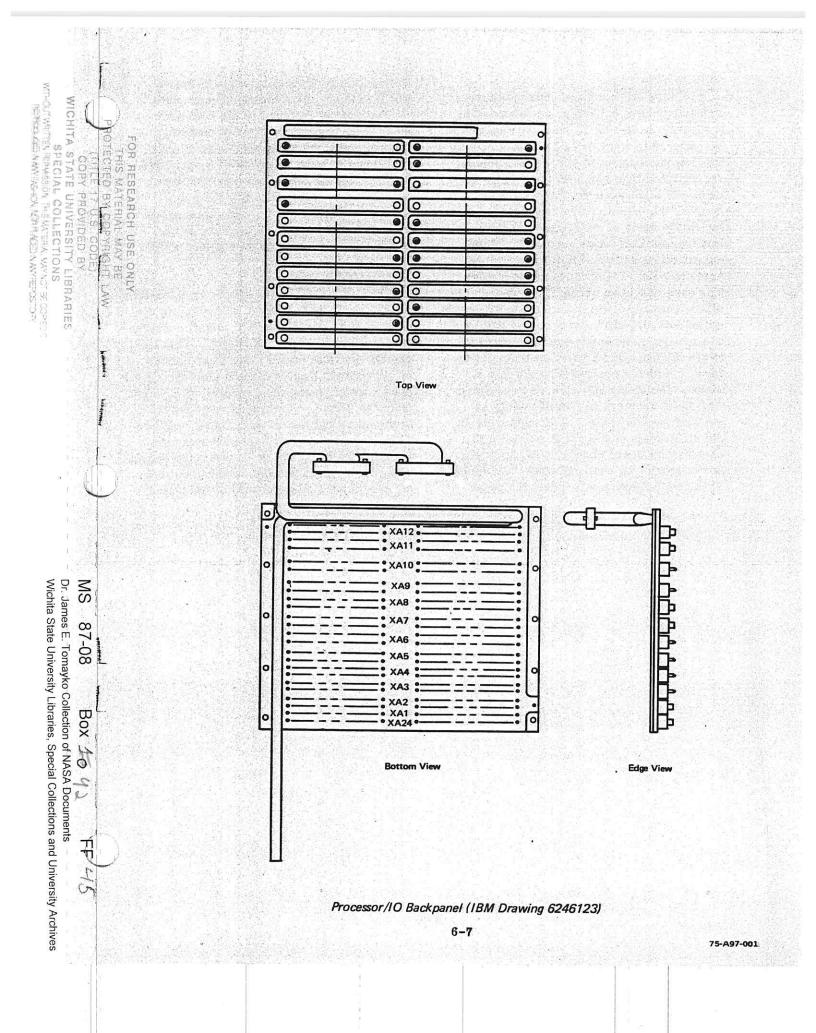

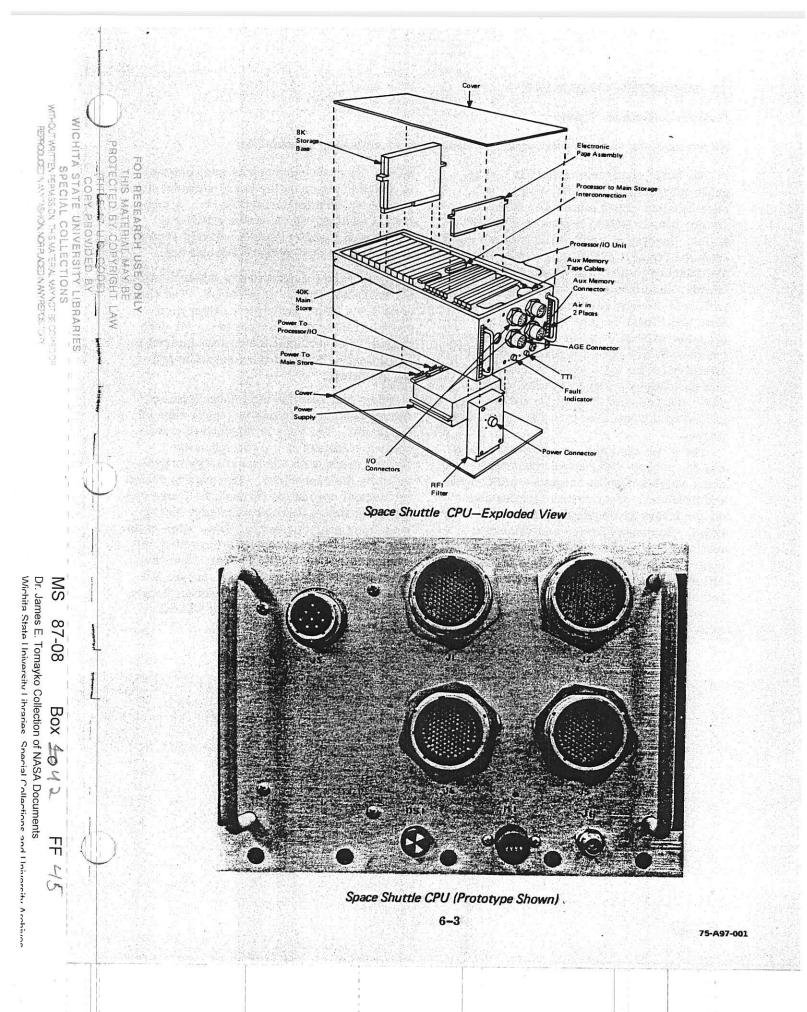

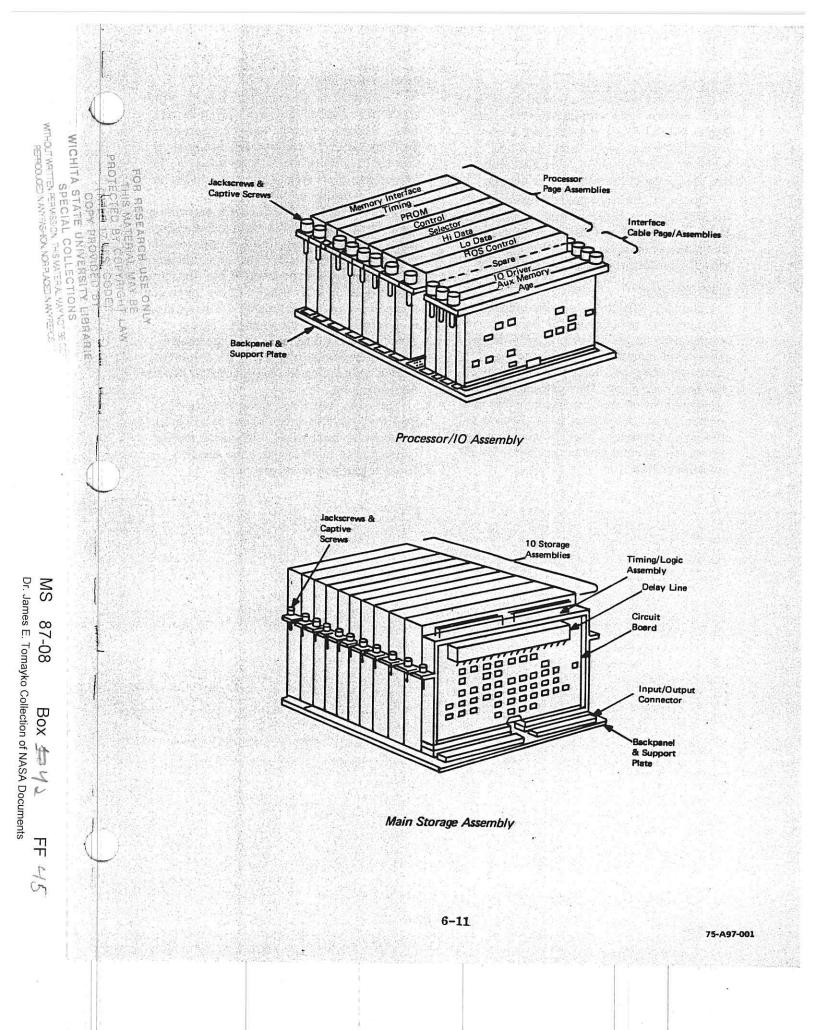

| 6     | MECHANICAL ASSEMBLY AND PACKAGING             | 6-1<br>6-2                |

| 6.1   | MECHANICAL DESIGN                             |                           |

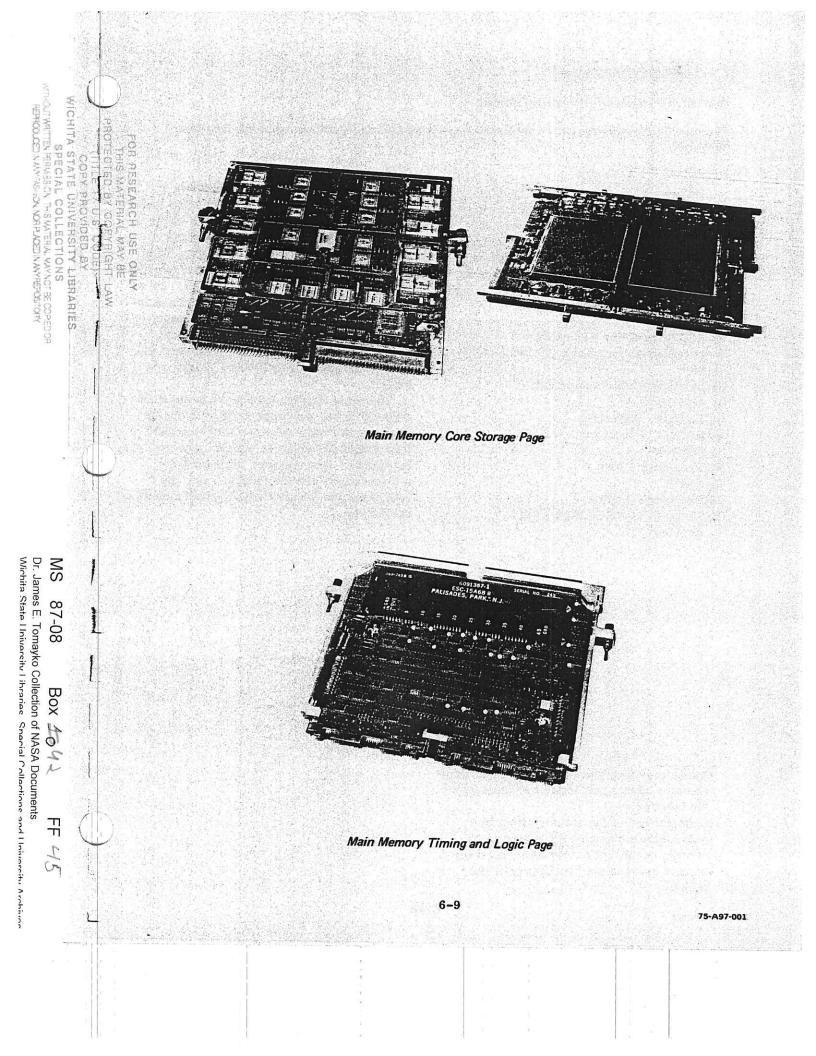

| 6.2   | SUBASSEMBLY PACKAGING                         |                           |

| 6.3   | ASSEMBLY DACKAGING                            | 6-10                      |

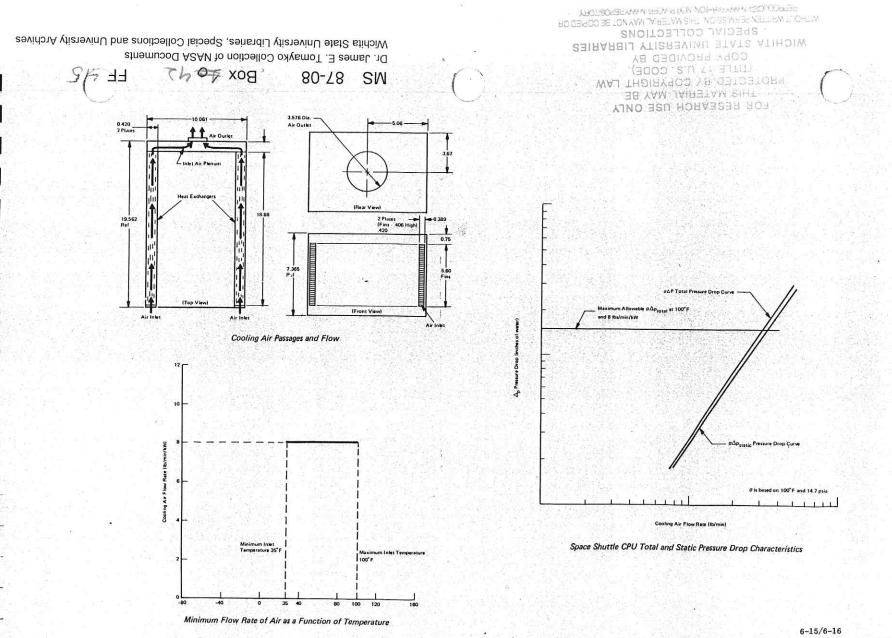

| 6.4   | THERMAL COOLING                               | 6-14                      |

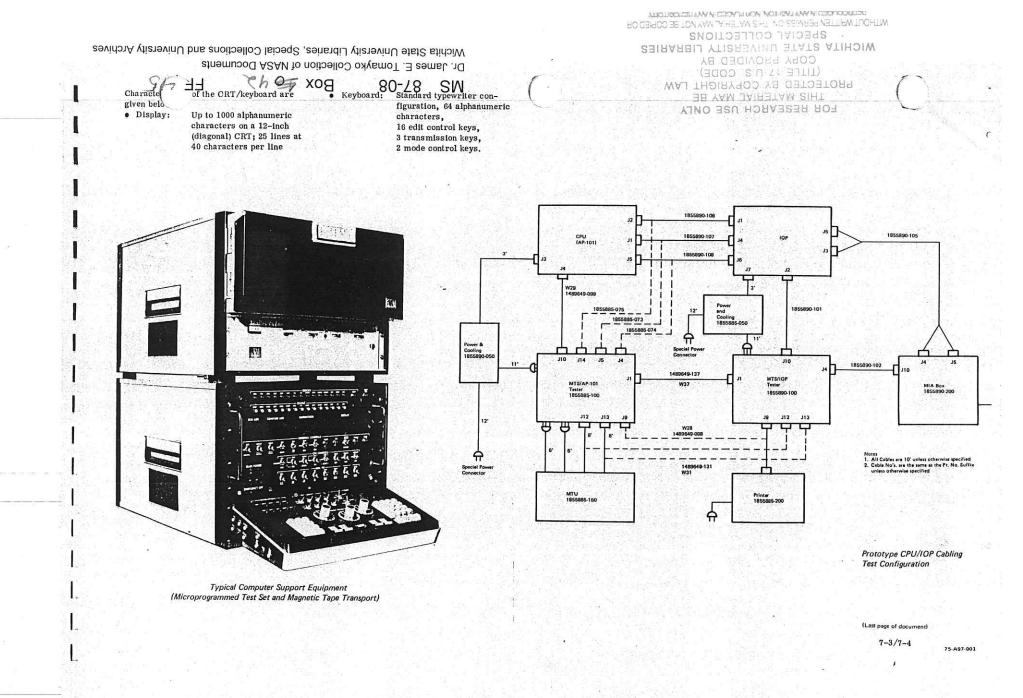

| 7     | MCDODDOCRAMMED TEST SET                       | . <i>1-</i> 1             |

| 7.1   | COMPUTER SUPPORT EQUIPMENT                    | . 7-2                     |

|       |                                               |                           |

Section 1

COPY

TATE UNIVERSITY LIBRARIES

Lanana...

.....

SW

87-08

Box 20 42

F

T'S

Dr. James E. Tomayko Collection of NASA Documents

SEARCH USE ONLY

### SUMMARY OF CHARACTERISTICS

1

# 1.1 SUMMARY OF CHARACTERISTICS

# The Space Shuttle Central Processor Unit is a General-Purpose Digital Computer

# The Central Processor Unit (CPU) provides real-time data processing.

The CPU is microprogram-controlled and provides 32-bit, parallel data flow, floating point arithmetic, and 40,960 36bit words of core main storage in a single LRU (line replaceable unit). The processing capability is 480,000 operations per second based on a typical distribution of instructions. The instruction repertoire includes short- and extended-precision floating point, conversion, input/output, fixed point, shifting, and logic operations.

The modular memory consists of pluggable modules containing 8192 18-bit halfwords. The failure of any module is detectable by self-test and built-in test hardware.

During periods of time when the CPU is operating below its processing capacity, power-switching places the memory in a low-power, quiescent mode when the memory is not addressed.

Support software and hardware features, such as halfword storage protect and interrupt masking, provide aids for debugging of software.

#### Machine Organization Type General-purpose, storedprogram, parallel, general register Organization Fixed-point, binary, fractional Floating-point, hexadecimal fraction Data Flow 32-bit, parallel Control Structure Microprogrammed Instruction Word 16-bit and 32-bit Lengths Fixed-Point Data 16-bit and 32-bit Word Lengths Floating-Point 32-bit and 64-bit Data Word Lengths **General Registers** Two selectable sets of eight (3 sets) 32-bit hardware registers for fixed-point operations; one set of eight 32-bit hardware registers for floating-point operations Number of 154 total Instructions Addressing Modes Base plus displacement, indexed, indirect, relative, extended, immediate and indirect address pointer Addressing Halfword resolution, 524, 288 Capability capacity Interrupt 35 interrupts, organized into Structure 19 priority levels and five classes

# CPU CHARACTERISTICS

75-A97-001

SW

87

-08

Box

0

## CPU CHARACTERISITCS (cont)

|               |                                      | Execution                                                                  | l'imes (µs)                        |

|---------------|--------------------------------------|----------------------------------------------------------------------------|------------------------------------|

|               |                                      | Register-<br>to                                                            | Storage-<br>to                     |

|               |                                      | Register                                                                   | Register                           |

| Fixed-Point:  |                                      | San and parts at                                                           |                                    |

| Add           |                                      | 1.2                                                                        | 1.8                                |

| Multiply      |                                      | 5.2                                                                        | 5.6                                |

| Divide        | Star Star                            | 8.8                                                                        | 9.4                                |

| Floating-Poir | <b></b>                              |                                                                            |                                    |

| Add (Short O  | Derand)                              | 2.8                                                                        |                                    |

| Multiply      | 1                                    | 6.4                                                                        | 3.0                                |

| Divide        |                                      | 9.8                                                                        | 6.6<br>10.0                        |

| and the state | Main                                 | Storage                                                                    | 10.0                               |

| Time          | State Market 1 at                    |                                                                            |                                    |

| Туре          | reado                                | om access,<br>ut (DRO) fei<br>core, nonvo                                  | rite mag-                          |

| Organization: | 2-1/2                                | D                                                                          |                                    |

| Capacity:     | data b<br>store<br>262, 14           | 6 36-bit wo<br>its, 2 parity<br>protect bits<br>14 words wit               | bits, 2<br>). Up to<br>th external |

|               | main s                               | storage unit:                                                              | 9                                  |

| Modularity:   | 8, 192<br>gable                      | 36-bit word<br>modules)                                                    | ls (2 plug-                        |

| Cycle Time:   | 800-ns<br>min. r                     | read/write<br>ead/modify                                                   | ; 1.2 µs<br>/write                 |

| Access Time:  | 375 ns                               |                                                                            |                                    |

| Addressable   |                                      |                                                                            |                                    |

| Unit:         | 16-bit                               | halfword                                                                   |                                    |

| Features:     | Power<br>power<br>ture co<br>parity, | transient pr<br>switching, t<br>mpensation,<br>halfword st<br>, interchang | empera-<br>halfword<br>orage       |

|               | Input/C                              | )utput                                                                     | Sakapel (1997)                     |

| /O Channel    | A startes                            | A state of the second                                                      | and the last                       |

| Туре:         | Micro<br>multir<br>duplex            | program-co<br>node, fullwo                                                 | ntrolled,<br>ord, half-            |

| Word Length:  | 32 bits                              | y + parity (2<br>protect (2)                                               | ) +                                |

PROTECT

PYRIGHT

>

MS

87-08

L

Box 东

50

(F

Dr. James E. Tomayko Collection of NASA Documents

RESEARCH USE ONLY

| . In                                                                                                           | put/Output (cont)                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

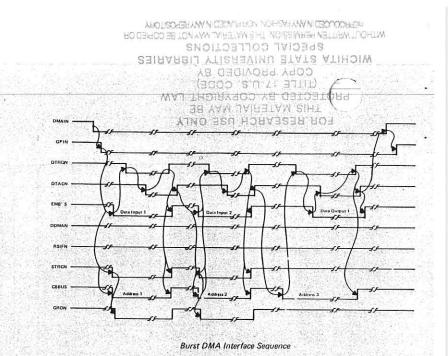

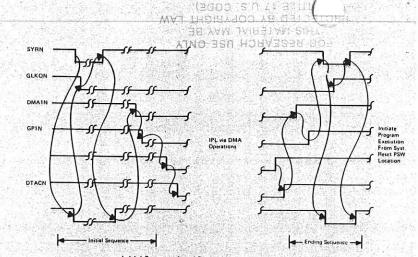

| Data Rates:                                                                                                    | 770,000 full words/s max<br>input (burst mode) and<br>625,000 full words/s max<br>input (normal mode)                                                                |

| Operating                                                                                                      |                                                                                                                                                                      |

| Modes:                                                                                                         | Program-controlled<br>direct I/O, externally<br>controlled DMA I/O                                                                                                   |

| External                                                                                                       |                                                                                                                                                                      |

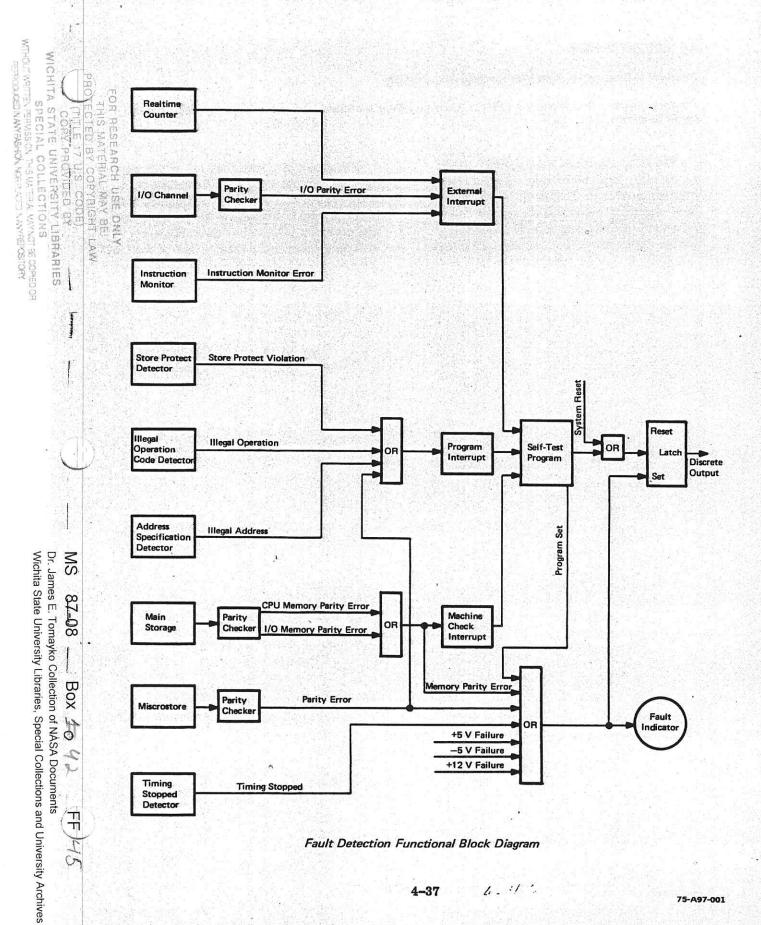

| Interrupts:                                                                                                    | 5 levels                                                                                                                                                             |

| Discretes:                                                                                                     | 4 outputs                                                                                                                                                            |

| Real-Time                                                                                                      |                                                                                                                                                                      |

| Clocks:                                                                                                        | Two 4295-second, with $1-\mu s$ resolution                                                                                                                           |

| The second s | Power System                                                                                                                                                         |

| Primary                                                                                                        |                                                                                                                                                                      |

| Power:                                                                                                         | 28 VDC                                                                                                                                                               |

| Regulated DC                                                                                                   |                                                                                                                                                                      |

| Output:                                                                                                        | +5, -5, +12 VDC                                                                                                                                                      |

| Features:                                                                                                      | Overvoltage, undervoltage,<br>and overcurrent protection:<br>power transient protection:<br>power sequencing                                                         |

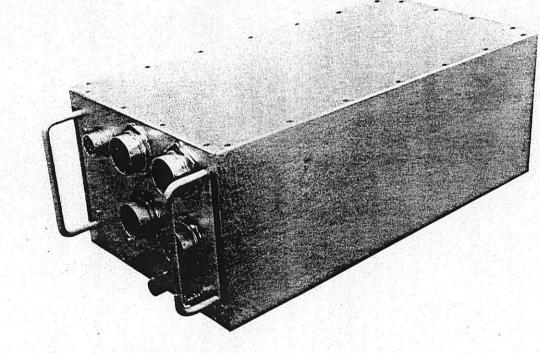

| Physic                                                                                                         | cal Characteristics                                                                                                                                                  |

| Weight:                                                                                                        | 57.9 lb (40K 36-bit words of main storage)                                                                                                                           |

| Size:                                                                                                          | Height 7.62, width 10.12,<br>depth 19.56 inches (full ATR)                                                                                                           |

| Volume:                                                                                                        | 0.87 ft <sup>3</sup>                                                                                                                                                 |

| Power:                                                                                                         | 350 W (50% memory duty<br>cycle, 40K main storage,<br>50% ones, 2 pages operate,<br>2 pages standby, 6 pages<br>quiescent) 2K x 48-bit<br>PROM and 72% PS efficiency |

| Construction:                                                                                                  | Plug-in modules                                                                                                                                                      |

| Cooling:                                                                                                       | Indirect air conductive, op-<br>tional blower available                                                                                                              |

| nvironment:                                                                                                    | Designed to meet MC 615-<br>0001 requirements                                                                                                                        |

DBY

BARI

T

-----

MS

87-08

L

Box 10

42

귀

ERIAL MAY BE COFYRIGHT

LAW

### ARCHITECTURE

1

### 2.1 ADDRESSING

### Sixteen-Bit Address with Expansion Capability

## Address field provides 64K halfword addresses with expansion to 512K halfwords.

The 16-bit address provides 64K halfword addresses. The addressing range is extended to 512K halfword locations by using PSW bits.

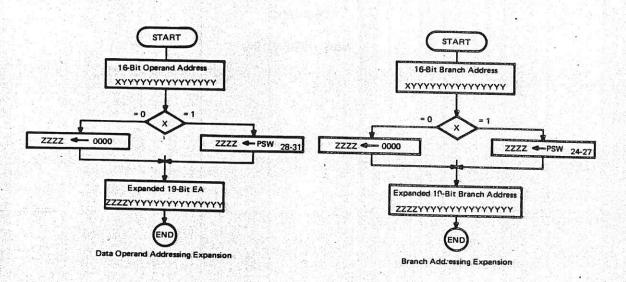

Address expansion to 19 bits is achieved by replacing the high-order bit of a 16-bit address with 4 bits, as shown below. Data operand addresses are extended to 19 bits by specifying either a 4-bit data sector register or an implied data sector register. When the high-order bit of a 16-bit data address is 1, a 4-bit data sector register (PSW bits 28 through 31) is selected to replace the high-order bit. When the highorder bit of a 16-bit data address is a 0, an implied data sector register containing 0000 is selected. Note that indirect addressing locates the indirect address pointer as if the pointer were a data operand. Branch addresses are extended to 19 bits in an equivalent manner. When the high-order bit of a 16-bit branch address is a 1, a 4-bit branch sector register (PSW bits 24 through 27) is selected to replace the high-order bit. When the highorder bit is a 0, an implied branch sector register containing 0000 is selected.

Expanded Addressing

SN

87-08

Box

3

9

# H The XOB 80-28 SW

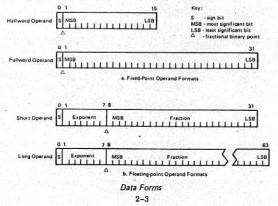

#### 2.2 DATA FORMATS

#### Flexible Formats Improve Storage Efficiency and Performance

Fixed-point data forms are halfword (16 bits) or fullword (32 bits), while floating-point formats are 32 bits and 64 bits, providing the equivalent of 6.2 and 15.5 decimal digits of precision, respectively.

Fixed-point data representation is two'scomplement-fractional with the binary point immediately to the right of the sign bit. A halfword is 15 bits plus sign; a fullword is 31 bits plus sign. In fractional data representation, bit position 1 represents the fraction  $2^{-1}$ , bit position 2 represents  $2^{-2}$ , and bit position 31 represents  $2^{-31}$ . Fixedpoint operands may be located on any halfword boundary.

The floating-point data formats are 32 bits and 64 bits long, differing only in the size of the fraction. The 32-bit length provides sign plus 24 bits of fraction (6 hexadecimal digits), equivalent to 6, 2 decimal digits. The 64-bit length provides sign plus 56 bits of fraction (14 hexadecimal digits), equivalent to 15, 5 decimal digits. In both lengths, bit position 0 is the sign of the fraction. Bit positions 1 through 7 of both formats constitute the exponent, which represents a hexadecimal (16) power and is expressed in excess 64 notation.

The value of a floating-point number is given by the product of the fraction times the power of 16 exponent. Since the exponent represents a hexadecimal base, the floating-point fractions are hexadecimally normalized; i.e., a normalized fraction has a nonzero hexadecimal digit in the first four bits of the fraction. Maximum precision is preserved in addition, subtraction, multiplication, and division, because all results are normalized.

The exponent field represents numbers from 0 through 127. To accommodate positive and negative exponents, the true exponent is determined by subtracting 64 from the value shown in the exponent field. This use of excess 64 notation permits an exponent range of -64 through +63 and a range of magnitude for normalized floatingpoint data of

- In short precision  $16^{-65 \le} M^{\le} (1-16^{-6}) \times 16^{63}$

- In long precision  $16^{-65} \le M \le (1 - 16^{-10}) \times 16^{63}$

- Thus, giving a range of approximately  $5.4 \times 10^{-79} \le M \le 7.2 \times 10^{75}$

The hexadecimal notation provides improved performance through shifting preand post-normalization operations four bits at a time.

75-A97-001

Wichita State University Libraries, Special Collections and University Archives Dr. James E. Tomayko Collection of NASA Documents

format bit, in conjunction with X and IA, specifies various addressing mode

Instruction Formats

2-4

RO DEROO BE TOWARM INTERTAN SIMT VOISPINEER VETTOWIN IN SPECIAL COLLECTIONS SEIRARBIJ YTIEREVINU ETATE ATIHOIW COPY PROVIDED BY (ados is nizi sobe) WAJ THZIPA 00 Y8 031031089 BRAYN IVHELVIA SIHD

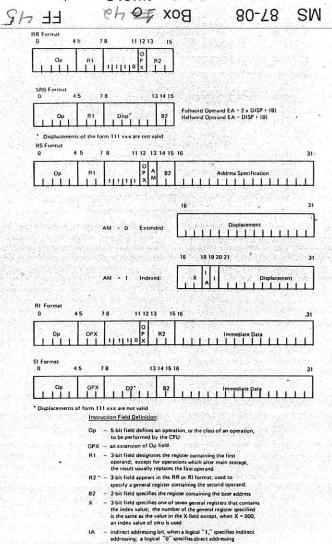

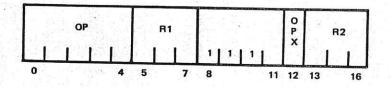

### 2.3 INSTRUCTION FORMATS

### POR RESEARCH USE ONLY Five Formats Provide Storage Efficiency and Speed

Two 16-bit formats permit storage effiency, while three 32-bit formats enhance execution speed and provide . xtensive addressing flexibility.

Note: The instruction formats discussed in this section are illustrated on fold-out sheets (see page 2-8) for ease of reference during the following discussions.

The short Register-to-Register (RR) and Short Register-to-Storage (SRS) formats minimize the amount of instruction storage required for a given problem. In addition, two short instructions can be read from storage with one storage access. RR format instructions execute operations when both operands are in general registers; this format has the shortest execution times since no storage access is required for operands. The SRS format executes operations when one operand is in a general register and the other is in storage. The SRS format is limited to addressing storage locations that are 56 or less fullword or halfword locations from the address in a base register. The assembler automatically uses the halfword length SRS format unless the fullword format is specified by the programmer.

#### Indexed Addressing

Indexed addressing is specified by RS format bit 13 equal to 1. This addressing mode contains three additional instruction fields which contribute to address generation as follows:

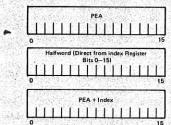

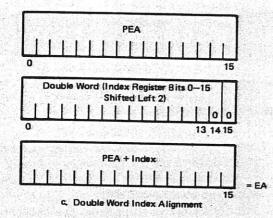

- X This 3-bit field specifies one of seven general registers containing the index. Indexing is not performed when X is equal to 000. An index is contained in the upper halfword of a general register. The index is automatically aligned with the preliminary effective address (PEA).

- General register contents can be used interchangeably as either a base or an index or both. When indirect addressing is specified, indexing follows indirect addressing.

a. Halfword Index Alig

The fullword Register-to-Storage (RS) format has two modes of operation - ex> tended addressing (RS bit 13 = 0) and indexed addressing (RS bit 13 = 1). Extended addressing provides a full 16-bit address displacement, either used as the absolute operand address or added to the address in a base register. Indexed addressing provides an 11-bit address displacement.

= EA

The Register Immediate (RI) and Storage Immediate (SI) instruction formats execute operations where the first operand is contained in the instruction. The second operand is in a general register for the RI format and in main storage for the SI format. An operand fetch operation is eliminated by using immediate instructions.

4

ONLY

MS

87-08

I

Box So

2

9

Ŧ

- IA This format bit, when a one, specifies indirect addressing. Indirect addressing is not performed when this bit is zero.

- I This format bit, in conjunction with X and IA, specifies various address modes which are explained below.

The development of the EA for the indexed mode of operand addressing is explained in detail in the subsequent steps:

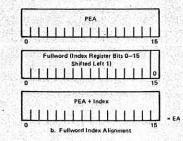

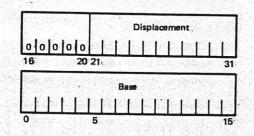

1) Indexed addressing is specified by RS format bit 13 (AM) equal to 1. This addressing mode provides an 11-bit displacement. The base and displacement are aligned when indexed addressing is performed.

Displacement Alignment for Indexed Addressing

The displacement is aligned so that bit 31 corresponds to base or index bit 15 and displacement bit 21 corresponds to base or index bit 5. The displacement is expanded to 16 bits by appending five leading zeros.

- 2) If B is not equal to 11, the 16-bit base, contained in the high order half of the specified register, is added to the aligned displacement. This results in a pre-liminary effective address (PEA) where-by the PEA = (B) + Displacement.

If B = 11, the aligned displacement is added to zero. This result is the pre-liminary effective address (PEA), where-by the PEA = Displacement.

- 3) If the X field is all zeros, IA (bit 19) is a zero and I (bit 20) is a zero, then the 16-bit result of Step 2 is added to the contents of the instruction counter (IC) to form the 16-bit EA whereby EA = IC + PEA. (This EA is then expanded to a 19-bit EA.)

- 4) If the X field is all zeros, IA (bit 19) is a zero and I (bit 20) is a one, the 16-bit result of Step 2 is subtracted from the contents of the IC to form the 16-bit EA whereby EA = IC PEA. (This EA is then expanded to a 19-bit EA.)

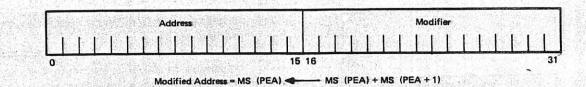

- 5) If the X field is all zeros, IA (bit 19) is a one and I (bit 20) is a zero, then Indirect Addressing is performed. The 16-bit result of Step 2 is expanded to a 19-bit address and is used as the address of a main-storage halfword. This halfword is then fetched and expanded to 19-bits by using expanded addressing to form the EA. EA = MS (PEA). Functional equivalency to preindexing capability can be obtained through modification of the base.

- 6) If the X field is all zeros, IA (bit 19) is a one and I (bit 20) is a one, Indirect Addressing is performed as described in Step 5. Then, storage modification is automatically performed. The indirect address is contained in a full word and must have an even address. A modifier is contained in bits 16 through 31. An address is contained in bits 0 through 15. The modifier is added to the address and the resulting modified address replaces bits 0 through 15.

The Contents of Storage Modification Word

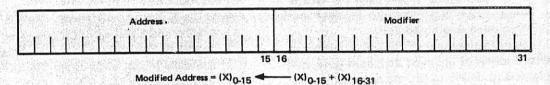

- 7) If the X field is not all zeros, IA (bit 19) is a zero and I (bit 20) is a zero, the most significant 16-bits of the general registers specified by the X field are aligned, and then added to the 16-bit result of Step 2 to form the 16-bit EA. (This EA is then expanded to a 19-bit EA.)

- 8) If the X field is not all zeros, IA (bit 19) is a zero and I (bit 20) is a one, the most significant 16 bits of the general register

specified by the X field are aligned, and then added to the 16-bit result of Step 2 to form the 16-bit EA. (This EA is then expanded to a 19-bit EA.)

The figure below illustrates the address and modifier format in the index register. The modifier is added to the address and the resulting modified address replaces bits 0 through 15 of index register after the EA is determined.

### The Contents of Index Register X

9) If the X field is not all zeros, IA (bit 19) is a one and I (bit 20) is a zero, Indirect Addressing (IA) with post-indexing is performed. The 16-bit result of Step 2 is expanded to a 19-bit address and is used to fetch a main-storage halfword. The index contained in the general register by X is aligned and then added to the fetched halfword to form the 16-bit EA. This EA is then expanded to a 19-bit EA by using expanded addressing. Func-

tional equivalency to preindexing capability can be obtained through modification of the base.

- 10) If the X field is not all zeros, IA (bit 19) is a one and I (bit 20) is a one, a direct addressing mode is defined using a 32-bit fullword indirect pointer as follows:

- a) First, the PEA from Step 2 must locate a fullword indirect address pointer, with the format as follows:

Fullword Indirect Address Pointer

75-A97-001

SN

87-08

Box

3

R

YIND SECHORA DE CULY HORASER NA CULY WAI THERANAL SIM WAI THERANAL SIM WAI THERANAL THERAL WAI THERAL COPY PROVIDED SECTIONE COPY PROVIDED SECTIONE COPY FROM OF THE CULY SECTIONE COPY FROM OF THE CULY COPY FROM OF TH

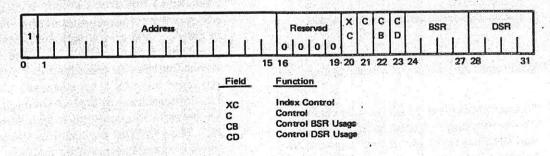

#### b) If C (bit 21) equals 0, XC (bit 20) equals 1, and the instruction is not a branch type instruction, the 19-bit EA equals the 4-bit DSR with the 15bit address field appended. When C (bit 21) equals 0, XC (bit 20) equals 0, and the instruction is not a branch type instruction, the 19-bit EA equals the 4-bit DSR with the 15-bit address field appended, with the result added to the index value in indexing register X. The current PSW's DSR is not changed. If C (bit 21) equals 0 and the instruction is a branch type instruction, the current PSW's BSR in conjunction with IA pointer bits 0 through 15 will be used to form the BA. If XC = 0, postindexing will occur,

SHAT

Wichita State University Libraries, Special Collections and University Archives

ChOF XOB

Dr. James E. Tomayko Collection of NASA Documents

- c) If C (bit 21) equals 1 and the instruction is a branch type instruction, the BSR and DSR fields may selectively replace the corresponding fields in the current PSW, based on the CB and CD bit values as follows:

- CB CD Result

- 0 0 Use current PSW's BSR to form the BA.

- 0 1 Replace the current PSW's DSR with this DSR. Form the BA normally.

- 1 0 Replace the current PSW's BSR with this BSR before forming the BA.

- 1 1 First, replace the current PSW's DSR with this DSR. Then, replace the current PSW's BSR with this BSR before forming the BA.

d) When C (bit 21) equals 1 and XC (bit 20) equals 1, postindexing is not performed. When C (bit 21) equals 1 and XC (bit 20) equals 0, the BA calculation includes a final addition of the index value in index registers X. If C (bit 21) equals 1 and the instruction is not a branch, the 19-bit EA equals the current PSW's DSR and the 15-bit field appended. If XC = 0, postindexing will occur.

80-78. 2M

The results of indexed mode RS operations normally replace the first operand except for store operation where the first operand replaces the second operand. The second operand is unaltered for nonstore operations, and the first operand is unaltered for store operation.

Effective address generations for the various instruction formats are summarized in the EA summary chart.

#### EFFECTIVE ADDRESS GENERATION SUMMARY CHART

|                                                |                                                                                                                                     |                                                                                                                                 |                                                         | 121                                    | RS Format                                                                                           |                                                                                                                                  |  |  |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                | SRS, SI<br>Formats                                                                                                                  | Extended                                                                                                                        |                                                         | Indexed Addressing (AM=1)              |                                                                                                     |                                                                                                                                  |  |  |

|                                                |                                                                                                                                     | Addressing<br>(AM=0)                                                                                                            | IA.                                                     | I                                      | X=000                                                                                               | X=000                                                                                                                            |  |  |

| 1.39                                           | 经总结局的产                                                                                                                              | and State                                                                                                                       | 201                                                     | SPE                                    | P                                                                                                   | EA=(B)+DISP                                                                                                                      |  |  |

| B≠11                                           | EA=(B)+DISP                                                                                                                         | EA=(B)+DISP                                                                                                                     | 0<br>0<br>1                                             | 0<br>1<br>0                            | EA-IC+PEA<br>EA=IC-PEA<br>EA=MS(PEA)<br>EA=MS(PEA)**                                                | $EA=(X)_{0-15}$ 'PEA<br>$EA=(X)_{0-15}$ 'PEA<br>$EA=MS(PEA)+(X)_{0-15}$<br>$EA=MS(PEA)$ ***+(X)_0-                               |  |  |

| Sec. Sec.                                      | a Constant of the                                                                                                                   |                                                                                                                                 |                                                         |                                        | 31. AP 1988                                                                                         | PEA=DISP                                                                                                                         |  |  |

| B=11                                           | EA=(B)+DISP                                                                                                                         | EA=DISP                                                                                                                         | 0<br>0<br>1<br>1                                        | 0<br>1<br>0<br>1                       | EA=IC+PEA<br>EA=IC-PEA<br>EA=MS(PEA)<br>EA=MS(PEA)**                                                | EA=(X) <sub>0-15</sub> +PEA<br>EA=(X) <sub>0-15</sub> +PEA<br>EA=MS(PEA)+(X) <sub>0-15</sub><br>EA=MS(PEA)***+(X) <sub>0-1</sub> |  |  |

| Definitio                                      | ons                                                                                                                                 |                                                                                                                                 |                                                         |                                        |                                                                                                     |                                                                                                                                  |  |  |

| RN<br>(B)<br>B<br>MS()<br>DISP<br>X<br>(X)0-15 | Contents of<br>B field of SI<br>Contents of<br>Displaceme                                                                           | RS, SI, or RS fo<br>the main storage                                                                                            | eral re<br>rmat in<br>e locati                          | gister<br>struct                       |                                                                                                     | ter B                                                                                                                            |  |  |

| IA<br>I<br>IC                                  | Most signifi<br>aligned,<br>AM (addres<br>IA (indirect<br>addressing<br>I bit of RS for<br>Instruction<br>Automatic I               | S format instruc<br>cant halfword (b<br>sing mode) field<br>address) field o<br>ormat instructio<br>counter<br>ndex Modificatio | tion wi<br>its 0-1<br>of RS i<br>f RS fo<br>n with      | 5) of ti<br>format<br>rmat l           | xed mode of addre<br>ac content of index                                                            | register X automatically                                                                                                         |  |  |

| AM<br>IA<br>I<br>IC<br>•                       | Most signifi<br>aligned.<br>AM (addres<br>IA (indirect<br>addressing<br>I bit of RS fi<br>Instruction<br>Automatic I<br>Automatic S | S format instruc<br>cant halfword (b<br>sing mode) field<br>address) field o<br>ormat instructio<br>counter                     | tion wi<br>its 0-1<br>of RS 1<br>f RS fo<br>n with<br>n | 5) of ti<br>format<br>rmat i<br>indexe | xed mode of addre<br>ne content of index<br>instruction<br>nstruction with the<br>d mode of address | ssing<br>register X automatically<br>indexed mode of                                                                             |  |  |

#### GENERAL REGISTER FUNCTION ASSIGNMENTS

| General            | Register Function |                  |       |  |  |  |  |

|--------------------|-------------------|------------------|-------|--|--|--|--|

| Register<br>Number | Operand           | Base             | Index |  |  |  |  |

| 0                  | 000               | 000              | None  |  |  |  |  |

| 1                  | 001               | 001              | 001   |  |  |  |  |

| 2                  | 010               | 010              | 010   |  |  |  |  |

| 3                  | 011               | 011 or None      | 011   |  |  |  |  |

| 4                  | 100               |                  | 100   |  |  |  |  |

| 5                  | 101               |                  | 101   |  |  |  |  |

| 6                  | 110               | 방법의 억식가지만        | 110   |  |  |  |  |

| 7                  | 111               | the state of the | 111   |  |  |  |  |

75-A97 001

2-7

### 2.4 INSTRUCTION REPERTOIRE

### Comprehensive Instruction Repertoire Enhances Programmability and Performance

The instruction repertoire consists of 154 operations in seven classes. A total of 480,000 fixed-point operations/second can be achieved using a typical instruction mix.

The instruction set was selected to enhance programmability and offers a balanced and comprehensive instruction repertoire. Since the CPU uses a microprogram control structure, the machine personality need not be permanent; that is, the instruction set can be modified or changed as necessary.

The instruction set along with typical execution times in microseconds is as follows:

SN

87-08

Box

ないろ

FF 4

### INSTRUCTION REPERTOIRE

the second

Contraction of the

PEDVID

LIBHAHTES

Support of

1

SW

.---- 80r28·

Box to Va

FF/45

MAY BE

LAW

|                                    |        | Execution Time (µs) |                             |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                         |

|------------------------------------|--------|---------------------|-----------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Fixed-Point Operations             | Format | Even                | Odd<br>NOK                  | Odd<br>NOK              | Even<br>100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Even<br>200<br>EMU                      |

| Add                                | RR     | 1.2                 | 0.8                         | 1.2                     | 1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.4                                     |

| Add                                | SRS    | 1.8                 | 1.4                         | 1.8                     | 2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.2                                     |

| Add                                | RS     | 1.8                 | 2.0                         | 2.8                     | 2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.3                                     |

| Add Halfword                       | SRS    | 1.8                 | 1.4                         | 1.8                     | 2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.2                                     |

| Add Halfword                       | RS     | 1.8                 | 2.0                         | 2.8                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.3                                     |

| Add Halfword Immediate             | RI     | 1.8                 | 2.0                         | 2.8                     | 1.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.0                                     |

| Add to Storage                     | RS     | 2.3                 | 2.4                         | 3.2                     | 2.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.9                                     |

| Compare                            | RR     | 1.6                 | 1.2                         | 1.6                     | 1.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.8                                     |

| Compare                            | SRS    | 2,2                 | 1.8                         | 2.2                     | 2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.6                                     |

| Compare                            | RS     | 2.2                 | 2.4                         | 3.2                     | 2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.6                                     |

| Compare Between Limits (Note 1)    | RR     | 5.4                 | 5.0                         | 5.4                     | 5.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.8                                     |

| Compare Halfword                   | SRS    | 2,2                 | 1.8                         | 2.2                     | 2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.6                                     |

| Compare Halfword                   | RS     | 2.2                 | 2.4                         | 3.2                     | 2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.6                                     |

| Compare Halfword Immediate         | RI     | 2.2                 | 2.4                         | 3.2                     | 2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.4                                     |

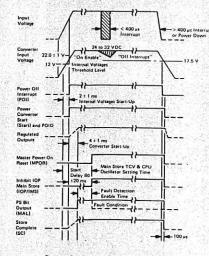

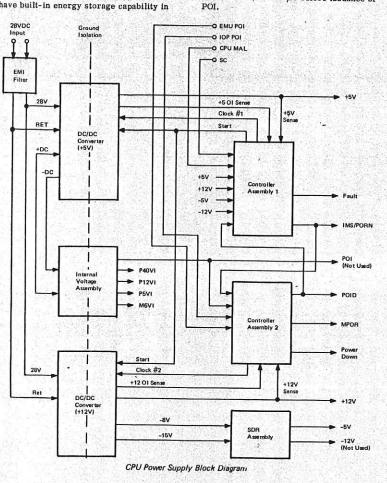

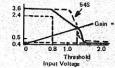

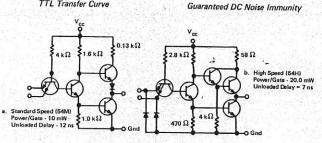

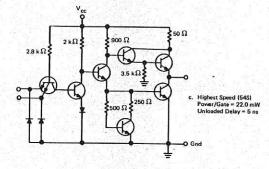

| Compare Immediate with Storage     | SI     | 2.6                 | 2.8                         | 3.6                     | 2.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.0                                     |