# Instrumentation and Communications Officer (INCO) Systems Briefs

Systems Division

Communications Systems Branch

Revision G March 1, 2006

National Aeronautics and Space Administration

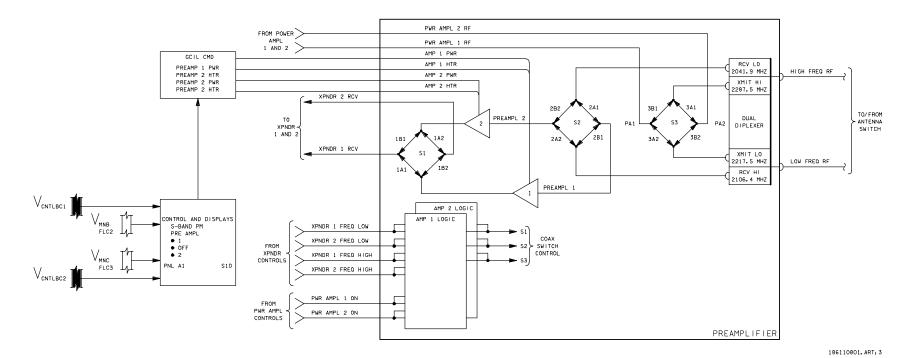

Lyndon B. Johnson Space Center Houston, Texas

#### Mission Operations Directorate

## Instrumentation and Communications Officer (INCO) Systems Briefs

Revision G

March 1, 2006

Prepared by

Original approval obtained

Eric Wingrove

Communications Systems Group

Approved by

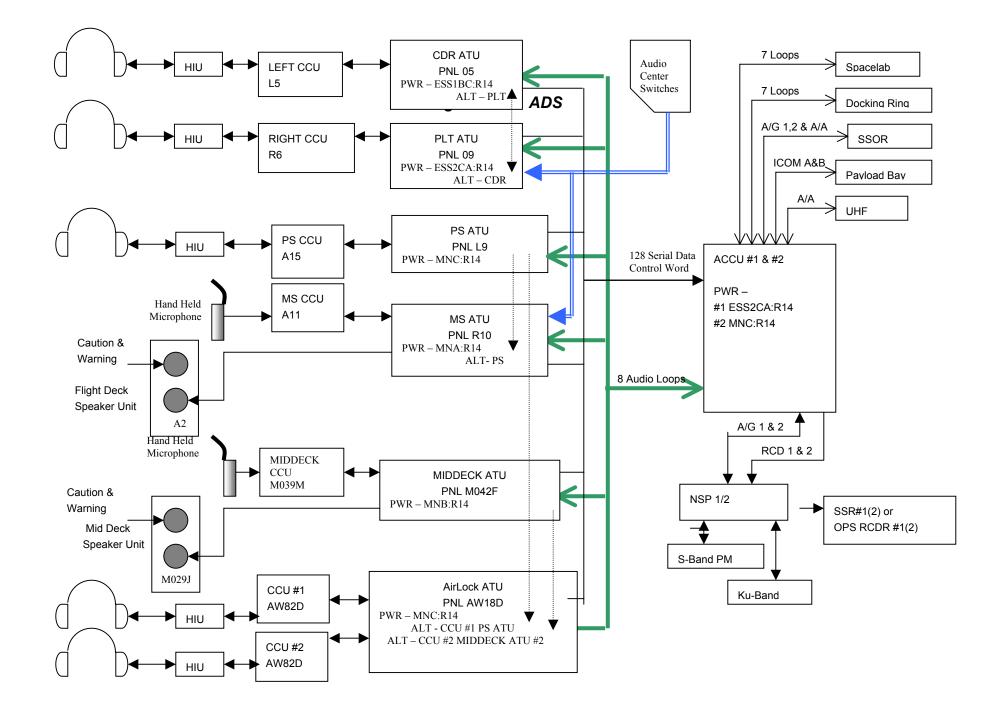

Original approval obtained

John McKinnie

Group Lead/Communications Systems Group

Original approval obtained

Ray B. Lachney

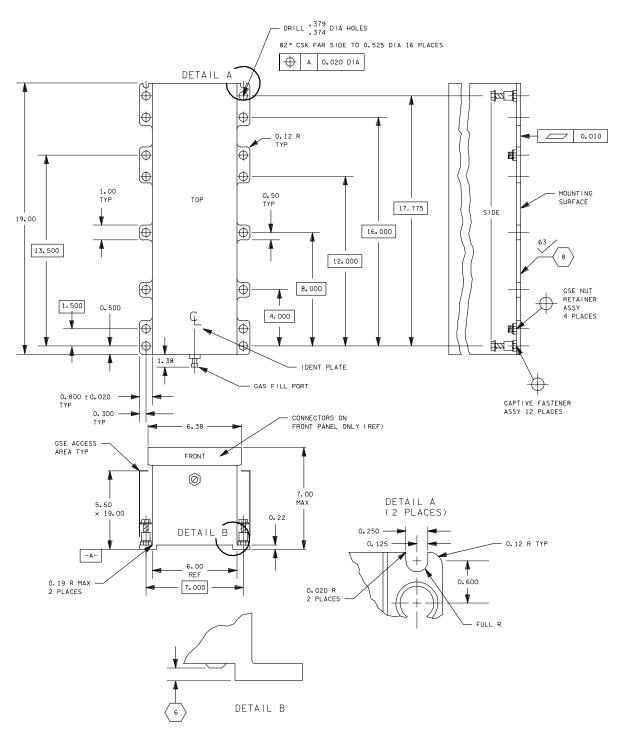

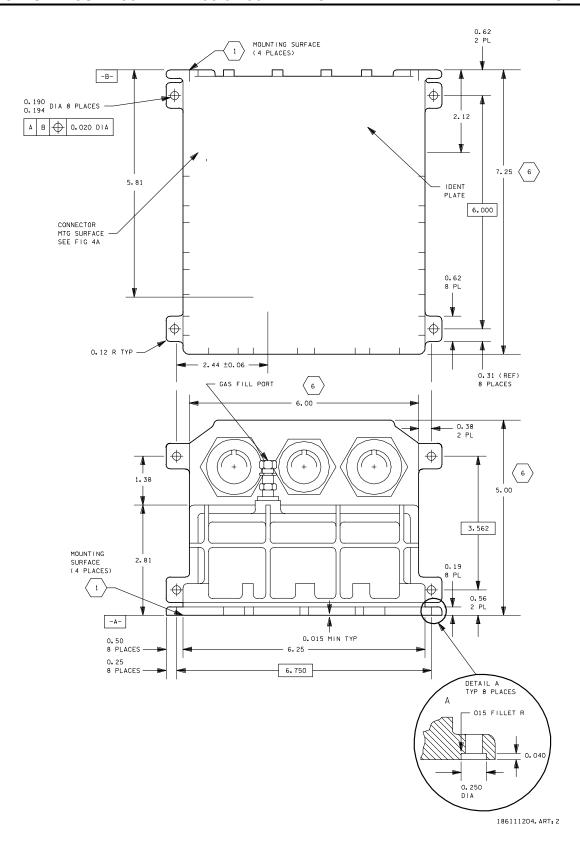

Chief, Communications Systems Branch

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION LYNDON B. JOHNSON SPACE CENTER HOUSTON, TEXAS

#### **CONTENTS**

| Section |                                                                                                       | Page |

|---------|-------------------------------------------------------------------------------------------------------|------|

| 1       | ONBOARD COMMAND SYSTEM                                                                                | 1-1  |

| 2       | GROUND COMMAND SYSTEM DESCRIPTION                                                                     | 2-1  |

| 3       | S-BAND PHASE MODULATION SYSTEM                                                                        | 3-1  |

| 4       | S-BAND TRANSPONDER                                                                                    | 4-1  |

| 5       | S-BAND PREAMPLIFIER                                                                                   | 5-1  |

| 6       | S-BAND POWER AMPLIFIER                                                                                | 6-1  |

| 7       | S-BAND ANTENNA SYSTEM                                                                                 | 7-1  |

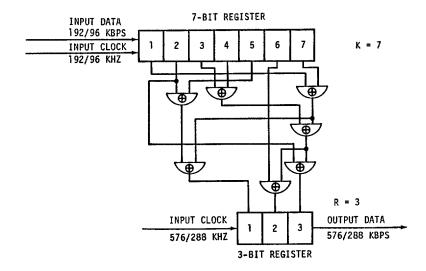

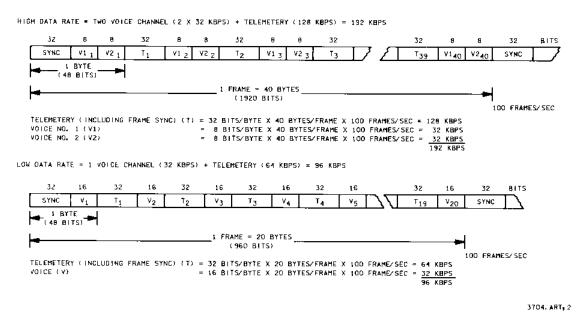

| 8       | S-BAND FREQUENCY MODULATION SYSTEM                                                                    | 8-1  |

| 9       | KU-BAND RADAR/COMMUNICATIONS SYSTEM                                                                   | 9-1  |

| 10      | SOFTWARE DESCIPTION FOR THE KU-BAND INTEGRATED RADAR AND COMMUNICATIONS EQUIPMENT ELECTRONIC ASSEMBLY | 10-1 |

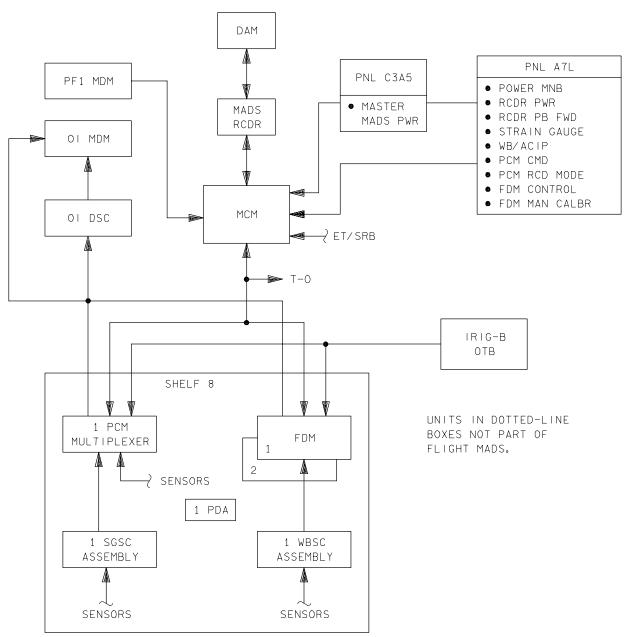

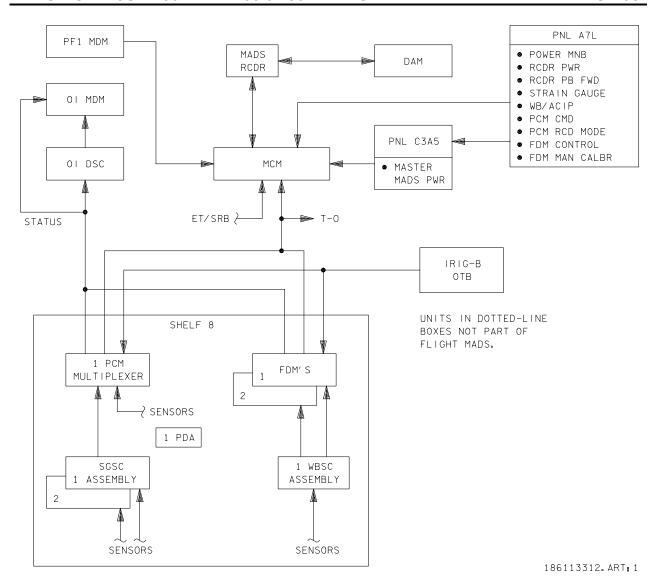

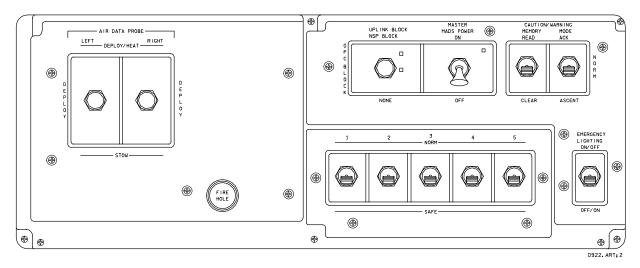

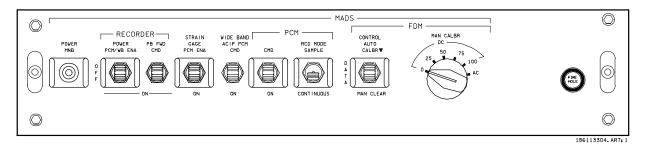

| 11      | GROUND COMMAND INTERFACE LOGIC CONTROLLER                                                             | 11-1 |

| 12      | NETWORK SIGNAL PROCESSOR                                                                              | 12-1 |

| 13      | COMSEC                                                                                                | 13-1 |

| 14      | ANTENNA MANAGEMENT                                                                                    | 14-1 |

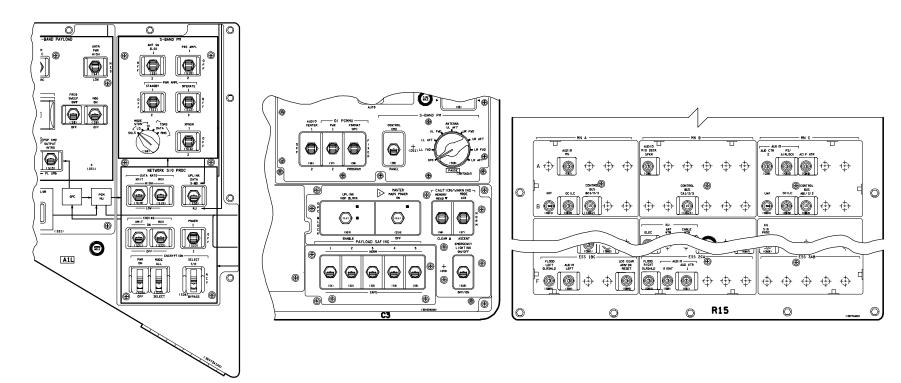

| 15      | AUDIO DISTRIBUTION SYSTEM                                                                             | 15-1 |

| 16      | OPERATIONAL WIRELESS CREW COMMUNICATIONS SYSTEM                                                       | 16-1 |

| 17      | ULTRAHIGH FREQUENCY SYSTEM                                                                            | 17-1 |

| 18      | RESERVED                                                                                              |      |

| 19      | SPACE-TO-SPACE COMMUNICATIONS SYSTEM                                                                  | 19-1 |

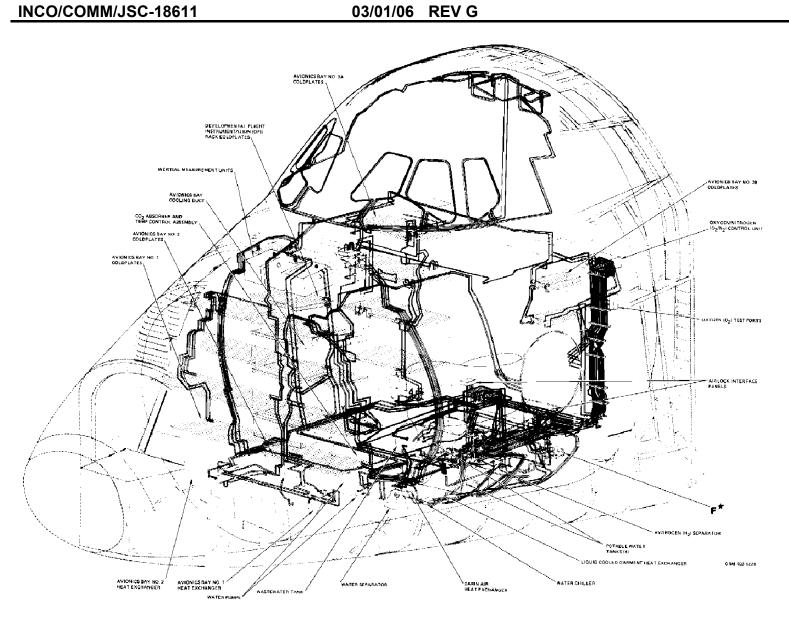

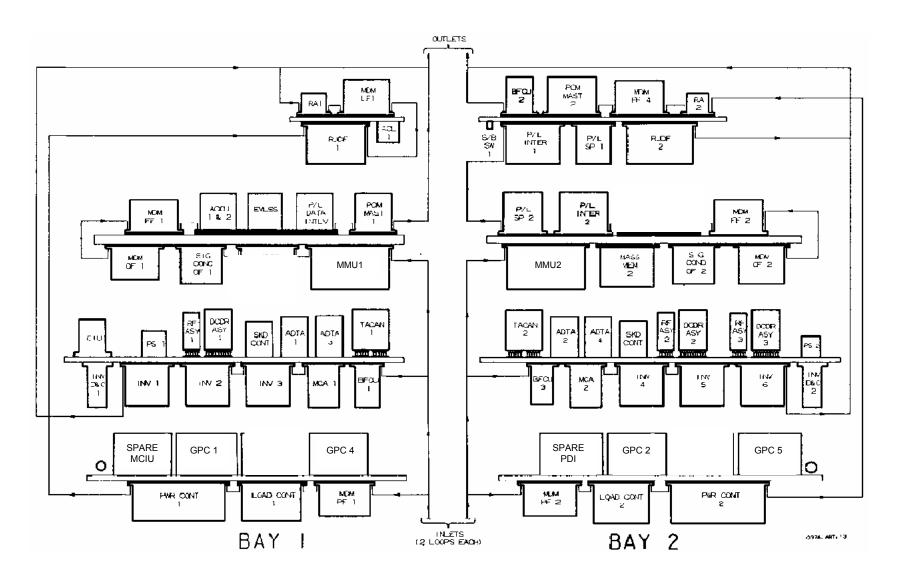

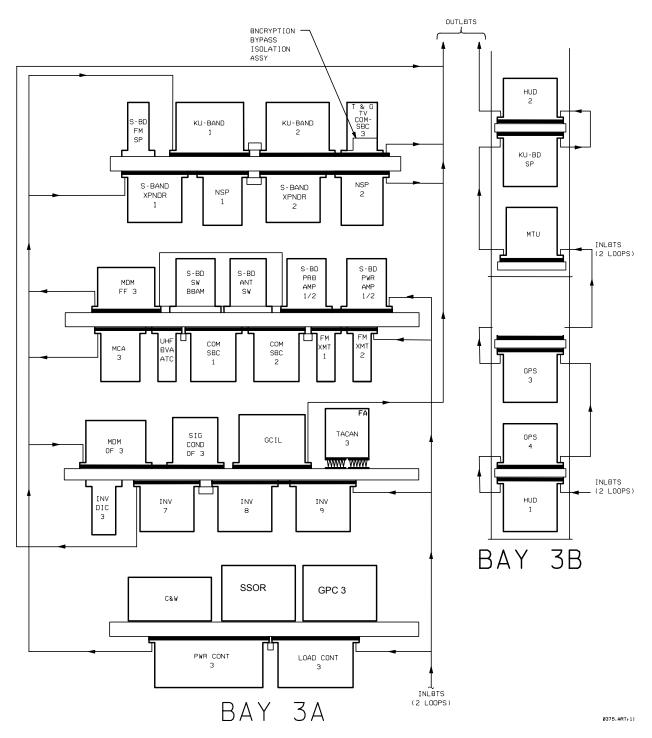

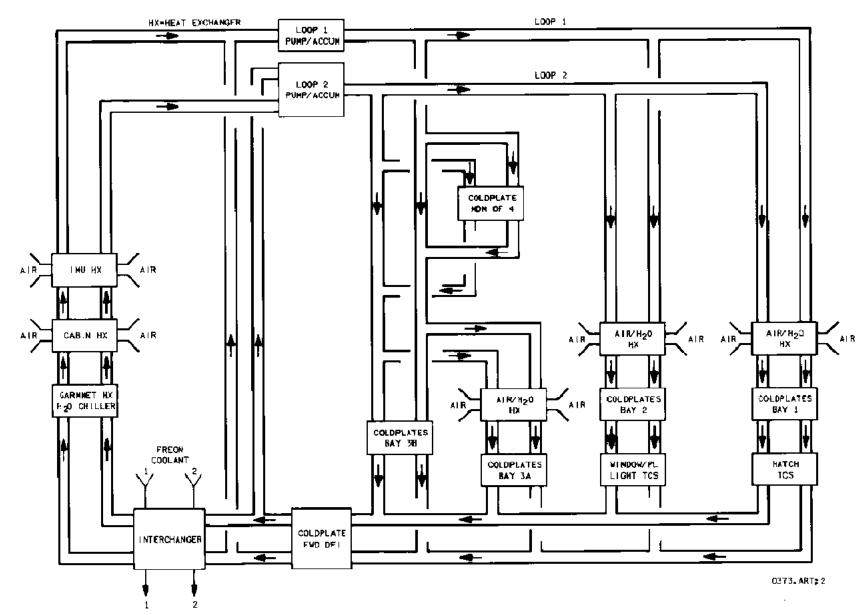

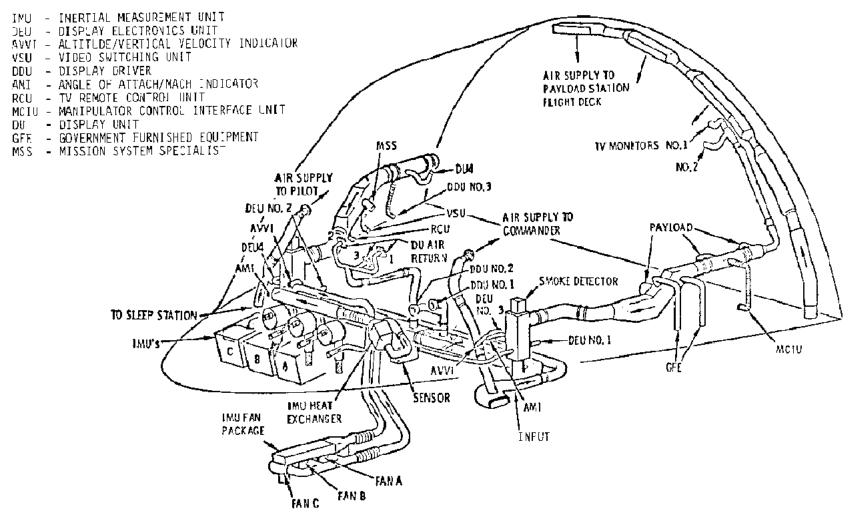

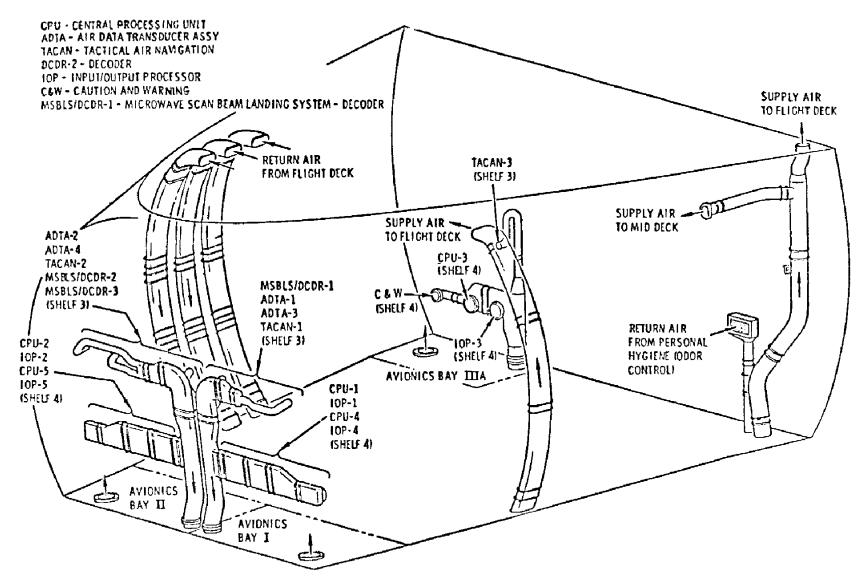

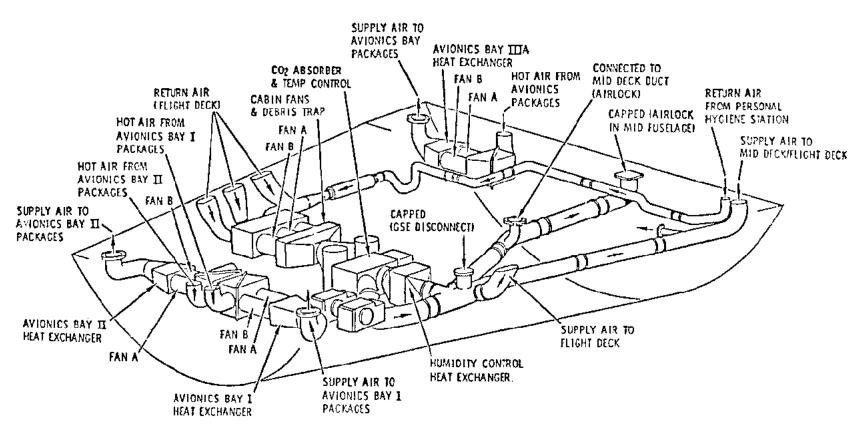

| 20      | COMMUNICATIONS AND INSTRUMENTATION SYSTEM WATER AND AIR-COOLED EQUIPMENT                              | 20-1 |

| 21      | RESERVED                                                                                              |      |

| 22      | RESERVED                                                                                              |      |

| Section |                                                         | Page |

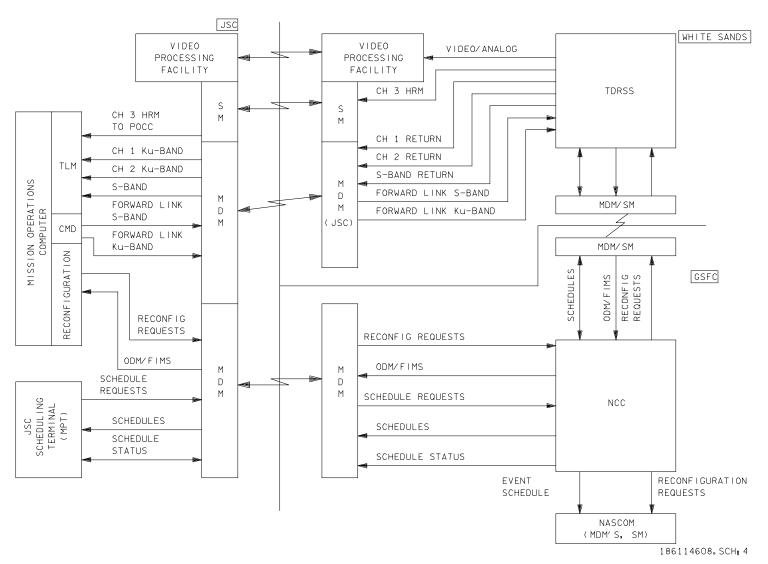

|---------|---------------------------------------------------------|------|

| 23      | RESERVED                                                |      |

| 24      | RESERVED                                                |      |

| 25      | RESERVED                                                |      |

| 26      | ORBITER OPERATIONAL INSTRUMENTATION OVERVIEW            | 26-1 |

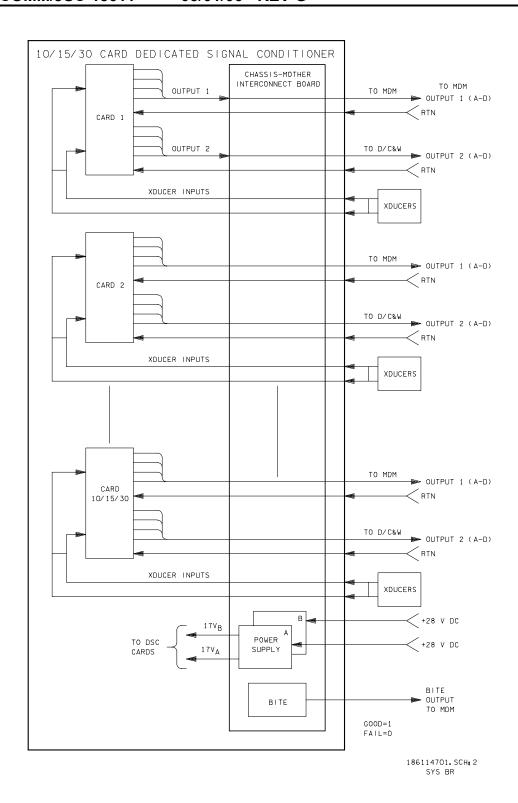

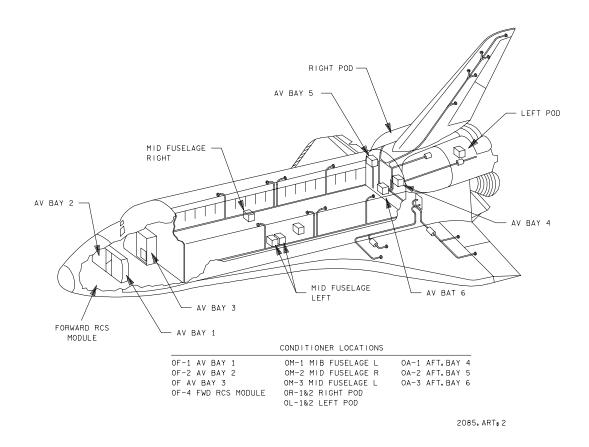

| 27      | OI DEDICATED SIGNAL CONDITIONERS                        | 27-1 |

| 28      | MULTIPLEXER/DEMULTIPLEXER                               | 28-1 |

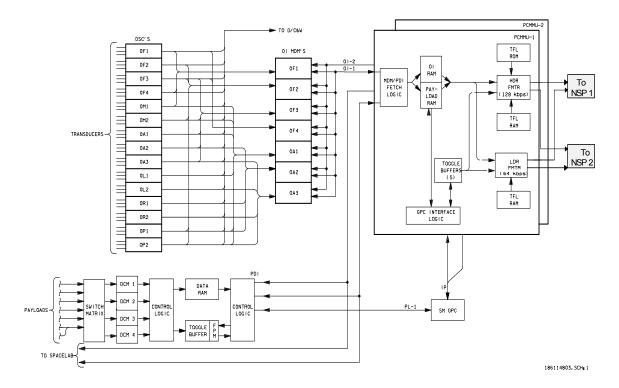

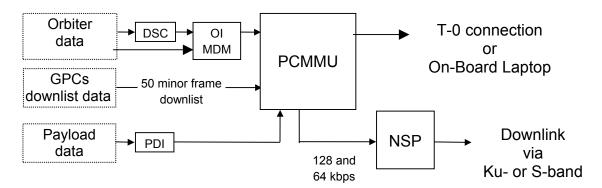

| 29      | PULSE CODE MODULATION MASTER UNIT                       | 29-1 |

| 30      | SM INPUT/OUTPUT AND ERROR PROCESSING SOFTWARE FOR PCMMU | 30-1 |

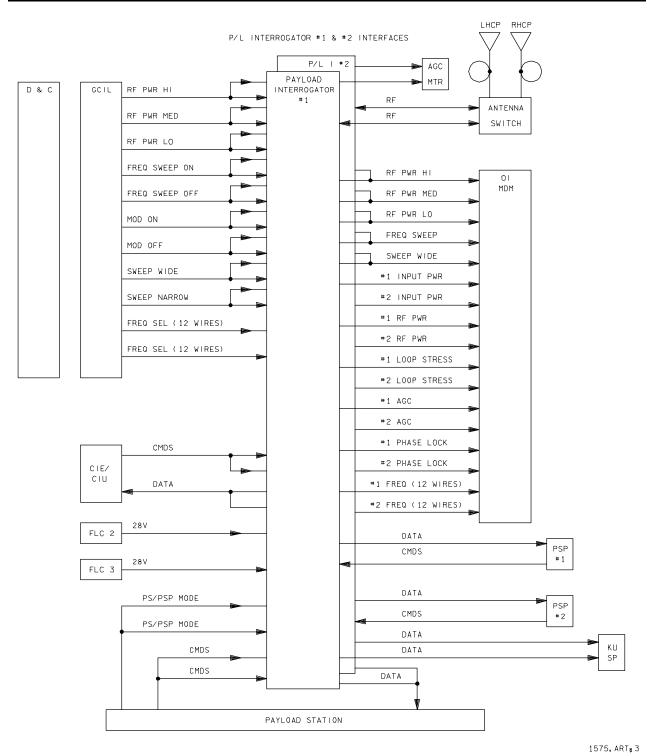

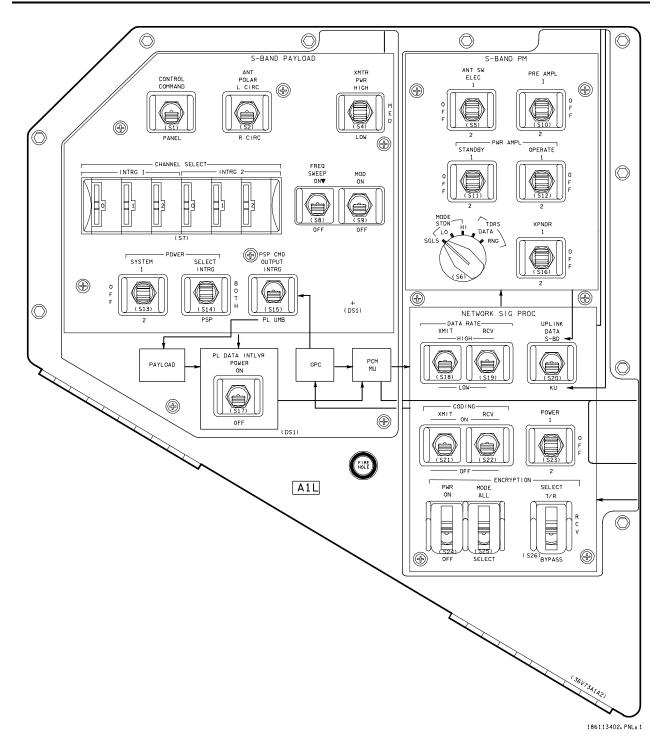

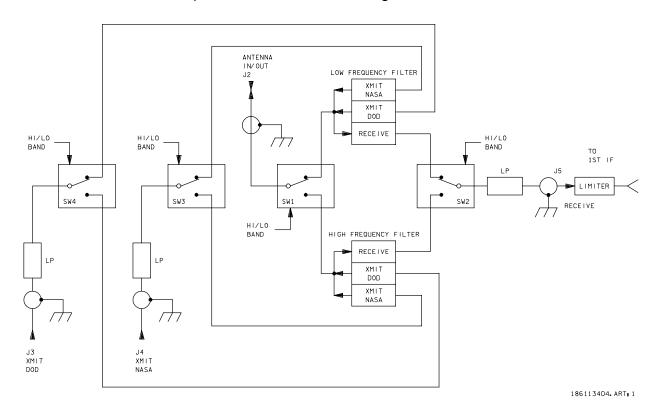

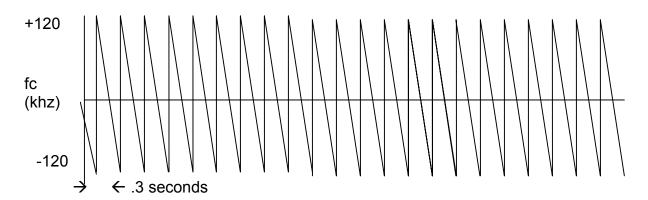

| 31      | PAYLOAD INTERROGATOR                                    | 31-1 |

| 32      | PAYLOAD SIGNAL PROCESSOR                                | 32-1 |

| 33      | PAYLOAD DATA INTERLEAVER                                | 33-1 |

| 34      | RESERVED                                                |      |

| 35      | MODULAR AUXILLARY DATA SYSTEM                           | 35-1 |

| 36      | RESERVED                                                |      |

| 37      | RESERVED                                                |      |

| 38      | ORBITER INTERFACE UNIT                                  | 38-1 |

| 39      | RESERVED                                                |      |

| 40      | MODULAR MEMORY UNIT/SOLID STATE RECORDER                | 40-1 |

| 41      | RESERVED                                                |      |

| 42      | RESERVED                                                |      |

| 43      | RESERVED                                                |      |

| 44      | RESERVED                                                |      |

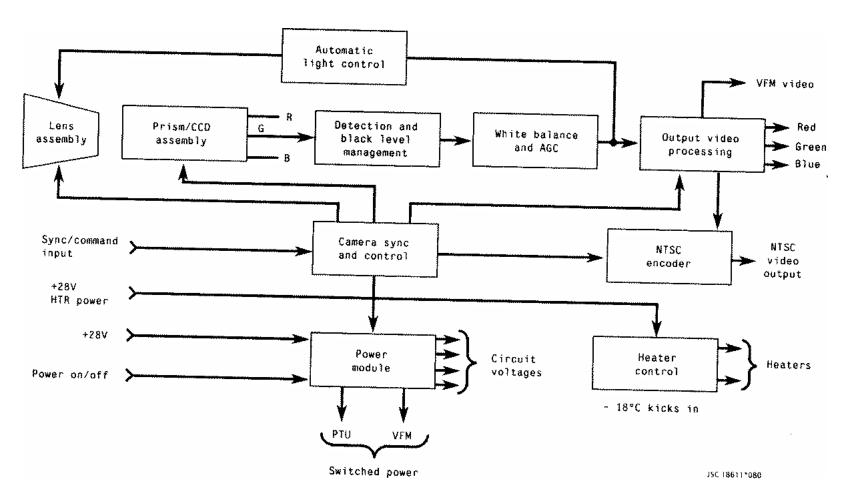

| 45      | RESERVED                                                |      |

| 46      | RESERVED                                                |      |

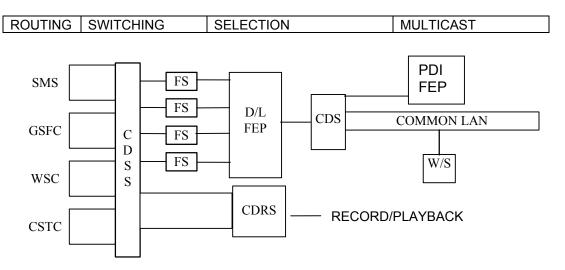

| 47      | GROUND NETWORK                                          | 47-1 |

| 48      | TRACKING AND DATA RELAY SATELLITE SYSTEM                | 48-1 |

| Section |                                     | Page |

|---------|-------------------------------------|------|

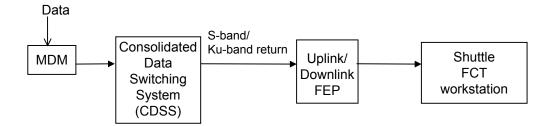

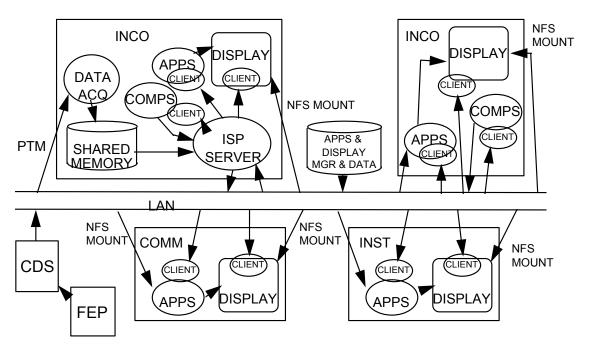

| 49      | TELEMETRY PROCESSING IN THE MCC     | 49-1 |

| 50      | RESERVED                            |      |

| 51      | RESERVED                            |      |

| 52      | RESERVED                            |      |

| 53      | RESERVED                            |      |

| 54      | RESERVED                            |      |

| 55      | RESERVED                            |      |

| 56      | RESERVED                            |      |

| 57      | RESERVED                            |      |

| 58      | RESERVED                            |      |

| 59      | RESERVED                            |      |

| 60      | RESERVED                            |      |

| 61      | RESERVED                            |      |

| 62      | RESERVED                            |      |

| 63      | RESERVED                            |      |

| 64      | RESERVED                            |      |

| 65      | RESERVED                            |      |

| 66      | RESERVED                            |      |

| 67      | RESERVED                            |      |

| 68      | RESERVED                            |      |

| 69      | RESERVED                            |      |

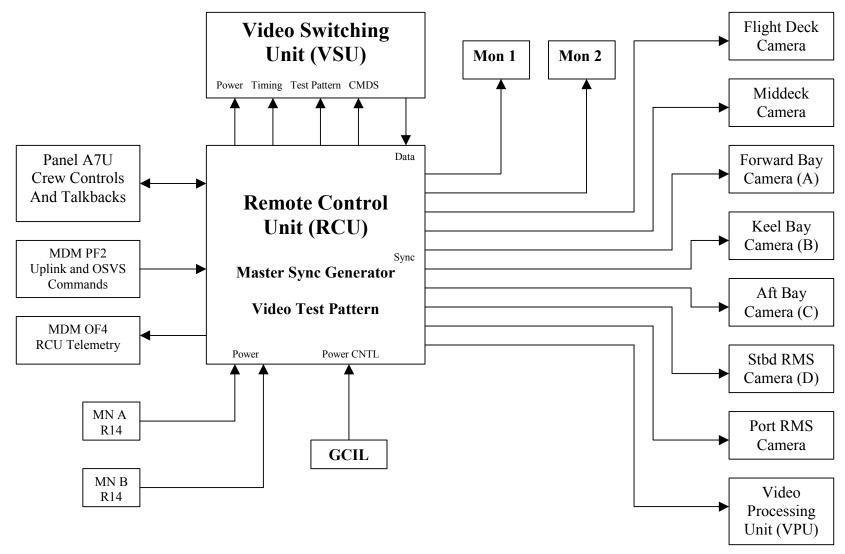

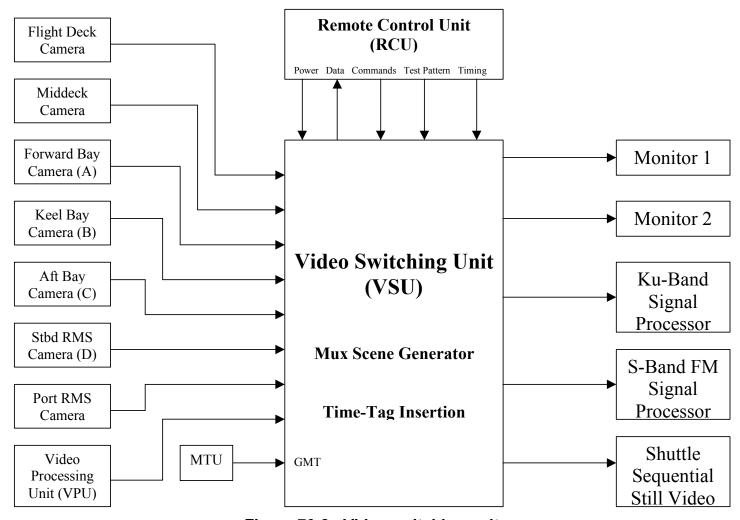

| 70      | CLOSED CIRCUIT TELEVISION           | 70-1 |

| 71      | SOLID STATE COLOR TELEVISION CAMERA | 71-1 |

| 72      | WIRELESS VIDEO SYSTEM               | 72-1 |

| 73      | SHUTTLE IN-CABIN VIDEO EQUIPMENT    | 73-1 |

| 74      | COLOR TELEVISION MONITOR            | 74-1 |

| Section |                                                        | Page |

|---------|--------------------------------------------------------|------|

| 75      | SEQUENTIAL STILL VIDEO                                 | 75-1 |

| 76      | DIGITAL TELEVISION                                     | 76-1 |

| 77      | ORBITER BOOM SENSOR SYSTEM                             | 77-1 |

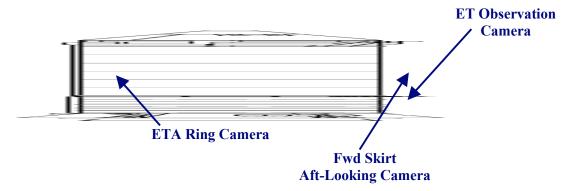

| 78      | ENHANCED LAUNCH VEHICLE IMAGING SYSTEM                 | 78-1 |

| 79      | RESERVED                                               |      |

| 80      | RESERVED                                               |      |

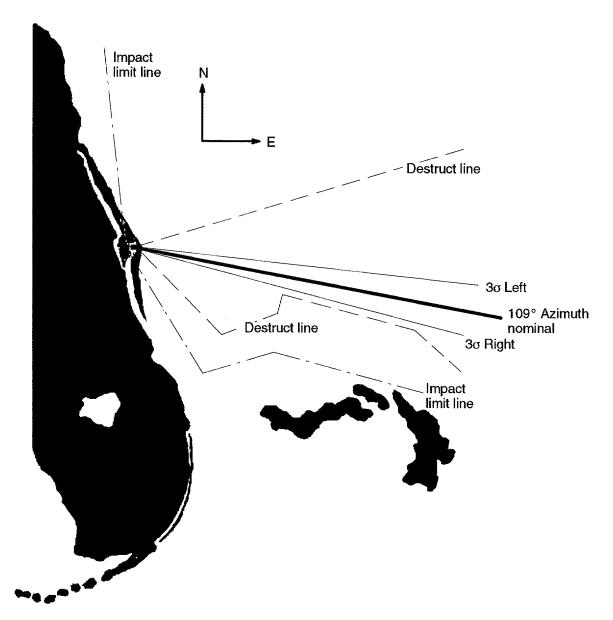

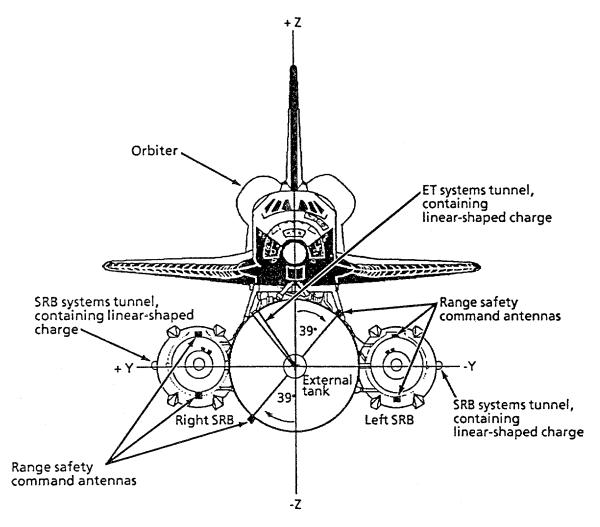

| 81      | SOLID ROCKET BOOSTER/EXTERNAL TANK RANGE SAFETY SYSTEM | 81-1 |

#### **List of Originators**

| SB | Title                                                                                                  | Originator |

|----|--------------------------------------------------------------------------------------------------------|------------|

| 1  | Onboard Command System                                                                                 | S. Sides   |

| 2  | Ground Command System Description                                                                      | S. Sides   |

| 3  | S-Band Phase Modulation System                                                                         | D. Brown   |

| 4  | S-Band Transponder                                                                                     | D. Brown   |

| 5  | S-Band Preamplifier                                                                                    | D. Brown   |

| 6  | S-Band Power Amplifier                                                                                 | L. Hoppe   |

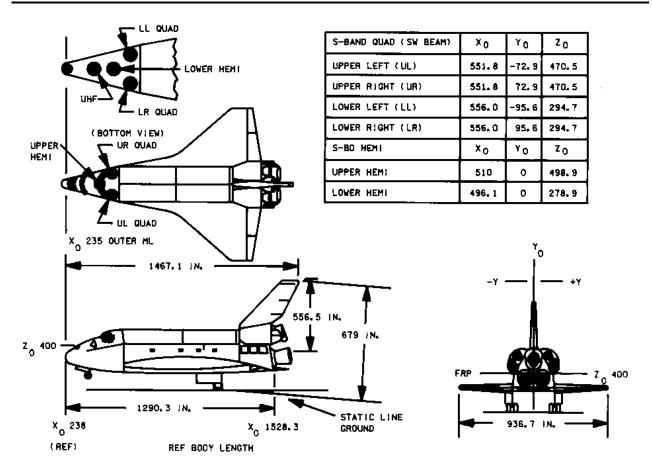

| 7  | S-Band Antenna System                                                                                  | L. Hoppe   |

| 8  | S-Band Frequency Modulation System                                                                     | D. Miller  |

| 9  | Ku-Band Radar/Communications System                                                                    | J. Fanelli |

| 10 | Software Description for the Ku-Band Integrated Radar and Communications Equipment Electronic Assembly | J. Fanelli |

| 11 | Ground Command Interface Logic Controller                                                              | D. Brown   |

| 12 | Network Signal Processor                                                                               | J. Fanelli |

| 13 | COMSEC                                                                                                 | S. Sides   |

| 14 | Antenna Management                                                                                     | S. Sides   |

| 15 | Audio Distribution System                                                                              | D. Branham |

| 16 | Operational Wireless Crew Communications System                                                        | L. Hoppe   |

| 17 | Ultrahigh Frequency System                                                                             | J. Scott   |

| 18 |                                                                                                        |            |

| 19 | Space-to-Space Communications System                                                                   | D. Branham |

| 20 | Communications and Instrumentation System Water and Air-Cooled Equipment                               | J. King    |

| 21 |                                                                                                        |            |

| 22 |                                                                                                        |            |

| 23 |                                                                                                        |            |

| 24 |                                                                                                        |            |

| 25 |                                                                                                        |            |

| 26 | Orbiter Operational Instrumentation Overview                                                           | D. Miller  |

| 27 | OI Dedicated Signal Conditioners                                                                       | D. Miller  |

| 28 | Multiplexer/Demultiplexer                                                                              | D. Miller  |

| 29 | Pulse Code Modulation Master Unit                                                                      | D. Miller  |

| 30 | SM Input/Output and Error Processing Software for PCMMU                                                | S. Sides   |

| SB | Title                                    | Originator  |

|----|------------------------------------------|-------------|

| 31 | Payload Interrogator                     | D. Miller   |

| 32 | Payload Signal Processor                 | J. Fanelli  |

| 33 | Payload Data Interleaver                 | J. Fanelli  |

| 34 |                                          |             |

| 35 | Modular Auxiliary Data System            | D. Miller   |

| 36 |                                          |             |

| 37 |                                          |             |

| 38 | Orbiter Interface Unit                   | D. Branham  |

| 39 |                                          |             |

| 40 | Modular Memory Unit/Solid State Recorder | J. Joy      |

| 41 |                                          |             |

| 42 |                                          |             |

| 43 |                                          |             |

| 44 |                                          |             |

| 45 |                                          |             |

| 46 |                                          |             |

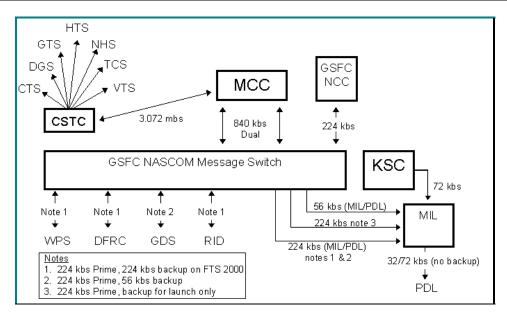

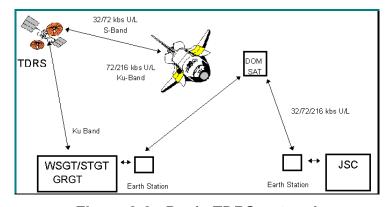

| 47 | Ground Network                           | J. McKinnie |

| 48 | Tracking and Data Relay Satellite System | J. McKinnie |

| 49 | Telemetry Processing in the MOC          | D. Miller   |

| 50 |                                          |             |

| 51 |                                          |             |

| 52 |                                          |             |

| 53 |                                          |             |

| 54 |                                          |             |

| 55 |                                          |             |

| 56 |                                          |             |

| 57 |                                          |             |

| 58 |                                          |             |

| 59 |                                          |             |

| 60 |                                          |             |

| 61 |                                          |             |

| 62 |                                          |             |

| 63 |                                          |             |

| SB | Title                                                  | Originator   |

|----|--------------------------------------------------------|--------------|

| 64 |                                                        |              |

| 65 |                                                        |              |

| 66 |                                                        |              |

| 67 |                                                        |              |

| 68 |                                                        |              |

| 69 |                                                        |              |

| 70 | Closed Circuit Television                              | J. McKinnie  |

| 71 | Solid State Color Television Camera                    | J. McKinnie  |

| 72 | Wireless Video System                                  | D. Bickham   |

| 73 | Shuttle In-Cabin Video Equipment                       | D. Branham   |

| 74 | Color Television Monitor                               | L. Hoppe     |

| 75 | Sequential Still Video                                 | D. Gresham   |

| 76 | Digital Television                                     | D. Branham   |

| 77 | Orbiter Boom Sensor System                             | E. Wingrove  |

| 78 |                                                        |              |

| 79 |                                                        |              |

| 80 |                                                        |              |

| 81 | Solid Rocket Booster/External Tank Range Safety System | G. Horlacher |

# SECTION 1 - ONBOARD COMMAND SYSTEM CONTENTS

| Section |                                                          | Page |

|---------|----------------------------------------------------------|------|

| 1.1     | INTRODUCTION                                             | 1-1  |

| 1.2     | SYSTEMS OVERVIEW                                         | 1-1  |

| 1.2.1   | Command Type Overview                                    | 1-2  |

| 1.2.2   | Command Validation Overview                              | 1-2  |

| 1.3     | COMMAND DATA STRUCTURE                                   | 1-2  |

| 1.3.1   | Command Header Information                               | 1-2  |

| 1.3.2   | Real-Time Commands                                       | 1-8  |

| 1.3.3   | Command Loads                                            | 1-12 |

| 1.4     | COMMAND PROCESSING                                       | 1-12 |

| 1.4.1   | NSP Processing                                           | 1-12 |

| 1.4.2   | NSP to GPC Interface                                     | 1-13 |

| 1.4.3   | GPC Processing                                           | 1-19 |

| 1.5     | INCO COMMAND TYPES                                       | 1-25 |

| 1.5.1   | Table Maintenance Block Update                           |      |

| 1.5.2   | Stored Program Command                                   | 1-26 |

| 1.5.3   | Time Executed Command                                    | 1-27 |

| 1.5.4   | Telemetry Format Load/Decomutator Format Load            | 1-28 |

| 1.5.5   | Payload Throughput Loads                                 | 1-30 |

| 1.5.6   | PSP Rejection Indicators from Uplinked Commands          | 1-31 |

| 1.6     | ON-BOARD COMMANDING                                      |      |

| 1.6.1   | Uplink Activity Indicator                                | 1-33 |

| 1.6.2   | Real-Time Commands via the DPS Utility Spec              | 1-33 |

| 1.6.3   | Crew Command Inhibits                                    | 1-35 |

| 1.7     | UPLINK ERROR CONDITIONS AND REPONSES                     | 1-35 |

| 1.7.1   | I/O Error FF3 [FF1]                                      | 1-35 |

| 1.7.2   | PASS/BFS Sync Is Lost                                    | 1-35 |

| 1.7.3   | BFS Not Tracking String 3 [1]                            | 1-35 |

| 1.7.4   | GNC-SM Loss of Common Set Sync                           | 1-35 |

| 1.7.5   | Bus Control Element (BCE) String 3 [1] - NSP             | 1-36 |

| 1.7.6   | On-Orbit SM GPC Fails                                    | 1-36 |

| 1.8     | COMMAND SYSTEM IDIOSYNCRASIES                            | 1-36 |

| 1.8.1   | Two-Stage Word-by-Word Problems                          | 1-36 |

| 1.8.2   | DEU Equivalent Commands (DR 36329)                       | 1-37 |

| 1.8.3   | Uplink Error Processing (DR 37553)                       | 1-37 |

| 1.8.4   | TM - SPEC vs. Uplink Interaction (DR 37572)              | 1-38 |

| 1.8.5   | Uplink to RS OPS-000 (DR 43987)                          | 1-38 |

| 1.8.6   | Ku Band/ PTC Overwritten (DR 55064)                      | 1-38 |

| 1.8.7   | Concatenation of Multiple PTCs (DR 55783)                | 1-38 |

| 1.8.8   | Multiple RTCIO on FC Buses may Jitter HFE I/O (DR 56157) | 1-38 |

| Section                                                                                     |                                                                                                                                                                                                                                                                                                                                                                             | Page                                                                              |

|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| 1.8.9<br>1.8.10<br>1.8.11<br>1.9                                                            | PSP Load In G9 Incorrectly Rejected (DR 111692)                                                                                                                                                                                                                                                                                                                             | 1-39<br>1-39<br>1-39<br>1-39                                                      |

|                                                                                             | TABLES                                                                                                                                                                                                                                                                                                                                                                      |                                                                                   |

| Table                                                                                       |                                                                                                                                                                                                                                                                                                                                                                             |                                                                                   |

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>1-6<br>1-7<br>1-8<br>1-9<br>1-10<br>1-11<br>1-12<br>1-13 | Orbiter Vehicle Codes  Major Function and GPC Codes  Op Codes  First Word/Last Word Indications  MDM Codes  NSP Power Discretes  Uplink Block Discretes  GPC Uplink Validity Bit Definition  Definition of GPC Bits in the NSP Validity Word  Definition of GPC Bits in the NSP Validity Word 2  Two-Stage Buffer Telemetry  TFL/DFL item entries  PSP Command Reject Flags | 1-3<br>1-4<br>1-7<br>1-10<br>1-15<br>1-16<br>1-20<br>1-22<br>1-24<br>1-29<br>1-32 |

|                                                                                             | FIGURES                                                                                                                                                                                                                                                                                                                                                                     |                                                                                   |

| Figure                                                                                      |                                                                                                                                                                                                                                                                                                                                                                             |                                                                                   |

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>1-6<br>1-7<br>1-8<br>1-9<br>1-10                         | Command System Overview Command Header RTC Routing Bits Example of an RTC Example of Reset/Set Mask Data Command Data Route NSP/GPC Interface NSP Serial I/O Structure NSP Validity Word NSP Val Word 2 DPS Utility SPEC Display                                                                                                                                            | 1-1<br>1-3<br>1-9<br>1-11<br>1-15<br>1-17<br>1-17<br>1-18<br>1-19<br>1-34         |

### SECTION 1 ON BOARD COMMAND SYSTEM

#### 1.1 INTRODUCTION

The command system on the orbiter is primarily used to control the operations of sub-systems and to make changes to flight software parameters. This systems brief will describe: (1) how the sub-systems involved in processing the commands interface to one another, (2) how the commands are validated, (3) how the commands are distributed to the sub systems or the flight software applications, (4) some safeguards that should be used to prevent erroneous commanding and (5) some idiosyncrasies of the on-board command system. Uplink of commands from the Mission Control Center (MCC) is described in INCO Systems Brief Section 2 Ground Command System Description.

#### 1.2 SYSTEMS OVERVIEW

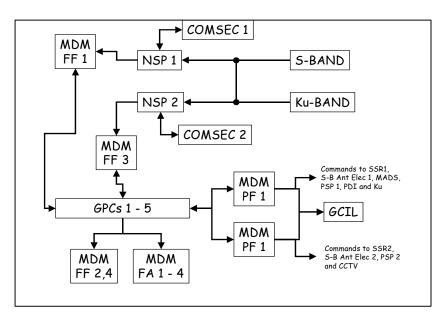

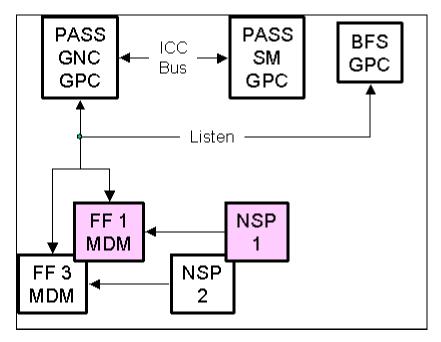

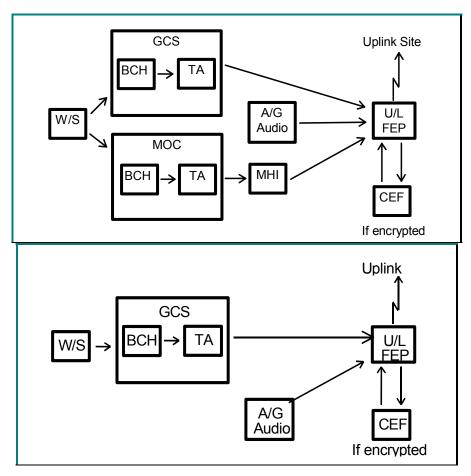

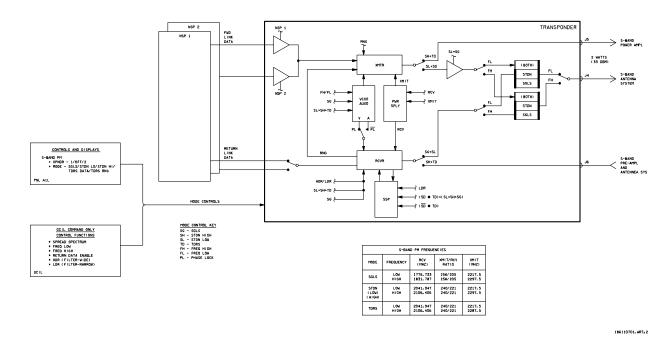

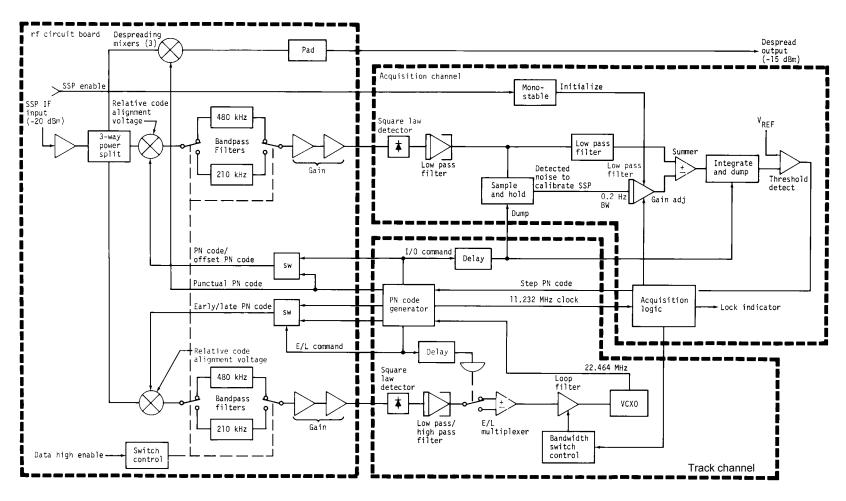

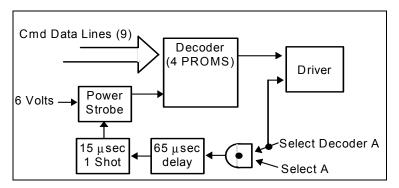

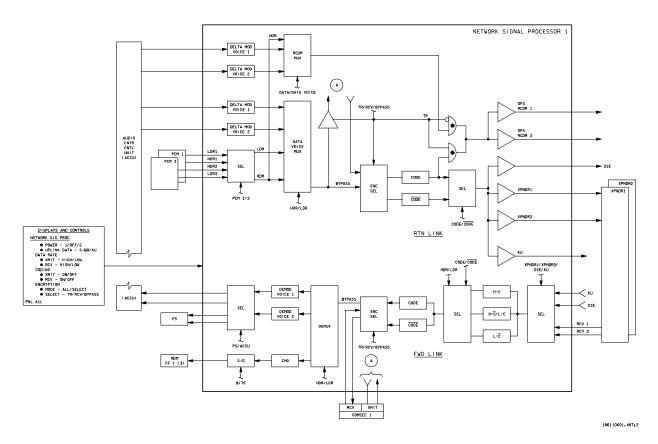

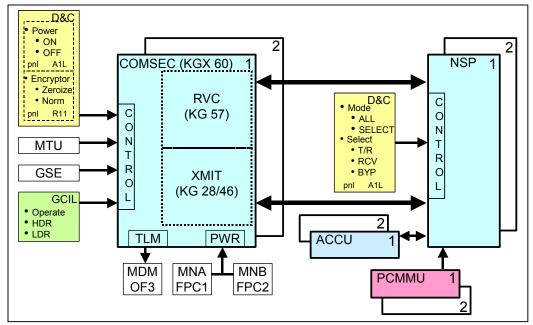

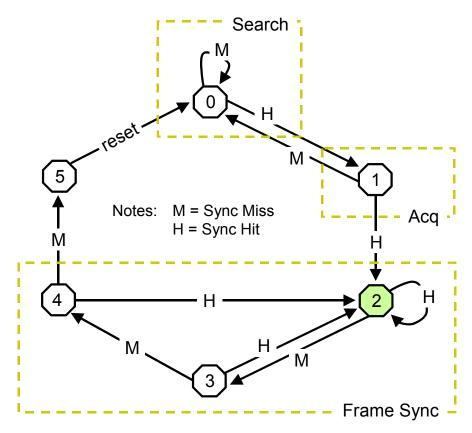

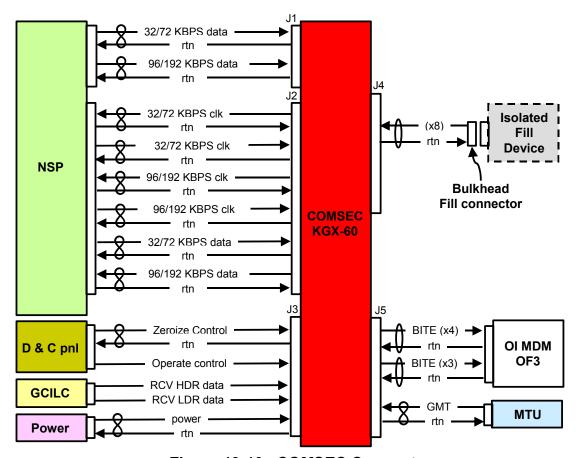

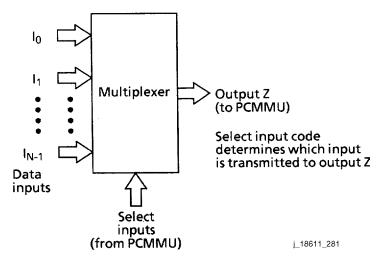

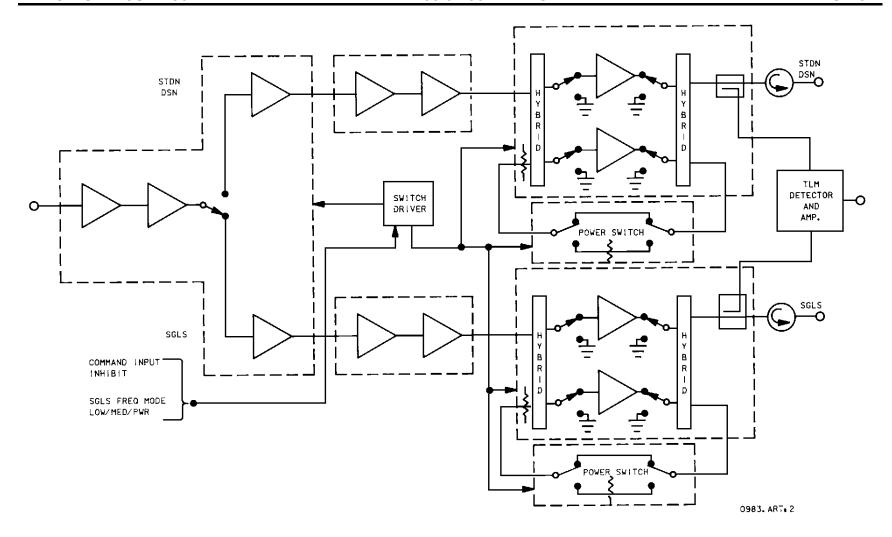

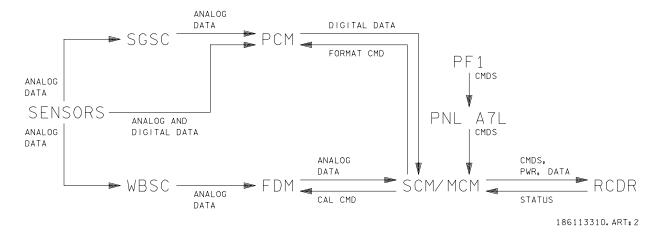

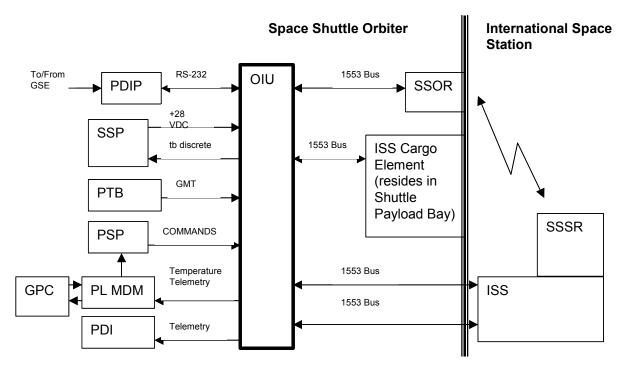

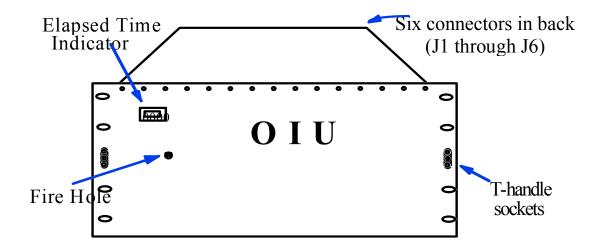

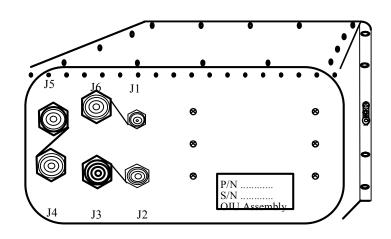

The orbiter Network Signal Processor (NSP) selects either the S-Band or the Ku-Band system 128 kbps multiplexed uplink. The uplinked data is sent to the Network Signal processor, which passes the data on to the Communications Security (COMSEC) line replaceable unit (LRU) if the uplink is encrypted. The COMSEC will decrypt the uplink data, time authenticate the command portion, multiplex it with the audio channels, and transfer it back to the NSP. Once the NSP has validated the command data, it will send the data via a flight critical Multiplexer/Demultiplexer (MDM) to a general purpose computer (GPC). The GPC will process the contents of the command data, looking for valid command structures and data types. After the GPC has confirmed that the command data is valid, it forwards the data to either a flight critical MDM, a payload MDM, or a flight software application. Figure 1-1 depicts these interfaces.

Figure 1-1. Command System Overview

ONBD CMD

SB 1

#### 1.2.1 Command Type Overview

There are several types of commands that can be uplinked to the orbiter. The various types of commands have different functions on board. The predominant type of command is the Real-Time Command (RTC). These commands are primarily used to change the operation of an onboard LRU. For example, INCO sends commands that control when the FM system is on or off. The other primary types of commands are called Loads. These commands are used to change the state of flight software, which may eventually change the state of some LRU. Each type of command will be covered in more detail later in this systems brief.

#### 1.2.2 Command Validation Overview

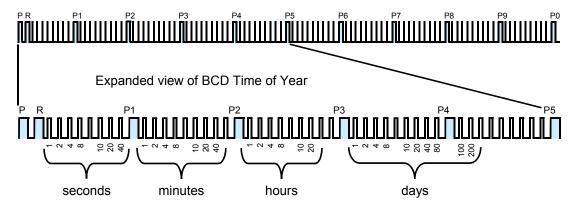

In order to ensure the data integrity of the commands that are sent to the orbiter, there are several operations that must occur in the MCC to validate the command data. The MCC will add a time stamp, BCH encode, add parity bits, and then encrypt the whole uplink to the orbiter. The time stamp is used to ensure the command originated from the MCC less than 19 sec apart from the on-board time. The parity bits are used by the NSP and the COMSEC to validate that the command data did not get corrupted during uplink. The encryption guarantees that the command data could not be tampered with during uplink. See the NSP and COMSEC Systems Briefs for details on these validation techniques.

#### 1.3 COMMAND DATA STRUCTURE

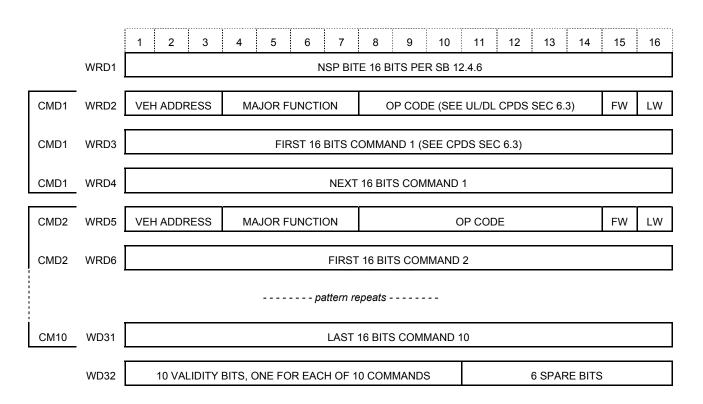

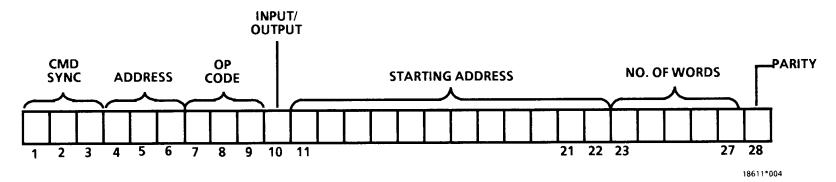

Commands are made up of one or more 48 bit command data words. These command data words must be correctly implemented for the command to successfully execute onboard. Each type of command is defined in the Downlist/Uplink Computer Program Development Specification (CPDS) for the Primary Avionics Software System (PASS) and the Program Requirements Document (PRD) for the Backup Flight Software (BFS).

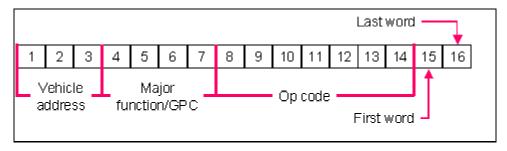

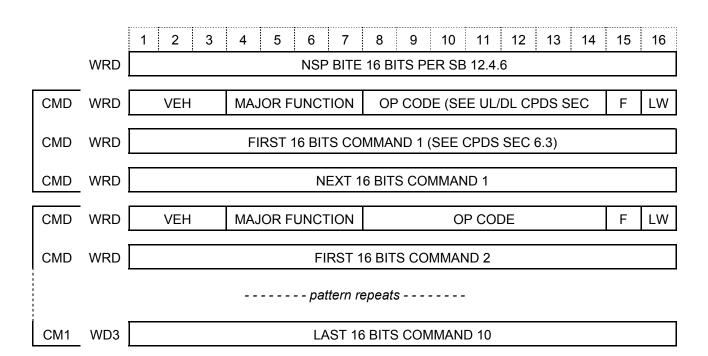

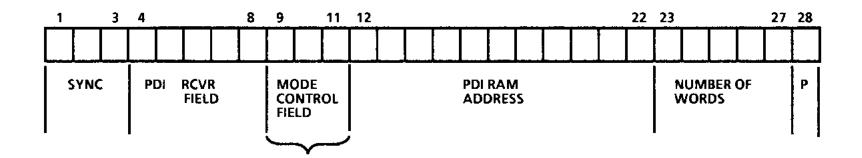

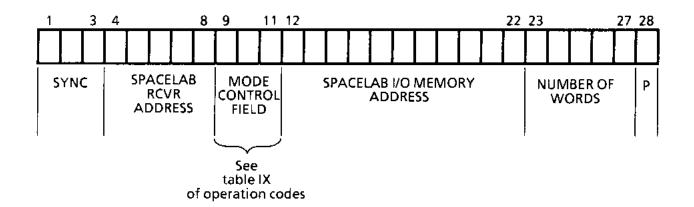

In all cases, the first 16 bits of the 48 bit command data word consist of: a vehicle address (i.e., orbiter tail number), a GPC major function (i.e., GNC, SM, BFS and PL), an operations code and a first word/last word indicator. The 32 bits of actual command data that will affect an LRU or flight software follow the first 16 bits. Each command uplinked could have up to 33 of these command data words.

#### 1.3.1 Command Header Information

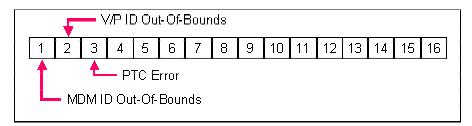

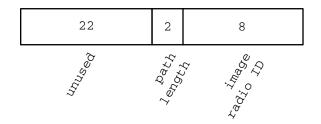

The command header information is contained in the first 16 bits of each command. Figure 1-2 shows how the bits in the command header are organized.

Figure 1-2. Command Header

#### 1.3.1.1 Vehicle Address

Each orbiter has a 3 bit address programmed within its five GPCs. This address uniquely identifies the orbiter to which the command is intended. If this value is not correct, the GPC will reject the command with a vehicle address error indication. This concept was implemented so that the MCC could support multiple orbiter activities at one time. The following table is the list of vehicle addresses.

Table 1-1. Orbiter Vehicle Codes

| <u>Code</u> | <u>Vehicle</u> | <u>Name</u> |

|-------------|----------------|-------------|

| 011         | 103            | Discovery   |

| 100         | 104            | Atlantis    |

| 101         | 105            | Endeavor    |

All other values are illegal

#### 1.3.1.2 Major Function (MF)/GPC Number

Each command must be addressed to either a major function (i.e., flight software configuration) or a particular GPC. The GPC flight software checks for this condition. The following table is the list of codes for the major functions and the GPC numbers.

Table 1-2. Major Function and GPC Codes

| <u>Code</u> | <u>GPC</u> | <u>Code</u> | <u>MF</u> |

|-------------|------------|-------------|-----------|

| 0001        | 1          | 0111        | GNC       |

| 0010        | 2          | 1000        | SM        |

| 0011        | 3          | 1001        | PL        |

| 0100        | 4          | 1010        | BFS       |

| 0101        | 5          |             |           |

| 0110        | ALL        |             |           |

1011 to 1111 are illegal codes

#### 1.3.1.3 Operation Code

The seven bit Operation Code, or Op Code, is used to define what type of command is contained in the command words. The flight software specifies what these Op Codes are and how the command data is organized within the command words. Some Op Codes are not valid in all flight software configurations (a.k.a. Ops modes). Table 1-3 provides GPC OI-30 Op Codes which list command types and software configurations.

Table 1-3. Op Codes

| Op Command Memory Config (Ops Mode) Code Type |                                    |    |    |    |    |    |   |    |    |    |    |    |

|-----------------------------------------------|------------------------------------|----|----|----|----|----|---|----|----|----|----|----|

|                                               |                                    | G1 | G6 | G2 | G3 | S2 | 0 | P9 | G8 | G9 | B1 | В3 |

| 0000001                                       | G-MEM Contiguous                   |    |    | •  |    | •  | • | •  | •  | •  | •  | •  |

| 0000010                                       | G-MEM Scatter                      |    |    | •  |    | •  | • | •  | •  | •  | •  | •  |

| 0000011                                       | MDM Multiple                       | •  | •  | •  | •  | •  | • | •  | •  | •  | •  | •  |

| 0000100                                       | MDM SPC MULT                       |    |    |    |    | •  |   |    |    |    | •  | •  |

| 0000101                                       | Equiv DEU                          | •  | •  | •  | •  | •  | • | •  | •  | •  |    |    |

| 0000110                                       | MMU Patch SM<br>Interface          |    |    |    |    | •  |   | •  |    |    |    |    |

| 0000111                                       | Ku Band / S Band<br>Antenna Cntl   |    |    |    |    | •  |   |    |    |    |    |    |

| 0001000                                       | IMU Refsmmat                       |    |    | •  | •  |    |   |    |    |    |    | •  |

| 0001001                                       | Orbiter State Vector               | •  | •  | •  | •  |    |   |    | •  |    | •  | •  |

| 0001010                                       | Rend Veh State<br>Vector           |    |    | •  |    |    |   |    |    |    |    |    |

| 0001011                                       | Wind Table                         |    |    |    |    |    |   |    |    | •  |    |    |

| 0001100                                       | Guidance<br>Polynomial             |    |    |    |    |    |   |    |    | •  |    |    |

| 0001110                                       | Throt-Vel & Tref-<br>Adjust        |    |    |    |    |    |   |    |    | •  |    |    |

| 0001111                                       | Launch Targeting                   | •  | •  |    |    |    |   |    |    |    | •  |    |

| 0010000                                       | On-Orbit Guidance<br>Targets PEG 7 |    |    | •  |    |    |   |    |    |    |    |    |

| 0010001                                       | Deorbit Guidance<br>PEG 7          |    |    | •  | •  |    |   |    |    |    |    | •  |

| 0010010                                       | IMU Gyro Bias                      | •  |    | •  | •  |    |   |    |    |    |    | •  |

| 0010011                                       | IMU Accelerometer<br>Bias          |    |    | •  | •  |    |   |    |    |    |    | •  |

| 0010100                                       | Deorbit Guidance<br>PEG 4          |    |    | •  | •  |    |   |    |    |    |    | •  |

| 0010101                                       | Deorbit Landing Site<br>Parameters | •  | •  |    | •  |    |   |    |    |    | •  | •  |

Table 1-3. Op Codes (continued)

| Op<br>Code | Command<br>Type                                               | Memory Config (Ops Mode) |    |    |    |    |   |    |    |    |    |    |

|------------|---------------------------------------------------------------|--------------------------|----|----|----|----|---|----|----|----|----|----|

|            |                                                               | G1                       | G6 | G2 | G3 | S2 | 0 | P9 | G8 | G9 | B1 | В3 |

| 0010110    | TDRS State Vector                                             |                          |    |    |    | •  |   |    |    |    | •  | •  |

| 0010111    | Ku Band Antenna<br>Bias Matrix                                |                          |    |    |    | •  |   |    |    |    |    |    |

| 0011000    | ADI Inertial Quaternion                                       |                          | •  | •  |    |    |   |    | •  |    |    | •  |

| 0011001    | OMS Targeting                                                 | •                        | •  |    |    |    |   |    |    |    | •  |    |

| 0011010    | Payload Data Load                                             |                          |    |    |    | •  |   |    |    |    |    |    |

| 0011011    | PSP Configuration<br>Message                                  |                          |    |    |    | •  |   |    |    |    |    |    |

| 0011100    | Vehicle Inertia<br>Matrix                                     |                          |    | •  |    |    |   |    |    |    |    |    |

| 0011101    | ADI Reference Quaternion                                      |                          |    | •  | •  |    |   |    |    | •  | •  | •  |

| 0011110    | ADI Bias LVLH Quat                                            |                          |    | •  | •  |    |   |    |    | •  | •  | •  |

| 0011111    | Deorbit TACAN<br>Para                                         | •                        | •  |    | •  |    |   |    |    |    | •  | •  |

| 0100000    | Delta Nav                                                     | •                        | •  |    | •  |    |   |    |    |    | •  | •  |

| 0100001    | Table Maintenance<br>Block Update                             |                          |    |    |    | •  |   |    |    |    | •  | •  |

| 0100010    | MSBLS Parameters<br>Load                                      | •                        | •  |    | •  |    |   |    |    |    |    |    |

| 0100101    | OMS Assist, Abort<br>Dump Timers,<br>Masses and<br>Velocities |                          |    |    |    |    |   |    |    | •  |    |    |

| 0100110    | IMU Accelerometer<br>Scale Factor                             |                          |    | •  | •  |    |   |    |    |    |    | •  |

| 0100111    | Throttle Levels                                               |                          |    |    |    |    |   |    |    | •  |    |    |

| 0101000    | Guidance<br>Polynomial PHI I                                  |                          |    |    |    |    |   |    |    | •  |    |    |

| 0101001    | Vent/RCS Body<br>Force Vector                                 |                          |    | •  |    |    |   |    |    |    |    |    |

| 0101010    | Drag Model Scale<br>Factors Load                              |                          |    | •  |    |    |   |    | •  |    |    |    |

| 0101011    | Covariance Matrix<br>Parameters Load                          |                          |    | •  |    |    |   |    |    |    |    |    |

| 0101100    | MDM BITE Data<br>Read                                         | •                        | •  | •  | •  | •  | • | •  | •  | •  |    |    |

| 0101101    | Insertion Guidance<br>Target PEG 4                            | •                        | •  |    |    |    |   |    |    |    | •  |    |

Table 1-3. Op Codes (continued)

| Op<br>Code | Command<br>Type                        | Men | nory | Confi | g (Op | s Mo | de) |    |    |    |    |    |

|------------|----------------------------------------|-----|------|-------|-------|------|-----|----|----|----|----|----|

|            |                                        | G1  | G6   | G2    | G3    | S2   | 0   | P9 | G8 | G9 | B1 | В3 |

| 0101110    | Time Executed SIO (TEC)                |     |      |       |       | •    |     |    |    |    |    |    |

| 0101111    | Star Catalog Update<br>Load            |     |      | •     |       |      |     |    |    |    |    |    |

| 0110000    | Orbiter Rate Gyro<br>Bias Update       |     |      |       | •     |      |     |    |    |    |    | •  |

| 0110001    | Accelerometer Assembly Bias Update     |     |      |       | •     |      |     |    |    |    |    | •  |

| 0110010    | RCS Quantity<br>Monitoring             |     |      | •     |       |      |     |    |    | •  |    |    |

| 0110011    | Notch Filter/Mass<br>Properties Update |     |      | •     |       |      |     |    |    |    |    |    |

| 0110100    | RMS End Effecter<br>ID Data Load       |     |      |       |       | •    |     |    |    |    |    |    |

| 0110101    | RMS Payload ID<br>Data Load            |     |      |       |       | •    |     |    |    |    |    |    |

| 0110110    | TFL and DFL and PSP I/O Enable         |     |      |       |       | •    |     |    |    |    |    |    |

| 0110111    | Variable D/L Select                    | •   | •    | •     | •     | •    | •   | •  | •  | •  | •  | •  |

| 0111000    | Time Execute<br>Command Clear          |     |      |       |       | •    |     |    |    |    |    |    |

| 0111001    | RMS Autosequence<br>Header Data Load   |     |      |       |       | •    |     |    |    |    |    |    |

| 0111010    | RMS Autosequence<br>Point Data Load    |     |      |       |       | •    |     |    |    |    |    |    |

| 0111011    | RNP Matrix Time<br>Parameter Load      |     |      | •     | •     |      |     |    |    |    |    |    |

| 0111100    | Scaling Corf Set & Data Type Update    |     |      |       |       | •    |     |    |    |    |    |    |

| 0111101    | Payload Throughput                     |     |      |       |       | •    |     |    |    |    |    |    |

| 0111110    | Payload MDM SPC<br>Mult                |     |      |       |       | •    |     |    |    |    |    |    |

| 0111111    | GPS SOP Time<br>Adjustment Load        | •   | •    | •     | •     |      |     |    |    | •  | •  | •  |

| 1000001    | 2-Stage Buffer Clear                   | •   | •    | •     | •     | •    | •   | •  | •  | •  | •  | •  |

| 1000010    | SPC Buffer Clear                       |     |      |       |       | •    |     |    |    |    | •  | •  |

| 1000011    | 2-Stage Buffer<br>Execute              | •   | •    | •     | •     | •    | •   | •  | •  | •  | •  | •  |

| 1000100    | Word By Word<br>Correction             | •   | •    | •     | •     | •    | •   | •  | •  | •  |    |    |

| 1000101    | MDM Single                             | •   | •    | •     | •     | •    | •   | •  | •  | •  | •  | •  |

Table 1-3. Op Codes (concluded)

| Op<br>Code | Command<br>Type                                            | Memory Config (Ops Mode) |    |    |    |    |   |    |    |    |    |    |

|------------|------------------------------------------------------------|--------------------------|----|----|----|----|---|----|----|----|----|----|

|            |                                                            | G1                       | G6 | G2 | G3 | S2 | 0 | P9 | G8 | G9 | B1 | B3 |

| 1000110    | UL Activity Off                                            | •                        | •  | •  | •  | •  | • | •  | •  | •  | •  | •  |

| 1000111    | UL Activity On                                             | •                        | •  | •  | •  | •  | • | •  | •  | •  | •  | •  |

| 1001000    | Memory Overlay<br>Uplink                                   | •                        | •  | •  | •  | •  | • | •  | •  | •  | •  | •  |

| 1001001    | Payload SPC Buffer<br>Clear                                |                          |    |    |    | •  |   |    |    |    |    |    |

| 1001010    | Uplink Command<br>Counter Reset                            | •                        | •  | •  | •  | •  | • | •  | •  | •  | •  | •  |

| 1001011    | PTC Buffer Clear                                           |                          |    |    |    | •  |   |    |    |    |    |    |

| 1100000    | Ascent Pseudo and ATO MECO Targets Load                    |                          |    |    |    |    |   |    |    | •  |    |    |

| 1100001    | GPCF Command                                               |                          |    |    |    | •  |   |    |    |    |    |    |

| 1100010    | RTLS Guidance<br>Parameters Load                           |                          |    |    |    |    |   |    |    | •  |    |    |

| 1100011    | Variable Intact Abort<br>Throttle Limit<br>Velocities Load |                          |    |    |    |    |   |    |    | •  |    |    |

#### 1.3.1.4 First Word/Last Word Indicator

The last two bits in the 16 bit command header are the first word/ last word indicator. As described in paragraph 1.3, each command uplinked could contain multiple 48 bit command words. The last two bits are used by the GPCs to determine if the 48 bit command word is the first word, last word, or "in the middle". They are also used to indicate if the 48-bit command word is a complete command. Table 1-4 describes the combinations for first word/last word indications.

Table 1-4. First Word/Last Word Indications

| Bits      | ;         |                                                                    |

|-----------|-----------|--------------------------------------------------------------------|

| <u>15</u> | <u>16</u> | Combination Meaning                                                |

| 1         | 0         | First command word in the load                                     |

| 0         | 1         | Last command word in the load                                      |

| 1         | 1         | Single command word load                                           |

| 0         | 0         | Intermediate command words in loads greater that two command words |

#### 1.3.1.5 Command Data Word

Bits 17 through 38 represent the portion of the command that will perform a configuration change to the flight software or directly to an LRU. These bits vary depending on the Op Code of the command. If a command is made up of multiple command words then each command word will contain the command header and last 32 bits of command data. If a command does not need all 32 bits of the last command data word, then the command processing on the ground will fill the remainder of the command with zeros.

#### 1.3.2 Real-Time Commands

Real-Time Commands (RTC) are designed to directly configure MDM output drivers. INCO is the primary user of this type of command although there are other systems that can be manipulated via RTCs. For a complete listing of the RTCs that are available for each mission, refer to either the Shuttle Data Tape file 5 or the generic command server RTC inventory display in the MCC.

#### 1.3.2.1 RTC Command Data Structure

An RTC usually consists of two 48-bit words, one with a reset mask and one with a set mask. Although these are usually thought of as one command, it is important to remember that the command system treats these as **two separate commands**. It is possible for half of the RTC to be rejected because of errors, and the other half to be executed. This has been experienced in flight and can result in unexpected command response (e.g., recorder going to run instead of standby). The number of single word RTCs is limited (i.e., U/L activity on/off, SPC and TEC buffer clears, 2-STG buffer exec). Since the first 16 bits of each command word has already been defined above, this section will only cover the reset and set masks for an RTC.

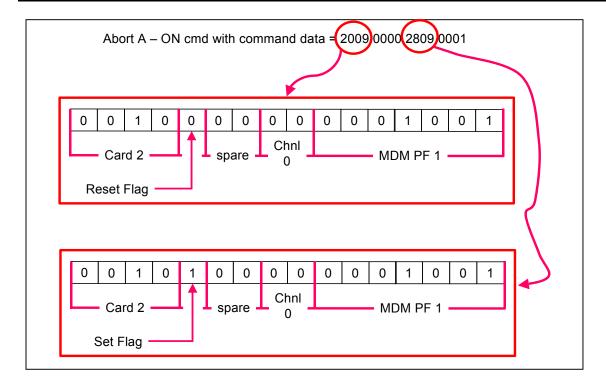

There are two major components of an RTC included in the last 32 bits of the command word. Bits 17 through 32 define which MDM card and channel to send the mask data (bits 33 through 48).

Bits 17 through 20 define the module address (MOD ADDR) which is the card on the MDM that is connected to the commanded LRU. Bit 21 indicates whether the command is a reset or a set command. Bits 22 and 23 are not used. Bits 24 and 25 are the channel selection on the MDM card that is specified in the MOD ADDR above. Lastly, bits 26 through 32 are the address of the MDM connected to the commanded LRU. Figure 1-3 graphically represents these bits.

03/01/2006 REV G

Figure 1-3. RTC Routing Bits

#### 1.3.2.2 Module Address

The module address, represented in binary in bits 17 through 20, is the card number in the MDM which is addressed in bits 26 through 32. As an example card 15 in the MDM would be represented by 1111 in these bits. An MDM has 16 cards, 0-15.

#### 1.3.2.3 Reset/Set

The reset/set bit 21 is used to determine if the command is a reset or a set command for the channel on the MDM card. If this bit is set low, '0', then the command is a reset command. Conversely, if it's high, '1', the command is a set command. Bits 22 and 23 are spares, which are not used for this type of command.

#### 1.3.2.4 Discrete Channel Select

The discrete channel select bits 24 and 25 are used to pick between the various channels on the MDM card. There are up to four channels (0-3) defined on an MDM card.

#### 1.3.2.5 MDM Number

Bits 26 through 32 indicate which MDM is addressed for the command. Bit 32 is the least significant bit. Table 1-5 is a summary of the 7 bit representation of Orbiter MDMs.

Table 1-5. MDM Codes

| <b>MDM Name</b> |

|-----------------|

| FF1             |

| FF2             |

| FF3             |

| FF4             |

| FA1             |

| FA2             |

| FA3             |

| FA4             |

| PF1             |

| PF2             |

| LF1             |

| LA1             |

| LM1             |

|                 |

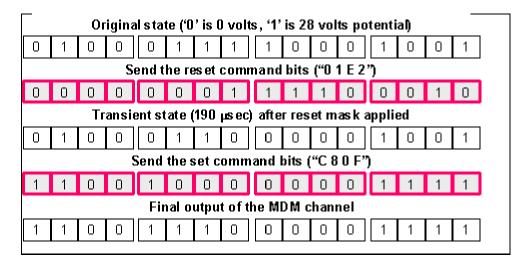

#### 1.3.2.6 Mask

Bits 33 through 48 of each RTC are used to set each of the bits on the specified MDM card and channel. In a reset command, the MDM will process the mask bits by interpreting any high bits, '1', as a request to drive the equivalent bit on the channel to low '0'. Any bits in the mask that are '0' will make no change to the equivalent bits on the channel. In a set command, any bits in the mask that are set high,'1', will drive the equivalent bits in the channel to high '1'. Just as with the reset command, any bits in the mask that are '0' will make no change to the equivalent bits on the channel.

#### 1.3.2.7 An Example of an RTC

To help in the understanding of the contents of an RTC, one command from the generic command server (GCS) was selected. This command is the Abort A On command which turns on a small light in front of the Commanders seat on the flight deck. Figure 1-4 details each bit in the command address.

Figure 1-4. Example of an RTC

For the mask part of each command, the process is different. Figure 1-5 is an example of how the reset and set masks affect the actual bits on the 16-bit channel of a card on an MDM. For better demonstration purposes, the mask is different from that shown in Figure 1-4.

Figure 1-5. Example of Reset/Set Mask Data

#### 1.3.3 Command Loads

A command load is considered to be a command that is processed as a two-stage command. Two-stage commanding is the process by which the command is uplinked to the GPCs. The GPC stores the command data, and sends a copy of it back to the ground. The generic command server (GCS) compares the uplinked command data to the downlinked command data. If the uplinked command is the same as the downlinked command, the GCS will send another command to the GPC to cause it to execute the previously stored command load. Details of the two-stage process are discussed later in the Command Processing section.

There are currently 64 different types of command loads. Although the INCO console position is responsible for the uplink of all the command loads, only those command loads that INCO regularly uses are discussed in this systems brief. Section 6.3 of the Downlist/Uplink Computer Program Development Specification (CPDS) contains the descriptions of all the command loads available for the GNC and SM major functions. Section 3.6.3 of the Program Requirements Design MG038101-30 (PRD) contains the descriptions of the command loads available for the BFS major function.

#### 1.4 COMMAND PROCESSING

Each command that is uplinked to the shuttle is processed the same way. First the NSP will receive the command from the uplink source, either the S Band or Ku band system. Next, the NSP will pass the command to the COMSEC for decryption. After the command is decrypted, the NSP will validate the command by comparing the parity bits. Once the NSP has validated the command, it is sent over to a GPC for final command processing and validation before it is sent to the LRU or flight software element. The following sections detail each of the preceding steps.

#### 1.4.1 NSP Processing

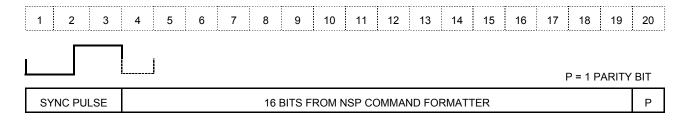

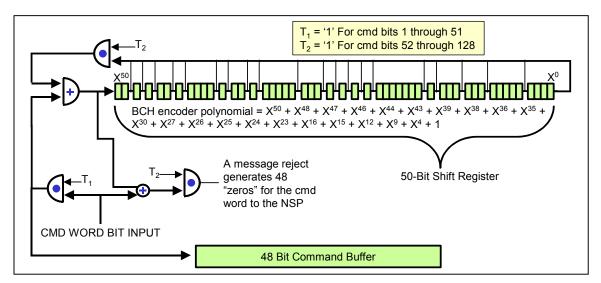

When the NSP receives the uplink source, it will bit synchronize the data and pass it on to the COMSEC to be processed (if the forward link is encrypted). The COMSEC will then return the decrypted uplink to the NSP. Next, the NSP will separate the uplink voice channels (A/G 1 and 2) and the command channel in the uplink data. The NSP uses the Bose-Chaudhuri-Hocquenghem (BCH) algorithm to determine if the command data uplinked has any bit errors. If it does, the NSP will change the vehicle address in the first 16 bits of the 48-bit command word to "0000". After all this has happened, the NSP sends the processed command data to the GPC for final processing and implementation. The "zeroed out" vehicle address is the only way the GPC will know there was a command bit error detected by the NSP.

#### 1.4.1.1 Bose-Chaudhuri-Hocquenghem (BCH) algorithm

BCH is a method of determining if the 48 bits of command data have been corrupted during uplink. The MCC command server will pass the 48 bits of command data through this algorithm and generate 77 bits of parity. The 48 bits of command and the

77 bits of parity are combined and sent as the uplink command data. The NSP and the COMSEC will separate the original 48 bit command word from the uplinked 77 bit BCH encoded command word. Next both the NSP and COMSEC will generate its own 77 bit BCH code and compare the uplinked 77 bits against the 77 bits that were generated. If the 77 bits are the same the command data is considered to be error free and the command continues through the process of being verified. For a more detailed discussion about BCH see section 13, COMSEC in the INCO Systems Briefs document.

#### 1.4.1.2 COMSEC Processing

The COMSEC receives the uplink from the NSP. It will decrypt the uplink before it starts to determine if the command data is valid. The COMSEC uses the same BCH algorithm to determine if there are errors in the command data but since the uplinked data was encrypted and time tagged, the process is slightly different than in the NSP. The COMSEC will get the current IRIG-B time from the Master Timing Unit (MTU). This time tag will be used to filter out the time tag in the uplinked command data (called time authentication). After this filtering is done, the COMSEC will complete the BCH test. If the command data passes this test, the data is sent on to the NSP for more processing. If the command data does not pass this test the original command data with time tag is filtered through a second time tag that is 10 seconds older than the first pass. The BCH process is repeated. If the command data passes during the second try, it is passed on to the NSP for further processing. If the command data does not pass the second time through the BCH/time authenticate test, the first 16 bits of the 48-bit command word are "zeroed out". This will guarantee that the command will fail the BCH check in the NSP, which will also make the command fail validity checks in the GPC.

#### 1.4.1.3 NSP Validation Process

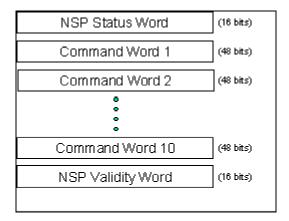

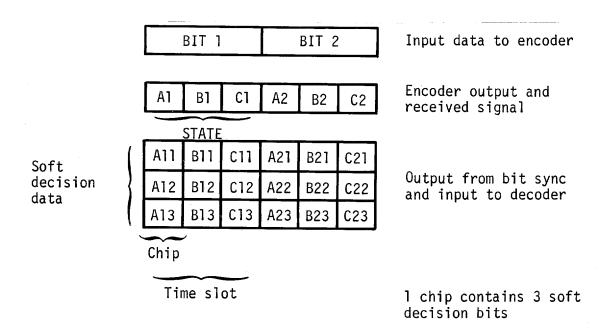

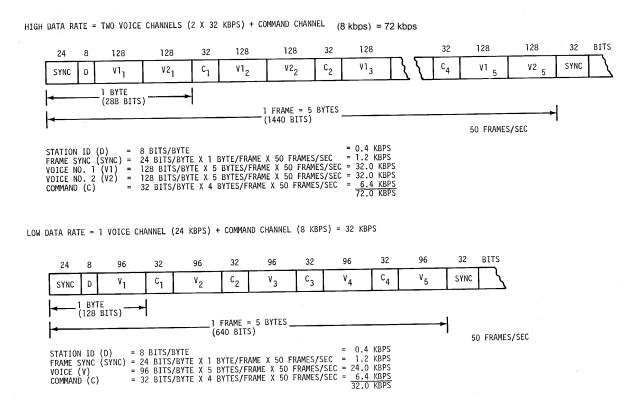

Once the command data and voice channels are returned to the NSP from the COMSEC, the voice channels are stripped off the uplink data so that the command data can be BCH tested again. If the data passes this BCH check it is placed into one of two 10 command word buffers. These buffers are polled by the GPC every 190  $\mu sec.$  The command word buffers are toggled each time the GPC reads one of them so that a new set of command words can be loading while the old set is being read by the GPC. The NSP will verify that each of the 10 - 48 bit command words are non-zero. This information is placed in the NSP validity word, which is sent to the GPC along with the 10-command word buffer.

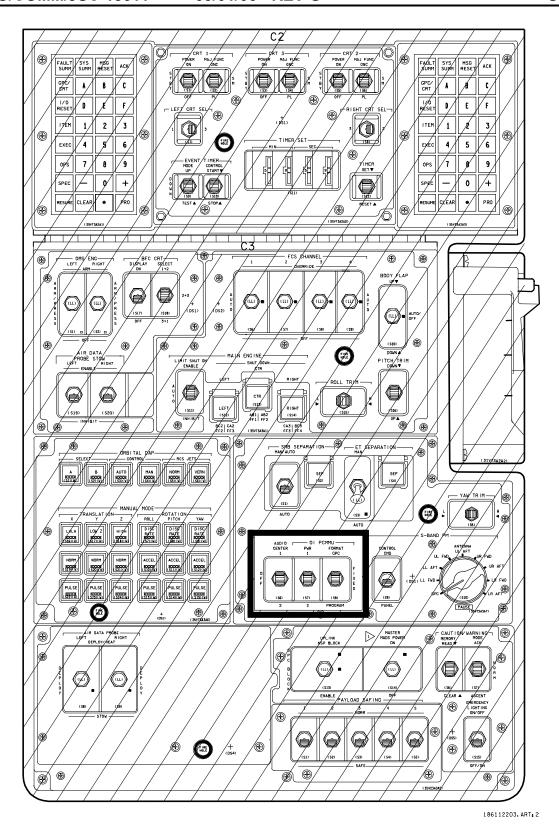

#### 1.4.2 NSP to GPC Interface

Once the NSP has processed the command data, it allows this command data to be retrieved by the GPCs. This process is accomplished differently depending on the type of flight software that is active in the GPCs. In order to process command, the GPCs must know which NSP is currently powered, the status of the uplink block switch on panel C3, and whether the command has been validated by the NSP. Only one NSP may be powered on at a time. The following paragraphs explain the different ways that

commands are distributed to the major functions and the processes of statusing the interfaces and the commands along the way.

#### 1.4.2.1 BFS Command Path

BFS acquires commands in two different ways. The BFS computer operates in the "Run" mode the majority of the time. While in this mode the BFS listens to all the Flight Critical strings, PASS input commands, and response words to ensure that the BFS does not directly interact with PASS.

This is done to protect against a BFS failure that could affect the PASS. If the crew has to engage the BFS GPC the PASS computers relinquish control over the FF MDMs, and BFS acquires command data by directly polling the NSPs via the MDMs.

For the BFS to receive data, the BFS "tracks" input/output on the orbiter data buses that are controlled by PASS. By "listening" to these transactions, BFS can "hear" any uplink commands as they are transmitted from the NSP to the PASS GNC GPCs. The PASS GNC GPCs reject the commands with the BFS address; the BFS accepts them and executes them.

This mode of operation causes two major constraints on uplink commanding to BFS pre-engage. First, BFS must be tracking PASS on the proper flight-critical strings. BFS downlists its status as to whether or not it is tracking PASS on flight-critical strings. These data are displayed on several INCO displays, including the INCO ASC/ENT Management and ASC/ENT INST Management. The second major constraint is that the BFS can only track PASS when the PASS GNC computers are in OPS 1 (ascent), OPS 6 (RTLS), or OPS 3 (deorbit/entry). It is impossible to uplink to BFS in other OPS pre-engage. Figure 1-6 shows these relationships.

Figure 1-6. Command Data Route

#### 1.4.2.2 SM Command Path

Commands enter the SM major function in a very different way from PASS GNC or BFS major function. Commands are routed to the SM computer via the PASS GNC computer. The GNC major function polls the NSP and collects the uplink command words. If the command destination is the SM major function, the GNC GPC will place the command data on an Inter-Computer Communication (ICC) data bus that links all GPCs. The SM computer retrieves the command data from the GNC major function and processes it accordingly.

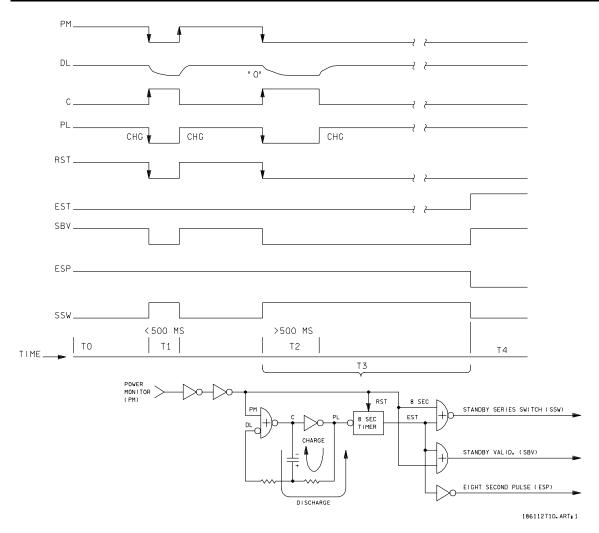

#### 1.4.2.3 Power Discrete

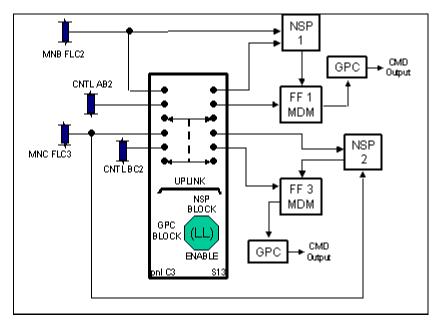

When an NSP is powered on, its power discrete is set in the forward load controller assembly (FLC). NSP 1 gets powered through forward FLC 2 while NSP 2 gets powered from forward FLC 3. The FLCs send a signal to flight critical MDMs, which pass the information on to the GNC and/or BFS GPCs. Table 1-6 shows these relationships.

Table 1-6. NSP Power Discretes

| NSP | Power Source | Power Controller | MDM  | Card | Channel |

|-----|--------------|------------------|------|------|---------|

| 1   | Main B       | FLC 2            | FF 1 | 9    | 1       |

| 2   | Main C       | FLC3             | FF 3 | 2    | 1       |

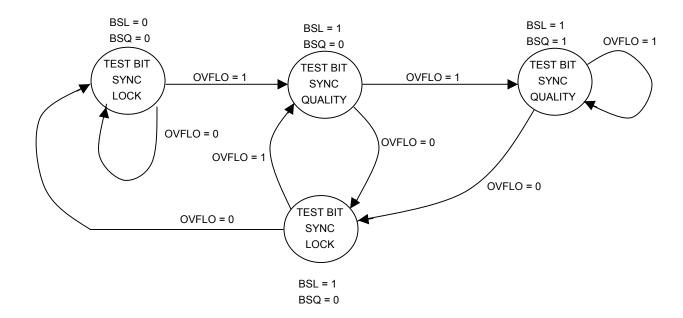

The systems software in the GPC, maintains the status of which NSP serial data path is currently active (being polled) and which NSP is currently bypassed. When the current NSP has its serial I/O bypassed by the GPC (FDA message "BCE STRG 3(1) NSP"), the GPCs will look to the power discretes to determine which NSP is powered on. The NSP power discrete that is ON (+28 volts) will be used as the "Current NSP" in the next computer cycle, while the other NSP will be considered the "Alternate NSP". This process of re-establishing serial I/O polling is called "Upmoding". This re-starts polling the current NSP without requiring the crew to execute a GNC I/O reset following an GNC Ops transition or an MDM port mode on flight critical strings 1 or 3. INCO Systems Brief 12 describes the NSP upmoding logic as it relates to the power discretes in more detail.

#### 1.4.2.4 Uplink Block Switch

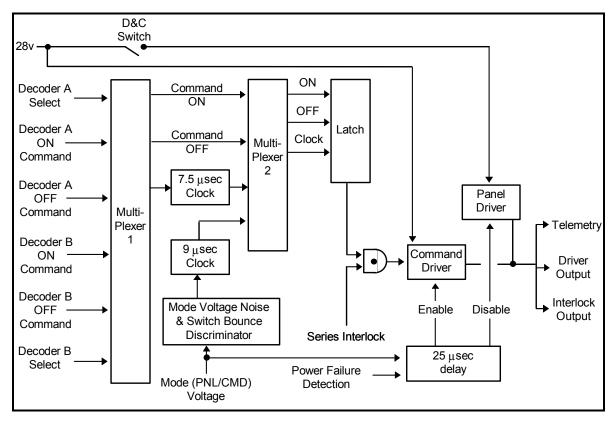

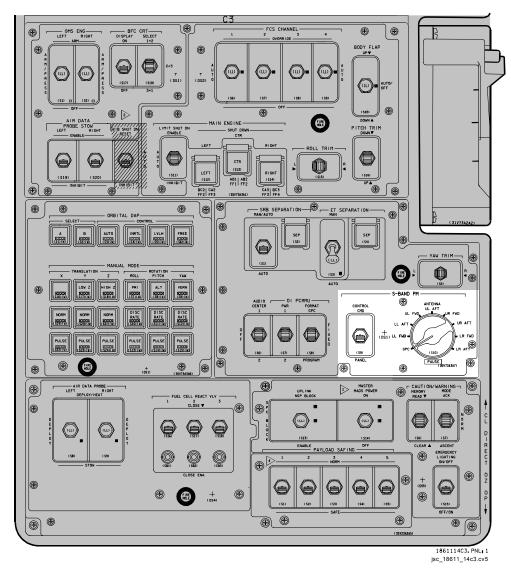

The crew can prevent uplink command processing by using, the Uplink Block switch. This switch has three positions. The bottom position is "ENABLE". This switch position is not electrically connected to anything, thus allowing the uplink commands to be processed nominally. The middle position of the switch is "GPC BLOCK" which is used to tell the GPC software to not allow commands to be processed and executed. There are 2 discretes that are added together to determine if the GPC is to not process commands. The first discrete, called "Discrete A" or "GPC UPLINK BLOCK CMD-FF1" is passed through MDM FF1 while "Discrete B" goes through MDM FF3. Both discretes must be high (+28 volts) before the GPCs will stop processing commands.

Table 1-7. Uplink Block Discretes

| NSP | Nomenclature             | MSID      | MDM  | Card | Channel |

|-----|--------------------------|-----------|------|------|---------|

| 1   | GPC Uplink Block CMD-FF1 | V72K8225X | FF 1 | 4    | 0       |

| 2   | GPC Uplink Block CMD-FF3 | V72K8226X | FF 3 | 4    | 0       |

The top position is "NSP BLOCK". This switch position is connected directly to the NSP to inhibit all command output and set the "Data Inhibit" bit (PASS V92X6082X, BFS V98X0232X) in the NSP status word. It prevents the GPCs from processing any command data and generates a "BCE STRG X NSP" message. The only way to re-establish the command interface after this has happened is to put the switch back in ENABLE and have the crew perform a "GNC I/O RESET". Figure 1-7 graphically shows these relationships.

The crew does not normally use the "NSP Block" switch position since it causes an error message. There is more discussion about this topic in INCO Systems Brief 12.

Figure 1-7. NSP/GPC Interface

#### 1.4.2.5 Transaction Data

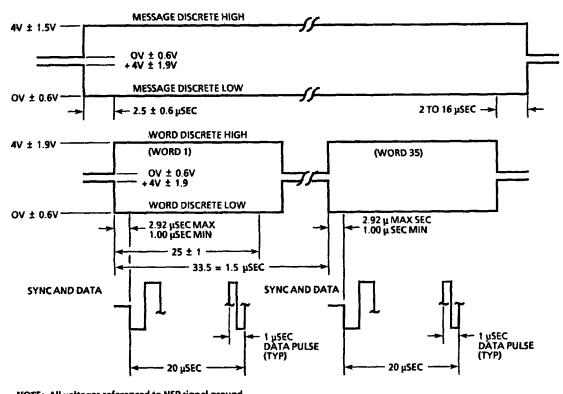

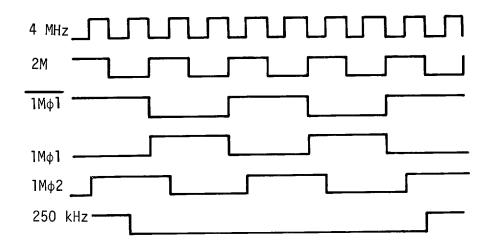

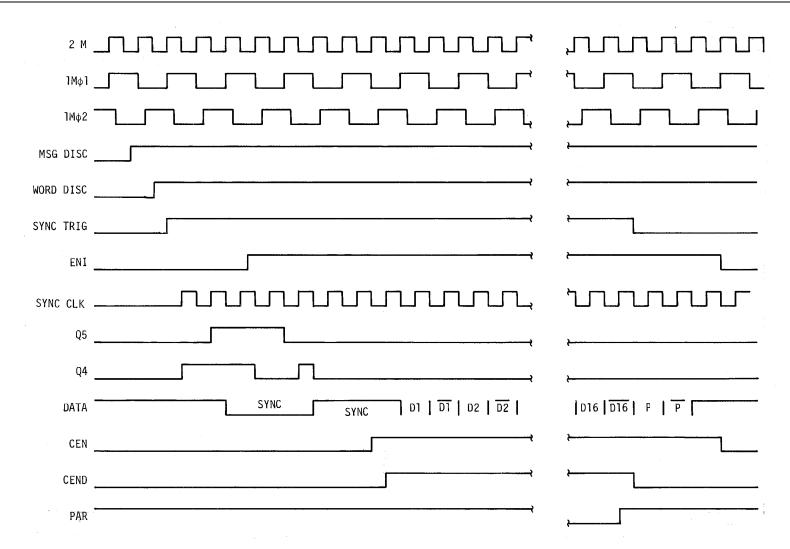

Once I/O is established between the NSP and the GPCs via the associated flight critical MDM, data transactions occur every 190  $\mu$ sec. These transactions transfer the status of the NSP, the command data from one of the two NSP command buffers and the indication as to which command buffers are non-zero. This information is vital to the GPC software so that the command data can be processed correctly. Each part of this transaction is discussed in the paragraphs to follow. Figure 1-8 shows the structure of the NSP serial I/O to the GPCs.

Figure 1-8. NSP Serial I/O Structure

#### 1.4.2.5.1 NSP Status Word

The NSP status word has two bits, which are very important to the GPC flight software. The Data Ready bit (PASS V92X6081X and BFS V98X0231X = 1), which is the first bit of the 16, indicates that at least one of the following 10 command words passed the BCH validity test in the NSP and has a nonzero vehicle address. When the Data Ready bit is set, the flight software in the GPCs examines the ten 48-bit command words and NSP validity word. The Data Inhibit bit (PASS V92X6082X and BFS V98X0230X = 1), which is the second bit of the 16, is set by the NSP when the crew "Uplink" switch on panel C3 is put in "NSP BLOCK". Discussion of the rest of the NSP status word can be found in INCO Systems Brief 12.

#### 1.4.2.5.2 NSP CMD Buffers

All ten of the 48-bit command words in the buffer are transferred to the flight software each transaction cycle. This process must be faster than the NSP can fill the command buffers so that no commands are lost. This results in the maximum command rate of 200 µsec.

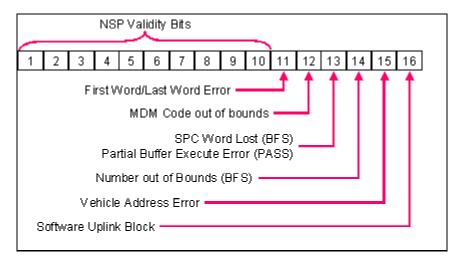

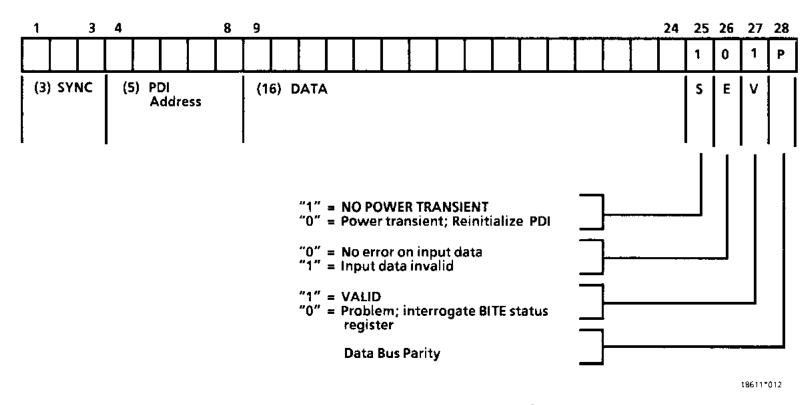

#### 1.4.2.5.3 NSP Validity Word

The NSP validity word is 16 bits long (V92M6078PX - GNC, V92M6078PY - SM, V92M6078PZ - Ops 0. V98M0250P - BFS). The first ten bits are set by the NSP, while the last six bits are set by the GPCs. Each of the ten bits set by the NSP corresponds to one of the ten 48-bit command words in the transaction. The NSP identifies nonzero 48-bit command words by a "1" in the appropriate bit in the NSP validity word. Even if a command word is identified by a "1" in the NSP validity, it does not necessarily mean that it is a valid command. It only means that it passed the BCH check and has a nonzero vehicle address. The last six bits are discussed in the GPC Validation Process section of this Systems Brief. Figure 1-9 shows the bits in the NSP validity word along with their function.

Figure 1-9. NSP Validity Word

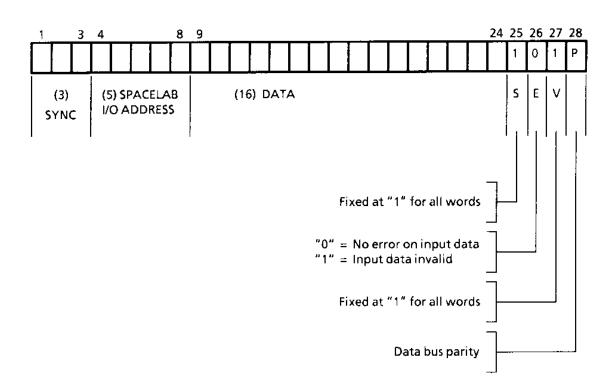

#### 1.4.2.5.4 NSP Validity Word 2

The second NSP validity word (V92M2922P) is an extension of the NSP validity function, which consists entirely of error indicators. Only the first three bits in this 16-bit word are used currently. The details of the first 2 bits are covered in the GPC validation section and the last bit is covered in the Payload Through Put section. Figure 1-10 shows the bits in NSP Val Word 2.

Figure 1-10. NSP Val Word 2

#### 1.4.3 GPC Processing

After the NSP has completed processing the command data, it places the data into the command buffer from which the GPC will poll the data for its command processing. The GPC flight software will perform a number of checks on the command data. These checks are done to ensure that the information in the command data word is properly assembled and correctly routed. Each major function (GNC, SM, BFS, PL and Ops 0) will downlist its command processing status independently.

The first step after the NSP has made the command data available is for the GPC Flight Computer Operating System (FCOS) to transfer the command data to the vehicle address/Op Code decoder module. This module will validate the command header information and determine how to route the command data inside the GPC software. The following paragraphs discuss the command validation process along with the downlisted indications of command errors, two-stage and single stage command processing, and special processing done for payload related commands.

#### 1.4.3.1 GPC Validation Process

The GPC validation process includes checks on the command header data (first 16 bits of the command word) as well as the information provided by the NSP in the NSP validation word and NSP status word. Each of these validation processes can generate an error condition. These error conditions are explained in Table 1-8 below. If the command is confirmed to be for the major function checking it and the vehicle address is valid, then the commands are forwarded to other command processes.

Table 1-8. GPC Uplink Validity Bit Definition

| Name                                        | Bit#         | MSID                                                    | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------|--------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPC Validity<br>Bits                        | Bits<br>1-10 | V92X6112X -<br>V92X6121X or<br>V98X0201X -<br>V98X0210X | If bit is on, it means that the corresponding command word in the 10-word buffer contained a command word with a nonzero vehicle address.                                                                                                                                                                                                                                                                                           |

| GPC/Major<br>Function<br>Check              | 11           | V92X6125X or<br>V98X0211X                               | This bit is set when the GPC/MAJOR FUNCTION code in a command word was not a legal code.                                                                                                                                                                                                                                                                                                                                            |

| Process Skip<br>Flag                        | 12           | V92X6126X or<br>V98X0212X                               | This bit is reset whenever a load has completed processing. It is set when FCOS/BSS determines that a load has not completed processing in an uplink cycle (because of GPC overload or delay in uplink processing caused by GPC errors).                                                                                                                                                                                            |

| SPC Buffer<br>Full                          | 13           | V92X6128X or<br>V98X0213X                               | Set whenever 25 SPCs are in the buffer (full). Reset whenever an SPC times out or the buffer is cleared.                                                                                                                                                                                                                                                                                                                            |

| Illegal Op<br>Code/ Memory<br>Configuration | 14           | V92X6132X or<br>V98X0214X                               | Each uplink is checked prior to processing to verify it is a legal command in the computer processing the load. If it is not a legal command, this bit is set.                                                                                                                                                                                                                                                                      |

| Two Stage<br>Error                          | 15           | V92X6134X or<br>V98X0215X                               | If two different OP codes are observed in between a command load with a first word set on and a command word with the last word bit set on, this bit will be set and the load rejected. This bit will also be set if more than 33 command data words of uplink are attempted in a single load (67 half words). This is also set if a command word with a zero vehicle address is found as an intermediate word in a two-stage load. |

Table 1-9. Definition of GPC Bits in the NSP Validity Word

|                                  |       | Checked       |                           |                                                                                                                                                                                                                                                                                                               |

|----------------------------------|-------|---------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                             | Bit # | Ву            | MSID                      | Meaning                                                                                                                                                                                                                                                                                                       |

| First<br>Word/Last<br>Word Error | 11    | PASS &<br>BFS | V92X5995X or<br>V98X4270X | <ul> <li>A. If first command word of a load does not have first word bit set on</li> <li>B. If a command load is in progress and command word with a first word bit set on is received prior to a word with the last word bit set on (i.e., start of a new command load prior to end of a previous</li> </ul> |

| MDM Code<br>Out of<br>Bounds     | 12    | PASS &<br>BFS | V92X5996X or<br>V98X4271X | load) This bit is set when an Illegal MDM number is found in an RTC or MRTC.                                                                                                                                                                                                                                  |

| SPC Word<br>Lost                 | 13    | BFS only      | V98X4272X                 | This bit is set when an attempt is made to load more than 25 SPCs.                                                                                                                                                                                                                                            |

Table 1-9. Definition of GPC Bits in the NSP Validity Word (continued)

|         |       | Checked  |           |                                                                              |

|---------|-------|----------|-----------|------------------------------------------------------------------------------|

| Name    | Bit # | Ву       | MSID      | Meaning                                                                      |

| Execute | 13    | PASS     | V92X5998X | This bit is set when an attempt has been                                     |

| Partial |       | only     |           | made to execute a two-stage buffer that does                                 |

| Buffer  |       |          |           | not contain a complete load (word with last                                  |

|         |       |          |           | word bit set on has not been received).                                      |

| Number  | 14    | BFS only | V98X4273X | The following conditions will cause a "Number                                |

| Out of  |       |          |           | Out of Bounds" error in the BFS.                                             |

| Bounds  |       |          |           |                                                                              |

|         |       |          |           | A. An MDM SINGLE, MDM MULTIPLE, or                                           |

|         |       |          |           | SPC MULTIPLE command load contains                                           |

|         |       |          |           | an MDM number that is zero or greater                                        |

|         |       |          |           | than 14.                                                                     |

|         |       |          |           | B. The number of command groups in an                                        |

|         |       |          |           | MDM MULTIPLE or SPC MULTIPLE                                                 |

|         |       |          |           | command load is zero or greater than 10.                                     |

|         |       |          |           | C. The number of words to be written in a G-                                 |

|         |       |          |           | MEM CONTIGUOUS command load is                                               |

|         |       |          |           | zero or greater than 64.                                                     |

|         |       |          |           | D. The starting address of a G-MEM                                           |

|         |       |          |           | command load, plus the number of words                                       |

|         |       |          |           | to be written, minus 1, is greater than                                      |

|         |       |          |           | 33FFF (hex).                                                                 |

|         |       |          |           | E. The number of address and word pairs in                                   |

|         |       |          |           | a G-MEM SCATTER command load is                                              |

|         |       |          |           | zero or greater than 32.                                                     |

|         |       |          |           | F. A G-MEM SCATTER command load                                              |

|         |       |          |           | contains a memory address that is                                            |

|         |       |          |           | greater than 33FFF (hex).                                                    |

|         |       |          |           | G. The number of data sets in a TABLE                                        |

|         |       |          |           | MAINTENANCE BLOCK UPDATE                                                     |

|         |       |          |           | command load is zero or greater that 10.                                     |

|         |       |          |           | H. There is an illegal data set type in a                                    |

|         |       |          |           | TMBU command load.                                                           |

|         |       |          |           | I. There is an illegal parameter                                             |

|         |       |          |           | interpretation in a TMBU command load.                                       |

|         |       |          |           | J. A displacement in a TMBU command load exceeds the length of the table for |

|         |       |          |           | which its data set is intended or causes a                                   |

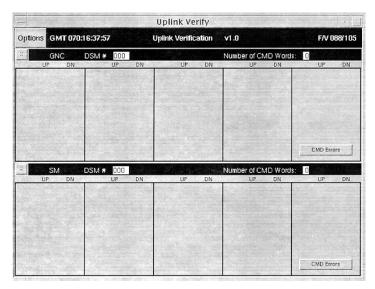

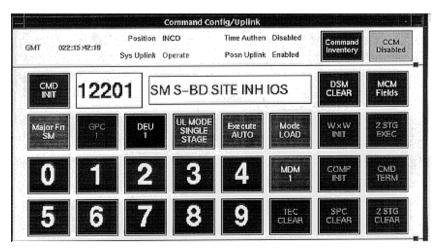

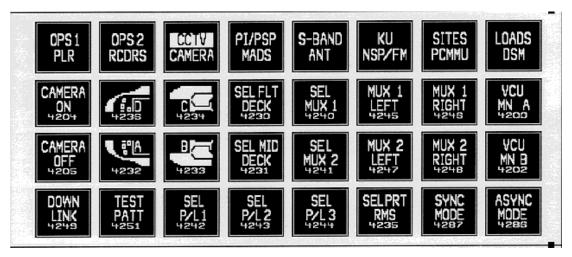

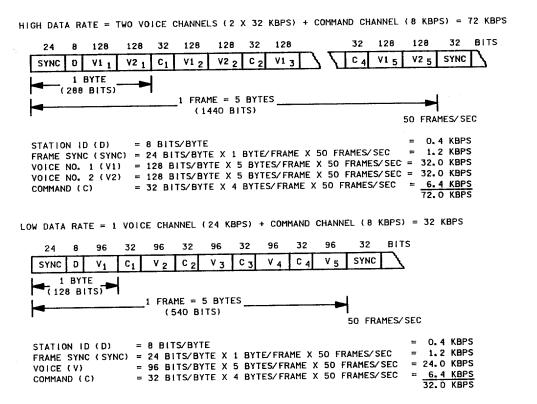

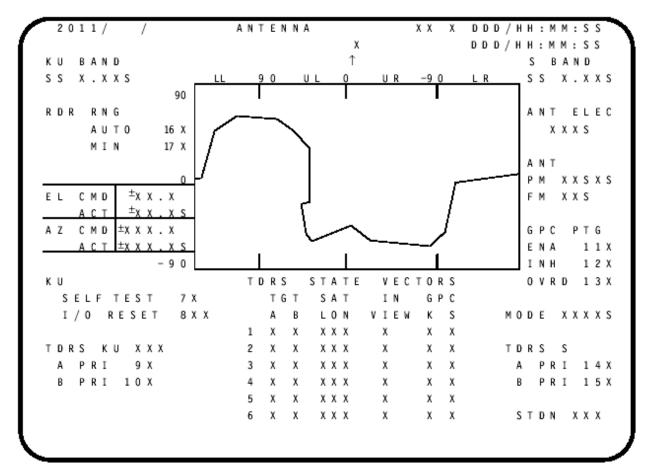

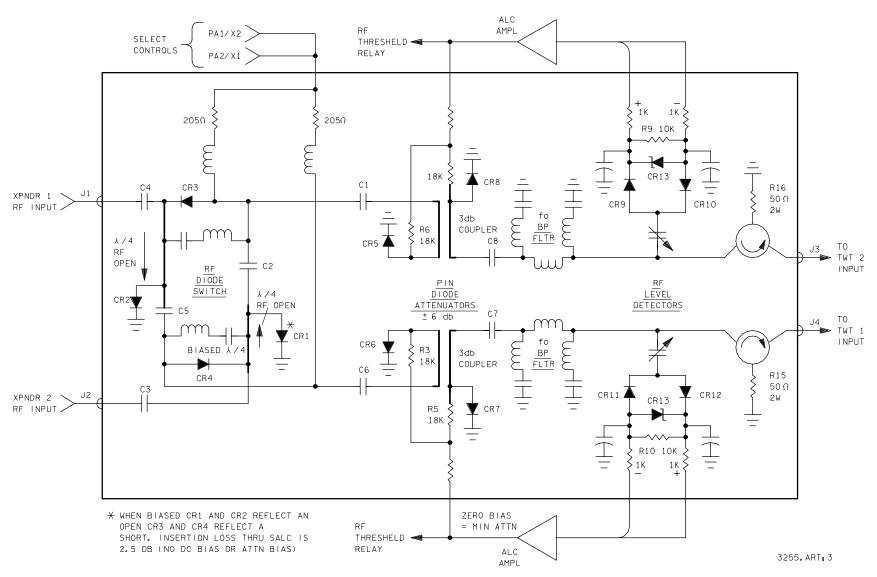

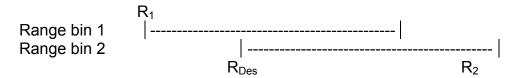

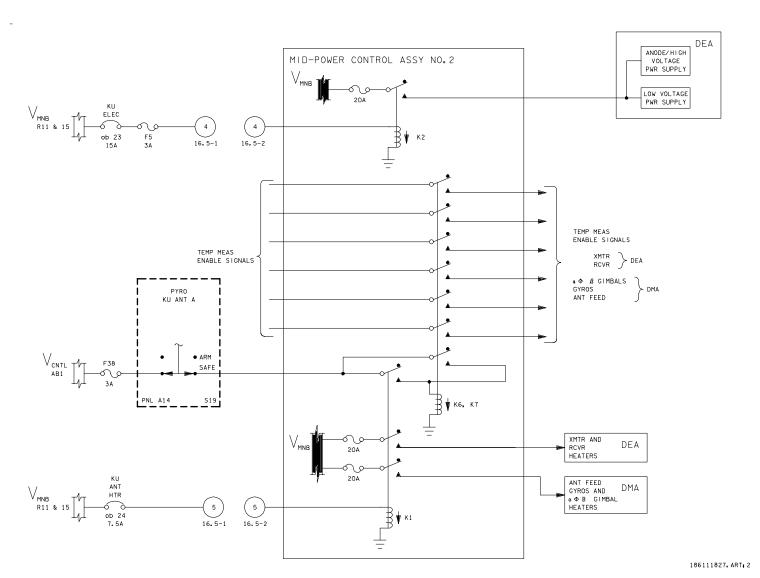

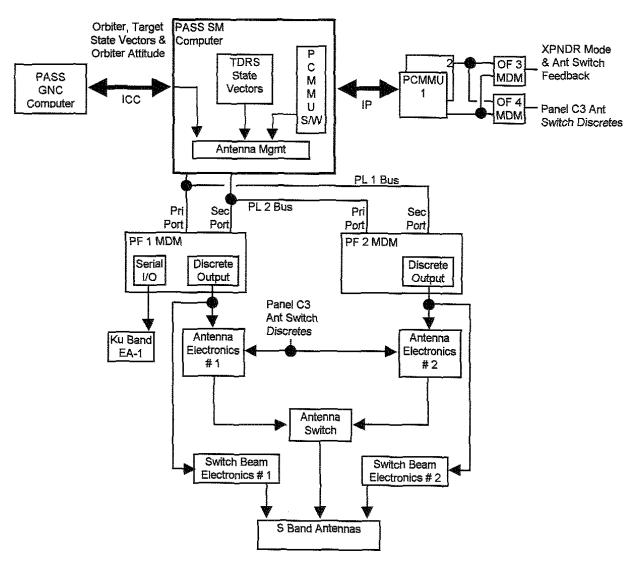

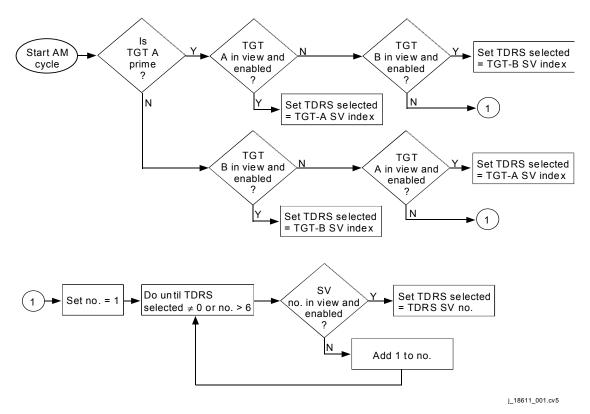

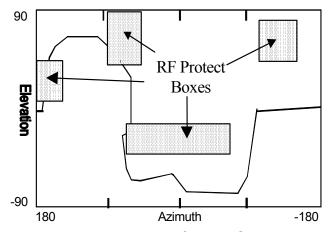

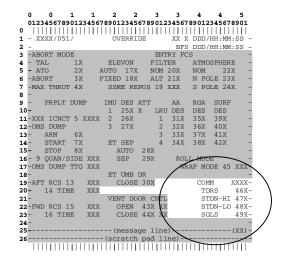

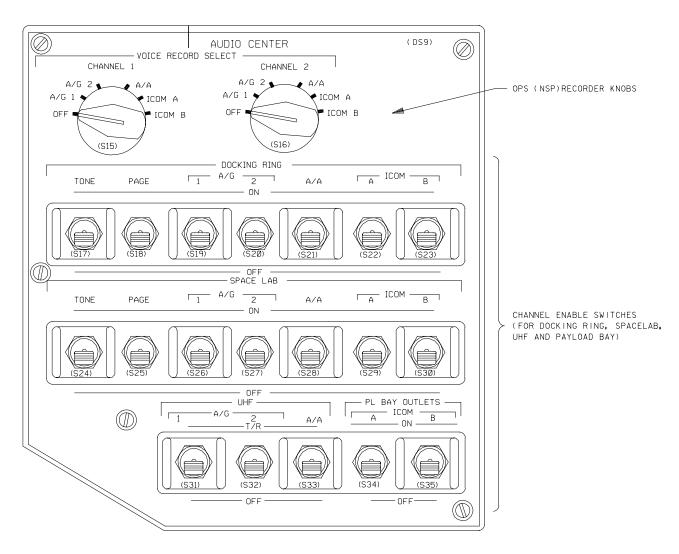

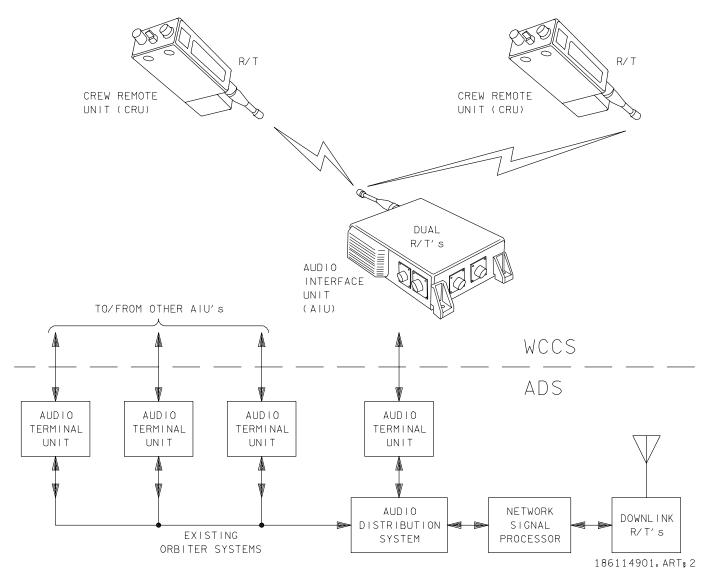

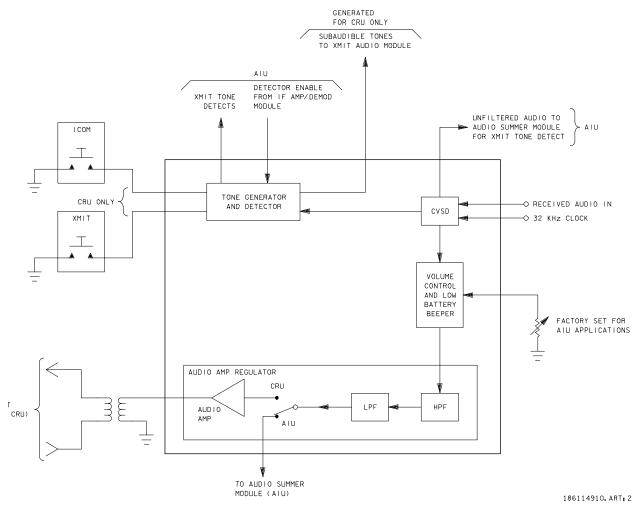

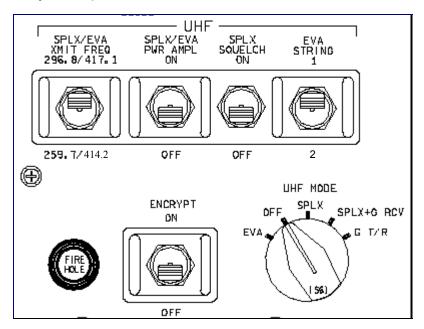

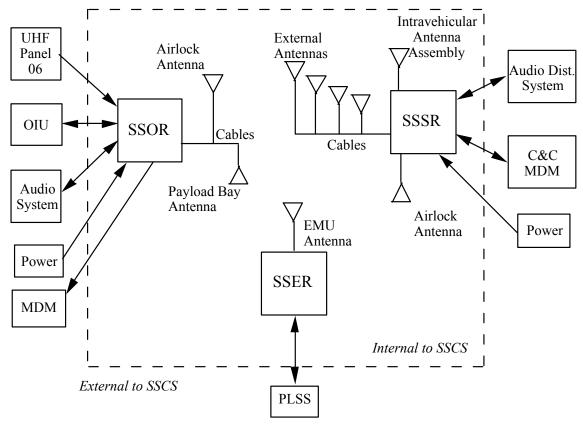

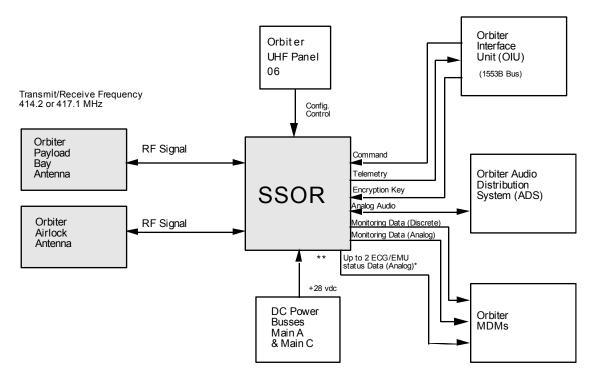

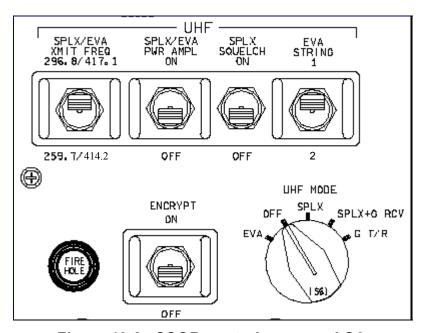

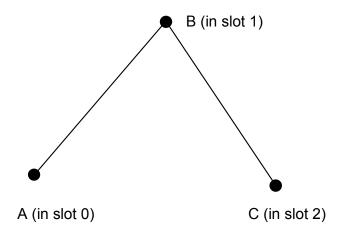

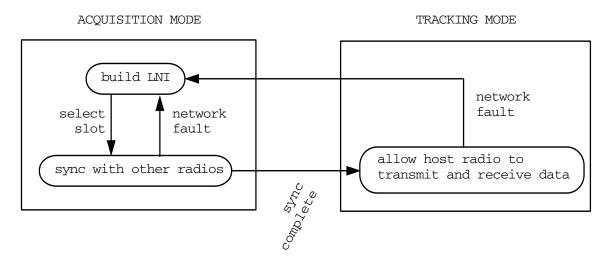

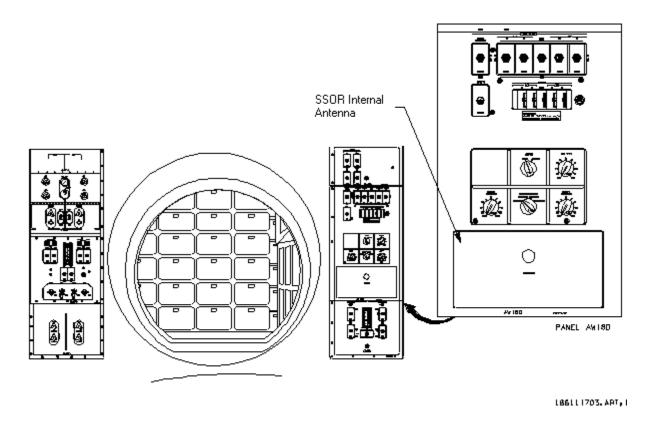

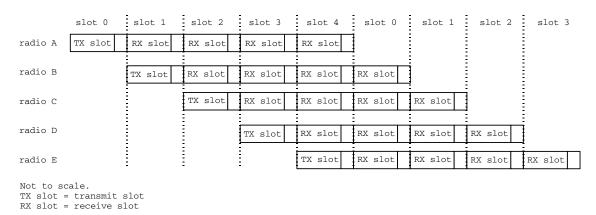

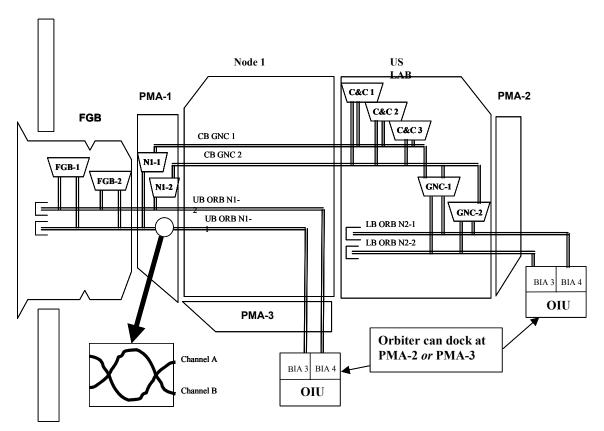

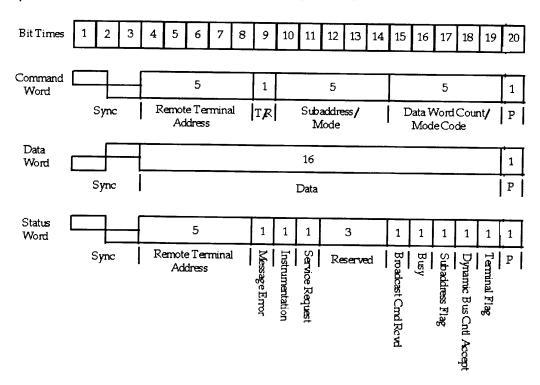

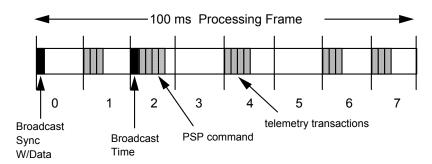

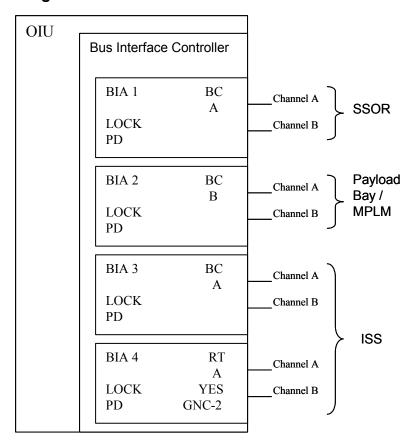

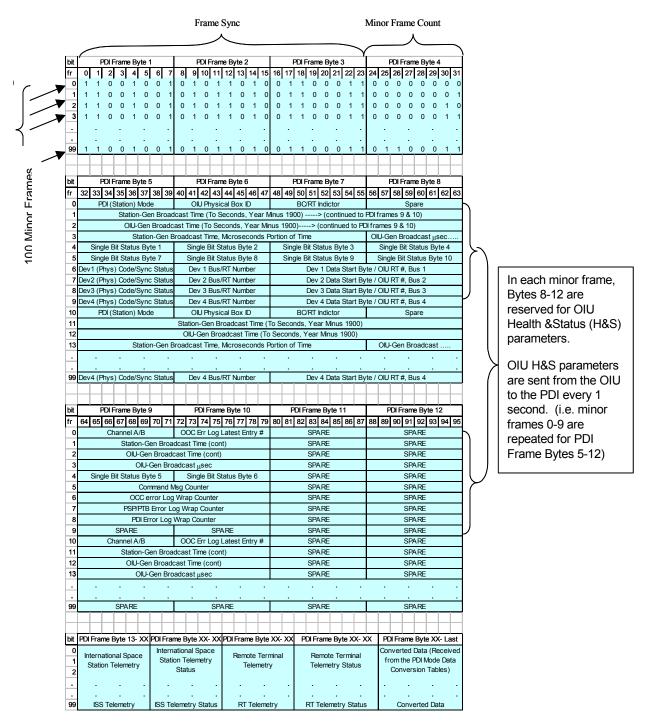

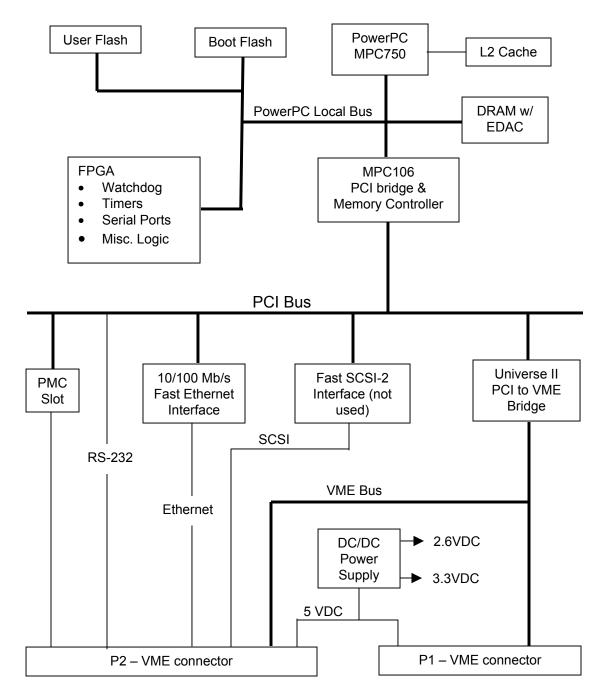

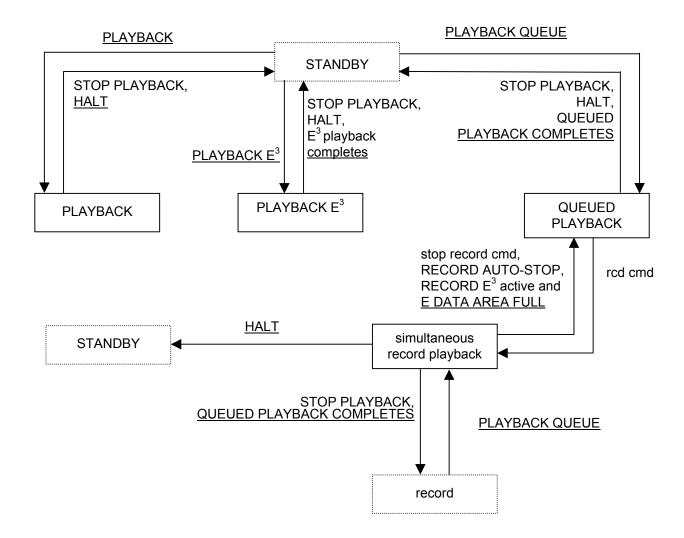

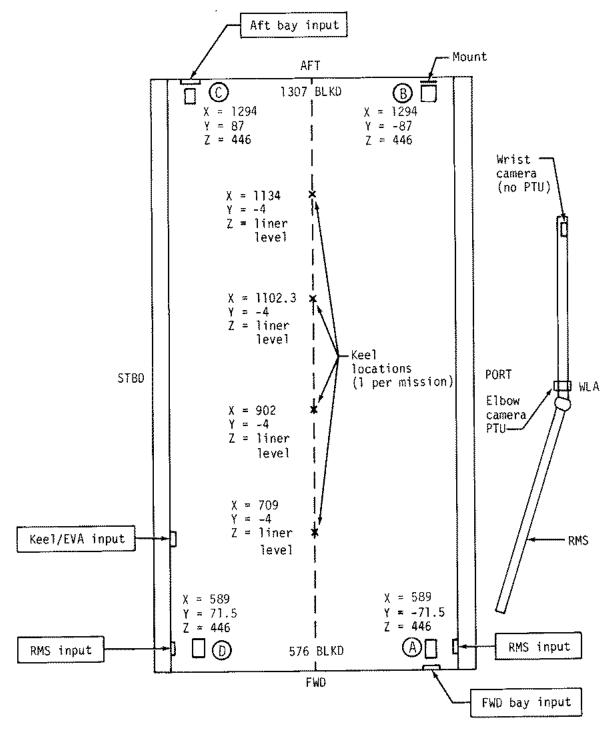

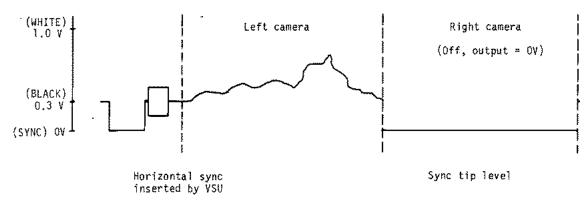

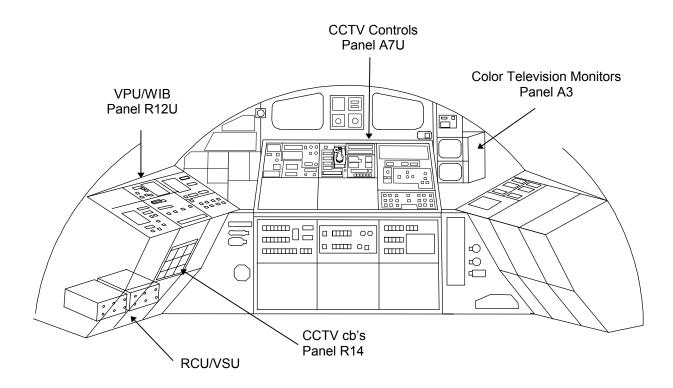

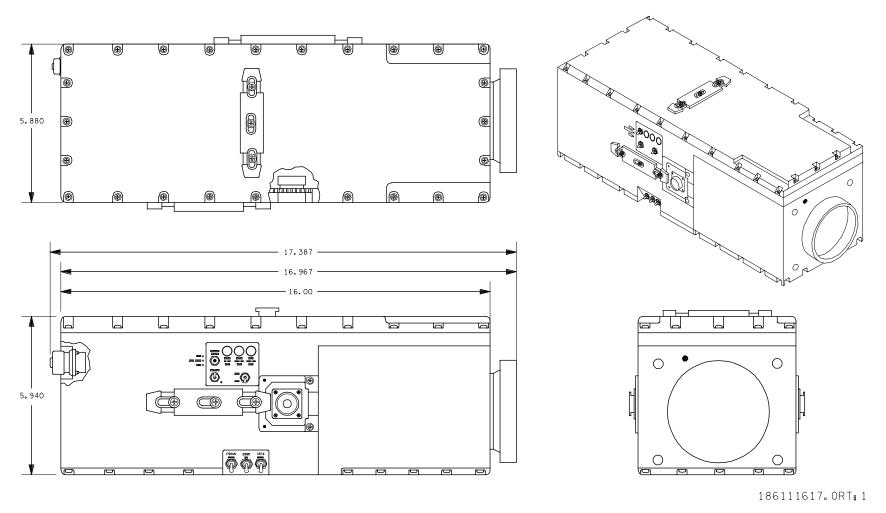

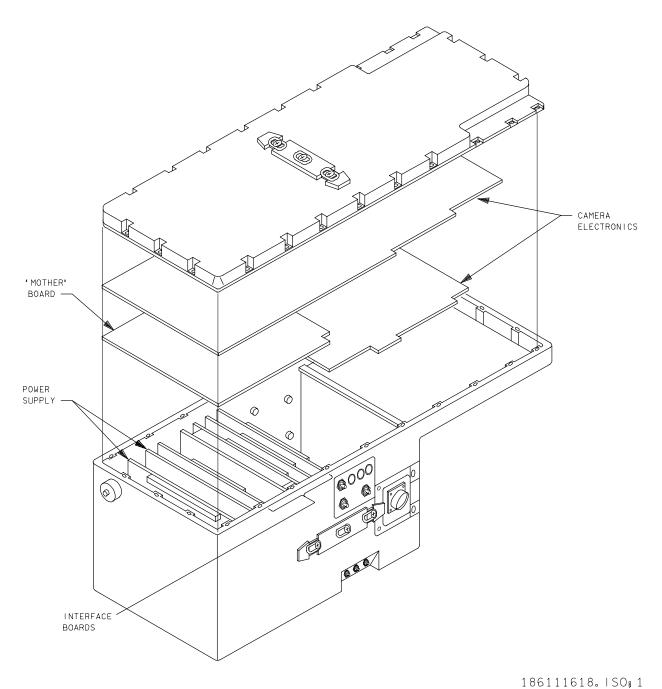

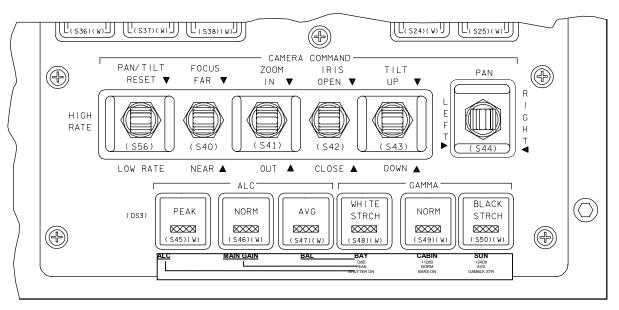

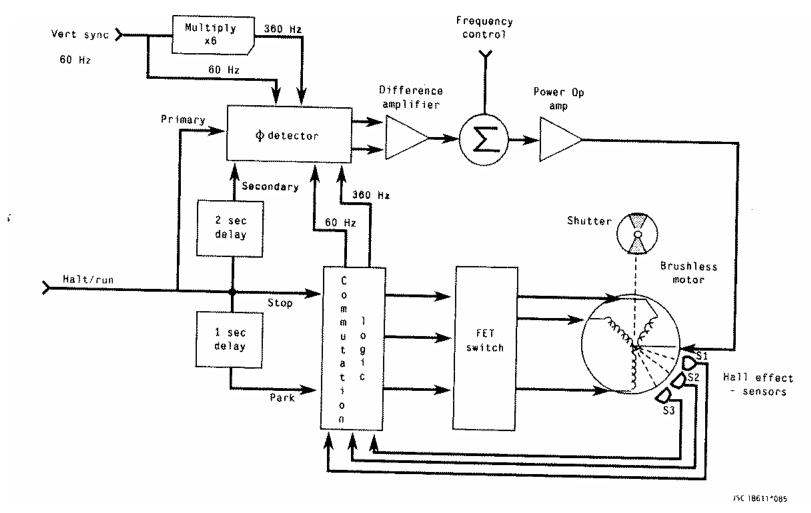

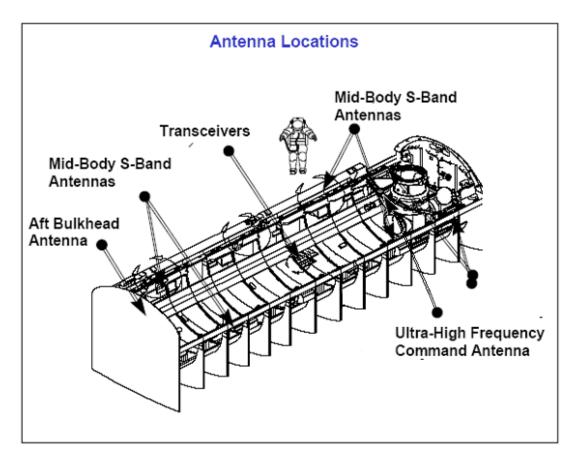

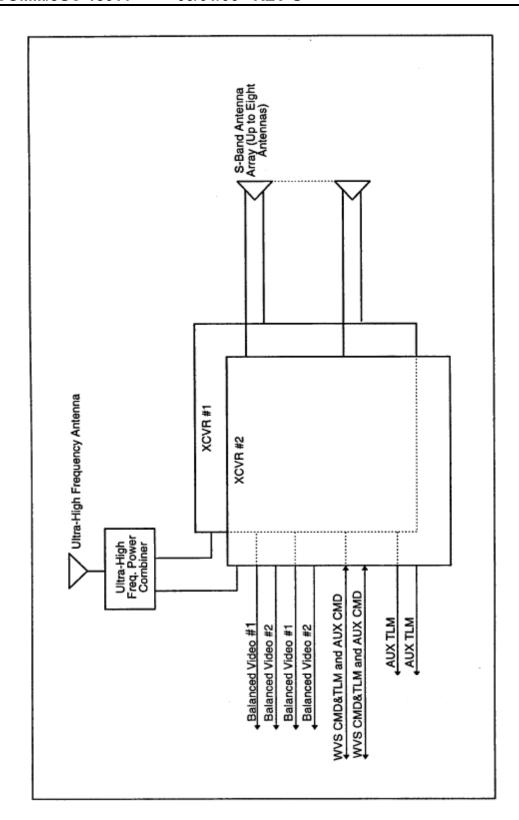

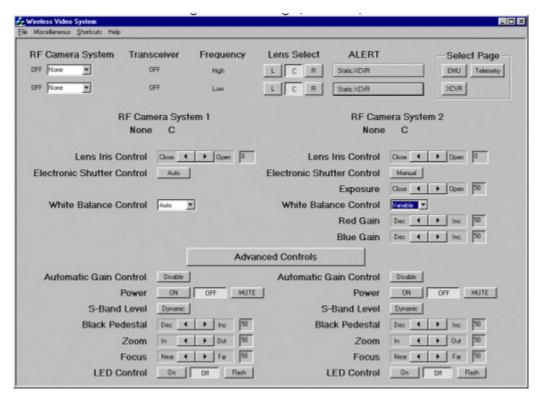

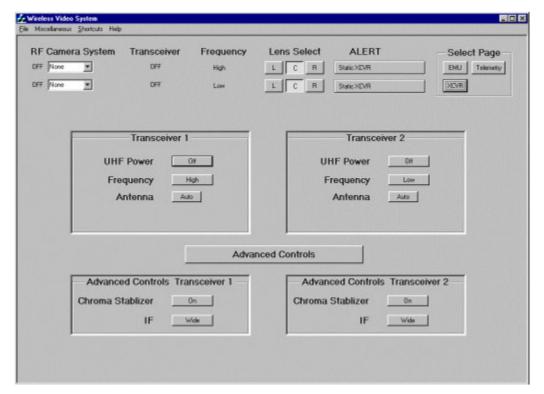

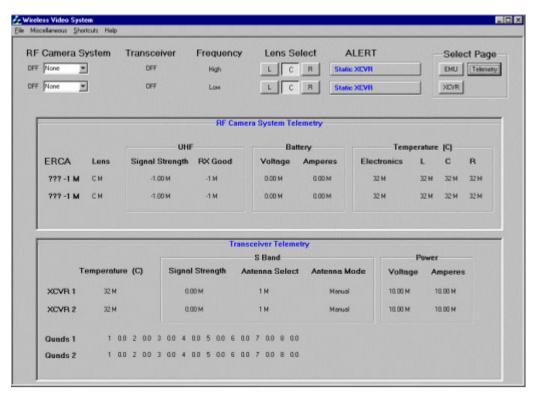

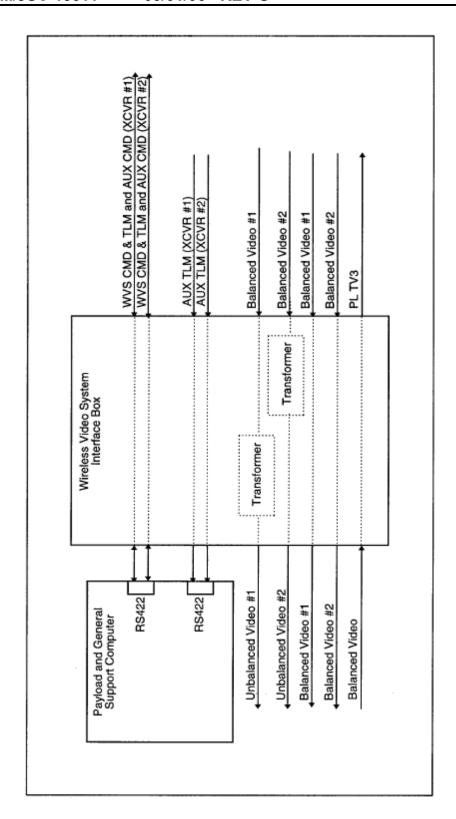

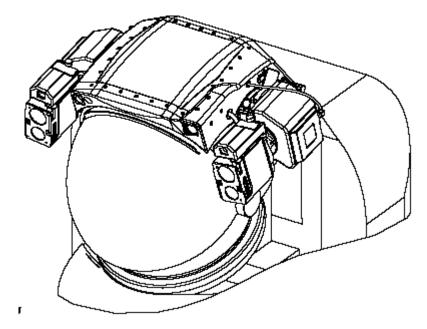

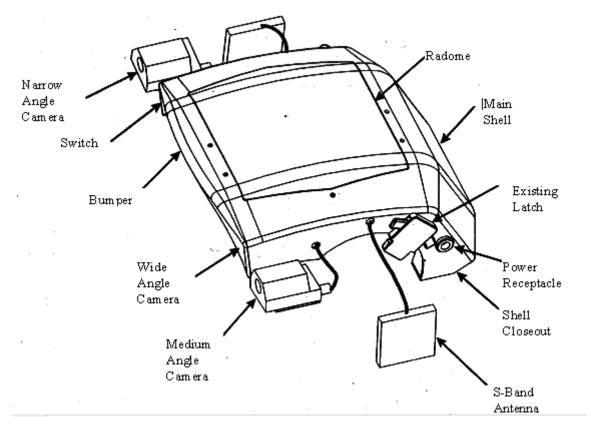

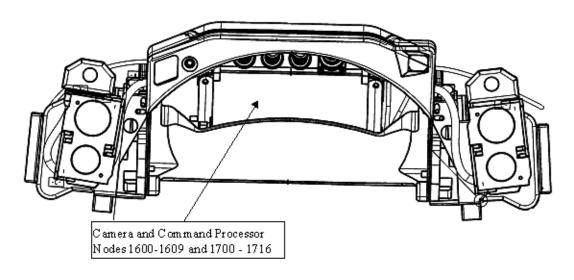

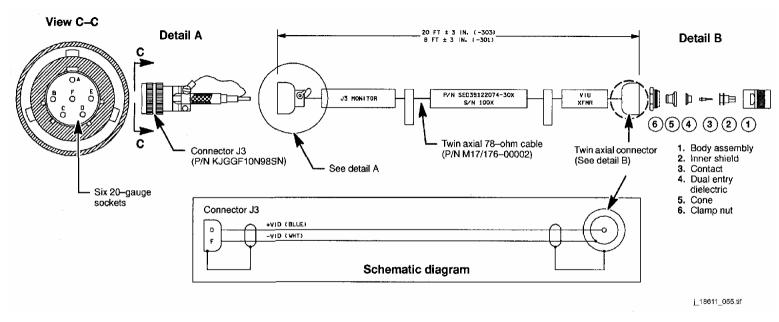

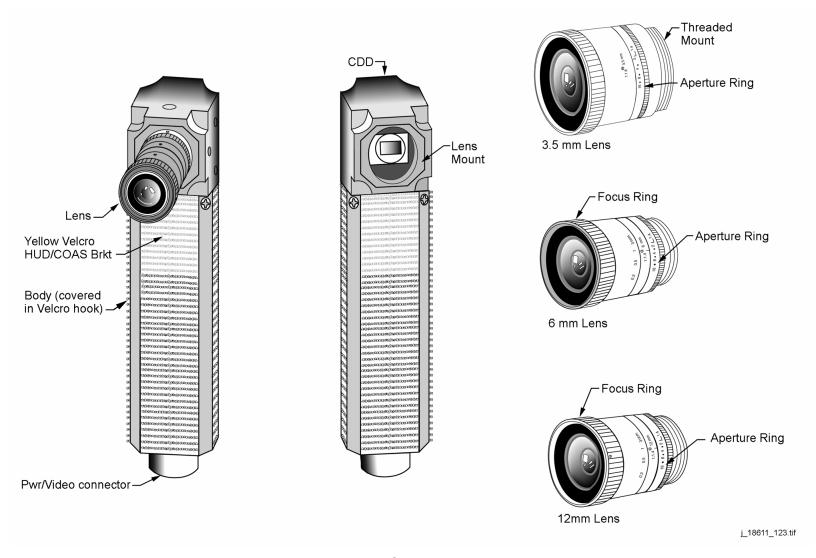

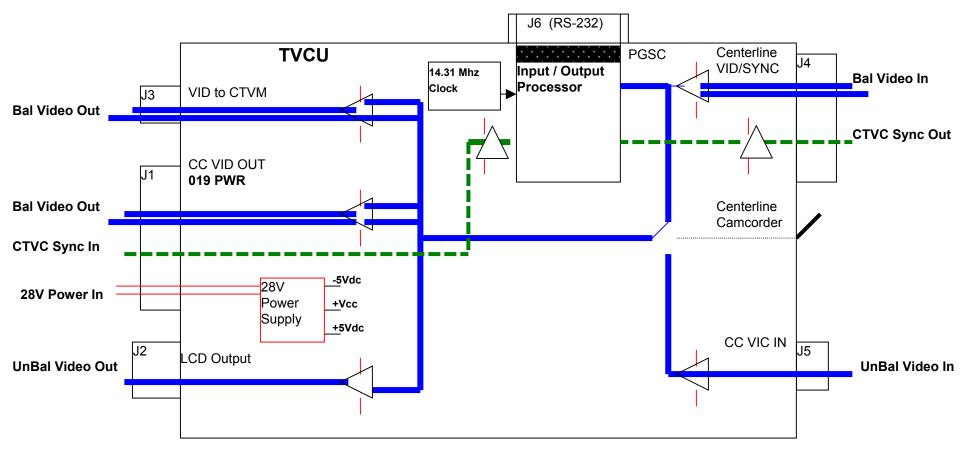

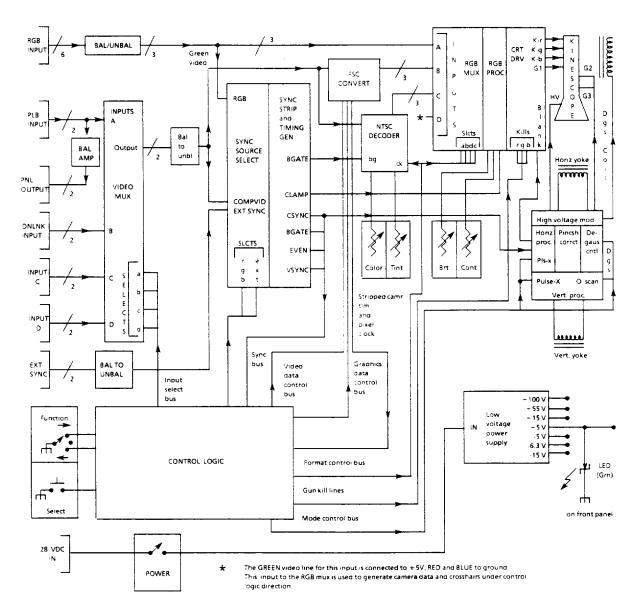

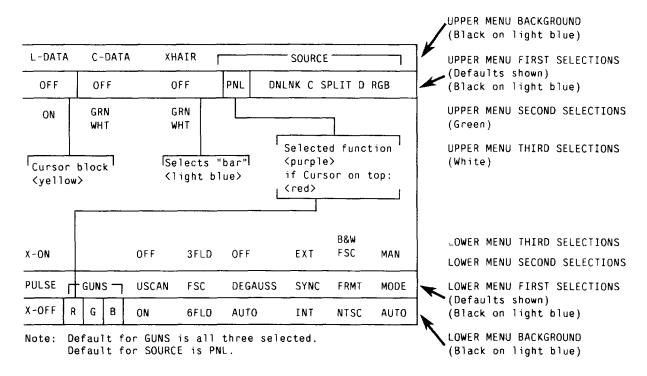

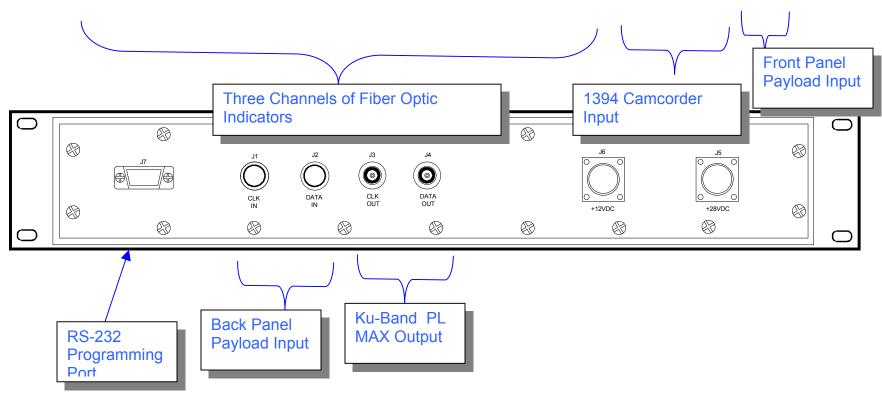

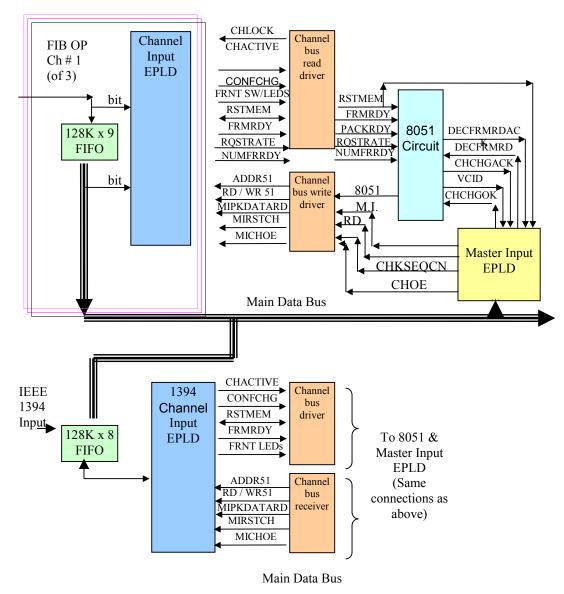

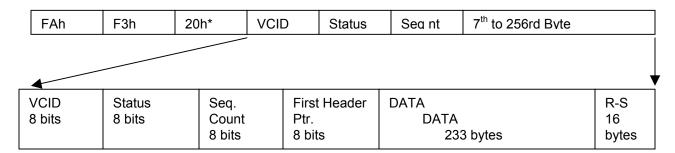

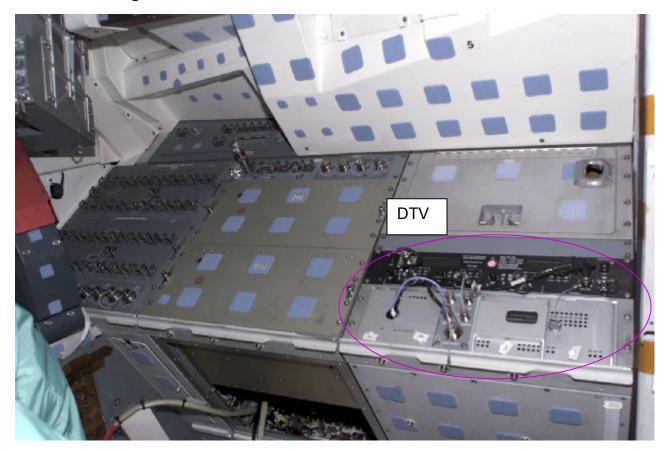

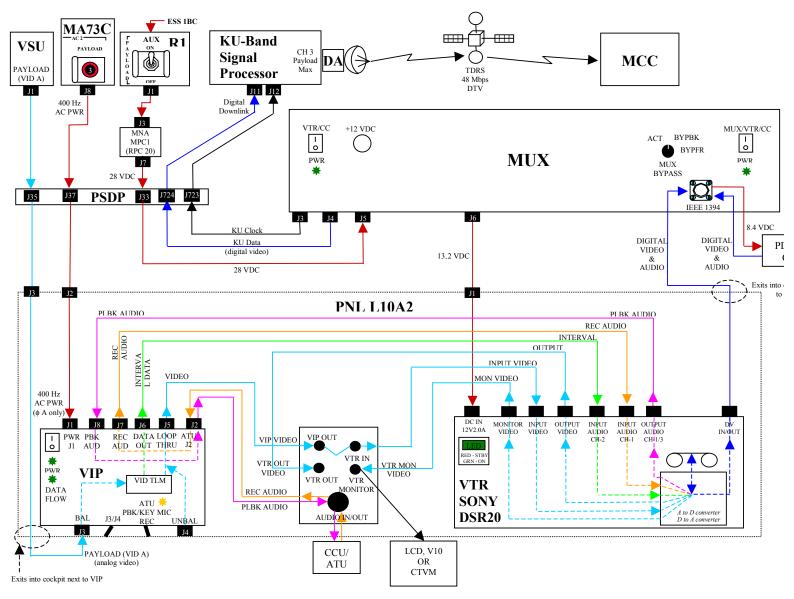

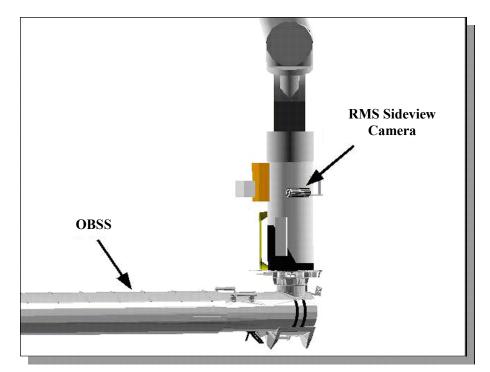

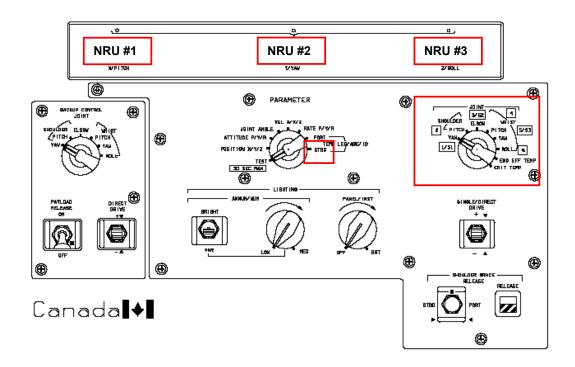

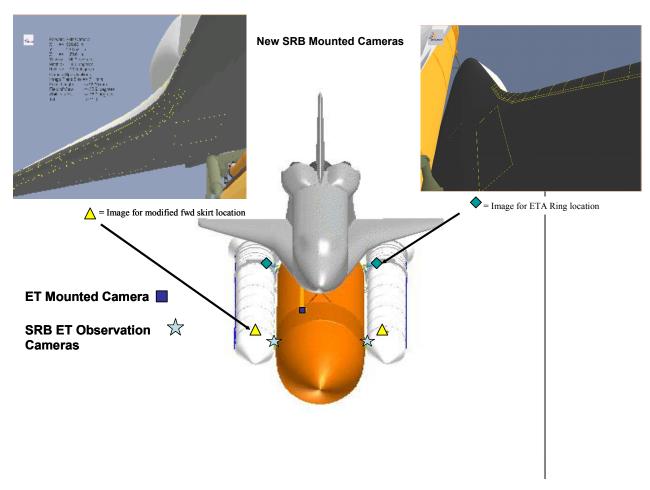

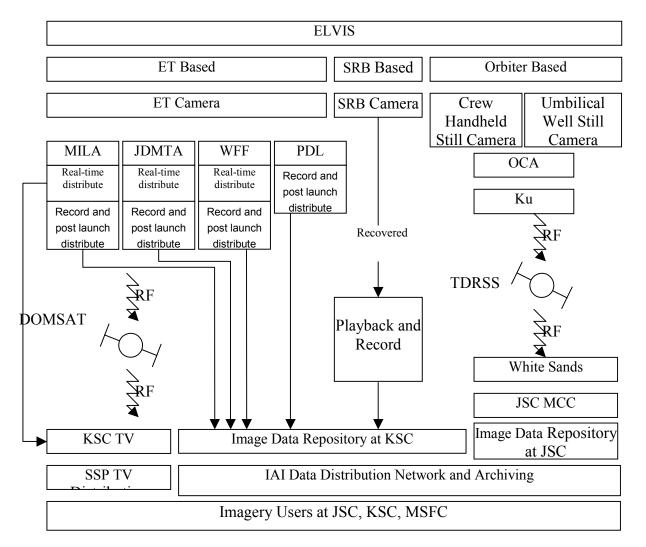

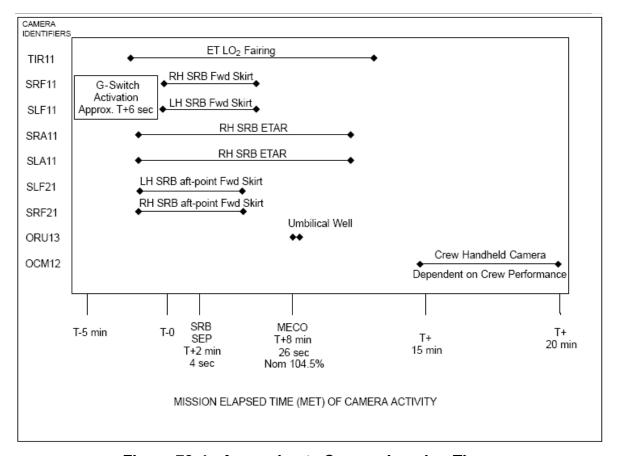

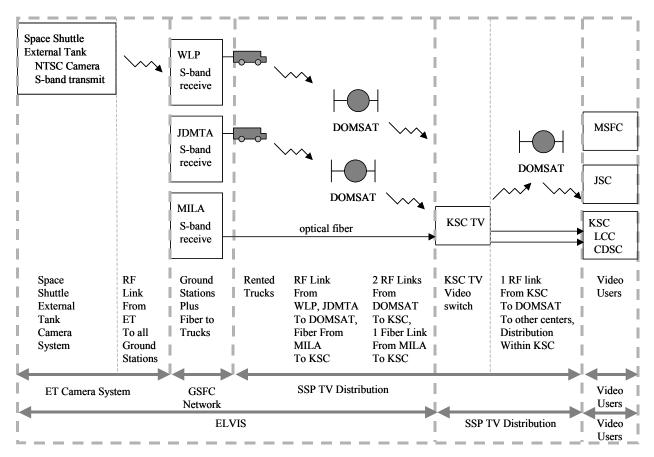

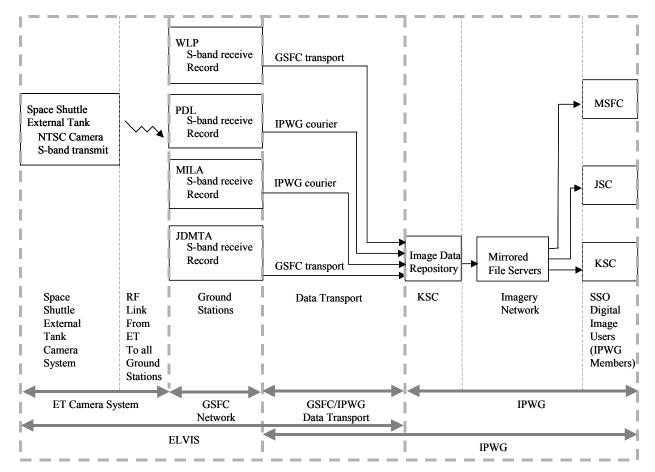

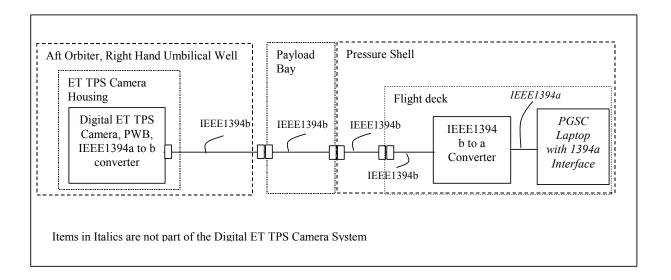

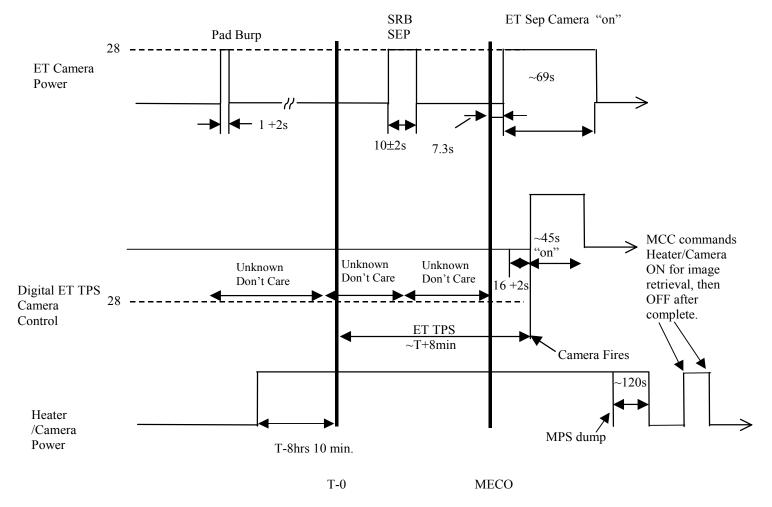

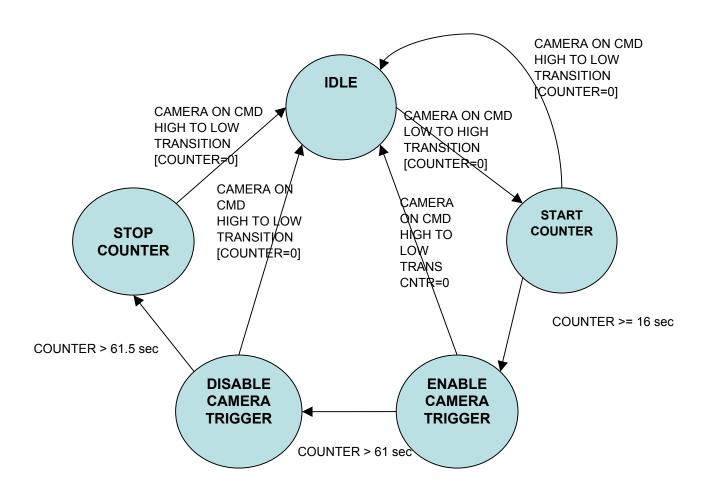

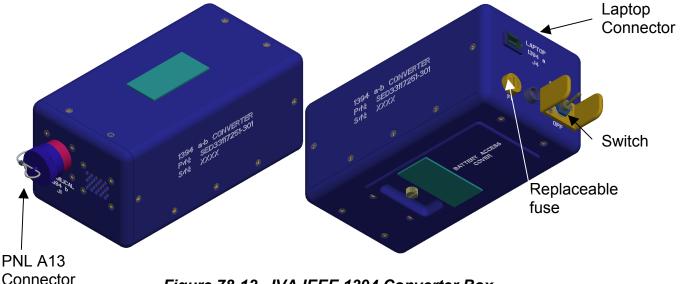

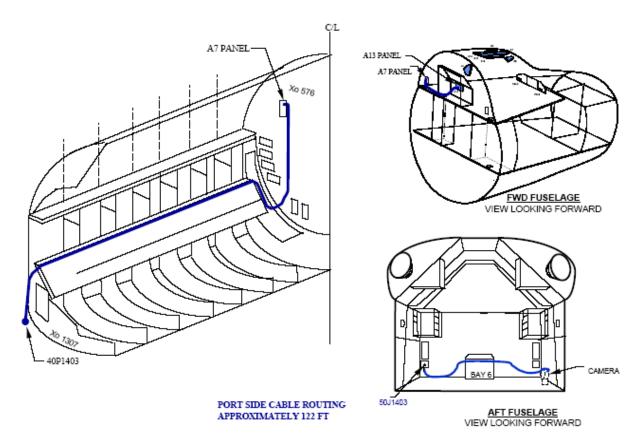

|         |       |          |           | full word parameter to be written to an                                      |