# NASA CONTRACTOR REPORT

LOAN COPY: RETURN TO AFWL (DOGL) KIRTLAND AFB, N. M.

SYSTEM CONFIGURATION AND EXECUTIVE REQUIREMENTS SPECIFICATIONS FOR REUSABLE SHUTTLE AND SPACE STATION/BASE

by J. R. Kennedy, R. T. Curran, W. S. Fitzpatrick, and J. M. Johnson

Prepared by

COMPUTER SCIENCES CORPORATION

Huntsville, Ala. 35802

for George C. Marshall Space Flight Center

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION . WASHINGTON, D. C. . MAY 1971

|                                                                                                                                               |                                                                                                                                                                                                                         |                                                                              | 007735             |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------|

| 1. REPORT NO.                                                                                                                                 | 2. GOVERNMENT ACCESSION NO.                                                                                                                                                                                             | 3. RECIPIENT'S CAT                                                           | TALOG NO.          |

| NASA CR-1820                                                                                                                                  |                                                                                                                                                                                                                         |                                                                              |                    |

| 4. TITLE AND SUBTITLE                                                                                                                         |                                                                                                                                                                                                                         | 5. REPORT DATE                                                               |                    |

|                                                                                                                                               | tive Requirements Specifications                                                                                                                                                                                        | May 1971                                                                     |                    |

| for Reusable Shuttle and Space S                                                                                                              |                                                                                                                                                                                                                         | 6. PERFORMING ORG                                                            | ANIZATION CODE     |

| 7. AUTHOR(S) J. R. Kennedy, R. T. and J. M. Johnson                                                                                           |                                                                                                                                                                                                                         | 8. PERFORMING ORGA<br>M534                                                   | NIZATION REPORT #  |

| 9. PERFORMING ORGANIZATION NAME AND AI Computer Sciences Corporation                                                                          | DDRESS                                                                                                                                                                                                                  | 10. WORK UNIT NO.                                                            |                    |

| Field Services Division, Aerosp                                                                                                               | ace Systems Center                                                                                                                                                                                                      | 11. CONTRACT OR GR                                                           | RANT NO.           |

| 8300 South Whitesburg Drive                                                                                                                   |                                                                                                                                                                                                                         | NAS8-24930                                                                   |                    |

| Huntsville, Alabama 35802                                                                                                                     |                                                                                                                                                                                                                         | 13. TYPE OF REPORT                                                           | & PERIOD COVERED   |

| 12. SPONSORING AGENCY NAME AND ADDRESS                                                                                                        |                                                                                                                                                                                                                         | Contractor Re                                                                | eport              |

| National Aeronautics and Space                                                                                                                | Administration                                                                                                                                                                                                          |                                                                              |                    |

| Washington, D. C. 20546                                                                                                                       |                                                                                                                                                                                                                         |                                                                              |                    |

|                                                                                                                                               |                                                                                                                                                                                                                         | 14. SPONSORING AG                                                            | ENCY CODE          |

| 15. SUPPLEMENTARY NOTES                                                                                                                       |                                                                                                                                                                                                                         |                                                                              |                    |

| Work performed for George C.                                                                                                                  | Marshall Space Flight Center                                                                                                                                                                                            |                                                                              |                    |

| Computation Laboratory                                                                                                                        |                                                                                                                                                                                                                         |                                                                              |                    |

| 16. ABSTRACT                                                                                                                                  |                                                                                                                                                                                                                         |                                                                              |                    |

|                                                                                                                                               |                                                                                                                                                                                                                         |                                                                              | ì                  |

| are defined which constrain or in<br>Functional requirements are def<br>Executive design requirements of<br>standards for system software for | we systems are delineated. Performpel system software to a specific rived for each respective vehicle's comprising preliminary guidelines unctional design are established. for effective operation of intricat plexes. | configuration.<br>executive system<br>, objectives, and<br>This report defin | m.<br>I<br>nes     |

| 17. KEY WORDS                                                                                                                                 | 18. DISTRIBUTION STA                                                                                                                                                                                                    | TEMENT                                                                       |                    |

|                                                                                                                                               | gement Systems Unclassified - U                                                                                                                                                                                         |                                                                              |                    |

| Executive Routine Information                                                                                                                 | on Management   Unclassified - C                                                                                                                                                                                        | milliod                                                                      | 1                  |

| Reusable Shuttle Systems                                                                                                                      |                                                                                                                                                                                                                         |                                                                              |                    |

| Avionics                                                                                                                                      | 1                                                                                                                                                                                                                       |                                                                              |                    |

| Real Time Monitor                                                                                                                             | 1                                                                                                                                                                                                                       |                                                                              |                    |

| Onboard Computer                                                                                                                              |                                                                                                                                                                                                                         |                                                                              |                    |

| <u>-</u>                                                                                                                                      |                                                                                                                                                                                                                         | Ya                                                                           |                    |

| 19. SECURITY CLASSIF. (of this report)                                                                                                        | 20. SECURITY CLASSIF. (of this page) Unclassified                                                                                                                                                                       | 21. NO. OF PAGES                                                             | 22. PRICE*<br>3.00 |

| Unclassified                                                                                                                                  | Unciassineu                                                                                                                                                                                                             | 1                                                                            | <b>0.</b> 00       |

For sale by the National Technical Information Service, Springfield, Virginia 22151

•

#### FOREWORD

The work reported herein was administered in the Systems Research Branch, Computer Systems Division, Computation Laboratory, MSFC, with Bobby C. Hodges assigned as Contracting Officer's Representative. In addition to his routine duties as Technical Monitor, Mr. Hodges has added significantly to our insight into and understanding of related NASA programs through careful planning, coordination with in-house effort, and encouragement.

#### SYSTEM CONFIGURATION

## AND

# EXECUTIVE REQUIREMENTS SPECIFICATIONS

#### FOR

#### REUSABLE SHUTTLE

AND

# SPACE STATION/BASE

# TABLE OF CONTENTS

|             |     |                                           | Page |  |  |  |

|-------------|-----|-------------------------------------------|------|--|--|--|

| SECTION I.  | INT | RODUCTION                                 | 3    |  |  |  |

|             | Α.  | General                                   | 3    |  |  |  |

|             | В.  | Scope                                     | 3    |  |  |  |

|             | c.  | •                                         | 5    |  |  |  |

|             | D.  | Executive Requirements                    |      |  |  |  |

|             | E.  | Conventions                               |      |  |  |  |

| SECTION II. | REU | JSABLE SHUTTLE                            | 9    |  |  |  |

|             | A.  | General                                   | 9    |  |  |  |

|             | В.  | Integrated Avionics System Functions      | 12   |  |  |  |

|             |     | 1. General                                | 12   |  |  |  |

|             |     | 2. Avionics System Functions              | 12   |  |  |  |

|             |     | 3. Avionics System Hardware Description   | 13   |  |  |  |

|             | C.  | Executive System Functional Requirements  | 35   |  |  |  |

|             |     | 1. General                                | 35   |  |  |  |

|             |     | 2. Central Computer Complex Monitor       | 36   |  |  |  |

|             |     | 3. Crew Display and Control Computer      | 49   |  |  |  |

|             |     | Subsystem Monitor                         |      |  |  |  |

|             |     | 4. Flight Control Subsystem Monitor       | 50   |  |  |  |

|             |     | 5. Navigation and Sensor Computer         | 60   |  |  |  |

|             |     | Subsystem Monitor                         |      |  |  |  |

|             | D.  | Executive System Performance Requirements | 62   |  |  |  |

|             |     | 1. General                                | 62   |  |  |  |

|             | •   | 2. System Performance Requirements        | 62   |  |  |  |

|             |     | 3. Subsystem Performance Requirements     | 62   |  |  |  |

|             |     | 4. Summary                                | 66   |  |  |  |

|              |                               |                                           | Page |  |

|--------------|-------------------------------|-------------------------------------------|------|--|

| SECTION III. | SPA                           | CE STATION/BASE                           | 69   |  |

|              | A.                            | General                                   | 69   |  |

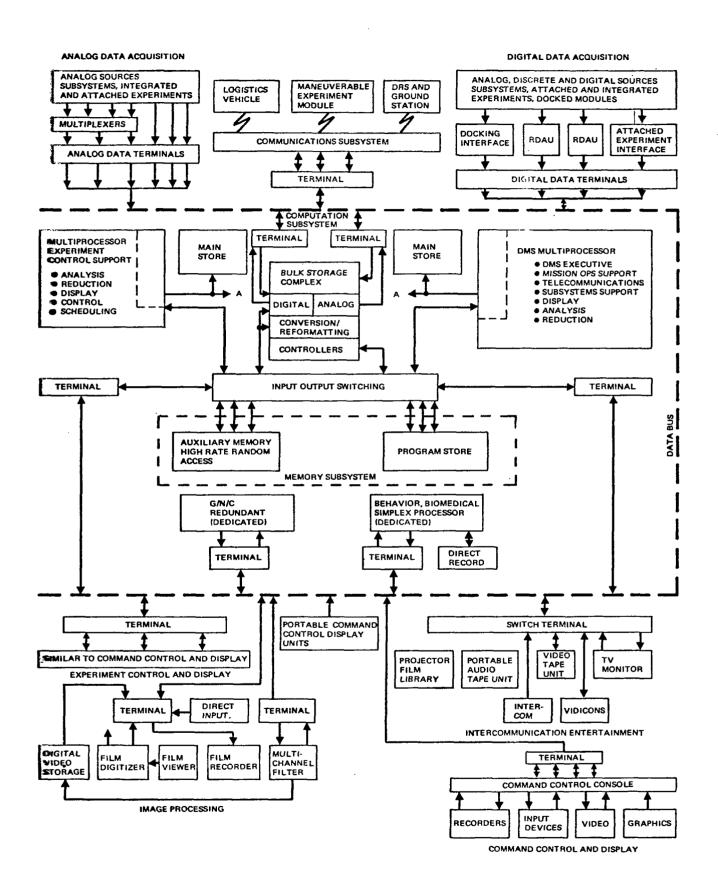

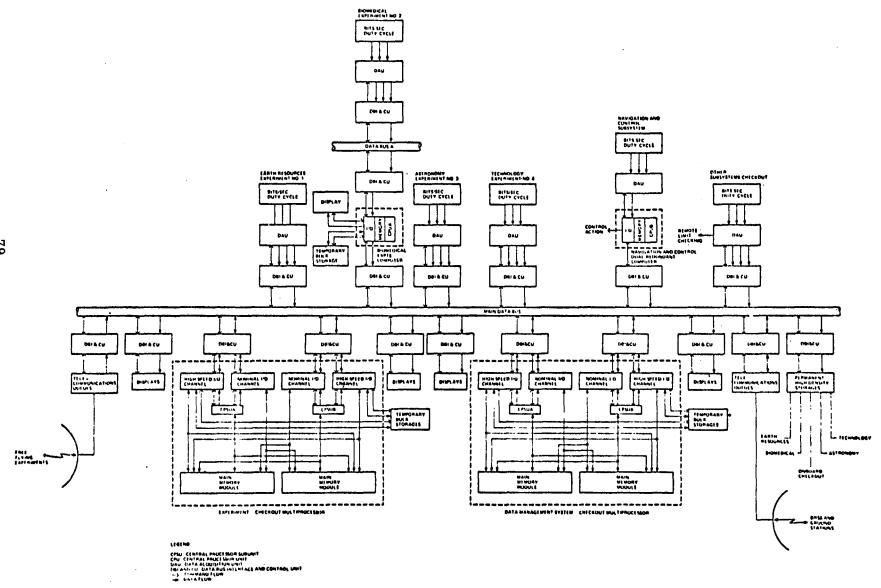

|              | в.                            | Data Management System Description        | 71   |  |

|              |                               | 1. General                                | 71   |  |

|              |                               | 2. DMS Functions                          | 71   |  |

|              |                               | 3. DMS Hardware Description               | 74   |  |

|              | C.                            | Executive System Functional Requirements  | 94   |  |

|              |                               | 1. General                                | 94   |  |

|              |                               | 2. DMS Executive                          | 103  |  |

|              |                               | 3. GNC Executive                          | 109  |  |

|              |                               | 4. Biomedical Executive                   | 112  |  |

|              | D.                            | Executive System Performance Requirements | 120  |  |

|              |                               | 1. System Performance                     | 120  |  |

|              |                               | 2. Subsystem Performance                  | 121  |  |

| SECTION IV.  | EXECUTIVE DESIGN REQUIREMENTS |                                           |      |  |

|              | Α.                            | General                                   | 131  |  |

|              | В.                            | Procedure Design Requirements             | 132  |  |

|              |                               | 1. Attribute Specification                | 132  |  |

|              |                               | 2. <u>Documentation Standards</u>         | 135  |  |

|              |                               | 3. Performance Measurement                | 135  |  |

|              | C.                            | Data Design Requirements                  | 138  |  |

|              |                               | 1. External Data Attribute Specification  | 138  |  |

|              |                               | 2. External Data Documentation Standards  | 140  |  |

|              | D.                            | Level of Design Detail                    | 140  |  |

|              |                               | 1. Executive Functions                    | 140  |  |

|              |                               | 2. Executive Modules                      | 145  |  |

|              | $\mathbf{E}_{ullet}$          | Evaluation and Comparison Methodology     | 147  |  |

|              |                               | 1. Evaluation                             | 148  |  |

|              |                               | 2. Comparison                             | 154  |  |

| REFERENCES   |                               |                                           | 158  |  |

| BIBLIOGRAPHY |                               |                                           | 159  |  |

# LIST OF ILLUSTRATIONS

| Figure  | Title                                                          | Page       |

|---------|----------------------------------------------------------------|------------|

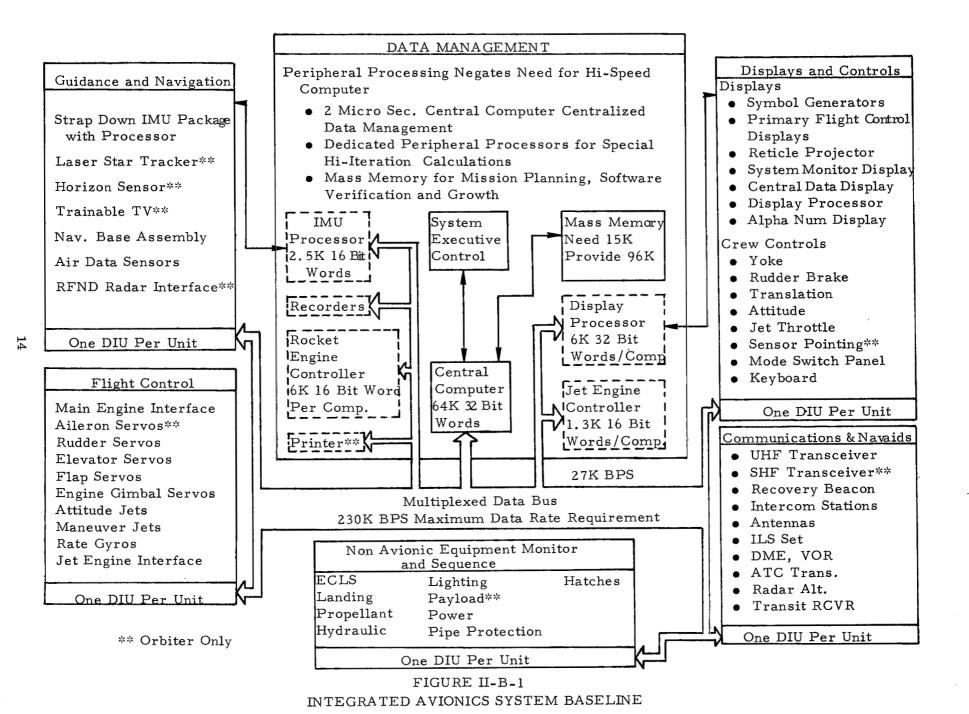

| п-в-1   | Integrated Avionics System Baseline                            | 14         |

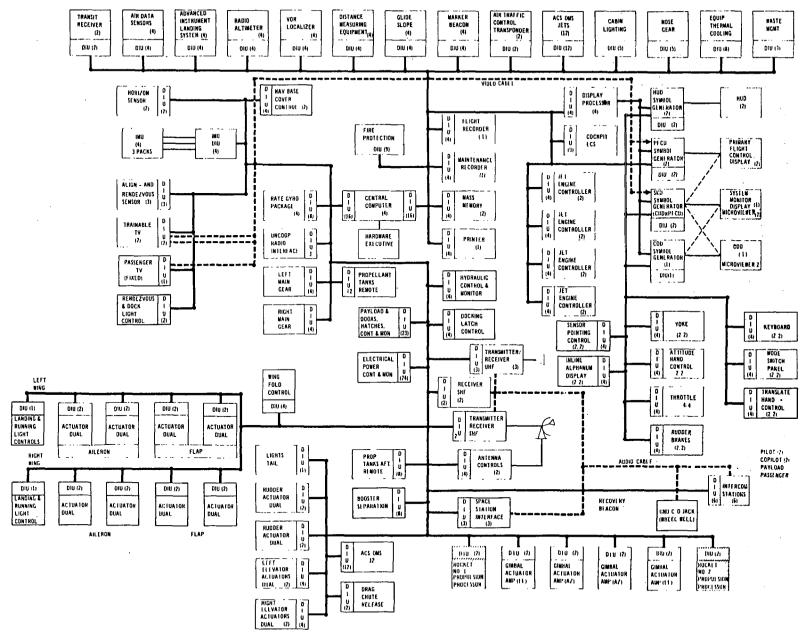

| II-B-2  | Space Shuttle Avionics System                                  | 15         |

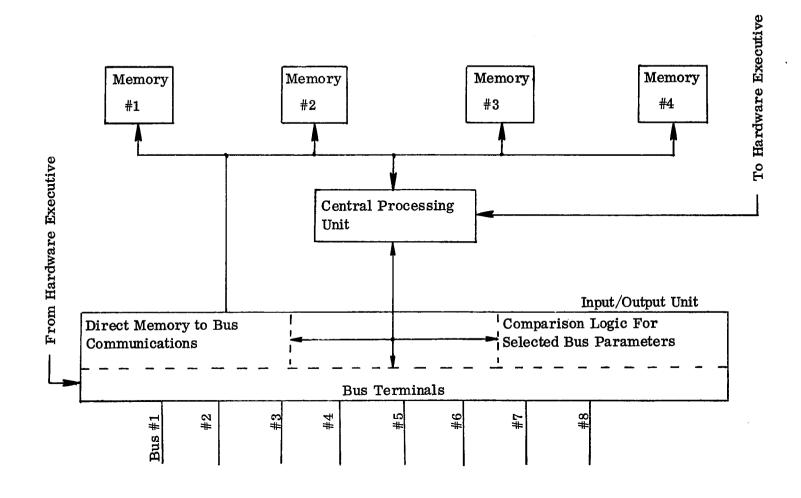

| II-B-3  | Baseline Computer Functional Diagram                           | 17         |

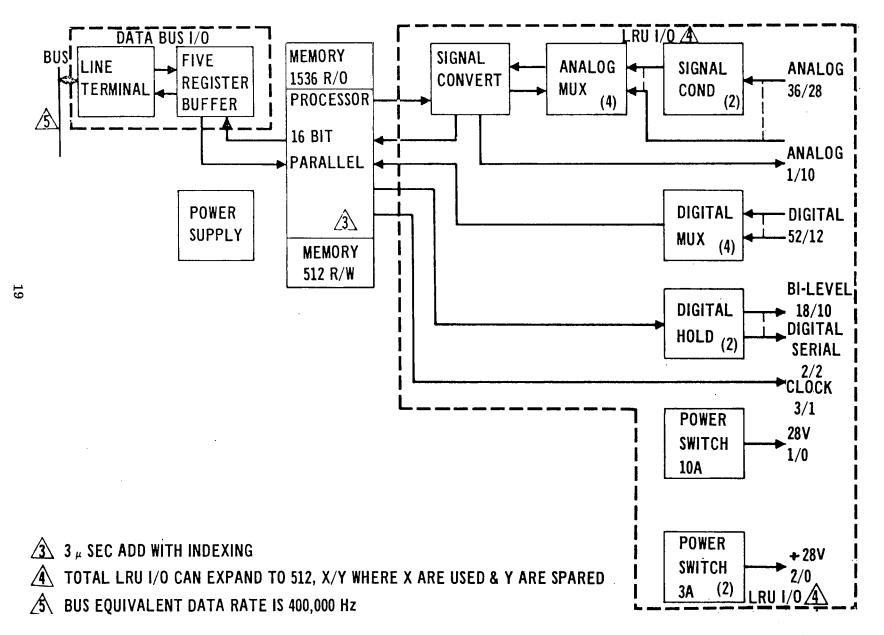

| п-в-4   | Inertial Measuring Unit DIU                                    | 19         |

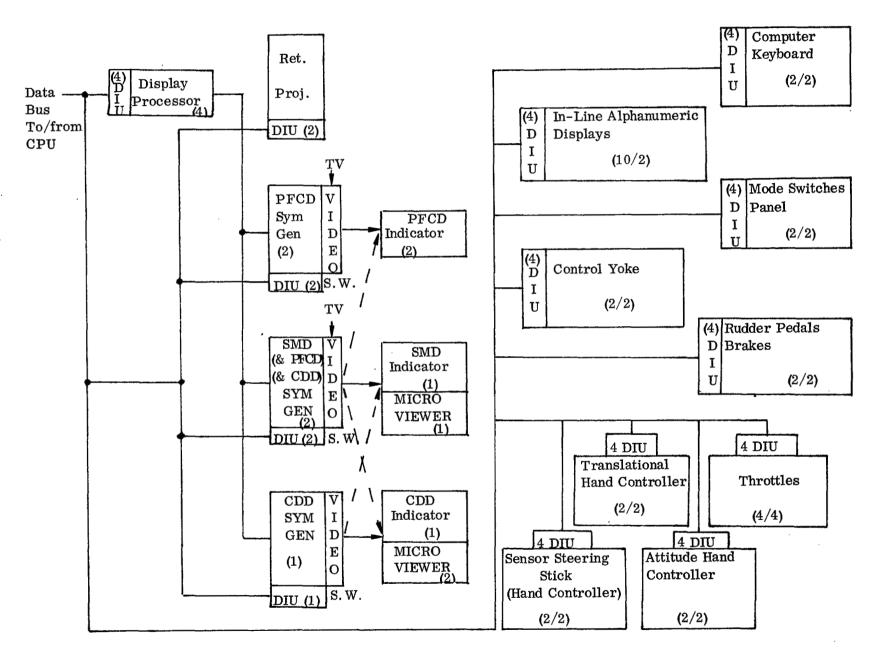

| II-B-5  | Controls & Display Baseline System Schematic                   | 20         |

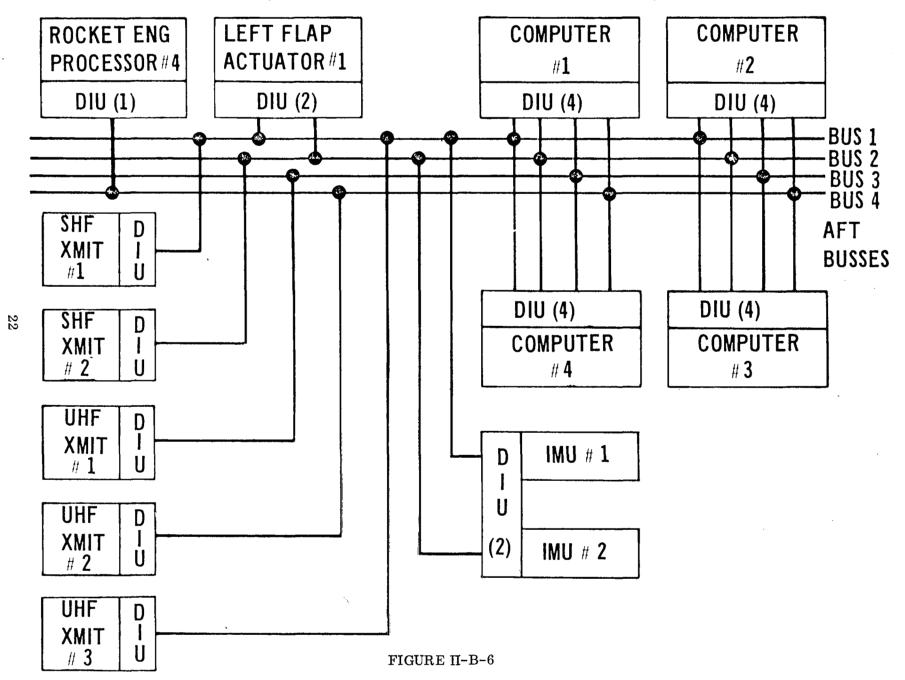

| п-в-6   | Simplified Data Bus                                            | 22         |

| II-B-7  | Dedicated Special Computer Configuration                       | 23         |

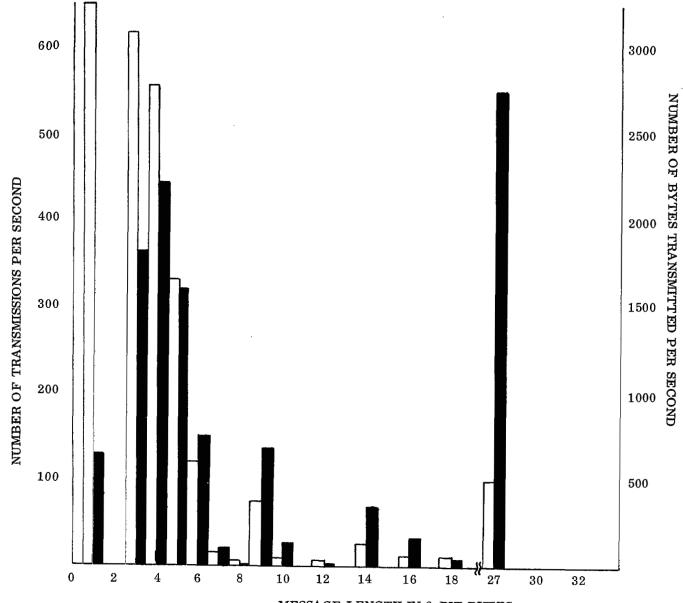

| II-B-8  | Data Transmission Distribution for the<br>Orbiter Aft Bus      | 24         |

| II-B-9  | Data Bus Message Structure                                     | 26         |

| II-B-10 | Reconfigurable Computer Functional Diagram                     | 27         |

| II-B-11 | Power and Mode Reconfiguration of Subsystems                   | 29         |

| п-в-12  | Checkout Functions                                             | 30         |

| II-B-13 | Display Checkout                                               | 31         |

| II-B-14 | IMU Checkout                                                   | 32         |

| II-B-15 | Central Computer Checkout                                      | 33         |

| п-В-16  | Computer Switching                                             | 34         |

| п-С-1   | Relationship of Kernel to the Remainder of the System          | 40         |

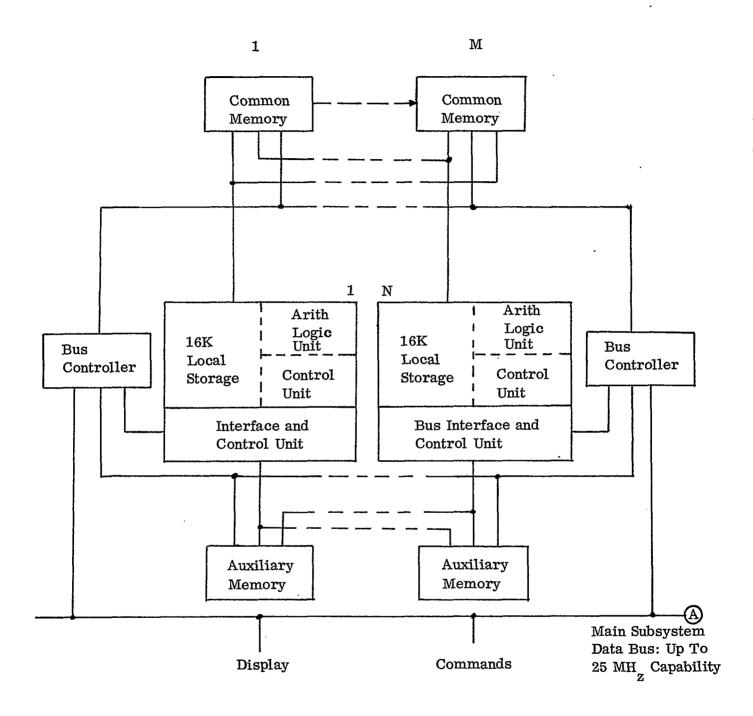

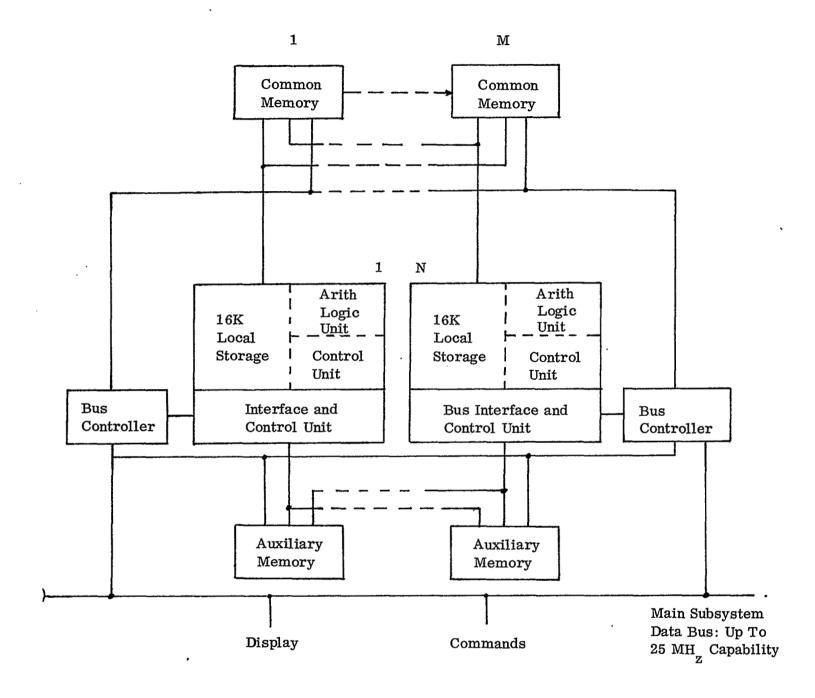

| ІП-В-1  | Distributed Multiprocessor Configuration;<br>Part A and Part B | 75-76      |

| III-B-2 | DMS Block Diagram                                              | <b>7</b> 8 |

| Figure  | Title                                                   | Page         |

|---------|---------------------------------------------------------|--------------|

| III-B-3 | Distributed Computer Configuration                      | 79           |

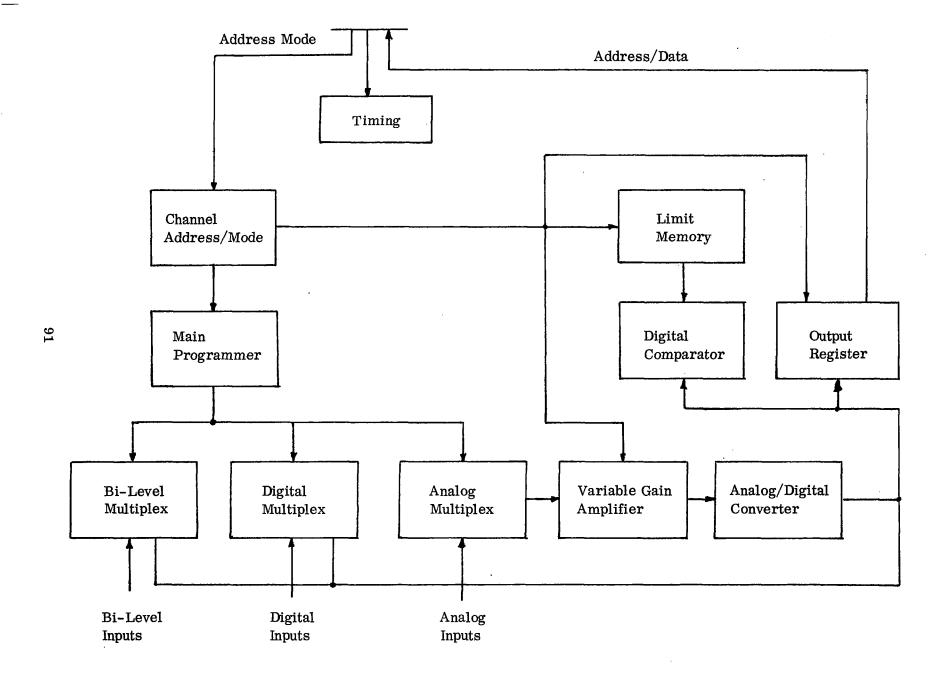

| ІП−В−4  | Design Reference Module Data Acquisition<br>Subsystem   | 87           |

| III-B-5 | Digital Data Terminal                                   | 89           |

| ш-в-6   | Analog Terminal                                         | 90           |

| ПІ-В-7  | Remote Data Acquisition Unit                            | 91           |

|         |                                                         |              |

| III-D-1 | Interface Identification                                | 122          |

| III-D-2 | Digital Data Interfaces to Data Terminals               | 123          |

| Ш-D-3   | Space Station Subsystem Data Acquisition Requirements   | 127          |

| ПІ-D-4  | Computer Subsystem Performance Requirements             | 1 <b>2</b> 8 |

| IV-B-1  | Form 1: Procedure Attribute Documentation Format        | 133          |

| IV-B-2  | Form 2: Functional Procedure Description Format         | 136          |

| IV-C-1  | Form 3: External Data Attribute Documentation<br>Format | 139          |

| IV-C-2  | Form 4: Functional External Data Description<br>Format  | 141          |

| IV-E-1  | System Feature Summary                                  | 150          |

| IV-E-2  | System Procedure Attributes                             | 156          |

| IV-E-3  | System Comparison Summary                               | 157          |

#### DEFINITION OF SYMBOLS

Symbol

Definition

ACK

Acknowledge

AIOP

Analog Input/Output Package

ALU

Arithmetic Logic Unit

AM

Amplitude Modulation

A/D

Analog to Digital

ASM

Assembly

BIT

Built In Test

CC

Central Computer

CCC

Central Computer Complex

CDD

Central Data Display

COSY

Checkout Operating System

CPU

Central Processing Unit (including ALU)

**CPSU**

Central Processor Subunit

CRT

Cathode Ray Tube

DAU

Data Acquisition Unit

DBI & CU

Data Bus Interface and Control Unit

DCC

Crew Display and Control Computer

DIOP

Digital Input/Output Package

DIU

Data Interface Unit

$\mathbf{DMS}$

Data Management System

DRSS

Data Relay Satellite System

Symbol

Definition

**ECLS**

Environmental Control and Life Support

ECR

**Executive Control Routines**

ELD

Error Logging Device

EOM

End of Message

ERD

Error Recording Device

EVA

Extra Vehicular Activity

FCS

Flight Control Subsystem

FDM

Frequency Division Multiplexing

$\mathbf{F}\mathbf{F}$

Free Flight

FO/FO/FS Fail Operational, Fail Operational, Fail Safe

**FWA**

First Word Address

G&N

Guidance and Navigation

GNC

Guidance, Navigation, and Control

HE

Hardware Executive

IAS

Integrated Avionics System

$\mathbf{IF}$

Intermediate Frequency

IMU

Inertial Measurement Unit

IOCU

Input/Output Control Unit

ЮР

Input/Output Package

I/O

Input/Output

JEP

Jet Engine Processor

$\mathbf{K}$

One Thousand (or 1,024)

**KBS**

Kilo Bits/Second

KB

Keyboard

Symbol Definition

KB/sec. Kilo Bits/second

LRU Line Replaceable Unit

LU Logical Unit

LSI Large Scale Integration

MBPS Million Bits/Second

MDC McDonnell Douglas Corporation

MODEM Modulator/Demodulator

MSA Main Store Allocator

MUX Multiplexer

NSC Navigation and Sensor Computer

OCS Onboard Checkout System

OS Operating System

PFCD Primary Flight Control Display

POL Problem Oriented Language

RDAU Remote Data Acquisition Unit

REP Rocket Engine Processor

ROM Read Only Memory

R/W Read/Write

SDI Standard Data Interface

SHF Shared High Frequency

SMD Systems Monitor Display

SOM Start of Message

Symbol

Definition

TBD

To Be Defined

TDM

Time Division Multiplexing

TLC

Time Line Controller

TTY

Teletype

UHF

Ultra High Frequency

XMIT

Transmitter

# SYSTEM CONFIGURATION AND EXECUTIVE REQUIREMENTS SPECIFICATIONS FOR REUSABLE SHUTTLE AND SPACE STATION/BASE

#### SUMMARY

The two major concerns of this document have been descriptions of the computational systems hardware and the requirements analysis of their impact on executive software development. The report outlines what are believed to be the current conceptual trends for both reusable shuttle and space station computational hardware. These discussions are in light of their effect on software executive requirements, of course. Specification of performance and functional executive software requirements for computer complexes on the reusable shuttle and on the space station are derived separately. A single set of design requirements is developed to apply to both systems. Design procedures and evaluation criteria have equal applicability to both systems.

The reusable shuttle executive software system operates in the environment of a distributed multi-computer system with dedicated computer subsystems. Logical procedure modules are derived to satisfy the requirements arising from interaction of mission requirements, avionics hardware and applications.

The space station executive software operates in an environment with many functional similarities and some important differences in hardware and applications. Hardware differences lie in the fact that the space station computer system does not exhibit dedicated characteristics to the degree that these characteristics are exhibited in the reusable shuttle. The applications or environment difference is caused by the existence of requirements to support experiments with high data rates, archival of results, and other more complex data management requirements.

Differences in mission, hardware, and level of available information cause separate treatments of the two executive software systems. Experience in computer applications with similar attributes has been drawn on in the definition of the executive software functional requirements for each.

|  |  |  |  | · |  |

|--|--|--|--|---|--|

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

|  |  |  |  |   |  |

#### SECTION I. INTRODUCTION

#### A. General

The development of design specifications for flight operational executive systems to support major NASA spaceborne electronics systems in the coming decades is an activity currently receiving growing attention. A primary objective of the Marshall Space Flight Center Computation Laboratory's Systems Research Branch has been a continuing effort to broaden the scope of awareness in the areas of future on-board executive system concept formulation and design philosophy. The purposes of this objective are manifold, in that many related benefits accrue from a coherent and persistent effort to refine the overall understanding of spaceborne executive systems. Some obvious benefits are:

- NASA can guide efforts in this area with clearer goals in mind,

- Proposed concepts can be more intelligently evaluated,

- The general state-of-the-art of the computing sciences may be enhanced, and

- Greater cost effectiveness can result.

to name but a few. This report, therefore, supports major NASA objectives through delineation and outline of spaceborne computer systems hardware features and executive system requirements for both the reusable shuttle and earth orbiting space station.

#### B. Scope

The development effort required for each of the vehicle software systems consists of Flight System Analysis and Software Development.

- 1. Flight System Analysis. This activity includes:

- Functional Specification

- Operational Specification

- Performance Specification

- Concept Formulation

- Algorithm Identification

- Simulation

- Equation Formulation

- Algorithm Evaluation

- System Functional Alternatives

- Trade Analyses

## 2. Software Development. This activity includes:

- Requirements Analysis

- System Design

- Program Functional Design

- Program Component Detail Design

- Program Component Coding

- Program Component Checkout

- Software Integration and Test

- Flight Readiness Verification

Flight System Analysis consists of mission problem analysis oriented toward determining and defining the solutions to mission problems such as vehicle guidance and control, experiments control, etc. Software Development, which can, to a limited degree, run concurrent with Flight Systems Analysis but generally follows it, consists of the total process of defining, designing, fabricating, and testing of the required software/hardware complexes.

The scope of this report is not broad enough to address any aspects of Flight System Analysis. This activity is currently being pursued under other NASA contracts, and preliminary reports are only now becoming available.

The two major concerns of this report have to do with descriptions of the computer systems hardware and the requirements analysis aspect of Software Development as it applies to executive systems for control of the space system computers.

#### C. Vehicle Electronics System Descriptions

Subheadings in Sections II and III of the report outline what are believed to be the most recent trends in concepts for flight hardware for both the shuttle and station. Every effort was made to critically survey all formal documentation describing requirements and trade studies leading to the designs depicted in this report; in many cases, preliminary and informal documentation was correlated to achieve a better perspective. However, much of the on-going design process is being executed in the fashion of a painter capturing a changing scene on canvas. For this reason, and also because we have attempted to observe the results of a process while it is evolving, we have managed to extract and describe only a "broad-brush" version of the system hardware; very little architectural detail has been defined and is therefore not described in the report. Since the primary concern here is with the computers and their gross relation to other subsystems, detail concerning other subsystems was, for the most part, intentionally supressed.

The report then concentrates on the computer complexes, mass and/or auxiliary storage, and the data bus subsystems. This is felt to be sufficient for support of a future executive functional design effort.

#### D. Executive Requirements

Requirements are considered to be grouped into classes depending on their nature as follows:

- Design Requirements

- Performance Requirements

- Operational Requirements

- Functional Requirements

Design requirements have to do with the specification of how a design is to be performed. Documentation and implementation standards, level of design detail, design flexibility, degree of modularity, and special features to allow for system testing and performance measurement are but a few typical design requirements.

Performance requirements specify how well a system is to perform. This specification is normally accomplished by the definition of a set of parameters that can be measured or evaluated through system operation. The specification outlines acceptable values for these parameters to aid in design and system performance evaluation. Timing characteristics, accuracy, reliability and capacity are examples of performance requirements.

Operational requirements specify aspects of the system peculiar to its operation under the various constraints and conditions imposed upon it. For example, environmental conditions such as temperature, humidity, pressure and foreign particle population counts constitute operational constraints that influence design. Another important class of operational requirements has to do with man-machine interactions and associated responses.

Finally, functional requirements specify operations to be performed, the inputs and resources to be used, and the associated outputs. Functional requirements are often extracted from not only the nature of the process involved but also from the previously mentioned requirements as influencing factors. Functional requirements are determined not only by the hardware architecture, but also explicitly and implicitly by applications programs. For example, the presence of a CRT display in the system indicates that the executive system must provide program modules to support these devices; complex display application programs may require a display file management program module in the executive.

A particular functional requirement may be satisfied in a design by any one of several logically different design procedures. These procedures may vary in execution time, core requirements, reentrancy requirements, or other attributes. Functional requirements and performance requirements are related by the fact that performance requirements may force selection of a particular technique from among the several possible techniques available. For example, in the calculation of spacecraft attitude, accuracy requirements may dictate that sampling and calculation routines must be entered every 100 ms rather than every 500 ms. If a particular task scheduling or dispatching technique does not permit execution of a program module at intervals of 100 ms or less, then it is eliminated from consideration. Failure mode requirements (FO/FO/FS) may require that multilevel interrupt techniques be employed rather than a single level priority interrupt scheme.

The report deals with performance and functional requirements for executive systems for both the shuttle and station separately. Because of the asynchronous phasing of these two NASA programs, the level of detail is not comparable for the two vehicles. A single set of design requirements was developed in a separate section to apply to both systems because of the dual applicability.

The development of meaningful performance and operational requirements specifications necessitates an in-depth analysis of all flight system application program and hardware requirements. Although this is clearly beyond the scope of the report, the major reason for lack of description in this area is the general lack of availability of documented results of flight systems analysis.

The major area of interest in the report is the specification of functional requirements. Every effort has been made to outline these requirements with clarity and comprehensiveness. In certain discussions, a tutorial approach was taken because the subject warranted it, while in other discussions, conciseness was the guideline because the concepts were assumed to be well understood.

#### E. Conventions

While every reasonable effort has been made to adhere to a common set of definitions and terminology, time has had a mitigating impact. For this reason, some of the areas of possible difficulty are clarified here in the interest of promoting understanding.

- CPU, ALU, computer and processor are frequently used interchangeably. In most cases, the arithmetic logic and control unit is the hardware device being discussed, but frequently, the combined (synergistic) arithmetic logic and control unit and main (macroprogram and data) memory complex is the functional entity of interest. In all cases, context should clarify the actual meaning.

- Bulk store, mass storage, mass memory, and auxiliary storage are interchanged promiscuously. Again, context should clarify the actual storage of interest.

|  |  |  | -[ |

|--|--|--|----|

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  |    |

|  |  |  | 0  |

#### SECTION II. REUSABLE SHUTTLE

#### A. General

This section of the report discusses the reusable shuttle by considering a hypothetical vehicle consisting of a composite of the booster and orbiter. The discussion is divided into three parts as follows:

- Integrated Avionics System Description,

- Executive System Functional Requirements, and

- Executive System Performance Requirements.

The first of these parts represents a comprehensive organizational delineation of the major hardware elements related to computing within the avionics system complex. Particular attention is given to reviewing the major avionics functions and discussing hardware specifics insofar as they are defined at this evolutionary stage. Major emphasis is placed on those elements relating to the computer complexes and their associated closely-related devices and peripherals. Particular attention is also directed to the bus structure and its related control and data transfer concepts. Due to the scope of the study, no details regarding non-computing subsystems are given.

The second part, based heavily on the hardware, concerns itself with the determination and description of functional requirements for a set of executive routines, or real-time monitors, for the various computer complexes within the shuttle avionics system.

The final part of the section deals with performance requirements for the executives. Ideally, the following methodology would be invoked to determine performance requirements. First, all application (problem- or mission-oriented) tasks would be modeled by analysis and simulator design to determine cumulative distribution functions for each of the following task attributes:

- Time interval allowed for task execution,

- Memory space,

- Number of normalized operations per execution,

- Number of input and output requests per execution, and

- Buffer size for input and output requests; next,

a typical mission profile would be developed to show when, on a relative time scale, each task would be activated for execution; this profile would then serve as the basis for a system load model that is used to envelope the following system load attributes:

- Memory space as a function of time,

- Number of operations per unit of time,

- Number of input and output requests per unit of time, and

- Data transfer volume per unit of time.

Certainly other task and system load attributes could be the object of determination, but these are sufficient to show the method.

The required number of operations per unit time is a function of the timeline task execution frequency, the time intervals allowed for task execution, and the number of operations per task execution. Task execution rate is the number of required operations divided by the allowed time interval. This rate must be maintained throughout the allowed time interval. Given the timeline scale showing when each task is activated, we can superimpose overlapping intervals additively to obtain required execution rate as a function of time. If we assume that this rate is absorbed mostly by accessing main memory (the validity of this assumption depends on how task operations are "normalized"), then we have developed a measure of required main memory access rate as a function of time. The volume of input/output distributed over the allowed execution time gives the other component of main memory access rate which, when combined with operation rate, gives a composite measure of required main memory speed.

This speed represents an "effective" speed which can be obtained in many ways such as by using one very large and fast processor/memory system, or by using several slower devices in parallel. Associated with each choice, of course, is a set of required executive routines for support. The cost and complexity of these routines must be merged into the overall trade analysis to determine an optimal configuration satisfying the mission timeline task requirements.

The trade analysis will result in specification of performance requirements for executive routines. These requirements might include:

- Maximum time to activate a task,

- Maximum time to initiate an I/O request,

- Maximum main memory used by the executive, etc.

The point of this discussion is now clear. A significant deficiency exists with regard to performance requirements for the shuttle executives. The reason for this is that comprehensive performance requirements are derived, as shown above, almost exclusively from application program performance requirement specifications, and these are not specified in sufficient detail at this time. Functional requirements, on the other hand, are based primarily on the hardware architecture and application program functions. Although considerably more definitive detail is required in these areas, a priori knowledge was applicable due to the nature of the mission functions and the applicability of past experience with related and/or similar systems.

#### B. Integrated Avionics System Functions

- 1. General. This section outlines the Integrated Avionics System for the reusable space shuttle. Specific mission oriented functions required to be performed by the complete system are described. Characteristics of the avionics hardware conceptual configuration described in various documents and presentation notes that directly impact upon the executive system requirements are delineated. Major emphasis is directed to the Arithmetic Logic Units (ALU's), storage, and data bus subsystems since they have the greatest influence on the executive design. Other aspects of the system are not considered in detail for this report.

- 2. Avionic System Functions. The space shuttle will utilize an on-board computerized integrated avionics system to provide information processing and system control required for autonomous vehicle operation. It will relieve the crew of excessive workload by automatically performing time critical functions and providing priority sorting and data compression of that information needed by the crew.

The general avionic functions to be performed are:

- a. Engine control jet and rocket.

- b. Communication to ground and space station.

- c. Attitude reference.

- d. Flight control aerodynamic and reaction jets manual and automatic.

- e. Navigation in orbit and atmosphere.

- f. Guidance during boost, orbital burns, entry and landing.

- g. Displays for pilot and copilot.

- h. Power control and conditioning.

- i. Control, checkout and status monitoring of vehicle subsystems.

- Environmental Control and Life Support (ECLS)

- Hydraulics

- Landing Gear

- Lights

- Hatches and Doors

- Electrical Power

- Propellant

- Separation

- Payload

- j. Flight recording: maintenance and emergency.

- k. Information management.

- 1. Software for on-board checkout, ground checkout, mission planning.

- m. TV cameras, alignment, closed circuit.

- 3. Avionics System Hardware Description. The space shuttle Integrated Avionics System baseline is shown in Figure II-B-1(1). References, shown in parentheses, are given at the end of each section. The Integrated Avionics System (IAS) is comprised of a central computer for centralized data management and several dedicated processors for special hi-iteration calculations. All other subsystems requiring IAS attention in the form of data communication, or command and control are interfaced through a network of multiplexed data buses. Data bus-to-device interface is accomplished through a standardized digital interface unit (DIU). This unit is to be designed with general purpose flexibility sufficient to allow direct computer communication with any external subsystem while requiring only minimal special interface circuitry design.

The major functional elements of the complete Integrated Avionics System and corresponding subsystems are shown in detail in Figure II-B-2(2). Quantity numbers are assigned to processing units and digital interface units (DIU's) reflecting the redundancy required for meeting failure mode criteria (i.e., fail operational, fail operational, fail safe).

a. Computers. The IAS system computers provide computational capability required by all other subsystems during all phases of the space shuttle mission. The majority of these computations are presently planned to

FIGURE II-B-2

be performed in the central computer complex. However, dedicated special purpose computational devices are utilized to satisfy unique computational requirements. Specific characteristics of each of these computer complexes are as follows:

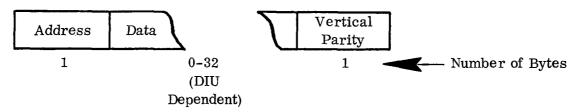

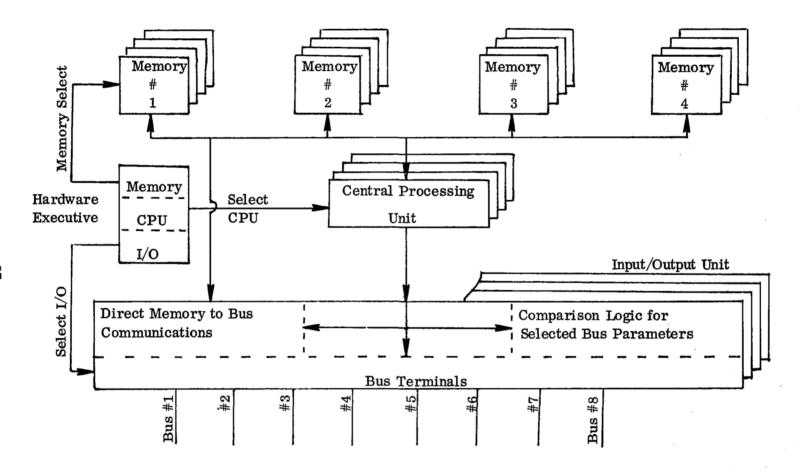

(1) Central computer (CC). A functional diagram of the Central Computer is shown in Figure II-B-3(1). The unit is comprised of an Arithmetic Logic Unit (ALU), 4-16K memory modules and an input/output (I/O) control unit. Data paths exist between each of the memory modules, the ALU and the I/O control unit. Eight buses are connected to the I/O control unit. Logic capability is available for direct memory to bus transfers or cycle stealing memory transfers.

The following Central Computer characteristics are defined:

| • | Number of computers (max.)   | 4    |

|---|------------------------------|------|

| • | Memory Size (max. words)     | 256K |

| • | Memory Modules (max.)        | 16.  |

| • | Word Length (bits)           | 32   |

| • | Half Word Length (bits)      | 16   |

| • | Add Time (microseconds)      | 2    |

| • | Multiply Time (microseconds) | 10   |

The central processor is projected to have an instruction set consisting of 100 instructions with eight general purpose registers. Direct addressing will be available to the 64K words of main memory. Each memory module will be powered and switched as  $16K \times 34$  bit modules. Two bits will be utilized for parity.

will be interfaced with the I/O bus through one of 16 slightly different variations of digital interface units. In most cases these units will consist of a line terminal only. However, in a few specific cases a more sophisticated approach is required. A 16-bit parallel processor with approximately 2.5K of memory is envisioned in addition to the line terminal. Basic building blocks for storage are 512 word blocks of MOS R/W and MOS R/O memory. Other characteristics of the Processor include add times in the 2 microsecond range; local memory is partitioned with approximately 25% having read/write capability and 75% with

BASELINE COMPUTER FUNCTIONAL DIAGRAM

FIGURE II-B-3

read only. Twelve to sixteen units of this type are envisioned.

A typical block diagram of this type of DIU is shown in Figure II-B-4(2).

(3) Main engine processor. Main engine or rocket engine control will be effected through the main engine processors. Each of these engines is currently envisioned to require the following computers with the indicated characteristics:

| • | Number of Computers        | 4  |

|---|----------------------------|----|

| • | Memory sizes, each (words) | 6K |

| • | Word Length (bits)         | 16 |

| • | Add Time (microseconds)    | 2  |

(4) Jet engine processor. Jet engine control will be effected through the jet engine processors. Each of these engines is currently envisioned to require the following computers with the indicated characteristics:

| • | Number of Computers       | 4    |

|---|---------------------------|------|

| • | Memory Size, each (words) | 1.3K |

| • | Word Length (bits)        | 16   |

| • | Add Time (microseconds)   | 2    |

(5) Display processor. Display of information is effected through the use of multimode cathode ray tube (CRT) devices. These programmable devices allow the display of only that data pertinent to the current mission phase; all other data is relegated to the status monitor or cautional warning classification.

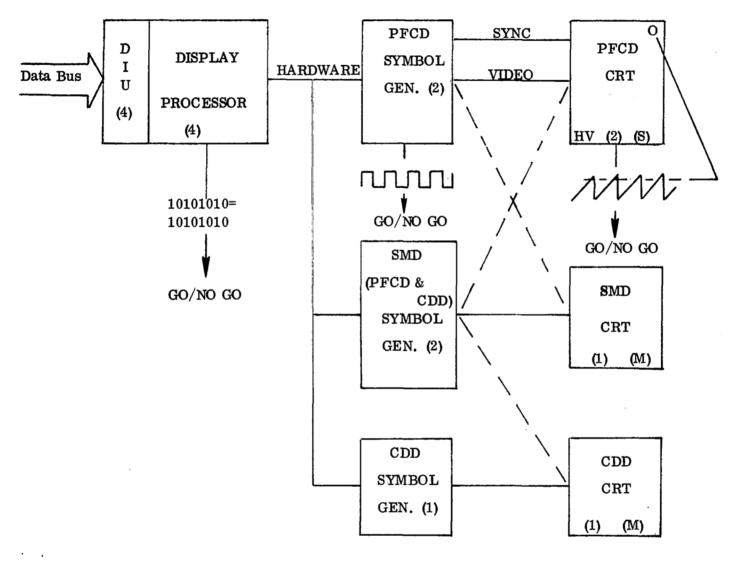

Each of the five CRT displays are driven by a symbol generator. The display processor is interfaced through a bus network to each symbol generator for display driving. Display driving is also possible from the central computer via the bus network to the symbol generator. Figure II-B-5(1) shows the complete control and display baseline schematic.

Characteristics of the display processor's are as follows:

# INERTIAL MEASUREMENT UNIT DIU

FIGURE II-B-5

| • | Number of Computers       | 4  |

|---|---------------------------|----|

| • | Memory Size, each (words) | 6K |

| • | Word Length (bits)        | 32 |

| • | Add Time (microseconds)   | 2  |

Memory is utilized to refresh the CRT's at a rate of 50-60 Hz to prevent flicker. Source data update occurs at a low 1 Hz rate.

b. Bus structure. Space shuttle intercommunication is to be effected utilizing individual hard wires as the transmission medium between black boxes and from subsystem to subsystem. The signal transmission technique chosen is the multiplexed data bus.

The system employs serial digital time division multiplexing (TDM) and is computer controlled using a request/reply data flow control technique. Bi-phase (Manchester) digital coding and alternating current coupling methods are employed. The system timing reference (clock) required for synchronization is transmitted over a separate bus.

Bus-to-subsystem interface is effected through standard Digital Interface Units (DIU's). An example of the interconnection technique and the interconnection redundancy is shown in Figure II-B-6(2). Four buses are run aft for interconnection to all subsystems in this area. An additional four buses are run forward (i.e., toward the cockpit) for interconnection with subsystems located there. Eight bus positions are available on each I/O controller for bus interconnection to the central computer.

Although computer-to-subsystem intercommunication is achieved via a bus network, each of the dedicated processors are afforded an intercomputer channel for additional communication. This capability is provided to enable simultaneous computer-to-computer communications while the bus network is in use for another function. The layout of the communication links is shown in Figure II-B-7(1).

Figure II-B-8(1) outlines the expected data transmission distribution over the orbiter aft bus. Message length in 8-bit bytes is plotted as a function of both number of transmissions per second and number of bytes transmitted per second.

A total traffic estimate for Aft Data Bus No. 1 by MDC/TRW has been placed at approximately 1.08 KB/sec. The possible operational capability range of the complete bus system is 100 KBS-5MBPS.

# SIMPLIFIED DATA BUS

### DEDICATED SPECIAL COMPUTER CONFIGURATION

FIGURE II-B-7

# DATA TRANSMISSION DISTRIBUTION FOR THE ORBITER AFT BUS

MESSAGE LENGTH IN 8-BIT BYTES

FIGURE II-B-8

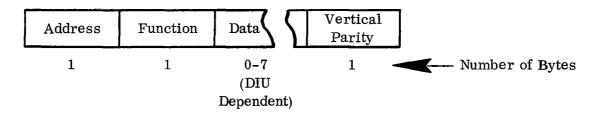

The data bus message structure is displayed in Figure II-B-9(1). Although the bus transmission structure is not specifically identified, it is assumed from the vertical parity byte provision that the transmission is parallel by bit up to one byte and then serial by byte.

Bytes are comprised of 8 bits plus one bit for horizontal parity. Data message length varies depending upon the specific DIU in use.

Computer memory requirements for data bus control are as follows:

|                 | Memory Requirements |  |

|-----------------|---------------------|--|

| <u>Function</u> | (Words)             |  |

|                 |                     |  |

| Bus Scheduling  | 500                 |  |

Control selection of appropriate I/O program for data bus.

Modify programs as required to accommodate changing requirements and reconfiguration.

Initiate IOCU action.

#### I/O Drivers

| Command List - List of Data Bus Commands | 1000                |

|------------------------------------------|---------------------|

| IOCU Programs - Bus Control Programs     | $\frac{1000}{2500}$ |

- c. System reconfiguration. Avionics system reconfiguration to meet the failure mode criteria as currently envisioned will be effected through two distinct techniques.

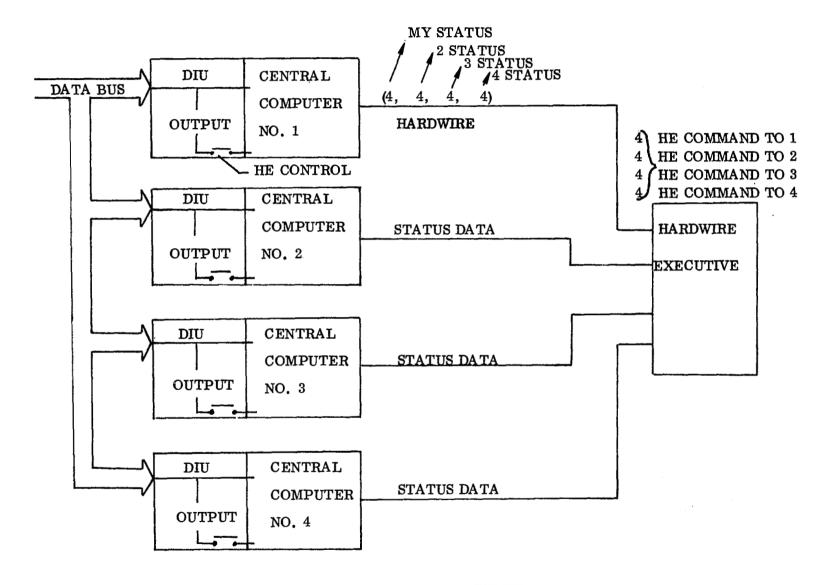

- (1) Central computer. The first is for protection of the central computer in event of an LRU failure. LRU's are identified to be the central processing unit, a 16K memory bank, and an I/O control unit. Each of these is quadruply redundant with module selection as a function of the system executive, envisioned to be "hardware" executive in this case. This is depicted schematically in Figure II-B-10(1).

- (2) Subsystem reconfiguration. Reconfiguration in the event of failures in the remaining subsystems is effected as a software function

#### FROM CENTRAL COMPUTER TO DIU'S:

Overhead: 3 Bytes

#### TO CENTRAL COMPUTER FROM DIU'S:

Overhead: 2 Bytes

Address: Identification of DIU

Function: Data Assignment or Request Data: Information to be Communicated Vertical Parity: Burst Error Detection

# DATA BUS MESSAGE FORMATS FIGURE II-B-9

RECONFIGURABLE COMPUTER FUNCTIONAL DIAGRAM

of the central computer. At this point in time it is not certain as to whether this is an application or system program function. Figure II-B-11(1) shows functionally how subsystem reconfiguration will be effected.

Figures II-B-12(1) through II-B-16(1) show checkout functions at various levels and for various subsystems. The significance of the central computer is shown in each case. Pilot/copilot activated reconfiguration capability exists for the central computer. This includes override capability for the executive.

POWER AND MODE RECONFIGURATION OF SUBSYSTEMS

FIGURE II-B-11

CHECKOUT FUNCTIONS

FIGURE II-B-12

DISPLAY CHECKOUT FIGURE II-B-13

IMU CHECKOUT FIGURE II-B-14

CENTRAL COMPUTER CHECKOUT FIGURE II-B-15

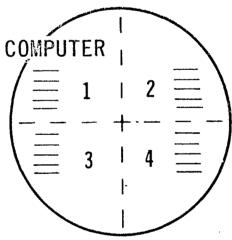

### COMPUTER SELF-TEST FAIL

DIAGNOSTIC CRT

## COMPUTER IN-COMMAND (SWITCH)

- 1. ALL FOUR COMPUTERS OPERATE AT CRITICAL TIMES. ONE IS IN CONTROL.

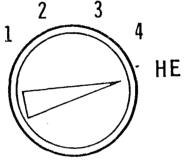

- 2. HARDWARE EXECUTIVE (HE) NORMALLY CONTROLS SWITCHING.

- 3. CREW CAN DISENGAGE HE AND SELECT ANY COMPUTER MANUALLY.

- 4. SELF-TEST LIGHTS AND COMPUTER DIAGNOSTICS ASSIST CREW IN COMPUTER EVALUATION.

- 5. COMPUTERS MONITOR HE ACTION TO INSURE SAFE CONDITION.

COMPUTER SWITCHING

#### C. Executive System Functional Requirements

- 1. <u>General</u>. Space shuttle Executive System Functional Requirements are derived from several sources:

- Mission requirements analysis,

- Hardware architecture analysis,

- Applications requirements analysis, and

- Combinations of the above.

Mission reliability requirements have significant effect on the monitor system complexity both explicitly and implicitly through hardware redundancy. In fact, this requirement implies multilevel program priority interrupt capabilities. Hardware affects monitor system requirements directly in that support must be provided for each peripheral device present in a computer subsystem. Subsystem complexity will be an indication of the number of possible concurrent activities. The relative importance of these activities with their response time performance requirements will determine the necessity for priority scheduling. This is an example of the interaction between Performance Requirements and Functional Requirements.

Monitor system functional requirements resulting from consideration of applications support requirements are as follows:

- The applications programmer will not have access to the complete instruction repertoire. The system will operate in a privileged mode. Capability must be provided to perform those needed functions which cannot be accomplished by applications due to this restriction;

- To ensure correct scheduling, the monitor must handle all requests for peripheral device usage;

- The monitor system can provide a virtual machine with programming conveniences that reduce applications development effort; and

• The monitor system can provide powerful tools for execution of applications programs by implementing supervisor calls such as TURN ON, DELAY, etc. The applications interface is provided by the Request Processor Module which processes all supervisor calls. Relatively few of the monitor system Functional Requirements are affected by the applications programs, per se. It is the interaction between the application programs primarily that gives rise to the Functional Requirements.

The Functional Requirements are grouped by computer subsystem. Requirements which are common to all subsystems are fulfilled by the Central Computer Complex.

- 2. <u>Central Computer Complex (CCC) Monitor</u>. The monitor subsystem for the Central Computer Complex must support the following mission functions (3):

- Guidance,

- On-Board Mission Planning,

- Configuration and Sequencing Control,

- Energy Management,

- On-Board Checkout,

- Display Executive Control, and

- Data Base Executive Control.

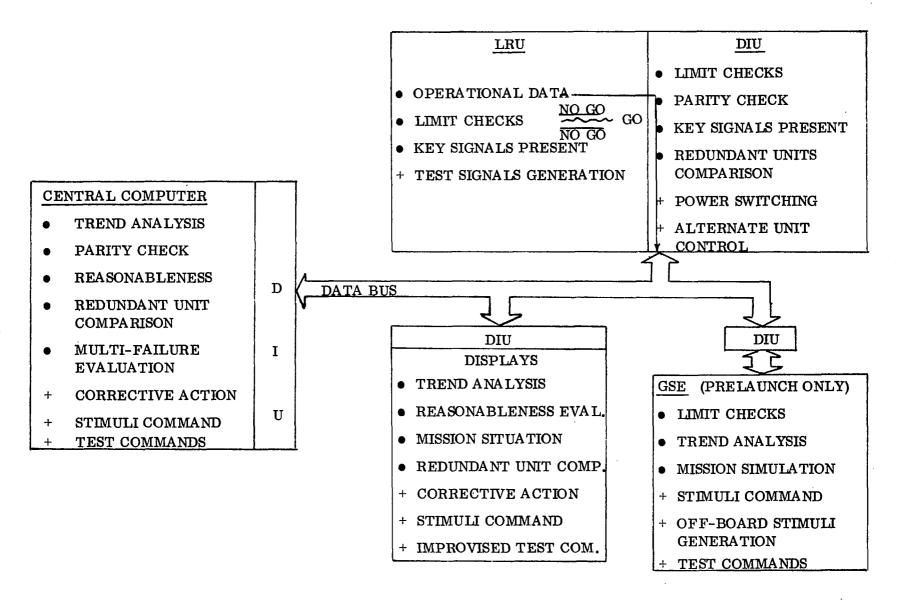

In order to accomplish this support, the CCC monitor will handle error detection, analysis, alarm, isolation, and recovery for other computer subsystems. For the recovery function, the monitor will maintain tables of reconfigurable subsystems. Upon detection of hard failures, the monitor will accomplish a preplanned reconfiguration to ensure mission integrity.

In addition, the monitor will accept data and task scheduling information from the Uplink Modem and other computer subsystems. It will also transmit data and task schedules to other computer subsystems. The monitor will interface with supervisors of the other computer subsystems in order to provide these task scheduling and data transfer functions.

- a. Capabilities. Thorough search of the available space shuttle documentation has indicated that the computer system executive requirements may have many similarities to existing computer applications. Process control applications, for instance, have the following requirements:

- Analog input/output.

- Digital input/output.

- Scientific calculations.

- Computer actuated displays.

- Error logging.

- Initialization.

Message switching applications have the following requirements:

- Message transmit initiation.

- Buffer manipulation.

- Message error detection.

- Error recovery procedures.

- Message-receive initiation/continuation.

- Error logging.

- Initialization.

Real-Time Terminal System applications must satisfy the following requirements:

- Time-slice partitioning.

- Error logging.

- Buffer manipulation.

- Message initiation.

- Error recovery procedures.

- Initialization.

All of the above requirements are present explicitly or implicitly in the space shuttle application. The above systems are characterized by stringent response time requirements, many concurrent activities, varying importance of activities, relatively slow speed peripheral devices, and a high degree of interaction of activities. These same characteristics are evidenced by the space shuttle.

Experience has shown that the following capabilities are necessary in order to satisfy requirements with the above characteristics:

- Priority interrupt structure.

- Priority level independent of priority hardware structure.

- Capability to selectively inhibit interrupts.

- All communication with I/O devices will take place via the supervisor.

- Privileged mode of operation (i.e., privileged instruction repertoire).

- Memory protect facilities for task and data protection, and

- Variable program priority level (dynamically variable in real-time under application, executive, or event occurrence control).

- b. Assumptions. The following functional requirements will be assumed for the computer architecture, which will significantly affect monitor requirements.

- (1) Portions of the monitor will reside in the main store. Parts of the monitor will possibly reside in bulk and be called into the main store as required. Performance requirements might ordinarily prohibit the delays associated with loading large portions of the monitor as needed. However, systems exist that would likely permit this form of memory hierarchy for executive residence. For example, this concept would be feasible with the IBM

System 360 Models 85 and 195. These computers use a cache execution memory with a large bulk or extended main store. The gross features are:

- Memory reference to an instruction located in cache memory brings in that instruction plus the next seven instructions for execution.

- Memory reference to an instruction not in cache memory brings that instruction, plus the next seven instructions from bulk to cache memory for execution and also loads blocks of instructions into cache memory. Since program instructions tend to cluster, many subsequent memory references will be directed to the relatively fast cache memory. Instructions are fetched in groups, reducing the number of memory references required. Experience has shown that this combination operates at about 80% of the rate that a computer with all cache memory would reach.

- (2) The functional relationship between elements of the Executive Control Routines and other elements of the software system is shown in Figure II-C-1.

- (3) The monitor system will consist of a kernel with ancillary program modules.

- c. Executive control routines (ECR). The ECR group of modules is associated with the functional requirements for resolving priority, resource allocation, and program execution conflicts. The following program modules will comprise the executive control routines portion of the CCC monitor:

- (1) Task Scheduler will have responsibility for appending requests for program module execution on the proper priority thread.

- (2) CPU Allocator will maintain records of available CPU's and upon request will perform necessary functions to associate an available CPU with an active program module. Upon release, the CPU will be returned to the available pool.

- (3) Main Store Allocator (MSA) examines indexed tables to isolate main store space needed by requesting program modules.

#### FULL OPERATING SYSTEM

Linking Loader Module Update Source Languages Utility Programs Simulators

#### BASIC MONITOR

Error Analysis/Recovery

Reconfiguration

Central Alarm Package

Uplink Modem Package

I/O Package

KB, Switch Panel

ELD, Maintenance Recording

Mass Store

Data Bus - FWD

Data Bus - AFT

Computer - Computer data link

Message Transmit

Message Receive

Message Queue Handler

Abort Routines

Initialization

#### KERNEL EXECUTIVE CONTROL ROUTINES

Interrupt Handler

Task Scheduler

Task Executor

Resource Allocator

Request Processor

Computer Hardware I

Computer Hardware Diagnostics

Tables

Watch-Dog Timers

FIGURE II.C.1. Relationship of Kernel to the Remainder of the System

If scratch or high speed store is used, then the MSA will determine demand for high speed store also. Given sufficient available storage, the MSA associates storage with program module and performs the necessary associated accounting.

Upon storage release, the MSA will return storage to the available pool. It is possible that periodic 'garbage collecting' may be necessary to provide sufficient areas of contiguous storage. This may imply necessity for dynamic relocation of active program modules.

- (4) Task executor (dispatcher). Functional Requirements are the following:

- Determine highest priority module requesting execution.

- Cause resource allocation to be effected.

- Perform initialization of module.

- Cause execution of program module.

- (5) Task terminator/suspender. This module must satisfy the following functional requirements:

- Remove program module in question from active priority thread.

- Perform necessary housekeeping operations to maintain thread integrity.

- For task suspension, an appropriate lock (state variable) must be set to ensure that module is not executed. The module, however, is not removed from priority thread. Then, when the lock is removed, the task can be executed.

- (6) Request processor. Functional requirements will be:

- Request analysis.

- Parameter passing, possibly by micro-code.

- Passing control to proper request program module based on logic of request analysis.

- (7) Main store protect/unprotect. This module must satisfy the following functional requirements:

- (a) Perform required hardware manipulations to cause read/write prohibition, if required. Such actions could be the following:

- Test key index data for validity.

- Execute computer instructions to effect inhibition.

- Perform error analysis on key index data.

- (b) Similar actions must be taken to remove prohibition.

- (c) It is possible that status must be updated so as to maintain records of available unprotected storage.

- (d) These functional requirements are generally satisfied by coordinating implementation with the resource allocation modules.

- (8) Interrupt handler. This module should accomplish the following Functional Requirements:

- Save required registers and storage contents for interrupted program. This may be done by micro-code.

- Analyze status registers for source of error interrupts. Invoke required error processing modules.

- Analyze status registers for source of abort interrupt. Invoke suitable abort procedure modules.

- Enable or disable preplanned interrupts.

- Determine interrupt priority and make monitor call to task executor at that priority level.

- When all interrupt requests have been serviced, notify task executor (dispatcher).

- (9) Abort procedures TBD.

- (10) Real-time clock/interval timer. These modules must satisfy functional requirements to accomplish functions associated with various software clocks that the monitor and (possibly) application programs use. Some of the clocks are the following:

- Diagnostic countdown(s).

- Program module execution(s).

- Program module delay(s).

- Interval timer(s).

- System performance measurements.

- (11) Time slice partitioning. Module must meet the following functional requirements:

- Maintain records of elapsed time since initialization of program module.

- Compare elapsed time with requested time.

- Cause elapsed time to approximate requested elapsed time/time period.

- (12) System performance measurement. These modules must satisfy the following functional requirements with respect to hardware and software:

- (a) Hardware.

- Error fault detection.

- Passive instruction examination.

- Other software triggers.

- (b) Software.

- System auditing.

- Event tracing.

- Performance recording and analysis.

These considerations are discussed in detail in Campbell and Heffner (4).

(13) Initialization routines. System initialization routines comprise the collection of programs necessary to meet Functional Requirements to bring the hardware/programming system on-line from a cold start. A cold start implies that no programs are running in the complex and, therefore, all bootstrapping must be done by the initialization programs.

Once system initialization has been performed, other application oriented initialization may be necessary. The act of loading or changing the operating system programs will be considered initialization. "Changing" is included in the definition because the monitor system required for pre-launch checkout and post-flight analysis may be considerably different from the system required to support flight. The following initialization programs will be required:

- System initializer (not part of this study).

- Pre-launch checkout initializer (not part of this study).

- Flight system initializer.

- Post-flight system initializer (not part of this study).

- Possible initialization routines to operate as a function of mission phase.

- d. Time line controller/interpreter (TLC). This module will satisfy functional requirements to act as the system manipulator for mission profile related requirements. The monitor system must support manipulation of space shuttle tasks based on the following factors:

- (1) Elapsed time.

- (2) Time difference from reference time.

- (3) Occurrence of arbitrary events.

- Events must be detected.

- Appropriate program modules must be notified of occurrence of specified events.

- Appropriate tasks must be scheduled to accomplish reaction to event occurrence.

- e. Central alarm package. This group of programs handles the tasks germane to satisfying functional requirements for recording errors within the computer system, logging on output media, displaying and maintaining a history, and other alarming requirements. The programs will format downlink output, output to the printer, and output to the Error Logging Device (ELD). The modules will maintain a history of alarms active within the system and output this history on demand to the specified output devices. The following program packages (modules) will be required:

- Alarm history maintenance,

- Alarm output,

- Alarm analysis, and

- History output.

- f. Input/output package (IOP). This collection of subroutines will satisfy message I/O functional requirements for the following devices: printer, ELD, keyboard inputs. Output messages will be formatted by the user routines.

The IOP will operate in conjunction with the device handler for the specific device. Since the IOP will place the message in an output buffer, the calling program may be rolled-back after the call is made without destroying the message. All output, correct returns, etc., become the responsibility of the IOP. Once the buffer has been loaded, the device handler will have the responsibility for outputting the message.

For keyboard input, the IOP performs error checking on words and message, and handles output error notifications, internal message formatting, analysis of message contents for action or data, and transmission of action requests. The following program modules will be required:

- (1) I/O request processor.

- (2) I/O initiator(s).

- (3) I/O continuator(s).

- I/O error analysis.

- Input message format.

- Input message error notice output.

- Input message decoding/analysis for action or data.

- Input message transmit action requests.

g. Device handlers. Device handlers are collections of program modules concerned with the functional requirements for manipulation of external devices that are usually interrupt driven. The modules are divided into initiator-continuator pairs. The initiator has the responsibility for analysis of the calling sequence, proper response (i.e., setting buffer lengths, etc.), and transmission/receipt of the first character or block. The continuator is an interrupt driven program responsible for send/receipt of character or that part of a message sent/received during an interrupt cycle, error analysis on character, if required, determination of termination conditions, proper return from termination (either normal or error), and housekeeping associated with termination.

Usually, a continuator will require either a predetermined number of characters or an EOM character. The transmission/receipt of characters will continue until one of these conditions is met or until an error is encountered.

Upon meeting termination conditions, the continuator will perform a longitudinal record check for errors. Response to error conditions may differ with the individual continuator.

Initiator/continuator pairs should be provided for the following devices:

- Keyboards.

- Uplink modem.

- Data buses and intercomputer data link.

- Error logging device (ELD).

- Health monitoring system.

- Printer.

- LRU checkout bus.

- Mass storage devices.

- Displays.

- Downlink modem.

- h. Error detection, analysis and recovery. Error routines will be concerned with functional requirements for the detection of malfunctions in the internal computer hardware and in peripheral devices attached to the computer, exclusive of the BIT panel, and compensation for these malfunctions to meet the system reliability performance requirement.

In order to accomplish error analysis and recovery in a sophisticated hardware/programming system, considerable study is required to determine the most propitious method of meeting the hardware system performance specifications. In nearly all cases, some combination of hardware/software will be required in determining hardware malfunctions, e.g., the interval timer or periodic interrupt-diagnostic countdown. In general, it is assumed that where transmission of data is involved, hardware parity checks of varying sophistication will be required. This is not to be limited to message checking, but is also to be done as a matter of course on transfers to and from storage. Furthermore, after distinguishing hard failures from transient failures, the usual requirement is for substitution of standby equipment for the LRU that has failed. The subsystem monitor will be notified of an error condition by the presence of an error-generated interrupt which will cause the related handler to relinquish control to the appropriate error processing program module.