NATIONAL TECHNICAL INFORMATION SERVICE Springfrold, Va. 22151 Report No. CS-7107-R0216 February 26, 1971

CR-1150B2

Advanced Software Techniques for Space Shuttle Data Management Systems

Final Report

By

Raymond J. Rubey, Wayne A. Ganzel, Michael D. Richter, and Steven A. Vere

$\mathbf{For}$

Manned Spacecraft Center National Aeronautics and Space Administration Contract No. NAS 9-11225

Approved

R. Dean Hartwick, Manager Computation and Software Department

255 w. fifth street, san pedro, california 90731

#### ACKNOWLEDGMENT

This study was carried out in cooperation with personnel from NASA/MSC EB5. The assistance of Irving Burtzlaff and Donald Barron is greatly appreciated.

Distribution of this report is provided in the interest of information exchange and should not be construed as endorsement by NASA of the material presented. Responsibility for the contents resides in the organization that prepared it.

### TABLE OF CONTENTS

| 1. | Introduction                                                                                                                                                                                                                    | 1                                                        |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 2. | Summary2.1Conclusions and Recommendations2.2Functional Analysis2.3Computer Configuration2.4Computer Architecture2.5Programming Languages2.6Verification Tools and Techniques                                                    | 3<br>5<br>7<br>10<br>12<br>13                            |

| 3. | Functional Analysis3. 1Inertial Reference3. 2Navigation Sensors3. 3Displays3. 4Trackers3. 5Landing Aids3. 6Primary Propulsion Subsystems3. 7Reaction Control Subsystem                                                          | 15<br>17<br>20<br>21<br>23<br>25<br>27<br>28             |

| 4. | <ul> <li>Computer Configuration</li></ul>                                                                                                                                                                                       | 31<br>33<br>35<br>39<br>59                               |

| 5. | Computer Architecture5.1Memory5.2Execution Speed5.3Input/Output Facilities5.4Instruction Set5.5Word Format5.6Register Organization5.7Restart and Self-Test Provisions5.8Interrupt-Handling Facilities5.9Summary of Conclusions1 | 63<br>64<br>73<br>77<br>79<br>86<br>89<br>93<br>96<br>00 |

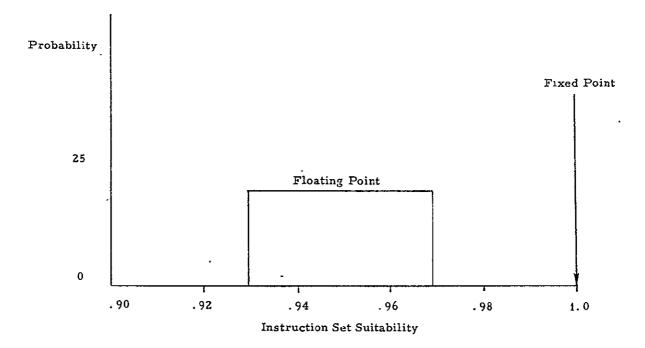

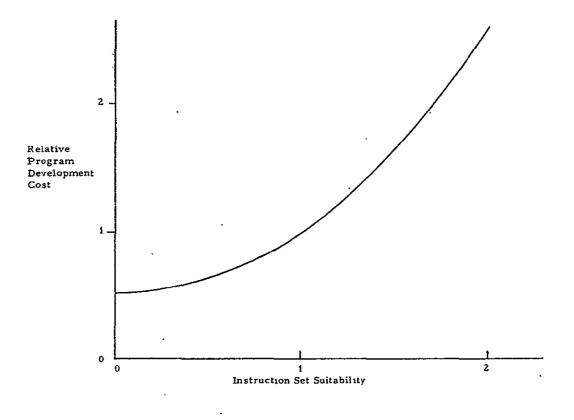

| 6. | Evaluation Methodology                                                                                                                                                                                                          | 03                                                       |

| 7. | 7.1       Language Suitability                                                                                                                                                                                                  | 11<br>12<br>15<br>20<br>24                               |

.

| 8.  | Veri             | fication Tools and Techniques            | 127   |

|-----|------------------|------------------------------------------|-------|

|     | 8.1              | Engineering Simulation                   | · 127 |

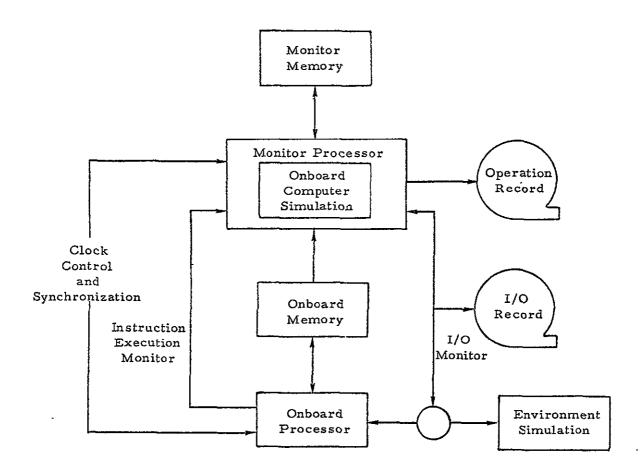

|     | 8.2              | Interpretive Computer Simulation         | 131   |

|     | 8.3              | Hybrid Simulation                        | 139   |

|     | 8.4 <sup>.</sup> | Other Verification Tools                 | 143   |

|     | 8.5              | Master Test Plan                         | 148   |

|     | 8.6              | Summary of Conclusions                   | 155   |

|     |                  | · ., · · ·                               |       |

| App | endix            | A - Task Interaction                     | 157   |

|     |                  |                                          | •     |

| App | endix            | B - A Methodology for Restart Protection | 169   |

| _   |                  | · · · · ·                                |       |

| App | endix            | C - Proving Program Correctness          | 177   |

|     |                  |                                          |       |

|     |                  |                                          | -     |

#### LIST OF FIGURES

.

-

| 1.  | Onboard Software Structure Outline            | 31  |

|-----|-----------------------------------------------|-----|

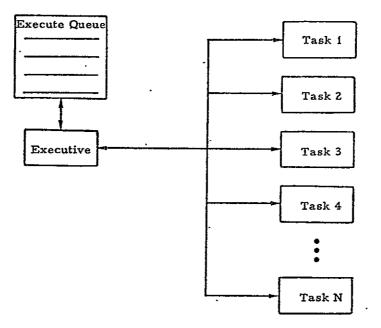

| 2.  | Implied Executive Concept                     | 41  |

| 3.  | Polling Executive Concept                     | 42  |

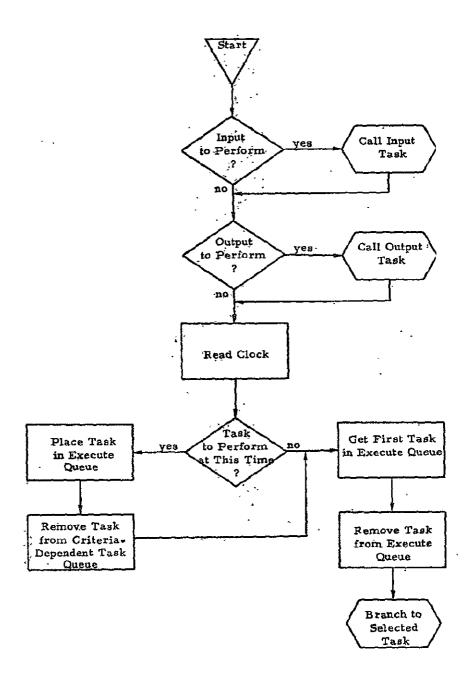

| 4.  | · Polling Executive Design                    | 43  |

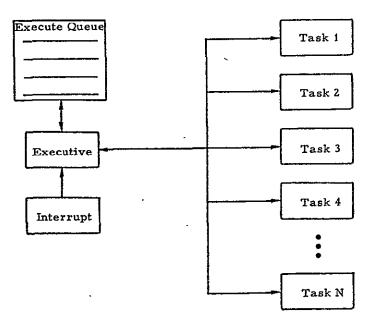

| 5.  | Interrupt Executive Concept                   | 44  |

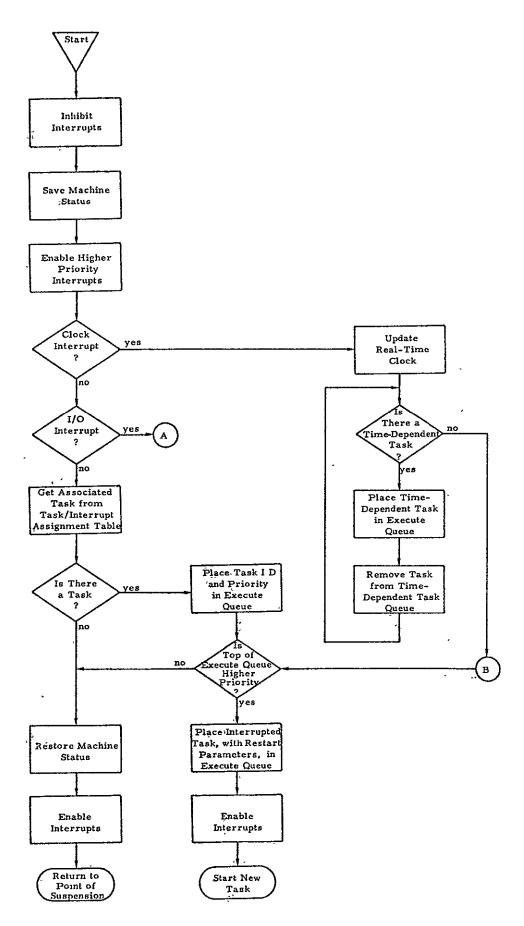

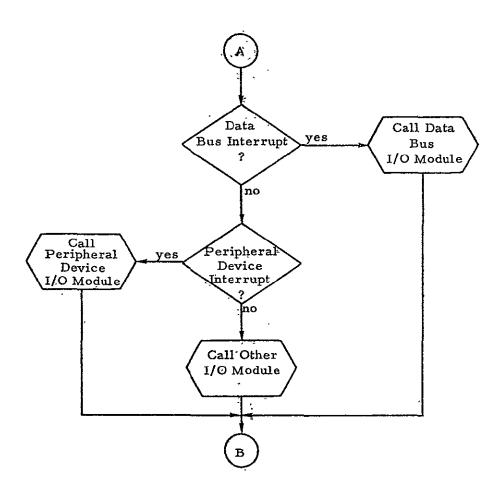

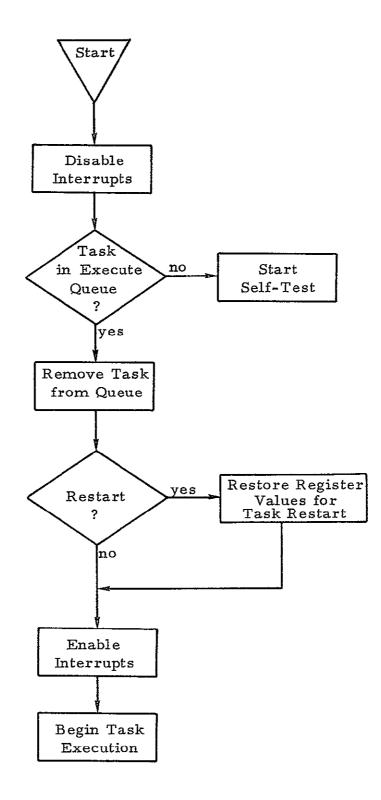

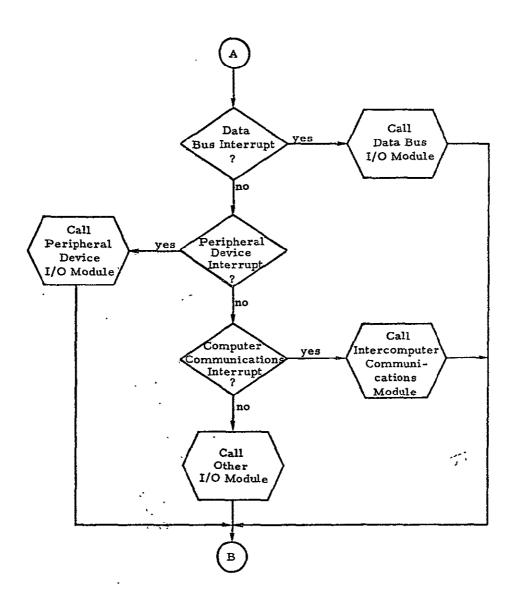

| 6.  | Interrupt Executive Design: Interrupt Module  | 46  |

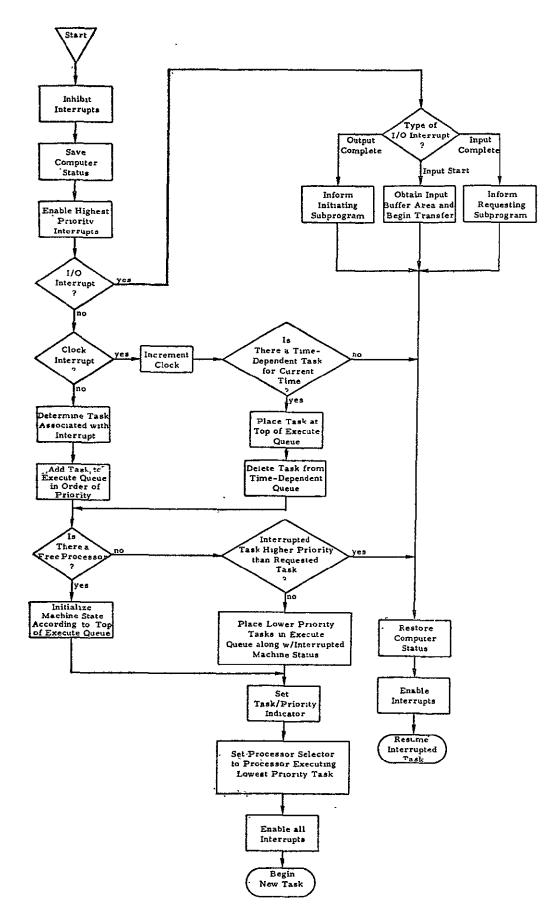

| 7.  | Interrupt Executive Design: Scheduling Module | 49  |

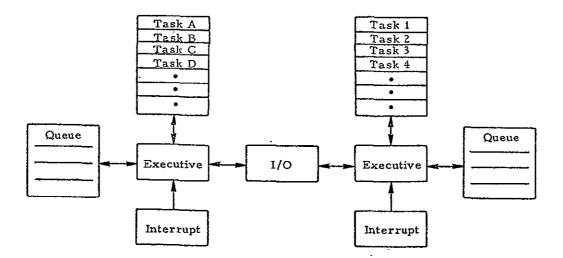

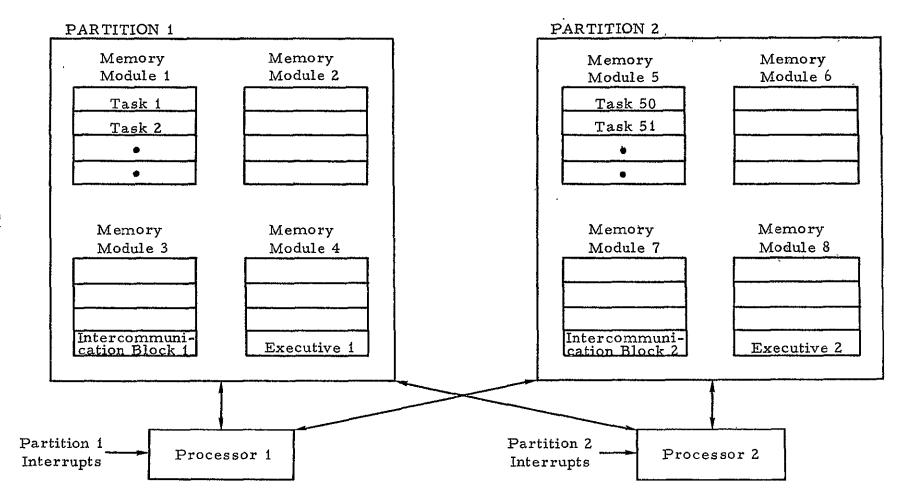

| 8.  | Distributed Executive/Multicomputer Concept   | 51  |

| 9.  | Distributed Executive/Multicomputer Design    | 52  |

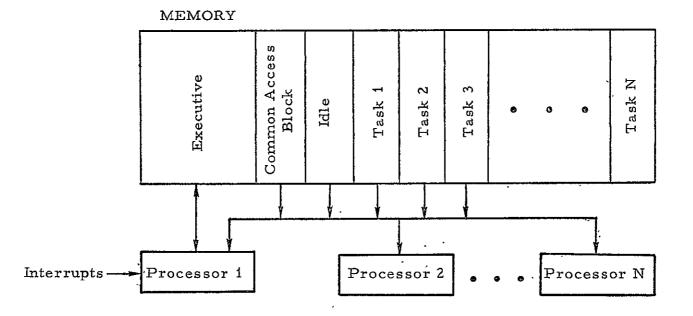

| 10. | Distributed Executive/Multiprocessor Concept  | 54  |

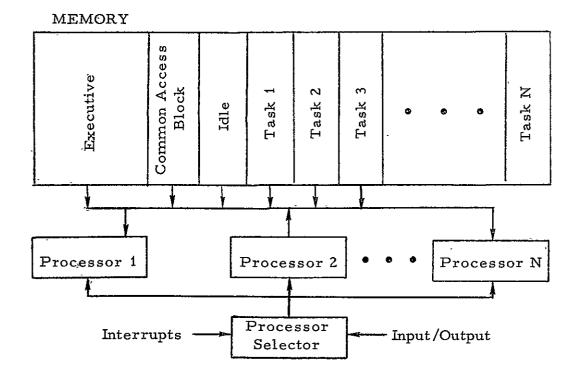

| 11. | Fixed Executive/Multiprocessor Concept        | 55  |

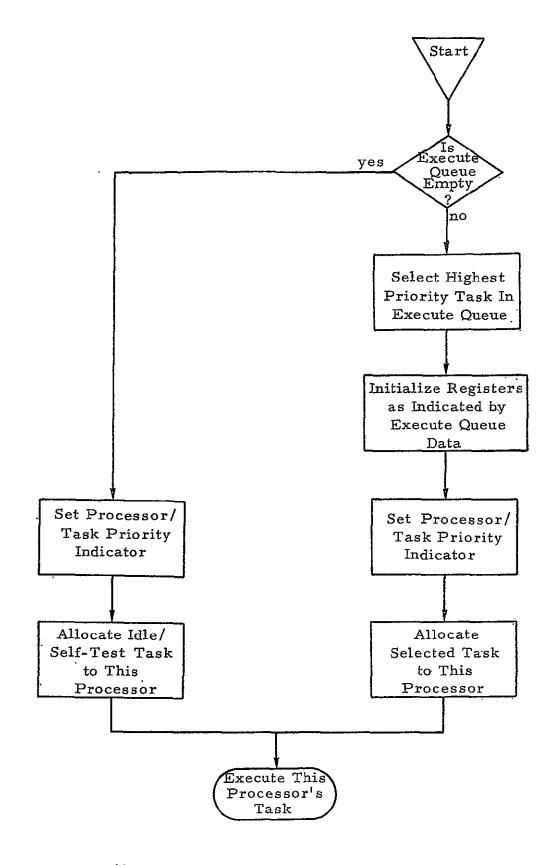

| 12. | Floating Executive /Multiprocessor Concept    | 56  |

| 13. | Floating Executive/Multiprocessor Design:     |     |

|     | Scheduling Module                             | 58  |

| 14. | Floating Executive/Multiprocessor Design:     |     |

|     | Interrupt Module                              | 60  |

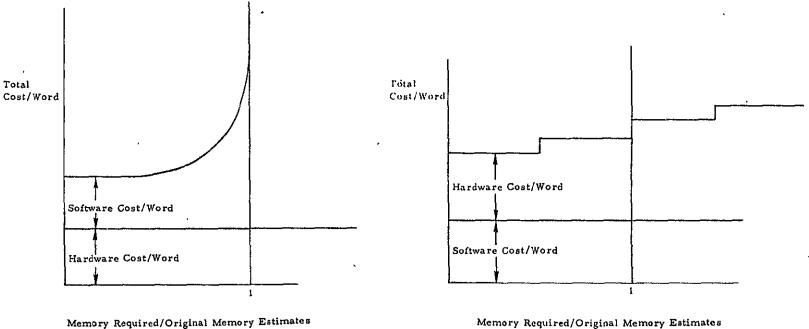

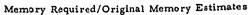

| 15. | Fixed Memory Costs                            | 66  |

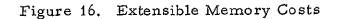

| 16. | Extensible Memory Costs                       | 66  |

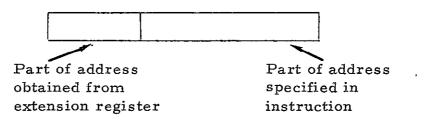

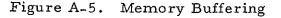

| 17. | Buffering Method of Interaction with I/O      |     |

|     | Controller                                    | 78  |

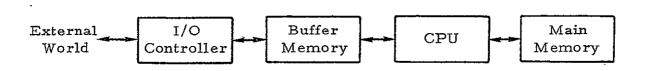

| 18. | Cycle-Stealing Method of Interaction with     |     |

|     | I/O Controller.                               | 78  |

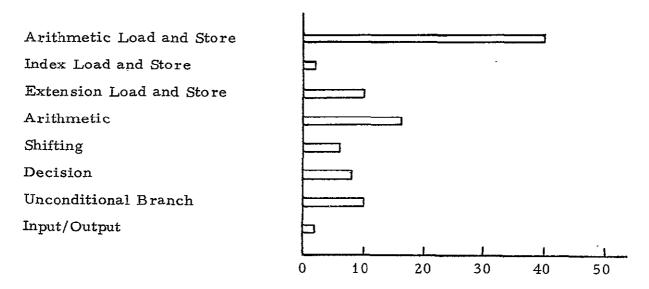

| 19. | Instruction Usage for Guidance, Navigation,   |     |

|     | and Control Programming                       | 80  |

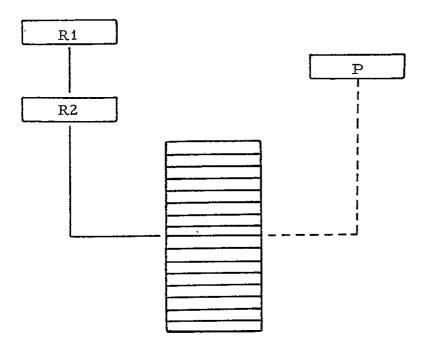

| 20. | Stack Operation                               | 92  |

| 21. | Performance-Probability Functions             | 105 |

| 22. | Performance-Payoff Function                   | 109 |

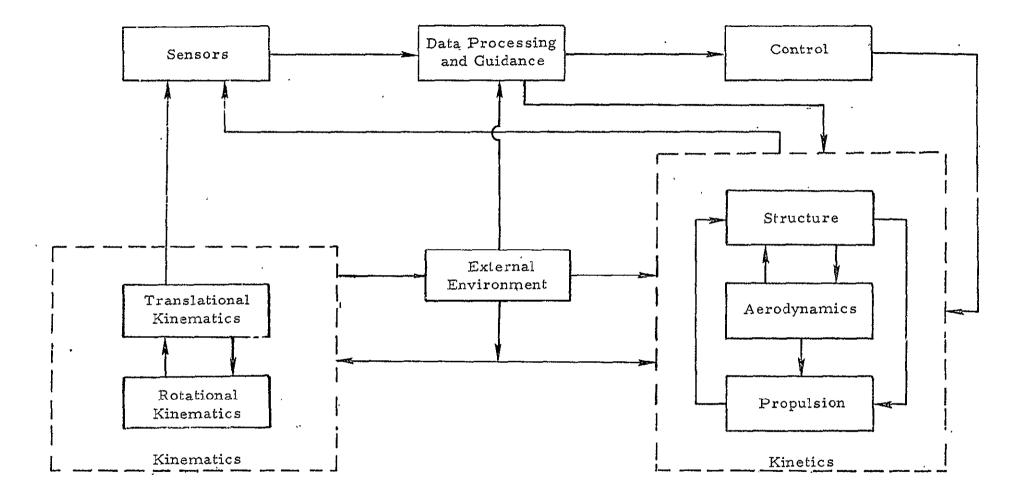

| 23. | Basic Simulation Model                        | 129 |

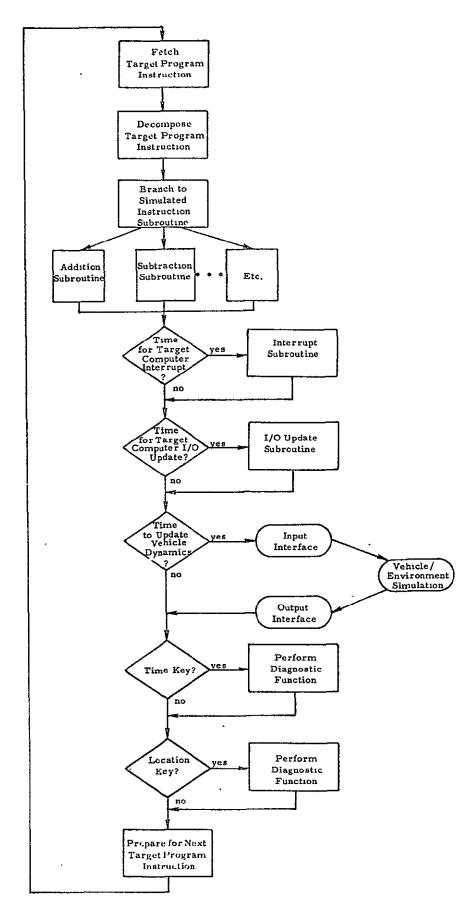

| 24. | Typical ICS Control Loop                      | 133 |

| 25. | Hybrid Simulation, Diagnostic Configuration.  | 142 |

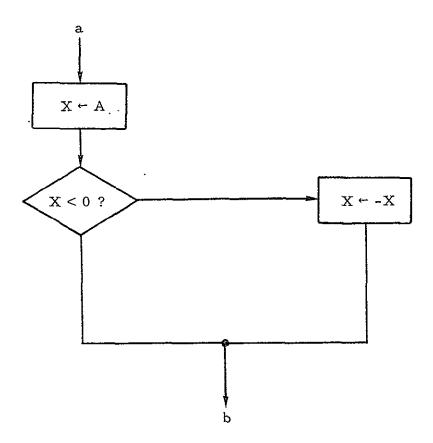

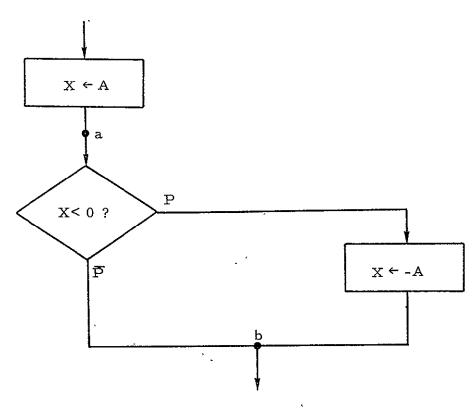

| 26. | Absolute Value Sequence                       | 147 |

#### LIST OF TABLES

| 1.          | Summary of Computational Requirements for         |     |

|-------------|---------------------------------------------------|-----|

|             | Three Space Shuttle Configurations                | 6   |

| 2.          | Computational Requirements for Three Space        |     |

|             | Shuttle Configurations                            | 17  |

| 3.          | Computational Requirements for Strapdown Inertial |     |

|             | References                                        | ť8  |

| 4.          | Computational Requirements for Navigation Sensors | 20  |

| 5.          | Computational Requirements for One Dynamic        |     |

|             | Display                                           | 23  |

| 6.          | Computational Requirements for Trackers           | 23  |

| 7.          | Computational Requirements for Landing Aids       | 25  |

| 8.          | Computational Requirements for Primary            |     |

|             | Propulsion Subsystems                             | 28  |

| 9.          | Executive Design Comparison                       | 61  |

| 10.         | Basic Instruction Set                             | 82  |

| 11.         | Performance-Probability Matrix                    | 106 |

| 12.         | Language Capabilities Required for Different      |     |

|             | Software Functions                                | 113 |

| <b>1</b> 3. | Computer Influence on Language Suitability        | 114 |

| 14.         | Language Characteristics for Different Software   |     |

|             | Development Phases                                | 121 |

#### i. INTRODUCTION

This report describes a hardware/software study of the Space Shuttle data management system. The study purpose was to identify at an early stage in system development those computer hardware characteristics and software development approaches that will have substantial impact on software costs and schedules. The underlying motivation was to prevent software development from becoming the pacing item in Space Shuttle system realization.

The study addressed three aspects of system development. An analysis of the overall Space Shuttle objectives, mission requirements, and baseline hardware configurations determined the nature and magnitude of the computational functions that the data management system will be called upon to perform. Tradeoff studies investigated the software advantages and disadvantages of alternative computer hardware configurations and architectures; single-computer (or simplex), multicomputer, and multiprocessor configurations were examined, together with detailed architectural features that could be used in each. Finally, support hardware/ software studies investigated means of facilitating flight software development. Two areas were addressed: high-order languages in which the flight software might be coded, and simulations and other analytic tools that might be used in verifying its correctness.

#### 2. SUMMARY

This section very briefly abstracts the study conclusions and recommendations and then goes into somewhat greater supporting detail on the individual study areas.

#### 2.1 Conclusions and Recommendations

The functional analysis revealed that some subsystem hardware configurations and system requirements pose unreasonable computational loads. The present overall range of computational requirements is extremely wide and must be narrowed if meaningful decisions are to be made as to the computer configuration. <u>Recommendation</u>: The functional analysis should be continued.

÷

Available data permitted basic computational requirements to be estimated for maximum, moderate, and minimum subsystem hardware configurations. From these requirements it was concluded that a simplex computer would be adequate for the minimum computational load, but that a multicomputer or multiprocessor configuration would be required for the moderate or maximum loads.

The computer configuration analysis showed that software costs would be lower for a centralized computer organization than for a distributed or federated organization. It was further determined that effective separation of a program's functional elements could be accomplished by software methods in a centralized organization, just as separation would be accomplished physically in a federated organization. <u>Recommendation</u>: A centralized computer organization should be used.

Studies of executive types as part of the computer configuration analysis showed a polling executive to be simpler to verify than an interrupt executive, but not as flexible or responsive to likely system requirements. Analysis of verification problems indicated that control of interrupts and of interrupt levels could minimize the verification problems associated with an interrupt executive. <u>Recommendation</u>: An interrupt executive should be utilized, suitably restricted as to interrupt occurrences and levels.

Further investigation of verification problems indicated that a simplex computer configuration would permit the simplest and easiest software verification. <u>Recommendation</u>: If the minimum computational requirements prevail, a simplex computer should be utilized.

A multiprocessor configuration with a distributed executive was found to result in slightly simpler software than an equivalent multicomputer, and in much simpler software than a multiprocessor with a fixed or floating executive. <u>Recommendation</u>: A multiprocessor configuration with a distributed executive should be utilized in the event that the computational requirements exceed the capabilities of a simplex computer.

In analyzing the architectural aspects it was determined that those most significant in terms of software costs would be adequate memory, speed, and input/output margins. <u>Recommendation</u>: Memory, speed, and input/ output margins of at least 40% should be provided in the hardware. Effective management controls will be required to prevent this margin from being utilized for new and possibly unneeded functions.

Software costs can be reduced by from 5 to 10% if other desirable architectural features are provided. <u>Recommendation</u>: The computer should have the following characteristics:

- Adequate instruction set, including floating-point arithmetic

- Hardware memory locks or their equivalent

- Extensive hardware error-checking, diagnosis, and correction facilities

- Save and restart facilities

- Interrupt-control facilities

Many additional architectural aspects individually have a small effect but in combination can significantly influence software costs. <u>Recommendation</u>: A computer having the features listed below on the left should be selected in preference to one having the characteristics listed on the right:

#### Desirable

- Read-only/read-write memory partitioning

- Uniform instruction execution times

- Buffered input/output

- Partial-word addressing

- General-purpose registers

Undesirable

- Auxiliary memory

- Virtual memory

- Interleaved memory

- Limited addressing range

- Unique or unusual instructions

- Variable-length instruction and data formats

The programming language investigation showed that the use of a highorder language will reduce software development costs, even though the language selected might not be completely suitable for all functions. The suitability of the compiler was found to be more important than that of the language itself. This is so because developing a completely efficient, correct, and comprehensive compiler for the Space Shuttle application will take a relatively long time. Portions of the flight software -- notably the executive -- will still have to be coded in assembly language, and verification will have to be performed at the assembly language level. <u>Recommendation</u>: A high-order language should be used, beginning as early as possible. Attention should be concentrated on compiler development rather than on further language development or refinement.

In the verification studies, the conclusion was reached that simulations will continue to be the most important verification tools. However, the anticipated speed, size, and complexity of the flight computer configuration will result in corresponding increases in simulation execution times, which, for interpretive simulations, will approach unacceptable amounts. <u>Recommendation</u>: Interpretive computer simulation diagnostic methods and outputs should be improved to maximize the information obtained from each simulation run. Further, hybrid simulation techniques should be extended to yield information now efficiently obtainable only from interpretive simulations.

Another conclusion regarding verification was that each type of simulation is suitable only for particular roles, and problems detected by one type may require the use of another for adequate diagnosis. <u>Recommendation</u>: A master test plan should be developed and implemented covering simulation use and comparison.

Finally, simulations can demonstrate the existence of software errors but cannot absolutely prove their absence. One technique was developed for designing programs whose correctness could be proved, and another for proving the correctness of relatively simple programs. <u>Recommendation</u>: These techniques should be further developed, and additional techniques should be investigated.

#### 2.2 Functional Analysis

Because hardware definition was incomplete and changing during the functional analysis, it was not possible to establish firm and detailed quantitative measures of the computational load to be imposed on the data management system. The analysis did illustrate how otherwise reasonable subsystem hardware configurations and system requirements, notably those of the docking laser and the displays, can result in an unreasonable computational load. Sufficient data were available to permit basic computational requirements to be determined for three possible Space Shuttle configurations:

- A maximum system able to satisfy all mission requirements and providing complete support and status monitoring for all associated subsystems

- A minimum system able to satisfy the basic mission requirements but providing for minimum onboard checkout and having many functions performed by hardware distinct from the central computer facility

- A moderate system providing capabilities midway between those of the two extremes

The primary computing requirements for these three configurations are summarized in Table 1. All requirements for the minimum configuration are within the capabilities provided by existing simplex computers. However, the computational speed required for the moderate and maximum configurations cannot be provided by either existing or foreseeable simplex computers: a multicomputer or multiprocessor would be required to provide the necessary effective computational speed.

For all Space Shuttle configurations, the table indicates only the minimum necessary capabilities. It does not include provision for expansion to support new subsystems and additional mission requirements, nor does it provide allowances for software inefficiencies. Even though the 24-bit word size would be adequate for the minimum configuration, a larger word size

|                                    | Configuration |          |         |  |

|------------------------------------|---------------|----------|---------|--|

| Parameter                          | Minimum       | Moderate | Maximum |  |

| Total memory size (thousand words) | 43            | 120      | 250     |  |

| Word size (bits)                   | 24            | 32       | 32      |  |

| Add time (microseconds)            | 25            | . 25     | .10     |  |

Table 1. Summary of Computational Requirementsfor Three Space Shuttle Configurations

would nearly eliminate the need for double-precision operations and hence is preferable. As regards memory size and computational speed, the architectural aspects studies indicated that adequate margins are the most important factors in determining software costs. Capacities exceeding the minimum values listed are mandatory if software costs are to be minimized. An allowance of 40% for the inefficiency component alone would permit use of a high-order language to simplify program coding and, in addition, executive design and programming standards that simplify software verification.

The range of requirements indicated for the three possible configurations is extremely wide. It must be narrowed so that decisions concerning the computer configuration can be made in a way that minimizes the cost and difficulty of software development. Therefore, the functional analysis should be continued through the completion of the flight software development.

#### 2.3 Computer Configuration

The software problems inherent in a computer system in which most of the computational capability is concentrated in a central facility were first contrasted with those inherent in a system in which the computational capabilities are in large part distributed to the subsystems. In the centralized system, the relatively small amount of processing performed at the subsystem level would largely be restricted to data formatting, compaction, and limit checking, and to input/output buffering. However, in a few instances -- for example, a strapped-down inertial reference unit -more complicated computations would be performed at the subsystem level. In a distributed, or federated, system, the central computer facility would do significantly less processing; its principal task would be to control and coordinate the activities of two or more computers that were both logically and physically closely linked to particular subsystems or sets of subsystems.

A centralized system would permit a substantial majority of the software to be developed for a computer architecture that facilitates both programming and verification, and it would simplify the communication between related functional programs. A federated system, on the other hand, would greatly complicate the problem of allocating computational resources and would be less flexible. Therefore, a centralized system would result in lower software production costs than a federated system. The isolation that prevents a program in one computer from erroneously interfering with a program in another can be achieved in a centralized system by proper

## PRECEDING PAGE BLANK NOT FILMED

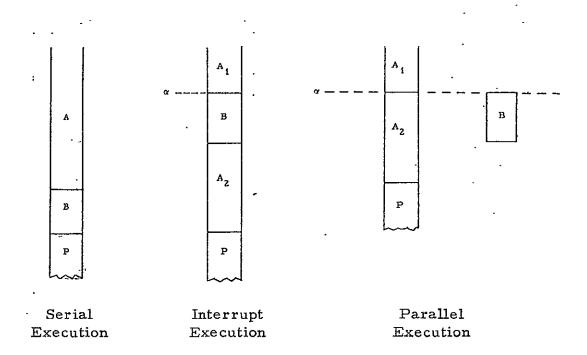

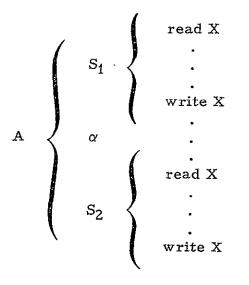

The executive, whether polling or interrupt, is in any event simpler to develop and easier to verify for the simplex computer than for the multicomputer or multiprocessor. For these two configurations, significant executive design aspects are the location of the executive and tasks and the assignment of processors to tasks. In the distributed-executive scheme, which is applicable to both configurations, each computer or processor has its own executive and tasks. In the multiprocessor/fixedexecutive scheme, the executive is assigned to one processor; this one executive then dynamically controls the execution of all tasks, allocating them to processors as dictated by the computational load. In the multiprocessor/floating-executive scheme, both the executive and the tasks are allocated according to the mix of tasks in execution.

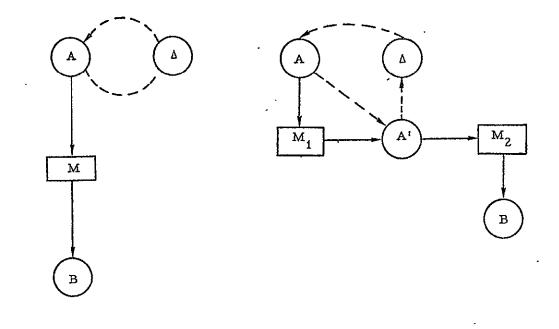

Although the fixed and floating executives offer increased flexibility and performance, the greatly increased verification problems they present led to the conclusion that the distributed executive is more suitable for a Space Shuttle multiprocessor configuration. As regards distributed executives for multicomputer vs. multiprocessor, the only significant difference lies in the mechanism for communicating between tasks allocated to different computers or processors. In the multicomputer, this communication must be done through the normal input/output operations, while for the multiprocessor it is accomplished by simple, direct memory access methods.

In terms of minimizing software development difficulty and cost, the simplex configuration would be best. A simplex configuration may not be sufficient, however, if anything more than the minimum functions are to be performed by the data management system. Indeed, great increase in software development difficulty will occur if a simplex configuration is chosen that provides inadequate or barely adequate computational capabilities. Of the two remaining configurations, the multiprocessor with a distributed executive would result in slightly lower software development costs than the multicomputer. Therefore, it is recommended that a simplex computer be selected if it can provide the necessary computational capability; this is likely only if the Space Shuttle hardware configuration and system requirements are close to minimal. If more computational capability is needed, the multiprocessor configuration with a distributed executive should be chosen in preference to a multicomputer configuration.

The multiprocessor with fixed or floating executive has been excluded because of the verification difficulties these two executive designs present. Indeed, verifying the executives for all of the configurations is one of the most difficult problems that will be encountered in software development. Enough excess computational capability must be provided so that programming standards can be employed that, although increasing the software overhead, reduce verification difficulty. That is to say, the selected computer or computers must provide an adequate margin of computional capability so that tradeoffs between program efficiency and verification ease can always be decided in favor of the latter.

#### 2.4 <u>Computer Architecture</u>

In this portion of the study, the advantages of specific architectural characteristics were identified and their impact on the cost and difficulty of Space Shuttle executive and task program development and verification estimated. Although hardware costs were not explicitly included, only those architectures that have been demonstrated or could practicably be implemented were considered.

The basic criteria influencing software development and verification difficulty and cost were defined in terms of the suitability or adequacy of the following classes of architectural features:

- Memory

- Execution speed

- Input/output facilities

- Instruction set

- Word format

- Register organization

- Restart and self-test provisions

- Interrupt-handling facilities

Minimum capability levels with respect to the first three criteria are mandatory if the software is to be produced at all. After the basic requirements have been satisfied, the most important characteristics were found to be the memory, speed, and input/output capability margins that simplify both coding and verification.

Coding and verification costs increase sharply as the memory usage and execution time approach the available capabilities. On the other hand, given sufficient memory, speed, and input/output capabilities, almost any instruction set, register organization, and word format can be used without drastically increasing software costs. Providing surplus capacity poses a problem, however. Unneeded functions may be added simply because the capacity exists, leading to an even larger program that may then have to be tailored to match what turns out to be a barely adequate computation capability. It is therefore vital that effective management controls be imposed so that the margins provided will be utilized for reducing rather than increasing software costs.

While no other architectural aspects were found to have an impact equal to that of adequate memory, speed, and input/output margins, appreciable reductions in software cost would result from a computer design that incorporates a significant number of those remaining. As an example, providing hardware floating-point arithmetic would reduce the size of the software by up to 5%, and this reduction would translate into even greater reductions in programming and verification difficulty. As another example, providing hardware memory locks and special save and restart instructions would have a smaller impact on program size but just as significant an impact on verification ease: many operations that otherwise would have to be checked individually would be accomplished automatically by the hardware. Finally, some aspects, such as interrupt-control mechanisms, would enable the adoption of software design approaches that would otherwise be impossible.

It is recommended that the computer configuration have memory, speed, and input/output capability margins of at least 40%. It should also provide the following architectural features, each of which will affect overall software costs by about 5 to 10%:

- A suitable instruction set, including hardware floatingpoint arithmetic

- Hardware memory locks, memory bound registers, or similar hardware protection mechanisms

- Extensive hardware error-checking and diagnostic facilities, with appropriate feasible correction capabilities

- Provisions for saving computer registers and other status information and for restoring these registers and the status with a minimum of program steps in the event of a computer malfunction

- Capability for enabling and disabling interrupts, both absolutely and according to at least three priority levels

Besides the architectural aspects already discussed, the overall software costs are affected to a lesser degree by the presence or absence of other features. Verification problems would be eased by providing partitioning into read-only and read-write segments, uniform instruction execution times, and buffered input/output. Capabilities for partial-word addressing and general-purpose registers would be beneficial because these features reduce data handling. With regard to the way in which an adequate memory margin is achieved, a computer architecture that used an auxiliary memory or some form of virtual memory would be less desirable than one that provided an equivalent amount of uniform main memory. Interleaved memory is similarly undesirable; even though it provided adequate speed margin, verification problems would ensue because repeatability of program execution times would be seriously compromised. Other architectural aspects such as limited addressing range, unique or unusual instructions, and variable instruction and data formats are undesirable because they require more effort on the part of both programmers and verifiers.

There are still other architectural aspects that are of even less concern in terms of software development costs, but of great concern to the hardware designer -- so much so that they may determine whether the more important software-impacting features can be incorporated at all. A facility for microprogramming is such an aspect. While the instruction set is software-important, the means of providing suitable instructions -whether by microprogramming or hardwired logic -- is of no significant concern to the programmer.

#### 2.5 <u>Programming Languages</u>

The suitability of six high-order languages for Space Shuttle onboard software development was investigated in terms of such characteristics as the amount of the problem that could easily and effectively be stated in the language, the control the language affords over computer hardware operations, and the extent that the language can be utilized throughout the software development cycle. Of the six languages, four were designed especially for aerospace applications: CLASP (Computer Language for Aeronautics and Space Programming), SPL Mk II (Space Programming Language Mk II), SPL Mk IV, and HAL. Two -- FORTRAN and PL/I -- were primarily designed for genéral-purpose applications. Compiler considerations were also investigated, with the most influential found to be the efficiency and correctness of the machine code generated, the diagnostic facilities provided, and the compiler development cost and time.

FOR TRAN was found to have few advantages and many disadvantages for enboard software development. A smaller portion of the software could be coded in CLASP or SPL Mk II than in the more comprehensive languages HAL, SPL Mk IV, and PL/I. However, with the simpler languages object code efficiency would be greater and the cost of compiler development smaller. The executive program would in any event have to be written in assembly language: the simpler languages lack the necessary features, while the compilers for the more comprehensive languages would be unable to generate the highly efficient object code required. Overall, it was concluded that use of any of the aerospace-oriented languages to the extent possible would reduce software development costs. The problem of compiler efficiency, the principal obstacle to the use of a high-order language, can be reduced by providing adequate memory and speed margins in the computer configuration.

Accordingly, it is recommended that a high-order language be used. Even though they have deficiencies, any of the existing aerospace-oriented programming languages would be appropriate, with their compilers being more significant than the language capabilities as such. Because of the difficulty in obtaining a completely suitable compiler, particularly for the larger languages SPL Mk IV and HAL, memory and speed estimates should provide for object code inefficiencies of about 15% and, for the reasons stated above, the executive program should be coded in assembly language. In view of the possibility that a new compiler will in some cases generate erroneous object code because of its own deficiencies, verification must continue to be done at the machine or assembly code level. Substantial verification benefits can be achieved, however, because the compiler can be so implemented as to enforce conformance with programming standards and conventions.

#### 2.6 Verification Tools and Techniques

In this part of the study it was determined that the three types of simulations used in previous aerospace software verification activities -- engineering simulations, interpretive computer simulations, and hybrid simulations -will continue to be the most important verification tools for the Space Shuttle onboard software. However, means of improving these tools and their use are required. A deficiency of interpretive simulations has always been the ratio between simulation time and real time, and with the much faster Space Shuttle computer system this unfavorable time ratio will become even worse. Two partial solutions to this problem were conceived. First, the interpretive simulation should contain more extensive and automatic diagnostic and information-gathering features that, at the expense of a slight increase in simulation time, would permit more to be learned from each simulation run, thus reducing the number of runs required. Second, the hybrid simulation should be improved so that it can provide much of the detailed information about internal program behavior that presently is obtained only through an interpretive simulation. One means of making this possible is to design the flight computer so that its internal operation can be monitored by another diagnostic computer that would be a new part of the usual hybrid simulation setup.

Of course simulation tools cannot be used to prove the absence of program errors; they can only demonstrate an error's existence. In view of the large number of errors possible in the large and complex Space Shuttle onboard computer program, analytic verification methods should be developed to aid in proving program correctness and to indicate program design methods that would result in programs whose correctness could be demonstrated. Two such approaches were explored: one defining the constraints that must be satisfied to achieve program correctness when a restart occurs, and one to prove program correctness for a limited number of program structures.

It is recommended that improvement of simulation tools and techniques be pursued, and that a master test plan be defined for comparing simulation results and validating the simulations themselves. Further, the development of means for demonstrating program correctness should also be pursued and the tools integrated into the Space Shuttle software development and verification procedures.

### 3. " FUNCTIONAL ANALYSIS

The analysis of the functions to be performed by the Space Shuttle computer system was undertaken to establish its desired characteristics in terms of the computational load to be imposed on it. Computational load can be estimated in terms of the computer memory required, the number of instructions that must be executed in a given interval, and the input/output rates that must be maintained. Also important are factors relating to the computational tasks: their relative priorities, their periodicity, the amount of intertask communication, and the number and attributes of routines shared between tasks.

The analysis began by assembling and evaluating available reference data. Where the available documentation was incomplete or inconsistent, assumptions were made as to the most probable hardware configuration. In some areas, models were constructed and the range of requirements for alternative configurations was determined; in others, experience with existing systems was sufficient to allow the expected behavior of their Space Shuttle counterparts to be determined. The most detailed analysis was performed on the guidance, navigation, and control portions of the system, since these offered both the greatest computational load and the most comprehensive source material.

It was not possible to establish firm and detailed functional requirements; rather, the functional analysis indicated the rough order of magnitude of computational requirements. At this stage of Space Shuttle system definition, the computational load ranges from one close to that of Apollo to one that large ground-based computers of today would have difficulty in supporting. As the interfacing hardware becomes firmer, extension of the functional analysis would allow requirements to be determined with greater realism.

A major computational function not analyzed in the present study is the malfunction (or error) diagnosis, circumvention, and system reconfiguration necessary to meet the fail-operational/fail-operational/fail-safe requirements. A preliminary survey of this function indicated that the software needed to implement this requirement could double the computational load, while the far greater number of possible sequences of program execution introduced by this software could increase by an order of magnitude the time and cost required for verification. The added information afforded by further hardware design definition should permit meaningful analysis of reconfiguration requirements. Overall computing load estimates were developed for three conceptual configurations -- minimum, moderate, and maximum -- defined as follows:

- <u>Minimum Configuration</u>: This system provides for a gimbaled inertial unit or a strapdown system with its own processor; a basic set of sensors (e.g., star tracker or telescope and RF-only navigation); limited onboard target-ing; basic telemetry without data compression; displays essentially unprocessed in the central unit; status monitor-ing for guidance and control and other subsystems; and an executive appropriate to a multiprogrammed simplex computer with an interpretive language.

- <u>Moderate Configuration</u>: This system allows for a strapdown inertial unit processed in the central computer; unitized pointing platform and docking laser (with minimum filtering); dual propulsion systems (main and orbit maneuvering) with active load alleviation; extended onboard targeting; downlink data compression; a pair of redundant unified displays; status monitoring for the extended sensor set and for single-parameter checks of interfacing systems; and an advanced simplex executive without interpreter.

- <u>Maximum Configuration</u>: This system assumes a strapdown inertial unit processed centrally; the full sensor complement with a state-of-the-art filter; adaptability to three propulsion systems (including turbojet) with active load alleviation; onboard targeting for arbitrary rendezvous; data analysis including pattern recognition and multiparameter trend analysis; dual, independent unified displays; full monitoring of status of avionics and all other reconfigurable systems; and a multiprocessor executive without interpreter.

The computational requirements for these three configurations are presented in Table 2. Supporting analyses for the individual hardware subsystems follow in the remainder of this section. These analyses include hardware configurations supplemental to the configurations of Table 2; and some subsystems, notably the display subsystem and the docking laser, can result in computational loads far in excess of the estimations in Table 2. That is, the data in Table 2 represent the best estimation of what actually will be required for Space Shuttle.

|                                      | Configuration |          |         |  |

|--------------------------------------|---------------|----------|---------|--|

| Parameter                            | Minimum       | Moderate | Maximum |  |

| Total manager size (thereased monda) | 43.0          | 120      | 250     |  |

| Total memory size (thousand words)   | 43.0          | 120      | 250     |  |

| Inertial reference                   | 2.5           | 15       | 15      |  |

| Navigation sensors                   | 2.5           | 20       | 50      |  |

| Guidance, navigation, and            |               |          |         |  |

| control                              | 10.0          | 40 ·     | 50      |  |

| Telecommunications                   | 0.5           | 2        | 20      |  |

| Display and control                  | 1.5           | 15       | 30      |  |

| Guidance and control status          |               |          |         |  |

| monitoring                           | 1.0           | 8        | 10      |  |

| Other subsystem status               |               |          |         |  |

| monitoring                           | 10            | 10       | 40      |  |

| Executive, interpreter, and          |               |          |         |  |

| overhead                             | 15            | 10       | 35      |  |

|                                      |               |          |         |  |

| Word size (bits)                     | 24            | 32       | 32      |  |

| Add time (microseconds)              | 25            | 0.25     | 0.10    |  |

#### Table 2. Computational Requirements for Three Space Shuttle Configurations

#### 3.1 Inertial Reference

Two major classes of inertial references exist, distinguished by the nature of the gyro integration. A gimbaled system implicitly integrates attitude changes by maintaining a stable member, while a strapdown system maintains its reference as a set of data in the computer, which performs an electronic (normally digital) integration. The strapdown system, with its explicit computer integration, is more computationally demanding than the gimbaled system. Its higher reliability and lower cost make it the more likely selection for Space Shuttle.

The computational requirements of four strapdown systems representative of the state of the art are summarized in Table 3. The Lunar Module Abort Guidance System (LM/AGS) was self-contained except for alignment (derived

|                             | System |       |           |          |

|-----------------------------|--------|-------|-----------|----------|

| Parameter                   | LM/AGS | ASST  | RSS       | MIT/SIRU |

| Memory capacity (words)     | 4096   | 2150  | 13,130    | 16,384   |

| Memory cycle time (µsec)    | 5.0    | 4.0   | 1.75      | 0.96     |

| Word size (bits)            | 18     | 18    | 24        | 16       |

| Number of instructions      | 27     |       | 43        |          |

| Add time (µsec)             | 10     |       | 3.5       | 1.92     |

| Multiply time (µsec)        | 70     |       | <b>i4</b> | 5.76     |

| Major cycle interval (sec)  | 2      | 1-2   | 1         | 0.5      |

| Minor cycle interval (msec) | 20-40  | 10-20 | 40        | 10       |

Table 3. Computational Requirements for Strapdown Inertial References

from memory of the primary system). The Advanced Supersonic Transport (ASST) strapdown system incorporated redundant sensors and limited logic for failure detection, diagnosis, and correction. The Redundant Sensor System (RSS) employed more elaborate reconfiguration logic, increasing the software requirements considerably. Of all the four systems, the MIT/ SIRU (Strapdown Inertial Reference Unit) most closely approximates Space Shuttle requirements.

The MIT/SIRU uses six gyros and six accelerometers aligned perpendicular to the faces of a dodecahedron. The computing capacity indicated for the MIT/SIRU is capable of performing the integration and formatting required of any strapdown system, plus fail-operational/fail-operational reconfiguration in its entirety. The logic to support reconfiguration for a third level of failure detection and diagnosis might be developed, but would be qualitatively different in form and would impose a very large load on the computing system. Instead of the extra software, a second SIRU may be used. That choice also protects against catastrophic failure, so is preferred. If the dual system is used, the computing load would be approximately double that shown in the table.

The primary information to be supplied by the inertial reference to the data management system is the attitude of the vehicle in inertial space. The

initial form of gyro data is the pulse representing an increment of attitude about that gyro's input axis. In any strapdown system, these pulses must be accumulated and transformed through rotation of coordinates to derive inertial attitude. The nonorthogonal arrangement of SIRU axes complicates the rotation algorithm but does not alter the basic task.

In dividing the attitude determination between local and central processors, three choices exist: local formatting only, local accumulation and formatting, or full local attitude determination. If local processing is restricted to formatting, major burdens are imposed not only on the central processor but also on the data bus, which must transmit up to 1600 pulses per second per sensor. By accumulating the pulses in a local buffer, the data rate may be reduced without adding major computation. During the 10-msec minor cycle, 16 pulses are accumulated per sensor and may be transmitted with only 4 bits. They may be packed into words of length established by the data bus design; the effective rate is fixed at 48 bits per cycle. Additional bits are required for sensor status data.

Full use of a local processor is desirable for the SIRU because the computing burden is high. The coordinate conversion must be performed every 10 msec, whether executed in the local processor or the central computer. A convenient form for the output of attitude from the local processor is a set of quaternions (four 16-bit words). Although local coordinate conversion increases the traffic on the data bus, the saving in central computing is felt to be worthwhile. The accumulated velocity increments may also be transformed into an inertial frame in the local processor (however, subsequent integration to a state vector in the local processor would require external data and thus is undesirable). The transformed velocity increment may be packed into a single 16-bit word for each minor cycle. In such application of the local processor, an interface is maintained with the data bus equivalent to that of a gimbaled platform with accumulated  $\Delta V$ . Development of suitable alignment algorithms may then permit central routines to be taken from programs proved on earlier projects.

In any division of computing burden between central and local units, status data must be provided for reconfiguration. The specific data required, their rates, and their processing requirements are not yet known. It is assumed that the local processor can perform high-rate filtering in the preferred configuration and that two 16-bit words per minor cycle will suffice to maintain the central files. In the absence of local processing, both high data rates and extensive central processing would be needed.

#### 3.2 Navigation Sensors

The attitude and state vector estimates maintained by the inertial reference must first be established and should be updated through the use of specialpurpose navigation sensors. A wide range of sensor systems has been considered for Space Shuttle. The simplest configuration in terms of computing load involves radio frequency transponding from known ground locations. The heaviest computing load is that for a system employing three sensors -- star tracker, sun sensor, and horizon scanner -- mounted on a unitized pointing platform having two degrees of freedom and driven by computer commands. Computational requirements for such a system are summarized in Table 4 and were derived as follows.

Initial alignment of the inertial reference will require stabilization of the spacecraft, acquisition of the sun and the horizon by the sensors, driving the platform to put each of at least two reference stars sequentially in the star tracker field of view, and processing tracker error signals, platform azimuth and elevation, and spacecraft attitude (from the inertial reference) for each sighting. Alignment will be confirmed confirmed driving the platform to at least one additional reference star and verifying its location in the star tracker's field.

Occasional star sightings will be made under computer control to maintain alignment, and the altitude of a sequence of reference stars above the horizon will provide position data. Operationally, one or two such points may be

| Component            | Data Format | Data Rate  |          |  |

|----------------------|-------------|------------|----------|--|

| , component          | Data FOIMat | Alignment  | Tracking |  |

| Platform orientation |             |            |          |  |

| Analog servo         | 2 x 16 bits | 10 sps     | 1 sps    |  |

| Digital servo        | 2 x 16 bits | 30 sps     | . 1 sps  |  |

| Star tracker         | 2 x 16 bits | · discrete | discrete |  |

| Sun sensor           | 2 x 16 bits | discrete   | discrete |  |

| Horizon scanner      | 2 x 16 bits | 10 sps     | 10 sps   |  |

Table 4. Computational Requirements for Navigation Sensors

taken every 10 minutes, as the other tasks permit, to minimize residual errors. Each platform angle covers a range of  $\pm 30^{\circ}$ , for which 16-bit quantization seems desirable. The horizon scanner provides only elevation deviation, which, depending on the scanner field of view, may be quantized with up to 14 bits. Similarly, azimuth and elevation deviation from the sun sensor may be quantized to 14 bits each; however, practical arguments suggest that 16 bits will be used. If the star tracker field is  $5^{\circ}$  in each axis, 16-bit quantization of its data pair appears more than adequate, yielding less than 0.6 sec error. With regard to data rate, it is assumed that the horizon scanner will provide periodic data of the order of 10 times per second. The sun sensor and star tracker will have data available continuously; the former will be sampled up to 10 times per second, while the latter need be read only once per star. These rates are marginal to obtain 5-sec accuracy with a residual attitude rate of  $0.01^{\circ}$ /sec.

Once alignment has been obtained, there appears to be no requirement to command the platform repetitively; that is, given an inertial reference, a single pair of platform commands will drive the sensors to the desired attitude through a platform servo loop. This implies a data rate of 10 samples per second. If the reliability or other cost of such a loop is unacceptable, it it will be necessary to generate incremental commands with computer-derived damping to drive the platform to the desired position. In that event, platform angles may have to be both read and commanded at up to 30 times per second to obtain the desired stability, and it may be preferable to use a platform rate command rather than an angle command as the interface. The analogy between these functions and those of the digital autopilot may be strong enough to allow some common usage of routines.

In addition to the estimates presented in Table 4, normal monitor and command functions will be required, and calibration is indicated for the horizon scanner and will probably be required for the other sensors as well. Lacking data on the mechanisms to be employed, it is estimated that a few hundred words of program may be needed for each sensor; that the star tracker and sun sensor would be calibrated once for each set of measurements (perhaps once per 10 minutes of use); and that the horizon scanner will require collection of data over several scans, perhaps 10, in every 10 minutes of use.

#### 3.3 <u>Displays</u>

The display hardware is less completely defined that any of the other avionics subsystems. To estimate computer requirements, one dynamic display example -- the video image of the runaway for blind landing -- was constructed and analyzed in detail. From AWAILS or from ILS and the altitude radar, the computing system determines the vector in inertial coordinates to the end of the runway; this may be rotated into the vehicle frame. The magnitude of the vector (distance to the end of the runway) establishes the scale of the image, while the pitch, roll, and yaw angles control the display perspective.

Any one of several analog mechanizations may be used to support a CRT image or a projected slide of the data with frequent update. The maximum load such an analog-supported display would impose on the computing system would be four 24-bit words sent 30 times per second. Up to 40 add times may be required to format each word, yielding 4800 adds per second.

The analog support equipment, while it reduces the digital load, is both heavy and subject to failure. Replacing the analog hardware with specialpurpose digital devices does not alter the problem; only centralized digital processing reduces the display penalty by providing redundancy through equipment already onboard. However, in providing the display of the example with digital processing, a heavy computing load is added to the central processor. The 30-frame-per-second rate is still required to avoid flicker, but now each point must be commanded by the central computer.

An algorithm that minimizes the central processing required was developed for generating the display. In constructing the algorithm and the example, it was assumed that only straight lines with a single intensity level would be required, even though several values of intensity may be desired for other purposes. Even so, each display frame requires six sets of four segment parameters and one inversion. For each of the 400 to 500 lines in a frame, the computer must apply the algorithm to each display line (six multiplies, six adds), determine the termini of each segment (12 adds), test each terminus for inclusion in the frame (four or eight compares), and assemble a sequence of binary words in which each bit corresponds to a point on the scan line. Typically, 15 words will be required to depict a scan line, suggesting a composite requirement for each line in excess of 6 multiplies, 18 adds, 24 compares, and 15 logical OR's. The available time, determined by the required frame-per-second rate, is 30 msec divided by 400 lines, or 75  $\mu$ sec. Assuming that 10 adds require the same time as one multiply, the arithmetic operations alone require an add time of less than 1 µsec.

Table 5 summarizes the results thus derived for the analog-supported and the centralized displays. It can be seen that even a central processor with a 0.5- $\mu$ sec add time would be hard pressed to handle the unsupported display when the logical operations for each line are added to the arithmetic operations, and when the projections required to provide segment information at

| Parameter        | Supported<br>Display | Centralized<br>Display |

|------------------|----------------------|------------------------|

| Bits per frame   | 96                   | 200,000                |

| Words per second | 120                  | 220,000                |

| Adds per second  | <5,000               | >1,000,000             |

Table 5. Computational Requirements for One Dynamic Display

the frame level are included. Further increases in computing load may arise from the need for color display; redundant and supplemental displays; and requirements for trend analysis or other digital processing. Thus from this work it is apparent that the range of requirements for the displays is several orders of magnitude. Fortunately, analog hardware can be used to maintain a reasonable computing load.

#### 3.4 Trackers

Three tracking subsystems were reviewed: the docking laser, the rendezvous radar, and the infrared tracker. The resulting computing load in terms of data and command rates is developed below and summarized in Table 6. It should be pointed out that no interaction between these subsystems was indicated in the pertinent preliminary literature -- although it is likely that such interaction will exist and that it will have significant computational impact.

|                  | Trac        | ker Data         | Compute      | r Commands,     |

|------------------|-------------|------------------|--------------|-----------------|

| Tracker          | Bits/Sample | Samples/Second   | Bits/Command | Commands/Second |

| Docking laser    | 24          | <10 <sup>3</sup> | 16           | 10 <sup>3</sup> |

| Rendezvous radar | 48          | 10               | 16           | noniterative    |

| Infrared tracker | 16          | 1                |              | . <b></b>       |

Table 6. Computational Requirements for Trackers

#### 3.4.1 Docking Laser

The Space Shuttle requires a new type of sensor to determine the attitude of a passive base for docking. The one studied employs a modulated laser beam to determine the range along the beam and the displacement from its center of the return from each of three reflective targets on the docking ring. The modulation allows a separate range processor to establish the distance to each target within a fraction of the shorter modulation wavelength (13 ft) over a separation equal to the longer wavelength (1300 ft). Target position in the plane perpendicular to the beam is determined by electronic scanning of the detector. The beam must dwell on each target long enough to obtain a suitable signal-to-noise ratio; it is estimated that the maximum data rate from the docking laser is 1000 measurements per second.

Range is quantized with 8 bits of coarse data and 4 of fine to provide resolution of 5 in. The position of the scan at maximum signal is encoded with 6 bits in each direction. Scan command may be provided by a local processor on receipt of a discrete from the central computer, or it may be provided directly by the central computer; this implies a data rate in excess of  $10^6$ bits per second. Another alternative is to use some local processing to reduce the load on the data bus, decoding a 16-bit word each millisecond into a search pattern.

Reduction of the laser data is a major problem for the computer. One method was studied in which a coordinate converter, dynamic models of the Space Shuttle and target, and a Kalman filter are employed. The coordinate converter rotates the reference system into a frame with minimum filtering to reduce the total computing load. The dynamic models then estimate the attitude and position of each vehicle for comparison with sensor data, and the Kalman filter determines the best estimate of attitude and position from the past and present sensor data, taking into account detectable sensor errors. The Kalman filter is the only known means of determining docking information with the required precision. Among the operations required for its use are the inversion of a matrix presently estimated to contain over 1000 elements. Ideally, the filter would be applied to each target as detected by the laser, requiring up to 1000 matrix inversions per second. The resulting load is the equivalent of 50 X 10<sup>6</sup> additions per second, a value which cannot be handled by even a large ground computer. Only when detailed system requirements and sensor designs have been established can a practicable filter be developed.

#### 3.4.2 Rendezvous Radar

The rendezvous radar locates an active target through scanning and detection of a microwave beam, with the electronic scan either generated in the radar or commanded by the central computer. The scan position at maximum return locates two coordinates of the target; each coordinate may require 8-bit encoding to maintain accuracy. Sixteen bits may be provided for each of range and range rate, so that there will be 48 bits in each data set. Although lower rates have been suggested for Space Shuttle, automatic rendezvous may require up to 10 data sets per second. The phased array used on the radar is amenable to a Cartesian coordinate system, with 8 8 bits in each dimension providing scan commands. Signal lock is maintained by radar electronics, so that only one set of commands is needed to acquire and maintain lock.

#### 3.4.3 Infrared Rendezvous Tracker

The infrared rendezvous tracker detects the thermal radiation of the base to determine polar coordinates within its field of view (5° full-cone angle about the longitudinal axis). Scanning is entirely under internal control. Data should be available at least once per second, each set consisting of the azimuth and elevation of the base, with each angle encoded to no more than 8 bits. Depending upon detector design, it may be possible to use the infrared rendezvous tracker with the sun in the field or reflected by the base. It is possible that sun-avoidance logic for the scan pattern may be required, suggesting two 8-bit words per second from the computing system to the scan control when the sun is in the field of view.

#### 3.5 Landing Aids

Five landing aids were reviewed: altitude radar, ATC transponder, VOR TACAN, instrument landing system (ILS), and all-weather automatic instrument landing system (AWAILS). Their computing loads, as derived during the functional analysis, are discussed below and summarized in Table 7 in terms of data rates. The last three systems are complementary in principle but will have significant periods of combined operation where their data will be supplementary.

Table 7. Computational Requirements for Landing Aids

| Landing Aid     | Data Rates                   |

|-----------------|------------------------------|

| Altitude radar  | 16 bits/100 milliseconds     |

| ATC transponder | 9 x 24 bps (output from DMS) |

| VOR TACAN       | 3 X 8 bps                    |

| ILS             | 2 x 8 bps + 1 discrete       |

| AWAILS          | 3 X 8 bps                    |

|                 |                              |

#### 3.5.1 Altitude Radar

This landing aid determines height above the local terrain from the transit time of a 9-GHz signal. Since terrain variation will be a significant factor in the received data; smoothing will be required by the computing system. It seems likely that 16 bits will suffice for the data, and that a nominal rate of the order of 100 msec between samples will provide rapid response and effective smoothing. One possibility is that landing at the nominal site would call for removal of known terrain variation from the data, either complementing or replacing smoothing. Since the vehicle must be capable of landing at unplanned sites, such a feature for the nominal seems to be of little advantage, while it might commit a significant portion of memory.

#### 3.5.2 ATC Transponder

The air traffic control transponder is modulated with avionics data for ground control. The following data should be required no more than once per second:

- Reference time (GMT): 16 bits

- Mean altitude above terrain (unweighted average of altitude radar data): 16 bits

- Inertial state vector (referenced to the rotating earth): 6 × 16 bits

- System status code (synthesized from individual status data): 16 bits

Other data available in the landing phase would appear to be of little value to those receiving the transponder signal, since the computing system interface is independent of the operating mode of the transponder during landing phases.

#### 3.5.3 VOR TACAN

VOR TACAN is a pair of data sources (omnirange and TACAN) providing inflight data relative to earth-fixed transmitters. Each system employs a signal from the ground, decoded onboard into an identifying tone for the transmitter, a reference bearing, and a variable bearing as a function of vehicle position relative to the antenna. It is assumed that manual identification of the station will be employed, since the analog/digital and digital requirements for automatic identification seem unnecessarily costly. TACAN also includes an active ranging path to its antenna. Particularly because of the short range over which VOR TACAN data are good, 8-bit encoding of each bearing signal and of range would appear sufficient. While data are available essentially continuously, sampling once per second should be sufficient.

#### 3.5.4 ILS

The instrument landing system is used to bring the vehicle to the middle marker of the runway through detection of azimuth and elevation from a reference transmitter; a supplementary antenna signals passing of the outer and middle markers. The detected signals of glide slope (elevation) and localizer (azimuth) may be usefully encoded to about 8 bits and sampled once per second. The two marker signals should be discretes to the computing system, and require sampling at the same rate but for only the brief period near their expected occurrence. Ambiguities exist in ILS data and may require resolution in the computing system, both for display and for automatic landing. Comparison between inertial reference and ILS data should be sufficient to determine which of the five possible ILS references has been detected and to optimize the landing trajectory.

#### 3.5.5 AWAILS

The all-weather automatic instrument landing system, employed only in the final stages of landing, provides angular interfaces equivalent to those of ILS and supplements them with measurement of range to a transponder on the runway. Again, 8-bit encoding of each of the three data inputs should suffice and sampling once per second would appear adequate.

#### 3.6 <u>Primary Propulsion Subsystems</u>

The orbiter primary propulsion subsystems may employ two separate sets of engines: the main engines for the final stage of boost and the orbit maneuvering subsystem for subsequent major thrust maneuvers. A reasonable construct for operation of either engine subsystem calls for a set of pre-ignition commands over a period of seconds to minutes, an engine-on signal maintained throughout thrusting, gimbal angle commands of indeterminate rate and quantization for both degrees of freedom, and a mixtureratio command. In the absence of data about a specific subsystem configuration, the estimates summarized in Table 8 were made for the design carrying least load on the computing system. These estimates assume that each engine may be gimbaled approximately 5° about each axis; quantization to 0.1° would be useful. A reasonable interface would allow for up to

# Table 8. Computational Requirements forPrimary Propulsion Subsystems

| Function       | Requirements                                   |

|----------------|------------------------------------------------|

| Gimbaling      | 4 axes: 10 bps/axis + 1 discrete               |

| Throttling     | 6 (air-breathing) engines: .? bps + 1 discrete |

| Start sequence | 1 command (discrete) with computer countdown   |

| Engine-on      | 1 command (discrete) with computer countdown   |

| Mixture ratio  | 2 (rocket) engines: 1 bps + 1 discrete         |

10 commands per second per axis, each incrementing or decrementing the gimbal angle by one count. Initiation of thrust may use two discretes (engine sequence start and thrust start), or it may require a sequence of discretes issued on a time base; the most difficult implementation would provide discretes triggered by measurements of propulsion parameters under computing system control. Measurement of propellant quantities and flow rates provides the data for computer determination of the desired mixture ratio; the increment/decrement discrete is required no more than once per second. Each incremental signal requires a discrete which causes the controller to drive to the reference (null) position.

#### 3.7 Reaction Control Subsystem

The reaction control subsystem employs 20 thrust chambers burning hydrogen and oxygen to generate relatively small torques and forces for attitude control and small velocity increments. If continuous thrusting is possible, the output of the computing system may be a discrete for each chamber (assuming hard-wiring rather than the use of the data bus). In that event, the signal is counted down with a tolerance of the order of 1 to 5 msec. If only a pulsed mode is available, the number of such pulses (up to perhaps 800 per second) must be transferred to the buffer in a local processor for each assembly. Two or three such items are required for each assembly, depending upon whether four or six thurst chambers are used.

Many configurations may be constructed in which computing system functions are assigned to local hardware and software. The above configuration does not allow for some modes of employing rate gyros, nor is it clearly the preferred type of interface for control surfaces in atmospheric flight. The specific mechanism by which a command signal actuates the reaction control subsystem was not clear, and is significant in determining the software requirements. A representative computing load might involve 20 thrust-on discretes, up to six active at once, and each counted down at 400 bits per second (may be synchronous).

# PRECEDING PAGE BLANK NOT FILMED

#### 4. COMPUTER CONFIGURATION

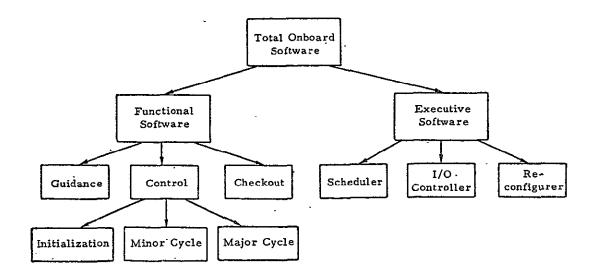

The Space Shuttle onboard software may be divided into two categories: functional and executive. The functional software performs the functions dictated by the requirements of the hardware subsystems and the mission objectives. The executive software controls and coordinates the execution of the functional software in accordance with overall system requirements.

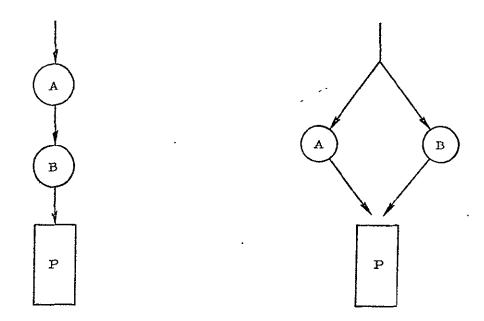

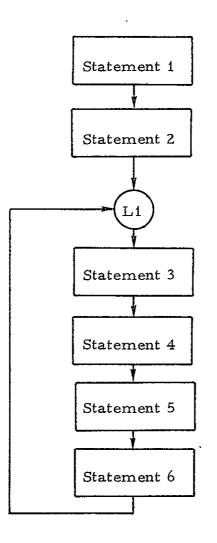

As shown in Figure 1, the functional software may be subdivided according to the functions to be performed, such as guidance, control, and checkout. Within these subdivisions it may be further categorized as to the specific computations to be performed, such as initialization and the computations performed at the minor and major cycle intervals. This final division of the functional software is made according to what will be called tasks; each task consisting of well defined computations to be performed at specified times or when specific criteria are satisfied. In general, each task will require some maximum time for execution.

Figure 1. Onboard Software Structure Outline

Executing the many tasks will require the sharing of computer resources such as the scratchpad memory and the input/output devices. The executive software will coordinate this sharing and control the resulting operations. Like the functional software, it may be divided into tasks, such as scheduing the functional tasks for execution, controlling and performing their input/output operations, and reconfiguring the computer system according to the computational load or the health of the computer hardware components.

The functional tasks can be designed, coded, checked out, and verified independently of the specific computer configuration, except for the ways which these tasks interact with the executive system. Development of the executive, on the other hand, is intimately tied to the computer configuration, both as regards: 1) the problems a particular configuration may present in performing the task-oriented executive operations, and 2) the special executive operations that the configuration might itself demand to be performed. Therefore, the tradeoff of alternative computer configurations was approached by studying the advantages and disadvantages of the executive software.

Three alternatives were examined to determine which, for the anticipated Space Shuttle functional requirements, would be the most suitable configuration from a software point of view:

- <u>Simplex Computer</u>: The simplex or single computer, by far the most common configuration for both aerospace and general-purpose applications, consists of a single arithmetic and control processor, a memory or a collection of memory banks, and an input/output processor or controller.

- <u>Multicomputer</u>: This configuration consists of two or more simplex computers, each having its own arithmetic and control processor and memory. The separate computers, which need not be identical, communicate with each other by means of their individual input/output provisions.

- <u>Multiprocessor</u>: This configuration consists of two or more arithmetic and control processors connected to a common memory such that, in general, any processor can execute any program or access data located anywhere in memory.

The simplex and multiprocessor configurations are inherently centralized organizations, both physically and logically; the central computer facility performs the computational functions required by the hardware subsystems,

similarly to the way a commercial data-processing center supplies computational services to its users. A multicomputer configuration can be physically and logically considered as either a centralized system or a decentralized (or federated) system, depending on the number of computers and how the computational capabilities are allocated. In a centralized system there would be relatively few computers, each servicing part of the hardware subsystems. In a federated system the computational functions would be allocated to the computers in more of a one-to-one manner, with the operation of these subsystem level computers under control of a master computer.

Among the software aspects relevant to the tradeoff between centralized and federated systems are the disciplines enforced in software production, the cost and difficulty of software production activities, the computational loads that can be supported with equivalent hardware complexity, and the protection that might be provided from software failures. These are discussed first, followed by a look at the functions to be performed by the executive, and next by preliminary executive designs for the three computer configurations. The section concludes with a summary of executive and computer configuration comparisons.

# 4.1 Centralization/Decentralization Considerations

The basic option available in the physical organization of the Space Shuttle data management system is that between centralization and distribution of the computing capacity. Neither extreme is probable: concentration of digital processing in a single central computer would overload the data bus, while some central functions (e.g., steering, mission control, reconfiguration) could not reasonably be allocated to a remote processor. Thus the requirement is to optimize the separation of functions into local and central processors under the mission and cost constraints. A complete tradeoff awaits a more complete functional analysis, and this itself awaits spacecraft design decisions. However, many important considerations are apparent at this time.

In the extreme represented by a fully centralized system, the computer is divided into processors whose number and usage are established by the instantaneous load. All data are fed over the data bus by analog/digital converters, with only minimal buffering to allow noninterfering, serial transmission. Fully resolved data are received at the subsystems, so that only format conversion is required to provide the stimuli needed for their checkout. The data rates associated with the fully centralized configuration would approach an order of magnitude increase over those attainable with more extensive local processing. That penalty increases not only the capacity required of the data bus, but also the input/output load on the central processor.

In the extreme represented by a fully federated system, all processing possible at the subsystem level is performed in dedicated processors located with the interfacing hardware; the central computer performs only the tasks involving the integration of data from several subsystems. A major advantage of such a design is the discipline it forces on defining the interfaces between software located at the subsystem level and the integrating software of the central computer. In addition, the powerful computing capability at the remote locations minimizes data rates and should save both cost and weight in the distribution system. However, the replication of routines among the local processors would be great, so that each would have to bear an overhead comparable to that of the entire centralized system. Memory and computation capacity would be committed to executive functions and to task programs and subroutines that are handled more efficiently in the centralized system. Furthermore, it is unlikely that the architectural characteristics of the smaller local processors would be conducive to easy programming. As a result, a considerable amount of software would have to be developed for hardware that is less than ideal from programming and verification points of view.

An essential computational function is the reduction of masses of data (e.g., accelerometer pulses, supply voltages) to significant information (e.g., steering commands, status displays). The partitioning of tasks to central and local processors is essentially a process of optimizing the allocation of data reduction to the different sites. The total data reduction load may be assumed to be independent of how it is allocated. Data compression, which represents an element of the filtering the system will be required to perform, would have to be executed either explicitly or implicitly in the central processor if local capability were omitted. Once such elementary capabilities as accumulation of accelerometer pulses are assumed in the local processors, there is a tendency to add others to reduce the load on the central unit.