## NASA CONTRACTOR REPORT

LOAN COPY: RETURN TO AFWL (DO 4L) KIRTLAND AFB, N. M.

## SPACEBORNE COMPUTER EXECUTIVE ROUTINE FUNCTIONAL DESIGN SPECIFICATION

Volume III. Executive Routine Primitives and Process Control

by James R. Kennedy, Sr.

Prepared by

COMPUTER SCIENCES CORPORATION

FIELD SERVICES DIVISION, AEROSPACE SYSTEMS CENTER

Huntsville, Ala. 35802

for George C. Marshall Space Flight Center

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION . WASHINGTON, D. C. . OCTOBER 1971

| 1. REPORT NO.                                                                                                                                                                                                                                          | TECHNIC                                                                                                                                                                          |                                                                                               | 161014                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------|

| 1. REPORT NO.<br>NASA CR—1869                                                                                                                                                                                                                          | 2. GOVERNMENT ACCESSION NO.                                                                                                                                                      | 3.                                                                                            |                           |

| 4. TITLE AND SUBTITLE                                                                                                                                                                                                                                  |                                                                                                                                                                                  | 5. REPORT DATE                                                                                |                           |

| Spaceborne Computer Executive                                                                                                                                                                                                                          | October 1                                                                                                                                                                        |                                                                                               |                           |

| Specification, Volume III. Exec                                                                                                                                                                                                                        | 6. PERFORMING OR                                                                                                                                                                 | GANIZATION CODE                                                                               |                           |

| and Process Control 7. AUTHOR(S)                                                                                                                                                                                                                       |                                                                                                                                                                                  | A PERFORMING ORG                                                                              | ANIZATION REPORT #        |

| James R. Kennedy, Sr.                                                                                                                                                                                                                                  |                                                                                                                                                                                  | 0                                                                                             |                           |

| 9. PERFORMING ORGANIZATION NAME AND ADD                                                                                                                                                                                                                | DRESS                                                                                                                                                                            | 10. WORK UNIT NO.                                                                             |                           |

| Computer Sciences Corporation                                                                                                                                                                                                                          |                                                                                                                                                                                  |                                                                                               |                           |

| Field Services Division, Aerosp                                                                                                                                                                                                                        | pace Systems Center                                                                                                                                                              | 11. CONTRACT OR G                                                                             | RANT NO.                  |

| 8300 South Whitesburg Drive                                                                                                                                                                                                                            |                                                                                                                                                                                  | NAS8-24930                                                                                    |                           |

| Huntsville, Alabama 35802                                                                                                                                                                                                                              |                                                                                                                                                                                  | 13. TYPE OF REPOR                                                                             | T & PERIOD COVERED        |

| 12. SPONSORING AGENCY NAME AND ADDRESS                                                                                                                                                                                                                 |                                                                                                                                                                                  | Contractor F                                                                                  | Report                    |

| National Aeronautics and Space                                                                                                                                                                                                                         | Administration                                                                                                                                                                   |                                                                                               |                           |

| Washington, D. C. 20546                                                                                                                                                                                                                                |                                                                                                                                                                                  | 14. SPONSORING AC                                                                             | SENCY CODE                |

| ,                                                                                                                                                                                                                                                      |                                                                                                                                                                                  | 14. SPORSORING A                                                                              | SENO! GOSE                |

| 15. SUPPLEMENTARY NOTES                                                                                                                                                                                                                                |                                                                                                                                                                                  |                                                                                               |                           |

| 16. ABSTRACT                                                                                                                                                                                                                                           |                                                                                                                                                                                  | · · · · · · · · · · · · · · · · · · ·                                                         |                           |

| Approaches for implementing the (the traditional approach) and display and control sequencing requires are shown. Software procedure depicted in an ALGOL-like sour approaches is made.  This document is Volume Computer Executive Routine Fundament: | gital hardware logic are detaile<br>nents are derived, and the assoc<br>is for performing a similar func-<br>ice program form. A brief com-<br>e III of a three-volume report en | d. Logic network ciated circuit diag tion are developed parison of the two ntitled "Spaceborn | grams<br>d and<br>o<br>ne |

| Volume I: Functional                                                                                                                                                                                                                                   | Design of a Flight Computer Example Shuttle                                                                                                                                      | ecutive Program                                                                               |                           |

| Volume II; Executive I                                                                                                                                                                                                                                 | Design for Space Station/Base                                                                                                                                                    |                                                                                               |                           |

| 17. KEY WORDS                                                                                                                                                                                                                                          | I 18. DISTRIBUTION S                                                                                                                                                             | TATEMENT                                                                                      | ,                         |

| Executive Routine Multipro                                                                                                                                                                                                                             |                                                                                                                                                                                  |                                                                                               |                           |

| _                                                                                                                                                                                                                                                      | gramming Unclassified =                                                                                                                                                          | OHIMITOGU                                                                                     |                           |

| Hardware Executive Scheduli                                                                                                                                                                                                                            |                                                                                                                                                                                  |                                                                                               |                           |

|                                                                                                                                                                                                                                                        |                                                                                                                                                                                  |                                                                                               |                           |

| Real Time Monitor Spacebox                                                                                                                                                                                                                             | rne Computer                                                                                                                                                                     |                                                                                               |                           |

|                                                                                                                                                                                                                                                        |                                                                                                                                                                                  |                                                                                               |                           |

| 19. SECURITY CLASSIF, (of this report)                                                                                                                                                                                                                 | 20. SECURITY CLASSIF. (of this page)                                                                                                                                             | 21. NO. OF PAGES                                                                              |                           |

| Unclassified                                                                                                                                                                                                                                           | <b>Unclassified</b>                                                                                                                                                              | 95                                                                                            | \$3.00                    |

### VOLUME III

## EXECUTIVE ROUTINE PRIMITIVES AND PROCESS CONTROL

### TABLE OF CONTENTS

| 4            |                               |     | Page |

|--------------|-------------------------------|-----|------|

| SECTION I.   | INTRODUCTION                  | • • | 3    |

|              | A. Concept of a Process       |     | 4    |

|              | B. Construction               | • • | 5    |

| SECTION II.  | PRIMITIVES                    |     | 9    |

|              | A. Wait                       |     | 9    |

|              | B. Continue                   |     | 9    |

|              | C. Wake                       |     | 10   |

|              | D. Stop                       |     | 10   |

|              | E. Suspend                    |     | 10   |

|              | F. Release                    |     | 11   |

|              | G. Termination                | • • | 12   |

| SECTION III. | PROCESS CONTROL STATES        |     | 13   |

|              | A. Compute Cycle              |     | 13   |

|              | B. The Work Variable          |     | 15   |

|              | C. Dispatching                |     | 17   |

|              | D. Cooperative Processes      |     | 18   |

|              | E. Suspended States           |     | 18   |

|              | F. Process Termination        |     | 20   |

|              | G. Example of Usage           |     | 22   |

| SECTION IV.  | IMPLEMENTATION                |     | 25   |

|              | A. Transition Matrix          |     | 25   |

|              | B. Control Variables          |     | 29   |

|              | C. Sum of Products            |     | 31   |

|              | D. Processor Control          |     | 34   |

|              | 1. Dispatcher                 |     | 34   |

|              | a. Ready List                 |     | 34   |

|              | b. Dispatcher Overview        |     | 35   |

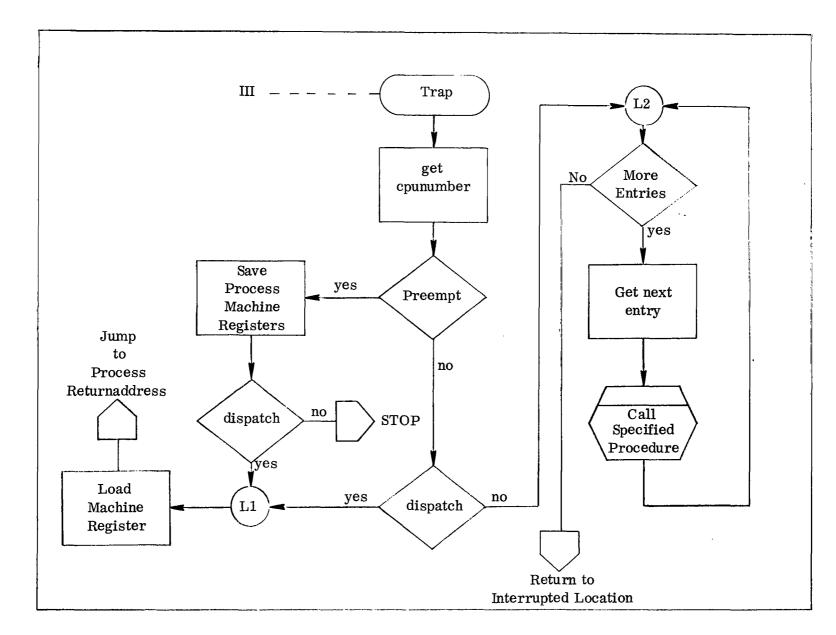

|              | 2. Trap Processing            |     | 37   |

|              | E. Hardware Implementation    |     | 41   |

|              | 1. Logic Network              |     | 43   |

|              | 2. Process Control Sequencing |     | 43   |

|              | F. Software Implementation    |     | 52   |

| SECTION V.   | MONITORING                    |     | 61   |

## VOLUME III

# EXECUTIVE ROUTINE PRIMITIVES AND PROCESS CONTROL

## TABLE OF CONTENTS (Continued)

|               |                                | Page |

|---------------|--------------------------------|------|

| SECTION VI.   | COMPARISONS                    | 65   |

| SECTION VII.  | CONCLUSIONS                    | 67   |

| SECTION VIII. | RECOMMENDATIONS                | 69   |

| A PPENDIX A   | LOGIC MAPS FOR PROCESS CONTROL | 71   |

| APPENDIX B    | PROCESS CONTROL FUNCTIONS      | 77   |

## LIST OF ILLUSTRATIONS

| Figure | Title                                                | Page  |

|--------|------------------------------------------------------|-------|

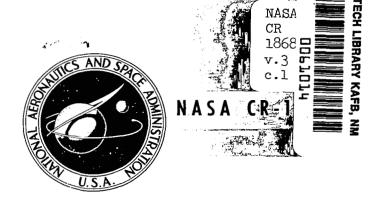

| 1      | Process Control Block                                | 6     |

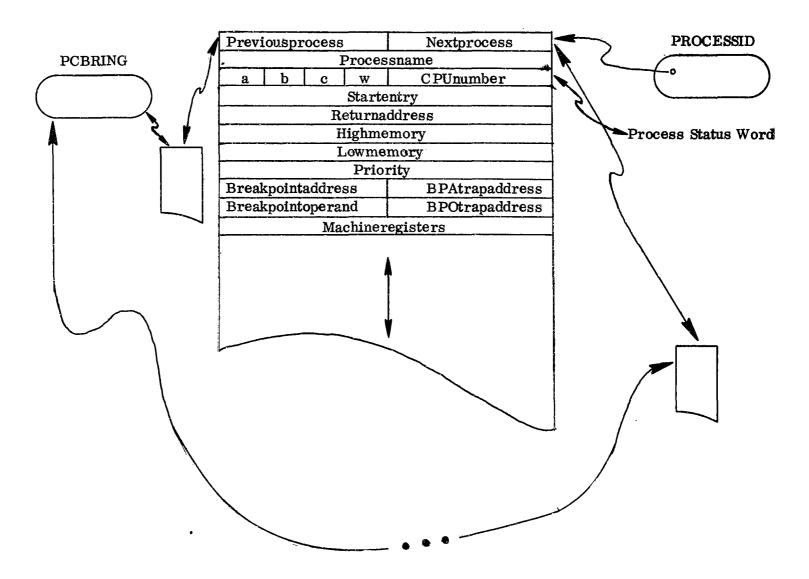

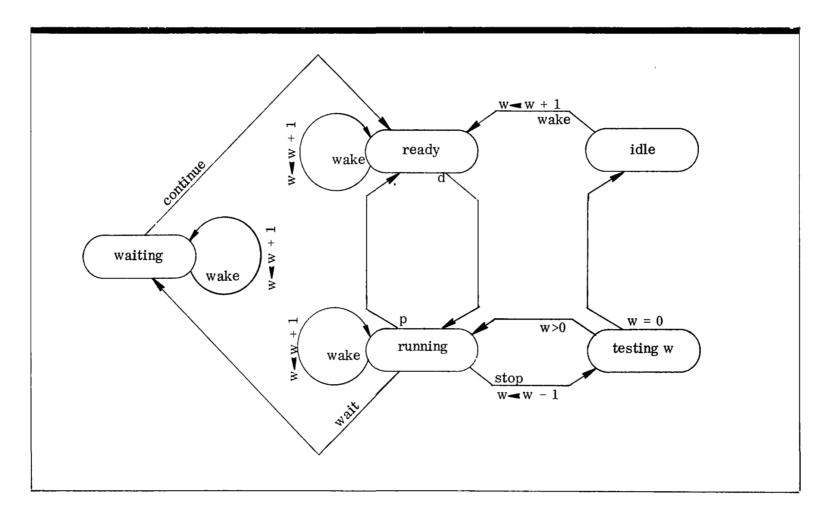

| 2      | Initial State Transitions                            | 14    |

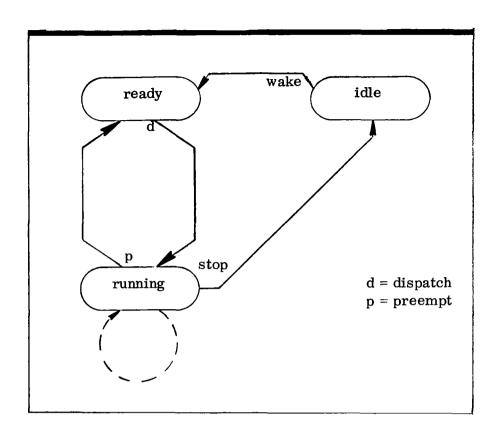

| 3      | Revised State Transitions                            | 16    |

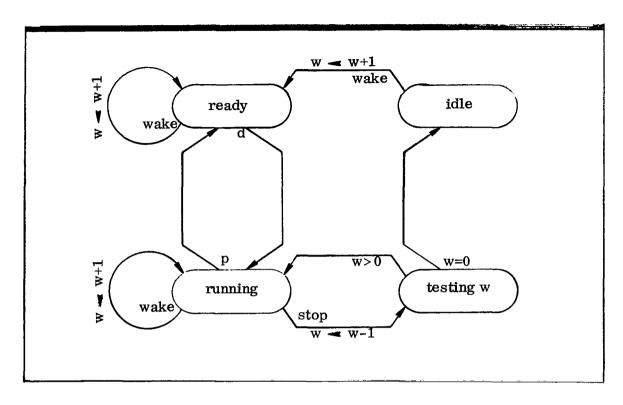

| 4      | Extended State Transitions                           | 19    |

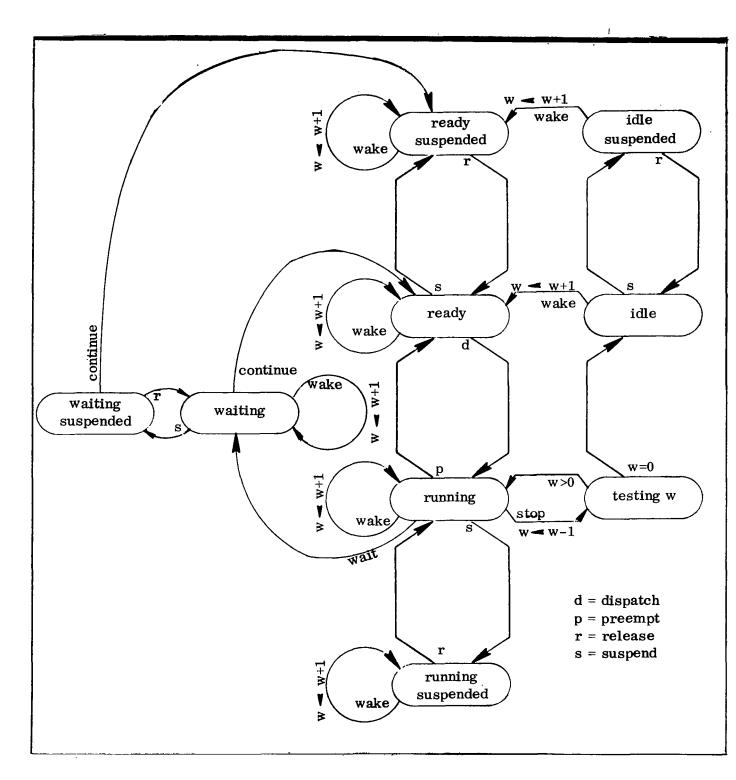

| 5      | Final State Transitions                              | 21    |

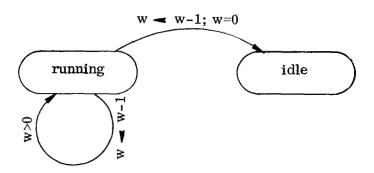

| 6      | Alternate Form for STOP Transition                   | 28    |

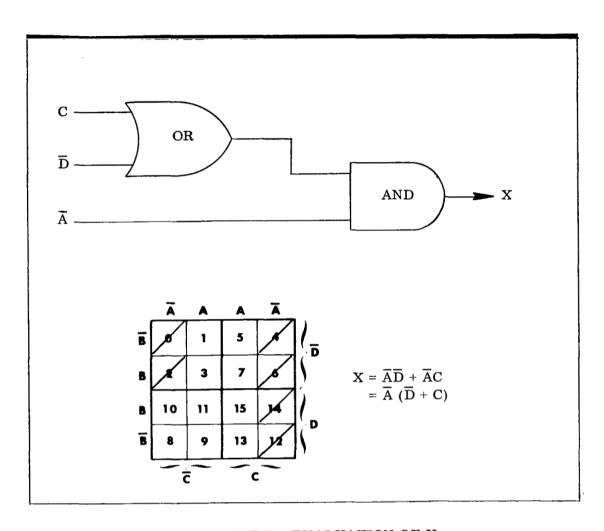

| 7      | Evaluation of X                                      | 33    |

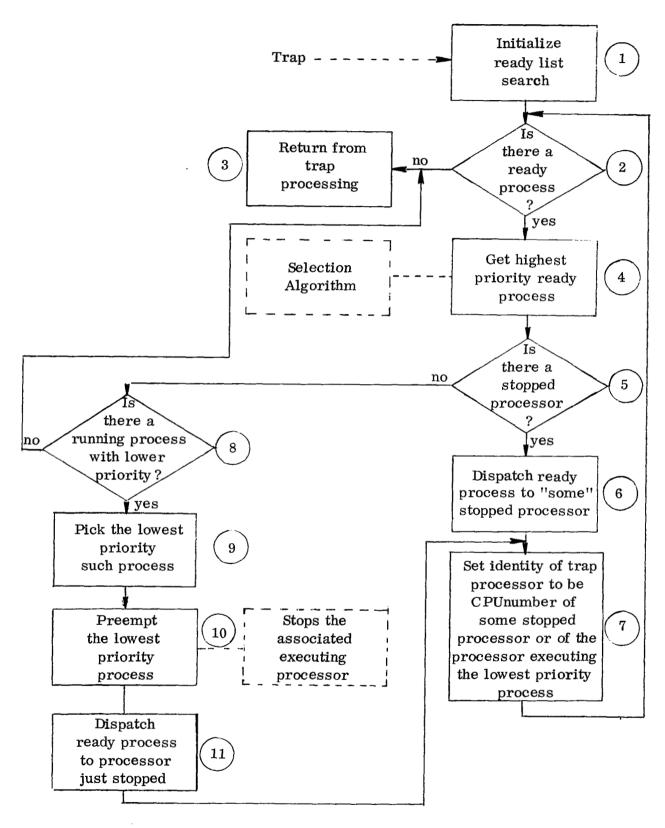

| 8      | Dispatcher Overview                                  | 36    |

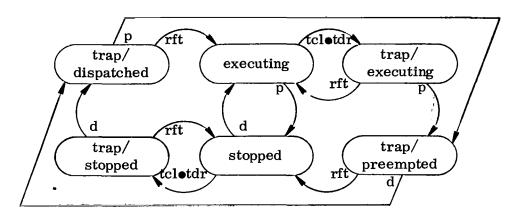

| 9      | Processor States                                     | 39    |

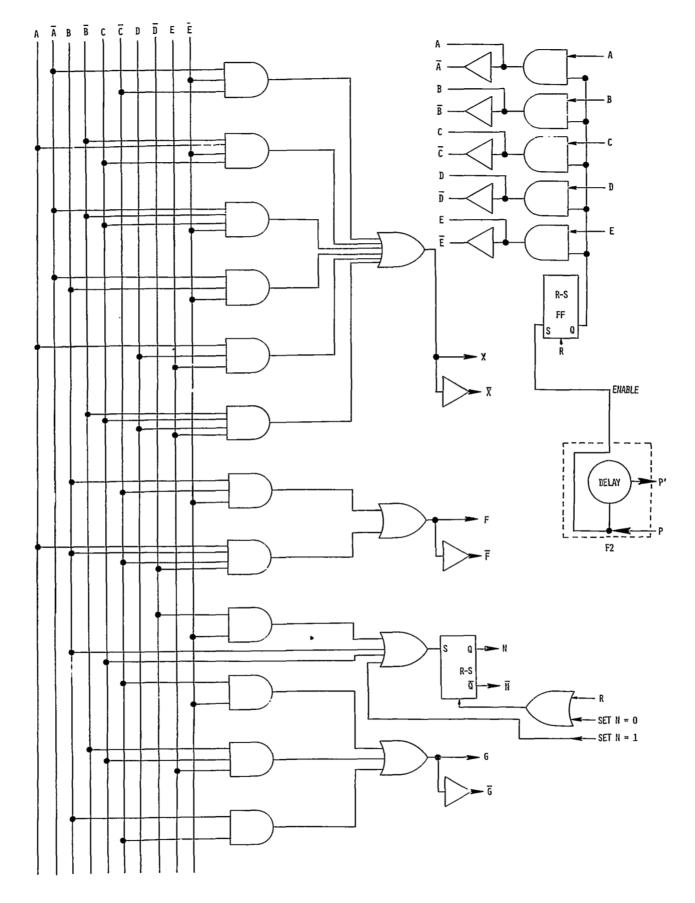

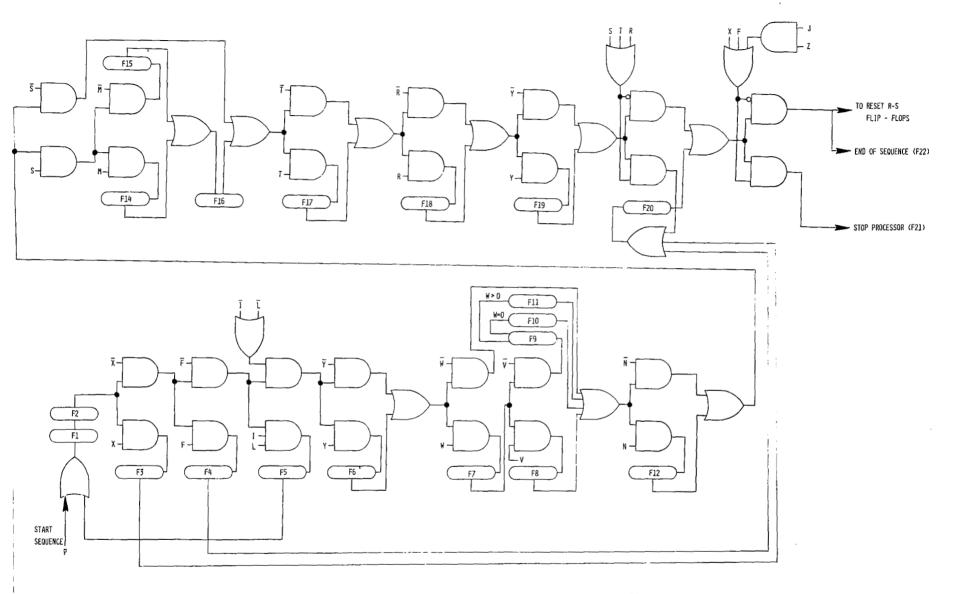

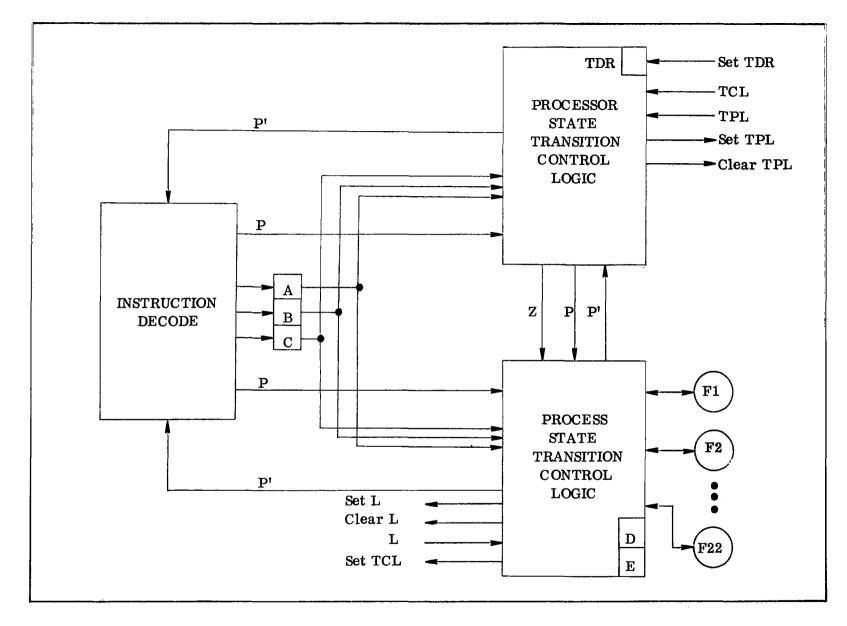

| 10     | Logic Network for Process Control                    | 47    |

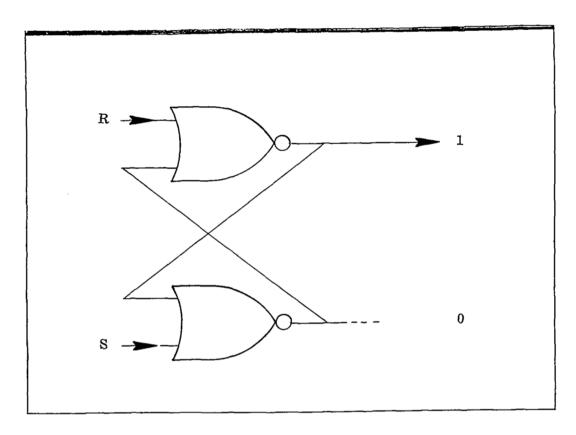

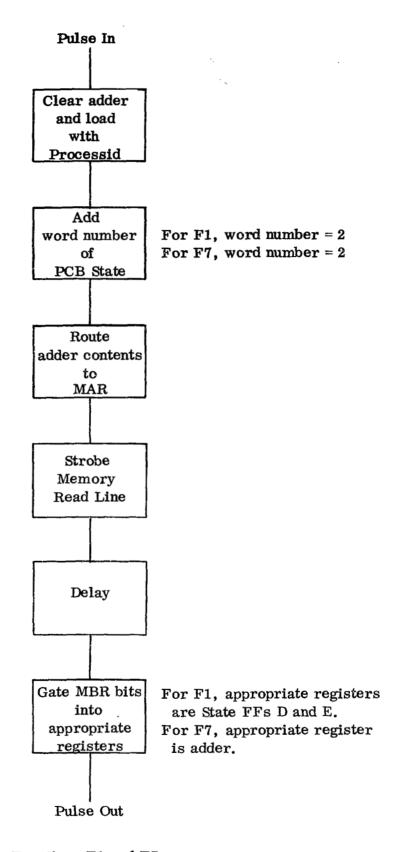

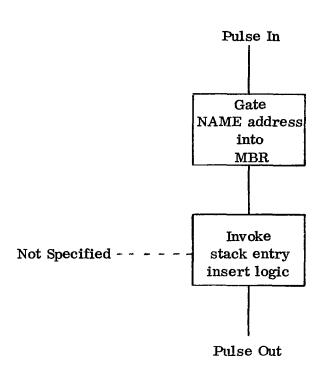

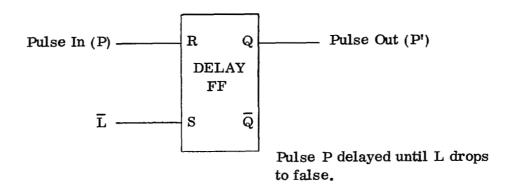

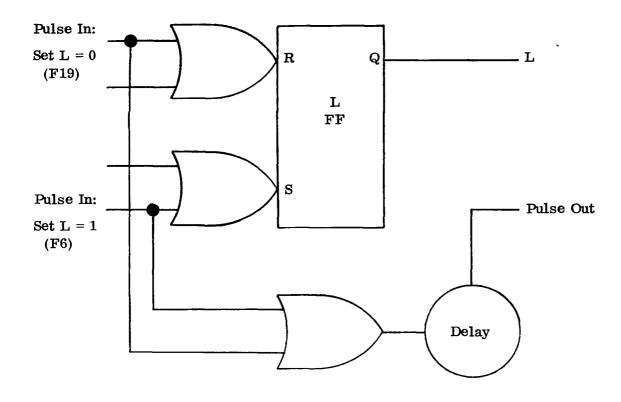

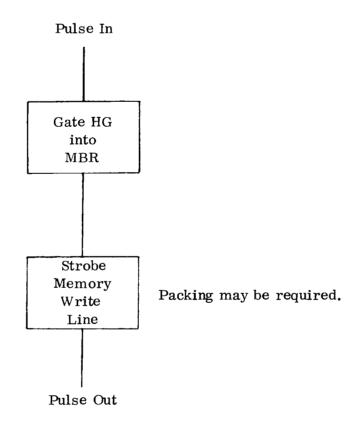

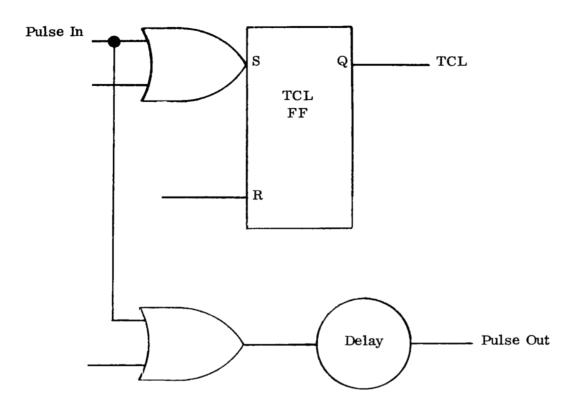

| 11     | R-S Flip-Flop                                        | 48    |

| 12     | Process Control Sequencing                           | 51    |

| 13     | Logic Overview                                       | 53    |

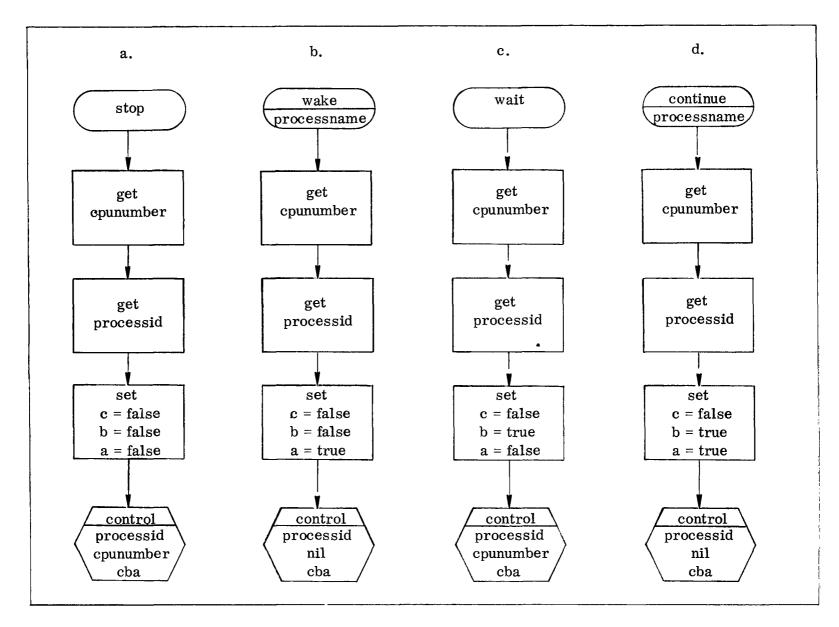

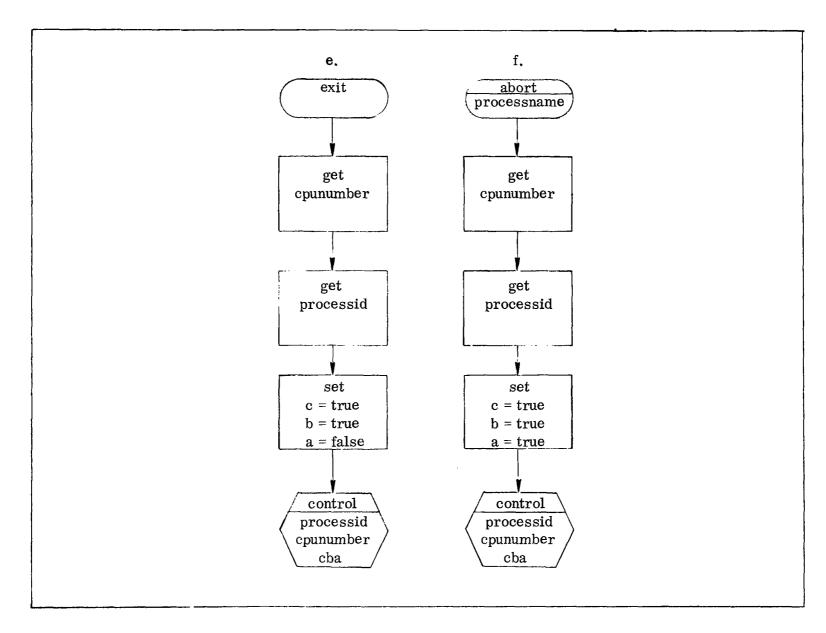

| 14     | Process Control Primitives                           | 56-57 |

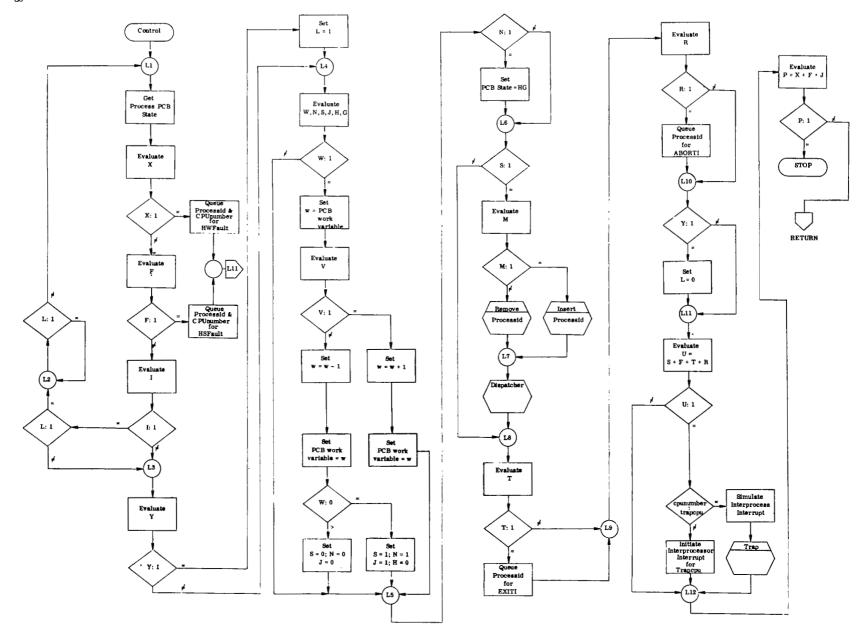

| 15     | Control Flow Diagram                                 | 58    |

| 16     | Interprocessor Interrupt Procedure (TRAP)            | 59    |

| 17     | Source Form Statement Listings for Process Control . | 60    |

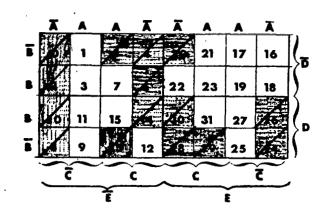

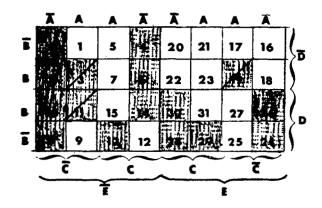

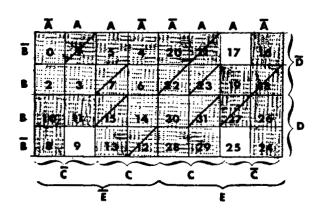

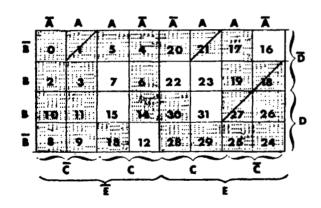

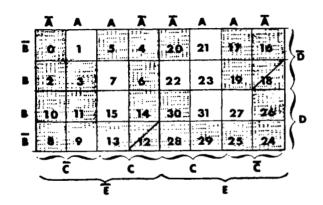

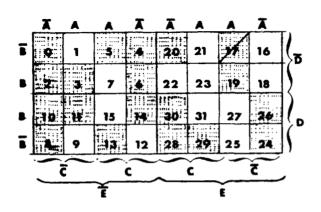

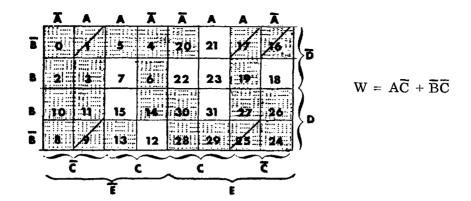

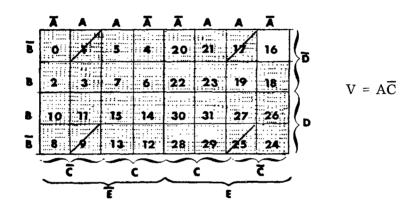

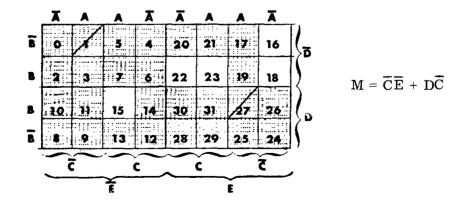

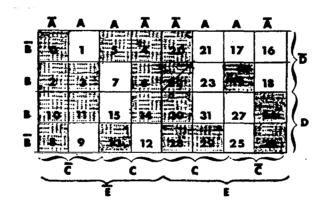

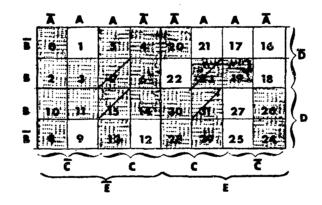

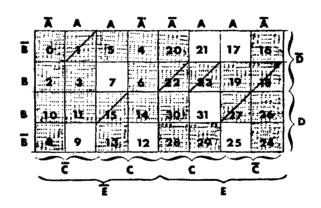

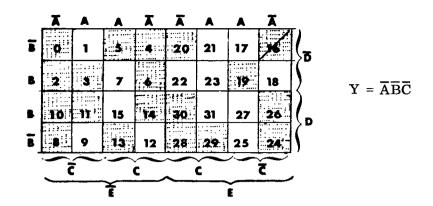

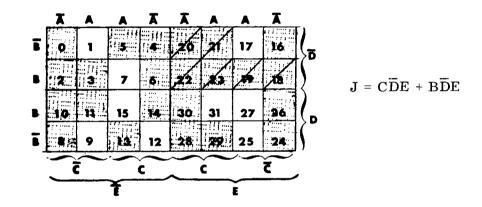

| A1     | Maps for Derivation of Boolean Expressions           | 72    |

| B1     | Process Control Functions                            | 78    |

## LIST OF TABLES

| Table | Title                                    | Page |

|-------|------------------------------------------|------|

| 1     | Process Control Block Entry Descriptions | 7    |

| 2     | State Transition Matrix                  | 26   |

| 3     | Work Variable Control                    | 27   |

| 4     | Example Standard Basis                   | 30   |

| 5     | Expanded Matrix                          | 42   |

| 6a    | Expanded Standard Basis                  | 44   |

| 6b    | Control Variables                        | 45   |

| 7     | Sum of Products Expressions              | 46   |

| 8     | Steps in Control Sequence                | 50   |

| 9     | Cost and Time Comparison                 | 65   |

#### DEFINITION OF SYMBOLS

AAIJ Allow all interrupts and jump. The jump in-

struction which transfers processor control to a process return address or entry point.

Backlog An amount of work which has been scheduled

but has not been completely processed.

Compute Cycle The complete transition cycle ("idle," "ready,"

"running").

III Initiate Interprocessor Interrupt. A computer

instruction used by one central processor, under executive control, to signal another central processor for the purpose of assigning

tasks.

LPS Load Processor State Register. The executive

instruction which enables the executive to set the state of a processor to insure system

protection.

LSR Load Storage Register. The executive instruc-

tion which sets the memory access boundaries

to those of a given process.

PCB Process Control Block

Preempt Dispatcher Action The act of seizing control of a processor from

a process for assignment to a higher priority

process.

Process The sequence of actions performed in order to

complete a task.

Process Construction The act of executing a set of procedures that

create a process.

State Diagram A representation for a finite state machine

that has inputs and outputs.

Task A specific quantity of work to be accomplished.

### DEFINITION OF SYMBOLS (Continued)

TCL Trap Control Line. Indicator denoting that a trap has occurred. Trap Designator Register. Indicator denoting TDR whether a processor is the trap processor or not. TDS Trap Designator Set TPLTrap Processing Line. Indicator to denote that trap processing is occurring. A list-driven processor capability activated Trap by the process control mechanism; a transfer of processor control to a specified location as a result of some event or condition requiring special attention.

#### **FOREWORD**

The work reported herein was administered in the Systems Research Branch, Computer Systems Division, Computation Laboratory, MSFC, with Bobby C. Hodges assigned as Contracting Officer's Representative. In addition to his routine duties as Technical Monitor, Mr. Hodges has added significantly to our insight into and understanding of related NASA programs through careful planning, coordination with in-house effort, and encouragement.

#### VOLUME III

## EXECUTIVE ROUTINE PRIMITIVES AND PROCESS CONTROL

#### **SUMMARY**

The feasibility of partitioning an executive routine into primitive controls, scheduling functions, and supporting supervisory software is shown. The report outlines an approach to a functional partitioning that lends itself well to automation.

Based upon general requirements for run-time support to arbitrary processes, a basic set of executive routine primitives is defined. Using an inductive approach, a state transition diagram is developed, thus forming the basis for the development of a finite state automata to control all processes. The state diagram is then used to derive a digital hardware logic device that provides the necessary sequential processing. A stacking mechanism is introduced to link the control hardware to certain software support procedures. The stack is processed through the use of a hardware trap scheme for executing procedures that have been stacked.

A software approach to mechanizing a comparable capability is developed. The method of depicting this approach is comprised of showing program flow diagrams and high-level source language statements. The architectural framework for specifying the software approach is taken to be the UNIVAC 1108 Multiprocessor System.

Finally a comparison of the two approaches shows that a hardware implementation is practical and displays significant advantages in terms of cost and system overhead. Although no explicit comparisons are given to contrast the two approaches with respect to weight, volume, reliability, and power consumption, the overwhelming simplicity of the hardware approach is felt to obviate the need for detailed comparisons. The results are clearly in support of a hardware logic design approach.

#### SECTION I. INTRODUCTION

The supervisory aspects of controlling program execution with a general purpose digital computer environment have become so complex that not only is it now difficult to implement scheduling procedures that have predictable effects, but it has also become difficult to establish design requirements and describe a control method that exhibits desirable features. This complexity is, of course, an inevitable result of a tendency to want more out of computing systems in terms of the total number of tasks completed in a given time interval. Since faster program development is also desirable, systems have been further complicated by the addition of functional responsibility in the area of development support through program debug, text edit, language translation, and file maintenance capabilities.

Relatively good success has resulted from recognizing that many functional responsibilities can be simplified through partitioning or segmentation into well defined and easily managed subfunctions. The purpose of this monography is to outline an approach to applying partitioning procedures to the supervisory function. The objective is to show simplicity in the methods involved, and to analyze and compare several possible methods for implementation.

The following discussion outlines the concept of a "process" as it relates to the computer executive function. Based on this concept, the important features of process "construction," "primitives," "control," "termination," and "monitoring" are discussed. Techniques for control implementation are examined, and examples of usage are cited. The discussion ends with concluding remarks and recommendations for further effort.

Implementation of the control concepts discussed in the report has historically been accomplished through the application of software engineering in order to design, fabricate, and test executive system programs that perform the required functions. Recent research and development has isolated program control principles that are reasonably general purpose, and necessary in all but the simplest sequential batch programming systems. The report expands on these principles, and emphasizes a digital logic approach to implementation; a software approach is also indicated.

To establish a frame of reference for the major points of interest that follow, the concept of a process and the meaning of construction of a process are outlined.

#### A. Concept of a Process

The usual quantity of work referred to in discussions regarding computer systems is the 'task.'' 'User tasks'' and 'system tasks'' have been accepted as terms for describing the entities that an executive system deals with in its supervisory capacity. A task will be similarly regarded in this discussion as a specific quantity of work to be accomplished.

Most of the discussion, however, will be concerned with the sequence of actions performed in order to complete a task. This sequence is referred to as a "process" and is discussed by Lampson /1/ and others /2/3/4/. It is important to note that a process may execute code from either system or user (application) programs, or both, in a more-or-less arbitrary order. Since the control devices of process-oriented systems may include those for stopping process execution, code which is shared among several (possibly concurrent) processes must be structured to support unsynchronized, multiple (simultaneous) execution instances. Such a program is often referred to as reentrant in that one execution instance can be suspended and another begun, both at (virtually) any location in the code. With a multiprocessor system, literal simultaneity is possible.

The definition of a "process" can be extended recursively by also considering a set of sequential processes to be a process. Such a definition would allow for (and require) a nested control capability. However, this discussion is concerned only with the simpler definition since no generality is lost.

<sup>&</sup>lt;sup>1</sup>Lampson, B. W.: A Scheduling Philosophy for Multiprocessor Systems. <u>Comm ACM</u>, V 11, N5, pp. 347-360, May, 1968.

<sup>&</sup>lt;sup>2</sup>Dijkstra, E. W.: The Structure of "THE" - Multiprogramming System. Comm ACM, V 11, N5, pp. 341-346, May, 1968.

Wirth, N.: On Multiprogramming, Machine Coding, and Computer Organization. Comm ACM, V 12, N9, pp. 489-498, September, 1969.

<sup>&</sup>lt;sup>4</sup>Hansen, P. B.: The Nucleus of a Multiprogramming System. Comm ACM, V 13, N4, pp. 238-250, April, 1970.

#### B. Construction

Process construction is the act of executing a set of procedures that create a process. In its broadest sense, process construction consists of program design and coding followed by translation to machine-executable code, collection into a module that is mapped onto main (instruction) memory, input to main memory, and creation and initialization of a block of main memory that constitutes a set of state variables for control of the process.

For purposes of this discussion, a truncated definition will be sufficient. It includes:

- Collection and mapping,

- Input to instruction memory, and

- Process control block formations.

Collection is a gathering together, from several sources, of the various uncollected routines constituting a set of process code. As the code is gathered, it is mapped one-for-one word-wise onto some contiguous set of instruction memory locations. Once collection and mapping has been accomplished, the code can be written into instruction memory and a process control block (PCB) constructed.

Figure 1 shows a possible structure for a typical PCB /5/ beginning at the ring pointer PCBRING. The contents of this block are for the most part self-explanatory; table 1 defines these entries. (In the event that multiple processors are allowed to concurrently execute common code from a given process, the entire process must be reentrant. The PCB structure shown will not support this requirement. Although it is certainly of academic interest, this possibility is not considered further here.)

<sup>&</sup>lt;sup>5</sup>The process control block discussed here is similar to the "Exchange Package" discussed in /6/ and the "Job Area" of /7/.

<sup>&</sup>lt;sup>6</sup>Reference Manual - Control Data 7600 "Preliminary Computer System," Control Data Corporation Publication Number 60258200, Revision 02, 1969.

<sup>&</sup>lt;sup>7</sup>Huberman, B. J.: Principles of Operation of the Venus Microprogram.

Mitre Technical Report MTR-1843, The Mitre Corporation, Bedford, Mass.,

1 May 1970.

FIGURE 1. PROCESS CONTROL BLOCK

TABLE 1. PROCESS CONTROL BLOCK ENTRY DESCRIPTIONS

| ENTRY             | DESCRIPTION                                                                                                                                                                                                    |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Previousprocess   | Pointer to the predecessor PCB on the ring.                                                                                                                                                                    |

| Nextprocess       | Pointer to the successor PCB on the ring.                                                                                                                                                                      |

| Processname       | Unique name for this process.                                                                                                                                                                                  |

| a b c             | Three bit process state indicator.                                                                                                                                                                             |

| Priority          | Relative process priority.                                                                                                                                                                                     |

| Startentry        | Instruction memory address of the first instruction.*                                                                                                                                                          |

| Returnaddress     | Instruction memory address of next instruction in case process activity is stopped; execution will be resumed at this location. Initially has the value of startentry.                                         |

| Highmemory        | Largest instruction memory address associated, for protection and access purposes, with this process.                                                                                                          |

| Lowmemory         | Smallest instruction memory address associated, for protection and access purposes, with this process.                                                                                                         |

| CPUnumber         | Hardware address of the processor unit associated, during execution, with this process.                                                                                                                        |

| Breakpointaddress | Instruction memory address which, if it becomes the argument of an instruction fetch cycle, will cause an internal processor trap to a predetermined instruction memory address specified by BPAtrapaddress.** |

| Breakpointoperand | Instruction memory address which, if it becomes the argument of a datum fetch cycle, will cause an internal processor trap to a predetermined instruction memory address specified by BPOtrapaddress.**        |

| Machineregisters• | A block of words reserved for saving all programmable processor registers when process activity is stopped. Must include all registers depicting process state information.                                    |

| w                 | Counter showing the number of unserviced WAKE primitives invoked for this process.                                                                                                                             |

<sup>\*</sup> The exact meaning of all main memory addresses is dependent on the details of hardware addressing. The preliminary organization shown here is merely representative. For instance, if data and instructions are separated a high and low data memory address would be required; if a paged memory is used, the page file map would be saved.

<sup>\*\*</sup>These values would have meaning only when the associated processor is operating in a debug mode.

At the time of construction, the values of a, b, and c, discussed in detail below, are all set to zero, as is the case with Returnaddress, CPUnumber, Breakpointaddress, and Machineregisters, while Startentry is stored in its designated space for the life of the process. It should be pointed out that no specific memory word size or processor register set is assumed; the organization of the PCB is, therefore, subject to optimization in a specific architectural case. Also, the storage area reserved for PCB's is assumed to be protected through definition of a set of privileged instructions (at least a "store-PCB" instruction).

#### SECTION II. PRIMITIVES

In order to accomplish control of processes, a set of primitive operators, or instructions, is defined. The exact effect of these primitives, when invoked by a process, is discussed in the next section; the general effect, however, is to alter the state of a process through specific executive system action. The states of all processes known to the system are kept current by recording these values as three bit binary numbers in the appropriate PCB's. The names used here for the primitives were chosen because of the intuitive thoughts evoked by them.

#### A. Wait

This primitive has no explicit arguments (parameters) associated with it. It is a command executed by a process when the process is executing and cannot proceed until some arbitrary, requested event has occurred. The effect of this primitive is to stop process action and thereby make the associated relinquished processor available for assignment to another process that is ready to proceed. The implied argument of this primitive is the "Processname" of the invoking process. Because no other arguments are recognized, it is not possible for process "A" to keep another process, "B," from proceeding by direct use of the WAIT primitive.

When execution of a process that has invoked a WAIT primitive is resumed, it will continue at the instruction immediately following the instruction sequence that invoked the WAIT. The address of this instruction is saved as Returnaddress in the appropriate PCB by the WAIT mechanism. The WAIT mechanism also saves all pertinent processor registers in the PCB and sets the values of a, b, and c to indicate that the process is in a "waiting" state. Other WAIT mechanism functions are discussed in the section on "Control."

#### B. Continue

When a process has placed itself in an inactive state through a WAIT, it can be resumed only by another (cooperative) process through use of a CONTINUE primitive. This primitive specifies the name of the waiting process as a parameter. The PCB for the specified process is located by use of its unique name (for instance, by searching a hash-coded table that associates a pointer, such as PROCESSID in figure 1, with the name); the process is then placed in a "ready" state wherein it may compete, on the basis of its relative priority, for assignment of a processor.

It is important to note that, prior to use of WAIT, every process must be assured that some cooperative process will invoke a CONTINUE in behalf of the waiting process. Normally, certain system support routines in the form of subroutines or supervisor calls would be provided to allow a process to request that it be continued for specific reasons. Examples might include completion of an input operation, expiration of a specified time interval, granting of a request for device assignment or storage allocation, etc.

#### C. Wake

After a process has been constructed, it is in the "idle" state. In this state, the process is prepared for execution but is not yet activated. The WAKE primitive is the mechanism for causing a specified idle process to be placed in the "ready" state where it will have processor time allocated for execution.

When a process is "idle" and a WAKE for it is invoked, the WAKE primitive will cause the process "startentry," stored in the PCB, to be copied into the returnaddress space in the PCB. The WAKE primitive specifies the object process name as an argument.

#### D. Stop

This primitive is invoked by a process that is in the "running" state in order to indicate to the system that it has completed its execution and wishes to return to the idle state. Once a STOP has been invoked, subsequent execution instances occur only as a result of WAKE primitives invoked for this process. Each such execution instance will begin at the process "startentry" saved in the PCB.

#### E. Suspend

This primitive and its converse, RELEASE, are defined to enable a process, "A," to stop and restart another process "B." This capability is provided primarily for the purpose of stopping a specified process to enable it to be examined intimately by some other process. From the point of view of the suspended process, there is no discernible effect; it therefore has no knowledge of having been suspended. While suspended, the process's data, instructions, and machine register contents can be examined or modified dynamically.

While the uses of SUSPEND are many, only debugging and synchronization are mentioned here. Several processes can be synchronized to the nearest instruction by breakpointing and suspending until all processes have been suspended. Then, upon release, they will be closely synchronized. In order to debug process code or analyze algorithm failures, it is necessary to suspend execution non-destructively to permit observation.

#### F. Release

The act of invoking a RELEASE primitive for a specified process will cause the process to revert back to the state it was in at the time of the most recent SUSPEND for the process (an exception is discussed below). For instance, if the process was executing code at the time of a SUSPEND, a cancelling RELEASE will cause it to continue execution where it was suspended.

#### G. Termination

The discussion has considered process construction and control. For completeness, primitive controls are specified to allow a process to terminate itself or for another process to cause its termination.

Self-termination can be accomplished by a process through an EXIT primitive, while termination of a process by an external mechanism is accomplished through an ABORT primitive. Processes that are aware of an internal anomaly may ABORT themselves also.

In effect, an EXIT will cause a process to be placed in the ''idle'' state, followed by release of main memory assigned for appropriate process code and PCB residence. An ABORT has all of the effects of an EXIT with additional capability for ''post-mortem'' main memory dumps and other terminal actions to aid in debugging.

|  |   | • |  |

|--|---|---|--|

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  | • |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

|  |   |   |  |

#### SECTION III. PROCESS CONTROL STATES

In this section, the use of system primitives is discussed through considerations with respect to state diagrams. Also, an alternate form for the state diagram is introduced in order to support the development of logic expressions for process control by an executive system.

Many of the details related to logic techniques are considered to be routine in the field of digital systems engineering. Similarly, many of the historically-"software" concepts are routine to the systems programming field. The (sometimes) tutorial nature of the discussions that follow has the major purpose of introducing readers in each field to the concepts and techniques of the other in order that more integrated systems will be appreciated.

The conventions used in the state diagrams developed here are standard in that arrows are used to show transitions; the name or symbol adjacent to the tail of each arrow is the identifier for the primitive, or input, which will cause the associated transition. Given a particular state, certain primitives may cause no state change. Also, certain primitives may not be valid. For instance, in the "ready" state, a WAIT primitive cannot occur. Such transitions as are nonvalid, or cause no state change or action, are not shown to avoid clutter.

#### A. Compute Cycle

A process enters the domain of the state diagram to be developed through process construction when the values of a, b, and c are set to zero in its PCB. For this reason, the discussion begins with state zero. The normal sequence of state transitions for a process is "idle"-"ready"-"running." This is shown in figure 2. A process in an "idle" state (state 000) will go to the "ready" state as a result of some other process having invoked a WAKE in behalf of the idle process. In the "ready" state, a process competes for processor time. An executive procedure, known as the "dispatcher," examines a queue of entries representing all processes in the ready state. Once the dispatcher determines a match between some process and processor, it will "dispatch" the process through a special system primitive which causes the processor to start execution of the appropriate process. The process is thereby placed in the "running" state. While a process is "running," it can invoke a STOP, thereby placing itself in the "idle" state again.

FIGURE 2. INITIAL STATE TRANSITIONS

The complete transition cycle ("idle," "ready," "running") will be referred to as a "compute" cycle. Many processes can be satisfied by simple, repeated loops through the compute cycle. Each time through the cycle,

- an idle process would be waked up by another process or the system,

- processor time would be allocated,

- the process would execute, and

- a STOP would be invoked to delay progress until the next compute cycle occurred or was needed.

#### B. The Work Variable

The diagram of figure 2, while satisfying many of the process control requirements, is nevertheless inadequate. For instance, it is possible that some event may occur causing a WAKE to be invoked while the affected process is in the running state. This is shown by the dotted transition in figure 2. In order to avoid the loss of such a WAKE, the state diagram is augmented to provide it with the ability to remember WAKEs that occur while a process is not in the "idle" state. This is accomplished through a state variable, "w," as shown in figure 3.

The scheme operates as follows: Each WAKE increases the value of 'w'' by 1 and each STOP decreases the value by 1. When a process invokes a STOP, a 'testing' state is entered wherein the value of 'w' is compared to zero. If 'w' is greater than zero, it means that some event requiring processing has occurred, and the process is returned to the running state at the start address to execute another pass through the compute cycle. If 'w' is zero, the process is placed in the 'idle' state as shown /8/.

The state variable, "w," is located in the PCB and can be initialized during process construction to any value. If it is initialized to zero, the normal compute cycle will occur as discussed above. If it is given a positive initial value of, say, n, the first n STOPs will loop through the testing state and back to the running state thereby effectively ignoring the first n STOPs. This is a useful capability that aids the programming of initialization for certain cyclic processes for the first (n) time(s) the process enters the running state. No consideration has been given in this report to possible uses of initializing "w" to a negative value; only non-negative values are treated properly in the state diagrams shown.

<sup>&</sup>lt;sup>8</sup>The interpretation of "w" as a semaphore /2/7/ is valid where STOP is similar to Dijkstra's "P" operator and WAKE is similar to "V."

FIGURE 3. REVISED STATE TRANSITIONS

The state variable, "w," has several useful side attractions that result from its role in the control diagram. First, the instantaneous value of "w" is a count of the number of WAKE primitives that have not been "serviced" through dispatching and subsequent processing. In the special case where, as a result of cooperative process action, a process is "waked up" periodically, say every 10 milliseconds, to perform some calculation, the value of "w" can be measured by the system to determine whether the calculations are lagging behind. If, because of a low relative priority, the waked-up process is not dispatched before the next WAKE, the "w" can be used as a direct measure of how far behind the process is. "w" will be referred to as the process "work variable" because of the apparently close relation to system workload.

#### C. Dispatching

Returning to the state diagram of figure 3, it is seen that a process in the "running" state can have its processor seized by the dispatcher for assignment to a higher priority process. This is known as a "preempt" dispatcher action. It causes the preempted process to be returned to the "ready" state to await a future "dispatch" primitive that will allow it to proceed. "Preempt" and "dispatch" are special system primitives that can be invoked only by the dispatcher which, as part of the process control mechanism, has privileged access to the necessary control devices to assign processor time to a process.

Extending the discussion farther, it seems clear that the dispatcher might be designed to dispatch processes with higher "w" values first, all other factors (such as priority) being the same. If "w" is interpreted as a measure of work scheduled for a process, then the sum of all "w" values over all processes known to the control system can be thought of as an indication of the total scheduled work for the system at any given time. With this interpretation, the "system work-load" can be measured as a function of "w."

In a "closed" system - such as certain industrial process control, message switching, avionics, ballistic missile defense, air traffic control, airline reservation, and other similar real-time systems - it would seem to be useful to sample 'w" dynamically. Analytical techniques applied to probability distributions of sampled "w" values might then be used to develop feedback scheduling and dispatching algorithms to dynamically optimize system performance under varying workloads.

#### D. Cooperative Processes

We have thus far developed a scheme that shows the relation between WAKE and STOP through the introduction of the concept of a compute cycle and the process work variable, "w." This scheme is particularly applicable in the case of cyclic or repetitive processes such as those found in all computer controlled real-time systems. It is necessary to incorporate an additional pair of primitives to support control of a process that is "waiting" for some requested event to occur before it can proceed.

Consider the case of a request for data input. Unless the data are already buffered in main memory at the time of the request, it would be necessary in most cases to queue the request and place the requestor in a waiting state until the data have been input and converted for use. A similar situation arises in the case of requests for main memory space, peripheral devices, timed delays, etc.

Figure 4 depicts a "waiting" state which is entered by a process that invokes the WAIT primitive. When the condition necessitating a WAIT has been eliminated, the process is placed in the ready state through the use of the CONTINUE primitive. When the dispatcher assigns a processor, control resumes at the "returnaddress" saved in the PCB by the WAIT mechanism.

It is interesting to consider what would happen if an 'unauthorized'' CONTINUE were invoked as a result of either a hardware or software error. The waiting process would, upon entering the running state, assume erroneously that the request had been granted and proceed to cause a further promulgation of the original failure – possibly beyond the point of recovery if this point had not already been reached.

One way of preventing such a CONTINUE would be to build into the WAIT mechanism a procedure for generating a unique "key." This key would be made available to the procedure authorized to invoke the corresponding valid CONTINUE. Then, whenever a CONTINUE is invoked, the key supplied by the invoker would be matched to the unique key generated at the time of the WAIT. Mismatches would determine program errors or system failures. The details of this form of validity checking will not be considered further in this report, but they certainly form the basis for further examination and definition.

#### E. Suspended States

The final alteration to the state diagram is an extension of figure 4 to include optional "suspended" states. The suspended states are companions to corresponding nonsuspended ("waiting," "ready," "idle," and "running") states and are provided as a mechanism for stopping the progress of a process. The

FIGURE 4. EXTENDED STATE TRANSITIONS

effect of a WAKE and CONTINUE primitive is preserved through an appropriate transition from 'idle suspended' and 'waiting suspended' to 'ready suspended.' Figure 5 shows the complete state diagram.

Suspended states can be associated with a special mode of processor operation which will support extensive observation by external processes of processing activity. This mode might be referred to as the "debug" mode. Figure 5 shows process state changes with regard to certain debugging primitives, namely "suspend" and "release," Other debugging primitives that influence processor states, but are unknown to processes, can be defined to enable the specification of a comprehensive automatic debug program as part of an executive. These concepts are properly discussed elsewhere. For the purposes of the present discussion, "suspend" can be considered to be equivalent to the (manual) depression of a console "stop" button in a single processor configuration; "release" is equivalent to a "go" button depression. In a multiprocessor configuration, the concepts assume more meaning in that actions equivalent to "stop" and "go" can be carried out under program control on one processor to "suspend" and 'release' a process executing on another processor. As was mentioned before, these primitives will have meaning only when the affected processor is operating in the debug mode. While in this mode, special logic sequences can be invoked to accomplish single-step and phase-step processor operation, register content readout and alteration, breakpointing, etc. The associated fully-integrated processor/process capabilities are not discussed here.

#### F. Process Termination

The diagram of figure 4 contains the essential ingredients of process control and will be the basis for discussion in subsequent sections. However, it does not include the two termination states into which EXIT and ABORT take a process. The reason for not showing the termination states is that they overcomplicate the diagrams and add little to the concept. EXIT and ABORT are considered, however, in the implementation schemes to be developed.

EXIT can be invoked only by a process in the running state in its own behalf. The primitive will place the process in the "unload" state and activate a system unload procedure to return all of the resources allocated to the process. In addition, all incomplete activities, such as input and output, initiated by the process will be completed by the system. An ABORT will cause the specified process to be placed in the "post-mortem" state and will activate a system abort procedure. This procedure will perform various debug functions such as dumping main memory at machine registers. Upon completion, the abort procedure will invoke an EXIT, thus causing the process to be unloaded.

FIGURE 5. FINAL STATE TRANSITIONS

#### G. Example of Usage

Before proceeding with a discussion of implementation concepts, a specific programming example is offered to show the use of WAIT and CONTINUE. Shown below is an "intuitive-ALGOL" source-form listing of two cooperative procedures. One, named "free," is intended to illustrate a procedure for finding and allocating to the caller a block of contiguous main-memory words. It is a function that returns the address of the block to the caller; the caller specifies the size of the requested block as a formal parameter. "Putback" provides the means whereby a caller may return a previously allocated block to the system. In this way, blocks which are no longer needed by the caller are made available for allocation to future callers of "free."

```

procedure free(request. size)

if another. block

look:

then begin

look.at.size;

if too. small then go to look;

remove(block.address);

if too. big then insert. block(excess. block. address, excess. size);

found:

free:=block.address:

return. to. caller

end

else begin

queue(request. size, processid, caller. return);

get(block.address, caller.return);

go to found

end;

procedure putback(block.address, block.size)

if more, queued, requests

scan:

then begin

if this. queued. request. size block. size then go to scan;

dequeue(this. queued. request);

fix. block(block, address);

fix. size(block. size)

continue(processid);

if block. size = 0 then return. to. caller;

go to scan

end;

insert.block(block.address, blocksize);

return.to.caller;

```

"Free" is an algorithm that locates a block by looking through a list or map of available storage blocks until one large enough to satisfy the caller's request is found. When one is located, it may be too big, in which case the excess sub-block is placed back in the map by a call to "insert-block." In case no available block is large enough to satisfy the caller's request, the size of the requested block, along with the caller return address and a pointer to the caller's PCB, is queued to allow the system to proceed. Until the request can be satisfied, the process remains in the waiting state.

"Putback" has the job of updating the map which specifies available storage so that "free" is made aware of the returned space. "Putback" first scans the queue of requests to determine whether the block being returned will satisfy some waiting request. If a request can be satisfied, the waiting process is CONTINUED. "Putback" continues to scan the queued requests until there are no more requests to check, or all of the returned space has been used to satisfy queued requests. When scanning is complete, the remaining space is inserted in the storage map.

Several interesting points can be derived from the example. The most important is the implication that, in a multiprocessor system wherein the example code can be shared among several processors simultaneously, the code must be reentrant. The code of "free," for example, represents part of the mechanization of all processes having queued requests. This is an important example of code and data sharing.

The reentrant coding requirement could be eliminated by provision of duplicates of the code as part of the mechanization of every process. Since the algorithm is likely to be rather complicated due to "garbage collection" and memory map characteristics, the cost in storage space would probably be accessible to (shared by) all processes. This requires some form processor lockout capability such as "Test and Set" /1/9/. This same lockout capability could be used to obviate the need for multiple copies of man-reentrant code but would require special attention to process coding. Reentrant code combined with Test and Set applied to the global data is preferable.

<sup>&</sup>lt;sup>9</sup>Blakeney, G. R., Cudney, L. F., and Eickhorn, C. R.: An Application-Oriented Multiprocessing System - Design Characteristics of the 9020 System. IBM Systems Journal, V6, N2, pp. 88, 1967.

|            |  |  |  | 1 |

|------------|--|--|--|---|

|            |  |  |  |   |

|            |  |  |  |   |

|            |  |  |  |   |

|            |  |  |  |   |

|            |  |  |  |   |

|            |  |  |  |   |

|            |  |  |  |   |

|            |  |  |  |   |

|            |  |  |  |   |

|            |  |  |  |   |

|            |  |  |  |   |

|            |  |  |  |   |

|            |  |  |  |   |

|            |  |  |  |   |

|            |  |  |  |   |

|            |  |  |  |   |

|            |  |  |  |   |

|            |  |  |  |   |

|            |  |  |  |   |

|            |  |  |  |   |

|            |  |  |  |   |

|            |  |  |  |   |

|            |  |  |  |   |

| , <u>.</u> |  |  |  | 1 |

#### SECTION IV. IMPLEMENTATION

This section outlines an implementation of the concepts of process control discussed previously. Two design approaches are developed for comparison purposes. The first is comprised of a combination of hardware and software; the emphasis is on digital logic. The second is predominantly software. While the hardware design is comprised of digital logic, and the software is depicted as a high-level language, it is important to realize that stored logic could replace any (or all) of the implementation media. This fact confirms the observation that there are no longer well-defined demarcations in the selection of implementation media for executive control. Such selections must be based on appropriate trade studies that include preliminary designs such as those discussed below.

Before depicting the actual implementation, it is necessary to discuss some concepts and techniques of general use as digital design aids. The applicability of transition matrices and the evaluation of control variables is outlined briefly to support the design rationale that follows.

#### A. Transition Matrix

The information shown in a state diagram can be represented in other forms that are often more compact. For the purposes of further discussion, an example is shown in table 2. This matrix depicts the important state transition aspects of the figure 4 state diagram with the exception of "d" and "p." (All future references to state diagrams developed in this report will imply that of figure 4 unless specifically indicated otherwise.) A state diagram is considered to be /10/11/ a representation for a finite state machine that has inputs, represented in these discussions by the primitives, and outputs, represented in report examples by increasing, decreasing, or doing nothing to the work variable. Table 3 shows an output matrix that could be used to control the value of "w."

<sup>10 -:</sup> Minsky, M.: Computation: Finite and Infinite Machines. pp. 21, Prentice-Hall, Inc., Englewood Cliffs, N. J., 1967.

<sup>-:</sup> Chu, Y.: Digital Computer Design Fundamentals. pp. 375, McGraw-Hill Book Company, Inc., New York, N. Y., 1962.

TABLE 2. STATE TRANSITION MATRIX

|           | State | Idle            | Ready | Running         | Waiting |

|-----------|-------|-----------------|-------|-----------------|---------|

|           | DC    | 00              | 01    | 10              | 11      |

| Primitive | BA    |                 |       |                 |         |

| STOP      | 00    | X               | X     | Y               | X       |

| WAKE      | 01    | 01 <sup>•</sup> | 01    | 10              | 11      |

| WAIT      | 10    | X               | X     | 11 <sup>•</sup> | X       |

| CONTINUE  | 11    | F               | F     | $\mathbf{F}$    | 01      |

- F Should not happen. (Could be used to flag software/hardware error.)

- X Cannot logically happen. (Could be used to flag hardware error.)

- Indicates state change.

- Y Final state depends on w.

TABLE 3. WORK VARIABLE CONTROL

|           | State | Idle | Ready | Running | Waiting |

|-----------|-------|------|-------|---------|---------|

|           | DC    | 00   | 01    | 10      | 11      |

| Primitive | ВА    |      |       |         |         |

| STOP      | 00    | X    | Х     | -1      | Х       |

| WAKE      | 01    | +1   | +1    | +1      | +1      |

| WAIT      | 10    | Х    | X     | 0       | X       |

| CONTINUE  | -11   | F    | F     | F       | 0       |

# Matrix element values:

- -1 Implies decrement w.

- 0 Implies no change in w.

- +1 Implies increment w.

- X,F Same as in previous figure.

The "Testing w" state, in effect, does not exist as far as processes are concerned; it acts like a pseudo, or "transient," state in that while the machine is in this state, it is merely in the process of deciding, on the basis of "w," whether the required transition should be "10"-to-"10" or "10"-to-"00." When a STOP is invoked (in the running state), w will be decremented and tested immediately to determine which transition to make. This could have been indicated in the state diagram as shown in the illustration below.

FIGURE 6. ALTERNATE FORM FOR STOP TRANSITION

WAKE is the only valid primitive that could conceivably be invoked while a process is in the "Testing w" state. There are several alternatives to controlling this situation. The simplest way would be to have an access lock placed on the value of w until it has been tested. After the proper transition has been made, the access lock would be removed. The only drawback to this scheme occurs in those cases where the process is placed in the idle state, only to have its state changed immediately to "ready" thus causing a large amount of work to be required to place it back in the running state. This problem arises only in a multiprocessor/multiprogramming environment, of course.

An alternative to the above scheme would be for each machine to set a control line indicating that it is executing a process in the "Testing w" state. All other process control machines would sense this line and delay further processing until the line is reset. For the particular conflict we are considering, this alternative has the advantage that no value access lock mechanism is required, the control line accomplishing the necessary control. However, the disadvantage of the first scheme is still inherent. This report will assume the second scheme although it is not necessarily best, and there may be other schemes. The "Y" shown in table 2 could be used to indicate that the "Testing w" control line should be set.

The "X's," shown as elements of both matrices, indicate combinations of input and state which are not valid by definition. These combinations would not normally go unrecognized, however, because of their value in detecting errors in a logic circuit designed to function like the finite machine. For this reason, a second output matrix might be constructed to control the detection of this class of error (caused by an input [e.g., primitive] or the machine [e.g., state] itself).

An "F" is used as an element to indicate those combinations which, although they could occur, would indicate another (possibly different from the "X") type of error. The relation between WAIT and CONTINUE is one which would be prohibited, by programming standards, from existing between more than one pair of processes or procedures at any given instance. Another, perhaps more precise, way of looking at this is to state that every WAIT has one and only one logically valid, matching CONTINUE. Also, every CONTINUE will always "unlock" (match) one and only one waiting process. An error would occur if some unauthorized process invoked a CONTINUE when, in fact, either the object (process) of the CONTINUE is not waiting or the event being waited upon has not occurred. The "F" indicator will flag the first of these two possible mismatches; a key of some sort would be required, as discussed previously, to flag the second.

### B. Control Variables

In order to develop a valid logic device to represent the finite machine of the process control state diagram, it is necessary to define several output variables, each having an appropriate output matrix to define the variable values. The form shown in tables 2 and 3 is awkward for space reasons and a tabular form, sometimes called a "standard basis" /12/ truth table, is preferred. Table 4 is a standard basis for representing all combinations of A, B, C and D (from the transition matrix) in the first four rows. The column numbers at the top indicate the sixteen possible elements of the matrix of table 2. Although it may be confusing, these numbers are referred to, in conformance with generally accepted policy, as "state numbers." Thus, state 5 represents the occurrence of the WAKE primitive (B = 0, A = 1) when a process is "ready" (D = 0, C = 1).

<sup>12-:</sup> Digital Systems Engineering: pp. 1.28, Lecture Notes, 5th Edition, RCA Institutes, Clark, N. J., 1965.

TABLE 4. EXAMPLE STANDARD BASIS

| VARIABLE |                    | ST                                                    | ATE                |                                               |

|----------|--------------------|-------------------------------------------------------|--------------------|-----------------------------------------------|

|          | 0 0 0 0<br>0 1 2 3 | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | 0 0 1 1<br>8 9 0 1 | $\begin{array}{c}1&1&1&1\\2&3&4&5\end{array}$ |

|          | 0 1 2 0            | ± 0 0 7                                               | 0 0 0 1            | 2 3 4 5                                       |

| A        | 0 1 0 1            | $0\ 1\ 0\ 1$                                          | $0\ 1\ 0\ 1$       | 0 1 0 1                                       |

| В        | 0 0 1 1            | $0\ 0\ 1\ 1$                                          | 0 0 1 1            | 0 0 1 1                                       |

| C        | 0 0 0 0            | 1 1 1 1                                               | 0 0 0 0            | 1111                                          |

| D        | 0 0 0 0            | 0 0 0 0                                               | 1111               | 1111                                          |

|          |                    |                                                       |                    |                                               |

| X        | 1010               | 1 0 1 0                                               | 0 0 0 0            | 1 0 1 0                                       |

| F        | - 0 - 1            | - 0 - 1                                               | 0 0 0 1            | - 0 - 0                                       |

| N        | - 1                | - 0                                                   | a 0 1 -            | - 0 - 1                                       |

| G        | - 1 <b>-</b> -     |                                                       | 0 - 1 -            | - <b>-</b> - 1                                |

| Н        | - 0                |                                                       | b - 1 -            | <b>-</b> - 0                                  |

| Y        | - 0                | - 0                                                   | 1 0 0 -            | - 0 - 0                                       |

| w        | - 1                | - 1                                                   | 1 1 0 -            | - 1                                           |

| V        | - 1                | - 1                                                   | 0 1                | - 1                                           |

- X: Invalid flag hardware error.

- F: Illogical flag hardware/software error.

- N: State change (• in transition matrix).

- G: New C when N = 1.

- H: New D when N = 1.

- Y: Indicates entering Testing w. Set appropriate control line.

- W: Change value of w (Test and Set could be used to gain access).

- V: Increment (=1) or decrement (=0) value when W=1.

- -: Don't care.

Note: "a" is a 1 if and only if W = 0 when tested.

"b" is a 0 if and only if W = 0 when tested.

Each row below the top four represents an output variable whose possible (Boolean) values are shown at the intersections with the different states (columns). The X condition defined in the transition matrix and discussed above is an example of a condition that must be detected. Therefore, X is defined as an output variable whose value will be "1" (Boolean True) for those combinations of A, B, C and D which are invalid; i.e., cannot logically happen. Therefore, a "1" is placed at the intersection of the X row with states 0, 2, 4, 6, 12 and 14. All other state numbers are valid; X is therefore "0" (Boolean False) for these states.

Notice that for some state-number/row-value intersections in the standard basis, a "-" is shown. If a logic circuit is developed to provide values for all of the output variables, and the value provided for X turns out to be "1," the values of all other output variables are useless since some error has occurred. For this reason, "-" is used to indicate a "don't care" value for certain variables at certain state numbers. Furthermore, if a don't-care condition exists for a particular variable, it does not matter whether the logic circuit produces a "0" or a "1" for that variable in that condition. It is common practice in digital design to take advantage of don't-care conditions in order to minimize or simplify the overall logic circuitry. Simplification often occurs when a specific circuit is intentionally designed to produce, say, a "1" for certain don't-care state numbers.

#### C. Sum of Products

A simple procedure is available for the derivation of equations to evaluate the various output variables for all combinations of inputs. Referring to the standard basis, it is clear that X must be "1" when A, B, C and D are "0," A, C and D are "0" and B is "1," etc. It must be "0" for all other combinations.

Taking state 0 first, it is clear that if the False ("0") A, B, C and D values are negated and "ANDed" (logical product) together, the logical result is "1" (True). State 1 can result in a "1" if the False values of B, C and D are negated and ANDed together with the True value of A. State 3 suggests ANDing a negated C and D together with A and B, and so on. The input standard basis thus provides an indicator for obtaining the desired logical values for all output variables.

The logical entities thus formed are sometimes called "minterms" and are designated by a lower case "m" subscripted by the appropriate state number. Thus, /13/

$$m_0 = \overline{A} \overline{B} \overline{C} \overline{D}$$

$$m_1 = A \overline{B} \overline{C} \overline{D}$$

$$m_2 = \overline{A} B \overline{C} \overline{D}$$

$$m_3 = A B \overline{C} \overline{D}$$

$$m_4 = \overline{A} \overline{B} C \overline{D}$$

$$m_5 = A \overline{B} C \overline{D}$$

$$m_6 = \overline{A} B C \overline{D}$$

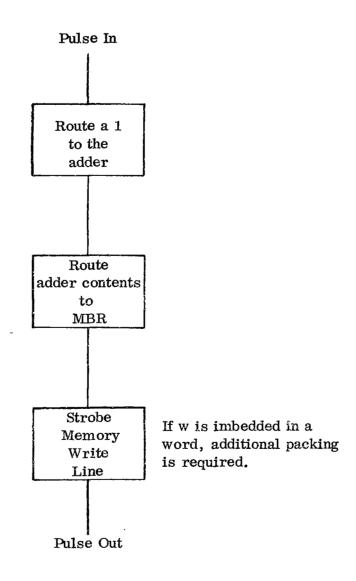

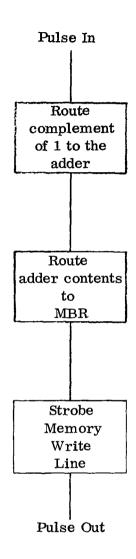

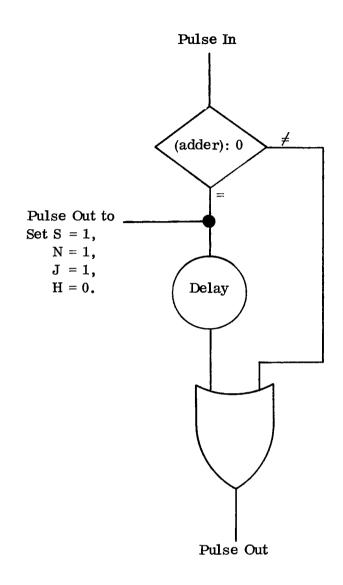

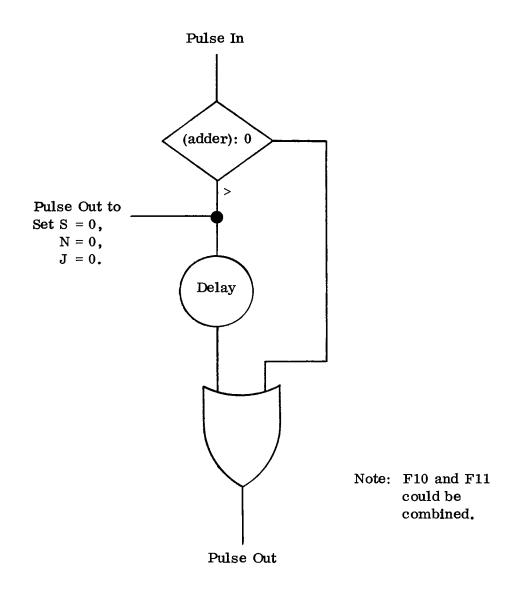

$$m_7 = A B C \overline{D}$$