#### **Space Shuttle Cockpit Avionics Upgrade**

**COTS Content in a Critical Manned Space Application**

#### **September 08, 2004**

Todd Smithgall, CAU Chief Architect, United Space Alliance LLC

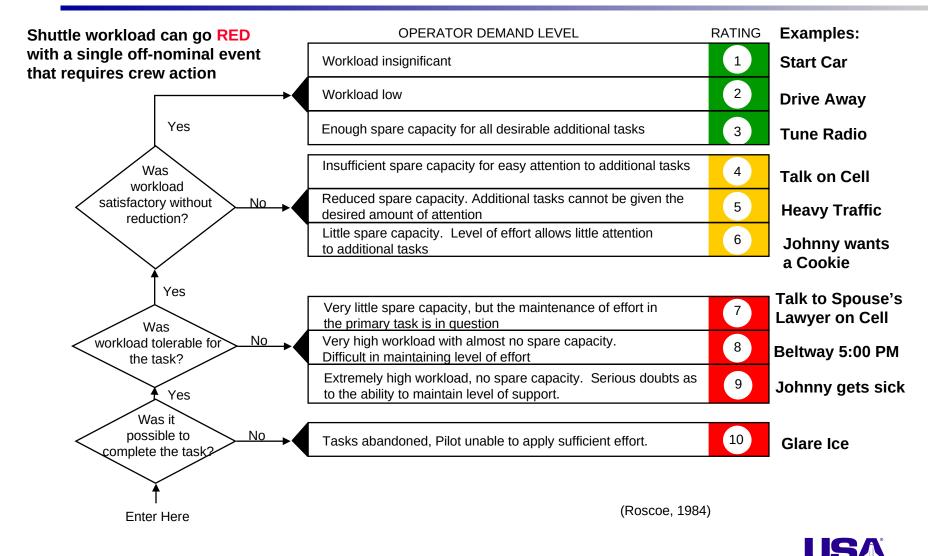

#### To increase situational awareness and reduce cockpit workload resulting in the execution of more accurate and timely decisions

note: crew error reportedly responsible for the majority of civil and military aeronautical accidents

# **CAU Project Background**

The Shuttle has complex flight regimes:

- Launch rocket for approximately 9 minutes

- Orbital spacecraft for 10-14 days

- Hypersonic plane for an hour

- Subsonic glider about 5 minutes

Large operational flight envelope is further complicated by an extremely large set of monitoring tasks and procedures over 10 major subsystems

- Propulsion, Guidance & Navigation, Flight Control, Hydraulics

- Power, Thermal, Environmental

- Data Processing, Communications

- Payloads

NASA chooses the "Best of the Best" for its astronauts

- Experienced test pilots with thousands of hours in 40+ aircraft

#### Minimum time required to train a shuttle pilot is 2-3 years!

See backup charts pp. 36, 37 for overview of Shuttle workload & task complexity

# **Need for Improved Situational Awareness**

- Situational Awareness (SA) is an understanding of the state of the environment

- It provides the PRIMARY basis for subsequent decision making and performance in the operation of complex, dynamic systems

- High workload

- What detracts from situational awareness?

- Too much data

- Too little time

- Malfunctions

- Lack of information

- Environmental distractions (noise, vibration, visibility, etc.)

- What are the consequences when these come together?

### Errors can be, and are, made

- Display navigation/command inputs

- Problem diagnosis and resolution

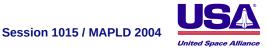

# **Current Shuttle Display Architecture**

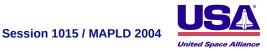

- 5X legacy General Purpose Computers (GPCs) perform redundant flight control, systems management, and display processing

- 4X legacy Integrated Display Processors (IDPs) perform text & graphics generation out to MDUs, keyboard I/O back to GPCs

- IDPs operate 100% independently from each other

- Each IDP's span to cockpit displays is limited by bus architecture

- **11X legacy Multi-Function Display Units (MDUs) are 7-inch backlit LCD displays**

- 7 MDUs have 2X 1553 ports, mapped to two different IDPs

- An IDP failure allows any of these 7 MDUs to switch to another IDP, but display continuity is lost as a result

- Remaining 4 MDUs are "dedicated" to an IDP, and do not have redundant ports

- 4X legacy Analog-to-Digital Converters (ADCs) gather legacy sensor data for display

# **Current Shuttle Display Architecture**

# **Key CAU Design Requirements**

- New displays <u>shall</u> provide both information and command path required to affect necessary change

- Composite displays <u>shall</u> present information from multiple data sources and multiple subsystems

- Logically arranged on single displays for streamlined cockpit operation

- Crew <u>shall not</u> be required to toggle between displays to gather information and take action

- Graphics performance (detail, rate, human factors) <u>shall</u> meet or exceed existing MEDS capabilities

- System <u>shall</u> be symmetric and modeless for critical operations

- Any display image is available on any of eleven (nine forward) physical displays

- Any keyboard is assignable to any display

- System <u>shall</u> remain symmetric and modeless after 1st failure

- After any single failure, cockpit looks and works the same as in normal operation

- Cockpit is fully functional after any two failures, with minor manual reconfiguration

- See backup charts pp. 38-47 for examples & summary of CAU human factors improvements

# **Design / Implementation Approach**

- Use COTS hardware and software to provide required system performance and development efficiency

- Survey of MIL & Space processor hardware showed a performance shortfall of 1 to 2 orders of magnitude

- Employ COTS hardware technology where feasible

- Processor, RAM, Flash, backplane standards, non-critical interfaces, test interfaces

- Employ MIL / MOTS / Custom / Radiation-Hardened technology where necessary

- Critical I/O interfaces, Gate Arrays (majority of custom logic)

- Use sound design mitigation techniques to select and adapt COTS to space environment

- Hardware-based error detection & correction

- Software-based correction (i-cache) or trapping (d-cache) of COTS processor cache upsets

- Exhaustive radiation test of COTS components, with strict pass / fail criteria

- Use & Enhance legacy Shuttle FDIR (Fault Detection Isolation and Recovery) capabilities

- GPC rejection of erroneous command inputs (syntax and content vs. current ops mode)

- GPC-generated test patterns for interface health monitoring

- Modify legacy architecture as necessary to meet unique user requirements

- Cross-Strapping of Command (DK Bus) and Display (1553 Bus) interfaces

- Ensure FO / FS (Fail OP / Fail Safe) Guidelines in effect at all stages of design

- System redundancy, power distribution, nominal command & display bus distribution vs. nominal cockpit operations, rigorous analysis of failure scenarios

- See backup charts pp. 33-35 for Data Pollution Prevention overview

# **FPGA Specific Implementation Approach**

- Xilinx for prototyping, convergence of requirements & design

- Note that the MIL hardware which is the design basis for much of CAU flies with Xilinx, so large portions of our prototype hardware was truly "off the shelf"

- Actel Commercial for Ground-use avionics hardware

- NASA manned space programs have non-flight hardware for verification & training labs that outnumbers flight hardware boxes ~2:1

- Majority of run time (~100:1) is accumulated on ground hardware, so "design similarity" to flight hardware (functional & performance @ bit level) is critical for accumulation of valid hardware design shelf life, software development & formal verification credit

- Actel Rad Tolerant for Flight avionics hardware

- Reserve highest cost components for actual flight hardware

- Based on the assumption (with proof required !) that the Rad Tolerant implementation is easily ported from, and "works like" the Commercial equivalent parts

- Design similarity of ground vs. flight hardware is ensured by screening logic designs against Commercial <u>and</u> Rad Tolerant FPGA timing constraints at each design iteration

## **CAU System Content**

- New CAU Software Applications Enable Cockpit Safety Goals

- Shuttle Abort Flight Management (SAFM)

- Graphically shows Abort Opportunities based on current vehicle energy and configuration during Critical Mission Phases

- New Display layout and navigation scheme

- Enhanced Caution & Warning (ECW) (Full ECW not currently funded, but baseline system achieves many of the ECW objectives)

- Uses graphics and text to show Configuration, Faults and Fault History of Shuttle Systems

- Onboard Systems & Flight Dynamics Monitoring equal or superior to Mission Control

- New CAU Hardware hosts New CAU Software Applications

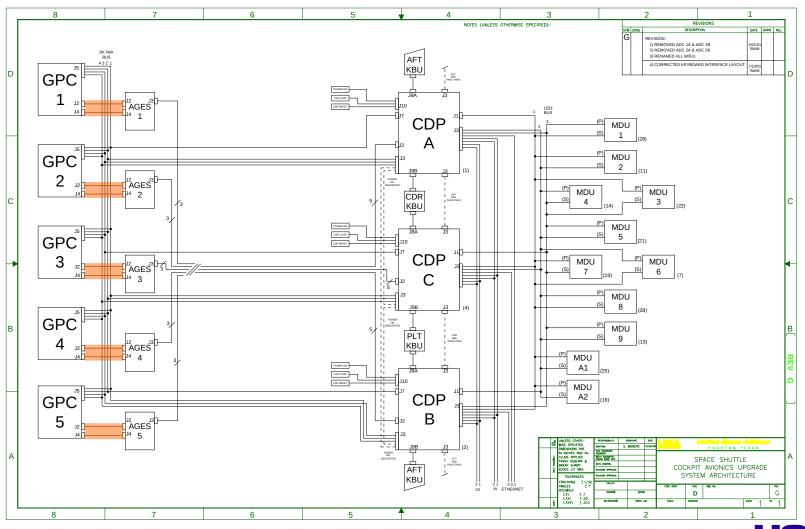

- Command & Display Processor (CDP)

- Three new CDP boxes replace four existing MEDS Integrated Display Processors (IDPs), with significantly more processing power and enhanced connectivity to Shuttle Vehicle Data

- ~1000 X as powerful as Shuttle flight control General Purpose Computers (GPCs)

- General Purpose Computer (GPC) Avionics Ground Equipment interface Serializer (AGES)

- Five new AGES boxes capture all memory data from the five existing GPCs, and forward that data to the CDPs, giving the CAU system full insight into existing Flight Software data and processes

- The CAU project will use pieces of the Multi-Functional Electronics Display System (MEDS)

- Integrated Data Processors will be replaced with Command and Display Processors (CDPs)

- Multi-function Display Units (MDUs) will be retained

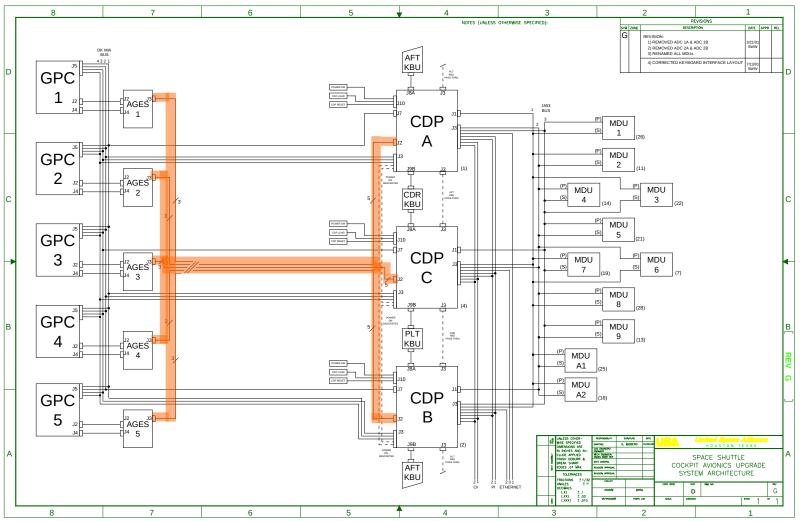

# **Cockpit Avionics Upgrade Architecture**

- 5X legacy General Purpose Computers (GPCs) perform redundant flight control, systems management (*but not display processing*)

- Display processing software has been excised from GPC Flight Software

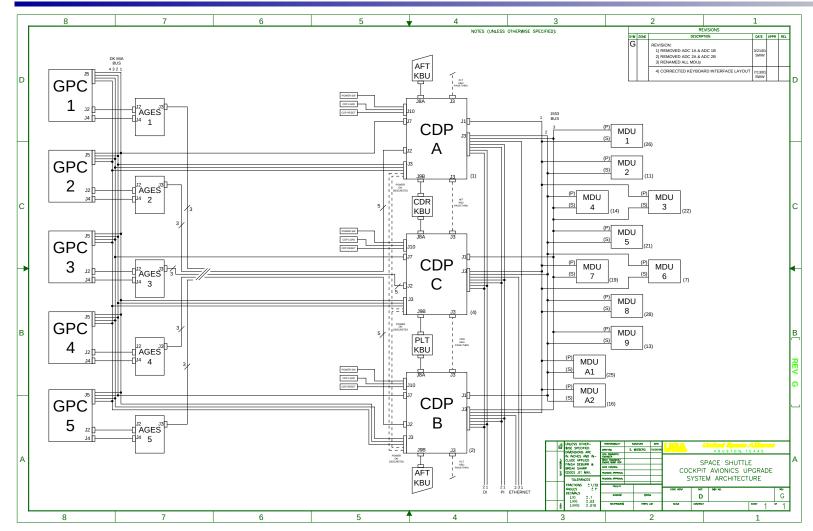

- 5X new Avionics Ground Equipment Interface Serializers (AGES) units act as Reflective Memory encoders & transmitters per GPC

- Xceivers plus one FPGA no RAM, no software, no firmware

- 3X new Command and Display Processors (CDPs) perform graphics generation out to MDUs, keyboard I/O back to GPCs

- CDPs operate *cooperatively and redundantly*, and are "aware" of each other's tasks

- Each CDP's span to cockpit displays is <u>not</u> limited by bus architecture

- **11X legacy Multi-Function Display Units (MDUs) are 7-inch backlit LCD displays**

- <u>All</u> MDUs have 2X 1553 ports, mapped to all CDPs

- A CDP failure allows <u>any</u> of the 11 MDUs to switch to another CDP, and display continuity is <u>maintained</u>

## **CAU Hardware Architecture**

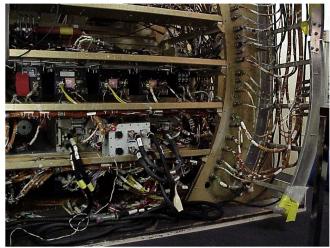

### **Vehicle Modification Kit**

#### **Representative Installation Views**

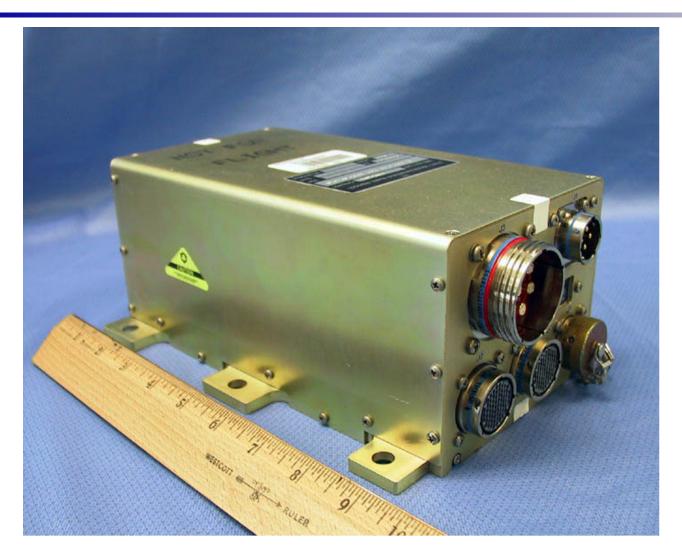

## **New CAU Hardware – AGES**

- AGES Avionics Ground Equipment Serializer custom reflective memory adapter

- AGES ties legacy Flight Control and Systems Management GPCs to new CAU System by duplicating memory contents of the 5 GPCs in EACH of the three CDPs, in real time

- AGES implemented (one per GPC) as a small, lightweight, low power (<10W) data serializer, to eliminate long, heavy runs of parallel data cable

- AGES tracks parallel data on GPC memory bus via a GPC factory diagnostic interface (currently unused in flight)

- AGES error-checks GPC interface, then streams each GPC memory transaction via Fibre Channel (FC physical level, custom 10 character protocol) serial bus to each of three CDPs, where GPC memory images are reconstructed in real time

- AGES sends GPC data @ 531 Mbps over 60' twinax copper FC media, Bit Error Rate requirement allocation < 1E-19 (FC BER spec is < 1E-12), open loop, no retry on error</li>

- Ultra high quality wiring & connectors, custom Reed-Solomon forward error correction encoding / decoding hardware to meet E-19 BER requirement using a 1E-12 BER (COTS) physical link

- CDP Software can now read all legacy GPC parameters directly from reconstructed GPC memory images sent by AGES, with ZERO GPC overhead

- AGES can be considered as an <u>extension</u> of the GPC for both operations and faultmanagement purposes

#### **AGES Photo – Cover Removed**

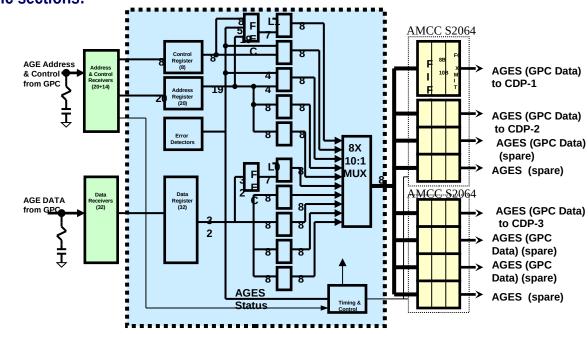

# **AGES AGE Capture Module (ACM)**

- The AGES AGE Capture Module:

- Captures information appearing on the GPC parallel AGE interface

- Interprets this information for valid or abnormal operations and status conditions

- Transmits this information to the CDP via a serial Fibre Channel interface

- The ACM has three major logic sections:

- AGE interface receivers

- An FPGA for data capture, timing and control

- Fibre Channel transmitters

AGES FPGA

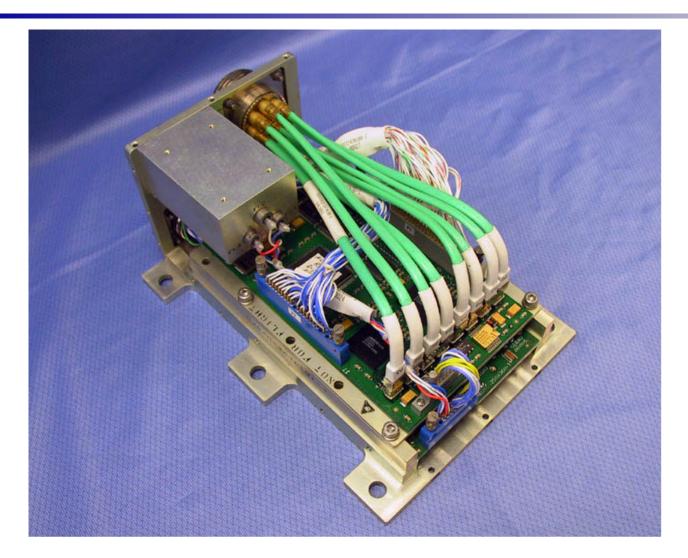

### **New CAU Hardware – CDP**

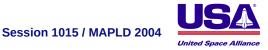

- CDP Command and Display Processor

- CDP (CAU) replaces legacy DEU (MCDS) or IDP (MEDS)

- General Purpose CPU (Motorola 7455) for OS and Apps (Displays, Commanding, SAFM, ECW)

- Dedicated radiation-tolerant channel processors for 1553 (COTS) and MIA (Custom) interfaces

- Discrete I/O for Power, Reset, Mode and Panel Indicator control

- Receives, checks and processes GPC memory contents from 5 AGES units

- CDP Software can now read all legacy GPC parameters directly from reconstructed GPC memory images sent by AGES, with ZERO GPC overhead

- Receives Crew Keyboard inputs

- Sends MDU Display Outputs, GPC Command Outputs

#### **CDP Photo – Cover Removed**

# **CDP Deserializer Module – DSM**

- AGES Interface

- 531 Mbaud interface

- Modified Reed-Solomon Forward Error Correction

- FIFO Interface

- Original design used 128K deep FIFO (≈ 28 msec @ 250 ns max GPC data rate)

- 32K deep FIFO adopted to replace 128K deep FIFO due to more favorable radiation characteristics, still with adequate performance margin

- ECC ("Modified Hamming Code") correct any one, detect any two bits in error

- SRAM Interface

- ARM 512K x 16 bits x 5 channels

- Holds real-time contents of memories of all 5 GPCs

- Event RAM 512K x 16 bits x 5 channels

- Holds programmable triggers that signal CDP of selected GPC software events

- Used to synchronize the CDP software with GPC software

- Both with ECC ("Modified Hamming Code") correct any one, detect any two bits in error

- PCI Bus Interface

- Built In Test (BIT) Features

- Data Wrap

- Forced Single Bit Error / Multi Bit Error at every stage

- BIT features enabled only via two or more dissimilar software actions, to prevent inadvertent activation during normal operation

# **Memory Technologies & Mitigations**

- EEPROM holds boot configuration parameters & hardware error logs

- Controlled by FPGA outputs (potential glitch issue), but device has write-protect "cipher" mechanism (managed in device driver software) to prevent stray writes during transients

- Minor exposure to corruption if in writable mode during power failure

- Exposure exists for a few tens or hundreds of milliseconds per Shuttle Mission

- Flash holds boot code on processor card and I/O channel cards, holds applications and logs on secondary VME card operating under True Flash File System (TFFS)

- Redundant Kernel images, redundant application file partitions

- but non-redundant COTS boot loader at least it's small...

- Radiation testing led to selection of a different component, and the addition of a softwaremanaged RESET function

- Software RESET is OR'd with Power-On / Off Reset at each Flash component

- 7X improvement in radiation performance while held reset

- SDRAM main processor memory

- 512M x 4 bit, 4-bit error detection, 1-bit error correction, via COTS memory controller

- Hardware-initiated background cyclic scrub (rewrite) of single bits in error

# Legacy GPC Test Port (Mem Addr, Data, Cntl)

# **CAU Interfaces – External – GPC AGE**

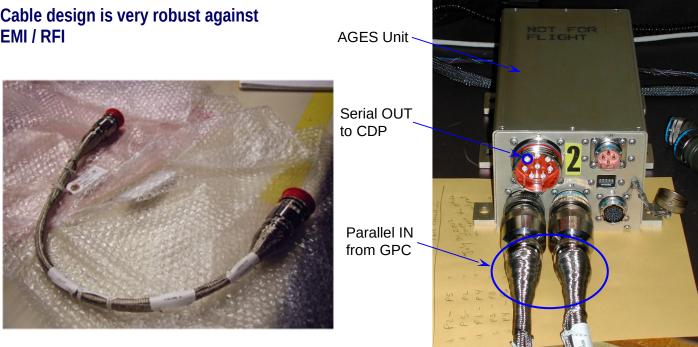

- GPC AGE to AGES cables are short (<3 ft.) high conductor count (parallel bus), internally shielded, with outer overbraid

- 2 cables connect each GPC to the associated AGES

- 10 cables total per vehicle 2 per GPC / AGES

- Cable design is very robust against EMI / RFI

- GPC interface design, conductor count and resulting bulk of the cables makes them unsuitable for long, multipoint runs to CDPs

- AGES unit is designed specifically to take the parallel data from each GPC and convert it to serial for more efficient multipoint distribution

# CAU Interfaces – Internal – High-Speed Serial

Session 1015 / MAPLD 2004

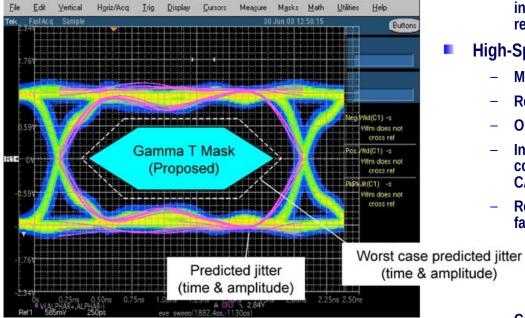

# **CAU Interfaces – Internal – High-Speed Serial**

#### High-Speed Serial Link Design

- Point-to-point from each AGES to each CDP

- Uses COTS Fibre Channel transceiver components

- 1E-19 Bit Error Rate (BER) allocation keeps link errors below 10% of intrinsic CAU hardware failure rate

- Native Fibre Channel spec 1E-12 BER requires 1E-7 BER improvement for use in CAU

- Reed-Solomon code corrects any one <u>character</u> in error (1 to 10 <u>bits</u> in error) per 10 character data packet on serial link

- Assuming random distribution of bits in error, design produces 4.5E-21 BER

- Correction code offers 4.5E-9 improvement factor over the spec'd 1E-12 interface BER

- Lab & Model evaluation of CAU implementation indicates that UNCORRECTED link meets 1E-19 requirement (see at left and below)

#### High-Speed Serial Link Model vs. Actual

- Model predictions in Pink

- Remaining trace is measured data

- Outer mask is worst-case noise prediction

- Inner mask is exclusion zone for 1E-19 BER without correction code – uncorrected physical design exceeds CAU system requirements !

- Reed-Solomon ECC improves link BER by 4.5E-16 factor: System BER < 4.5E-35 !</p>

- Link MTBF = 1.2E24 hours = 1.3E20 years

- System 15-Link MTBF = 8.8E18 years

- (Age of Universe is 1.4E10 years...)

- Conclusion: CAU High-Speed Serial Interface is ~immune to noise, thermal & jitter effects

# The Rest of the Story...

- Preceding analysis is valid for the superposition of all known thermal & electrical noise contributions to Bit Error Rate (BER), but...

- Recent radiation testing of COTS Fibre Channel Interface chipset revealed a failure mode that does NOT map to the design assumptions on the previous page !

- Inadequate fidelity of initial COTS component test allowed the escape, caught (late) in system-level test

- In addition to expected bit inversions, we occasionally see single MISSING or EXTRA bits, which cause loss of correct data sync until the next sync character (channel resyncs only between whole message packets)

- Causes ALL data characters within a data packet after the initial error to be garbled, which sometimes exceeds the error-correction capability of the FPGA-based custom Reed Solomon (RS) error correction scheme

- Since links are ~redundant at the system level, we prefer to lose a link rather than accept bad data

- **Fix (actually a statistical mitigation, not a fix) is a design tweak to the FPGAs on either end of the link:**

- Transmitter send less data, more idle (sync) characters, by eliminating "unimportant" GPC data

- Receiver DO NOT fail the link in response to garbled sync characters that are bracketed by good sync characters

- Receiver deterministically FAIL the link, rather than attempt to correct detected sync errors and "codeword violations" (morphing of data characters into control characters)

- Result is a 5X improvement in radiation tolerance, and no known way to induce xfer of erroneous data

- Link reliability still meets top-level system requirements, but is now somewhat lower than "age of the universe"

- Predict one serial link radiation upset every 2560 days

- Was one upset every 482 days prior to design tweak

- "Do-Over" (big redesign) would perhaps interleave individual data and sync characters, isolating each erroneous data character from other data characters, preserving the RS error correction capability

- Cost, schedule and (perhaps) performance prohibitive, not required for adequate radiation tolerance

- Test non-pedigree components as early as possible

- Test non-pedigree components in a manner that is as high-fidelity as possible vs. your intended design application

- Conduct rigorous comparison between your test pass / fail criteria and any <u>assumptions</u> you make about component behavior, both specified and unspecified

- DO NOT assume that all logic features & functions within a component have similar radiation sensitivity

- Exercise all the component features you intend to use, at realistic duty cycles, during component test

- Iterate component test (spiral development!) as design application detail is revealed or modified

- ✓ Confirm component test results (and extrapolations!) via system-level test

- Downside all this is expensive and takes a long time, but it's a bargain compared to a failed project

# **CAU Project Status & Accomplishments**

#### Software

- Ten major software builds complete

- Data Management

- GPC commanding & state tracking

- 1553 & DK bus management

- Keyboard input

- 120+ new displays

- Shuttle Abort Flight Management (SAFM)

#### Hardware

- Mature Flight-Like Hardware installed in numerous NASA facilities

- Flight Hardware Production ramping up

- Vehicle Modification Kits Complete, ready to support Vehicle Installation

- Full System is being "flown" in the Shuttle Mission Simulator (SMS) by Astronaut crews, for human factors evaluation purposes, with great results

- Strong Cost & Schedule posture for On-Time, On-Budget Completion

## **Backup Charts**

# **Hardware-Based Data Pollution Prevention**

- Data Pollution = ANY erroneous transfer of data from one unit to another

- AGES

- Inhibits outputs during AGES and GPC power transients

- Validates clocks and control signal sequences of every GPC memory transaction

- CDP

- Hardware disable of all external and critical internal interfaces at power on / off and reset

- Dual bus transmitter disable controls, per each 1553 channel and MIA channel

- Independent dissimilar software actions required to enable external interfaces

- Independent dissimilar software actions required to invoke Built In Test Equipment (BITE) logic

- Robust error detection / correction on internal interfaces and memories

- Robust bus energy detection on MIA interfaces to preclude dual-transmitter bus collisions

- Synchronization of DK Bus transmitter <u>cutoff</u> to GPCs upon error, to prevent mixed perception of I/O error signature among redundant GPCs due to time-slivering

- Comprehensive detection and status of errors (critical and non-critical) on internal interfaces and memories, for software mitigation, annunciation or downlist as required

# **Software-Based Data Pollution Prevention**

- **1.** Failed CDPs purge any pending GPC commands

- 2. Commands are only sent from the "Prime" CDP (usually this means only from the CDP with MDU focus)

- 3. Don't respond to invalid GPC DK Bus Polls

- 4. Don't command to GPC bus polls which had transmission errors

- 5. In addition to CDP-detected errors, use GPC parameters ("Fail Indicator DEUX GPCY") to determine if a DK Bus is failed

- 6. Do not command on a failed DK Bus (CDP-detected or GPC-detected)

- 7. Do not command to a failed GPC

- 8. Do not command to a GPC if that GPC's Major Function can't be determined by CAU "GPC State ID" process

- 9. Reject user commands targeted for a GPC Memory Configuration which does not exist

- **10.** Reject user commands targeted for a GPC Memory Configuration to which the CDP does not have a DK connection

- 11. Reject user commands targeted for GPC Software OPS 0 if GNC, Sys Mgt, Payload modes all exist

- 12. Reject user commands during Primary Avionics System Software (PASS) Ops Transitions and Major Mode boundaries

- 13. Purge latent user commands during PASS Ops Transitions and Major Mode boundaries

- 12 & 13 satisfy legacy GPC Flight Software OPS / User Notes

- 14. Sniff Backup Flight Software (BFS) GPC memory to verify commands targeted for BFS arrive correctly.

- 15. "Bus Busy" detection on the MIO (hardware & software) prevents dual responding

- 16. Detect Dual GPC bus commanders and annunciate to crew, but do not respond to GPCs

- 17. Disable DK Bus if dual CDP responders detected protects legacy system against bus collisions

- 18. Perform Dual-Software-Path GPC Command computation in CDP, compare results on rad-tolerant MIO (GPC command path I/O channel hardware inside CDP), discard if not equal

- 19. Command Key Timer in CDP prevents latent or spurious GPC commands ensures GPC commands are from REAL (human-initiated, not hardware transient) keystrokes

# **System-Level Data Pollution Prevention**

- In addition to all previous Hardware & Software techniques for preventing erroneous results from single units, do the following to prevent system-level errors:

- Within a single CDP, Compare & Vote critical redundant data from redundant GPCs (when available) @ 25 Hz, to detect otherwise undetectable interface, storage or processing errors

- Auto-Inhibit (fail) minority external data source, select next available redundant data source

- Across multiple CDPs, Compare & Vote critical CAU System Configuration parameters (data bus commander & responder assignments, keyboard & display assignments) @ 25 Hz, to detect divergence between CDPs

- Auto-Inhibit (fail) minority CDP, reassign Displays to other working CDPs

- Manual intervention required if no minority CDP (rare multiple failure scenario)

# **Bedford Workload Scale**

Session 1015 / MAPLD 2004

United Space All

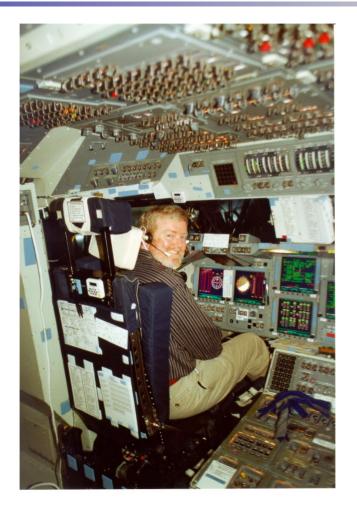

# Shuttle Cockpit is a Complex Work Environment

- 100+ time / safety critical dynamic flight procedures

- Aborts to KSC, East Coast, Spain, Africa, Orbit

- ~1000 on orbit procedures

- Systems, Payloads, Mission Objectives

- On orbit in-flight maintenance procedures designed in real-time

- Problem diagnosis and repair / recovery

- Pre-CAU Signature Recognition required for almost every procedure

- Obscure problems are recognized by specific 'Christmas Tree' warning light patterns

- Pre-CAU Rote memorization required in display navigation and problem diagnosis

- Backed up by hundreds of pages of printed manuals, carried each mission

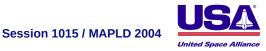

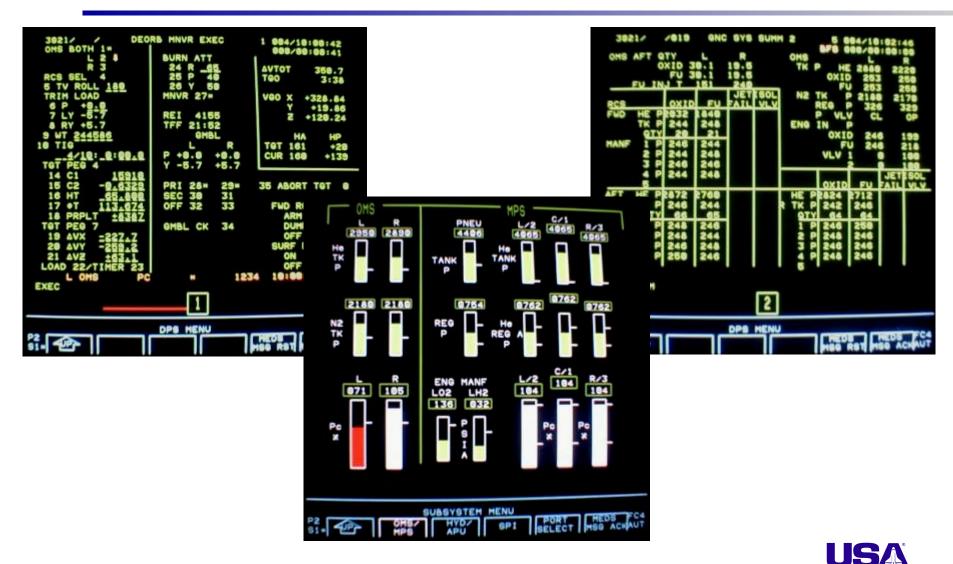

# Legacy vs. CAU Display Quality

- The following charts show examples of legacy displays vs. new CAU displays

- **Each pair of charts shows the same fault scenario or emergency procedure**

- Observe that fault conditions are often obscured on the legacy displays, requiring the crew to perform pattern recognition vs. <u>memorized</u> display appearance

- Conversely, observe that CAU displays highlight fault conditions in a more logical, more easily recognizable manner

United Space Alliance

## Legacy Displays to support OMS Burn Task

# **CAU Display to support OMS Burn Task**

| 0001/                                 | /078  |      | SYS SUMM  | •   | BFS  | 00/00: | 88:00<br>88:00 |

|---------------------------------------|-------|------|-----------|-----|------|--------|----------------|

| SMOKE                                 | 1/4   | 2/8  | 00 1101 1 |     |      |        |                |

| CABIN                                 | 0.0   |      | DC VOLT   | 5   | 1/4  | 2/8    | 3/C            |

| L/R FD                                | 0.0   | 0.0  | FC        |     | 30.2 | 0. OL  | 28.3           |

| AV BAY 1                              | 0.0   | 0.0  | MAIN      |     | 30.2 | 28.3   | 28.3           |

| 2                                     |       | 0.0  | CNTL      | AB  | 28.6 | 28.6   | 28.6           |

|                                       | 0.0   | 6.0  | -         | BC  | 28.6 | 28.6   | 28.6           |

|                                       | BIN   |      |           | CA  | 28.8 | 28.6   | 28.6           |

| PRESS                                 | 14.0  |      | ESS       |     | 28.5 | 28.8   | 28.8           |

| DP/DT                                 | +.00  |      | AC        |     |      |        |                |

| BU/EQ                                 |       | +.80 | VOLT      | •   | 118  | 118    | 117            |

| PP02                                  | 3.00  | 3.00 |           | +B  | 117  | 117    | 118            |

| FAN AP                                | 5.88  |      |           | +C  | 117  | 117    | 118            |

| HX OUT T                              | Θ     |      | AMPS      | •A  | 6.4  | 4.3    | 3.0            |

| 82 FLOW                               | 8.8   | 8.8  |           | +B  | 5.8  | 4.8    | 4.3            |

| N2 FLOW                               | 8.8   | 0.0  |           | +C  | 3.4  | 4.2    | 4-1            |

| IMU FAN                               | AP    | 0.00 | FUEL CE   | ELL | PH   |        |                |

| AV FC1                                | FC2   | FC3  | AMPS      |     | 229  | GL     | 4651           |

| SS1 22                                | GL    | 22   | REAC      | VLV | OP   | CL     | OP             |

| SS2 22                                | GL    | 23   | STAC      | K T | +204 | +2221  | +289           |

| SS3 23                                | eL.   | 21   | EXIT      | т   | +151 | +173   | 156            |

| TOTAL AM                              | PS 63 | 4    | COOL      | P   | 60   | 168    | 59             |

|                                       | KW 1  |      |           | UMP |      | APS    |                |

| YS SUMM                               |       |      |           |     |      |        |                |

| o o o o o o o o o o o o o o o o o o o |       |      |           |     |      |        |                |

|                                       |       |      |           |     |      |        |                |

|                                       |       |      |           |     |      |        |                |

|                                       |       | 0    | S MENU    |     |      |        |                |

| 6661/                     | /879     | SM   | SYS SI | JMM 2  | 5 00   | 4/10:0           | 4:16                  |

|---------------------------|----------|------|--------|--------|--------|------------------|-----------------------|

| CRYO T                    |          | 2    | 3      | 4      | 6      | MANF 1           | HANF2                 |

| H2 PRESS                  | 210      | 210  | 239    | 239    | 239    | 239              | 238                   |

| HTR T1                    | -164     | -164 | -137   | -137   | -137   | 852              | 852                   |

| 12                        | -164     | -164 | -137   | -137   | -137   |                  |                       |

| TEMP EGT                  | 1        | 2    | 3      | PRESS  | •      | 2                | 3                     |

| B/U EOT                   | õ        | ĕ    |        | ACUM P |        |                  |                       |

| OIL IN                    | 0        |      | 0      | REVR T |        | ē                |                       |

| OUT                       | <u>e</u> | 2    | 2      | QTY    |        | ۲                |                       |

| GO BED                    |          |      |        |        |        |                  |                       |

| SPEED *                   | ĕ        | ĕ    | ĕ      | W/B    |        |                  |                       |

| FUEL GTY                  |          | ē    | 0      | H28 QT | Y O    |                  | 0                     |

| PHP LK P                  |          | 0    | ۲      | BYP VL | V BYP  | BYP              | BYP                   |

| OIL OUT P                 | •        | ۲    | 0      |        |        |                  |                       |

| FU TK VLV                 |          |      |        | THE    | M CNTL | 1                | 2                     |

| B Ť                       | ĕ        | ă    | - i    |        | MP P   | 68               | 2<br>58<br>2888<br>58 |

| AV BAY                    | 1        | 2    | 3      | FREON  | FLOW   | 50<br>2000<br>50 | 2000                  |

| TEMP                      | 69       | 0    |        | EVAP O | UT T   | 50               | 60                    |

| FAN AP                    |          | 0.00 | 0.00   |        |        |                  |                       |

| SYS SUMM                  |          |      |        |        |        |                  |                       |

| Contraction of the second |          |      |        | 1      |        |                  |                       |

|                           |          |      | 2      |        |        |                  |                       |

|                           |          | -    |        |        |        |                  |                       |

| P2-                       | _        |      | PB MEN | 0      |        |                  | DE FC4                |

| S1 42                     |          |      |        |        | HOG R  | 81 189           | ACHAUT                |

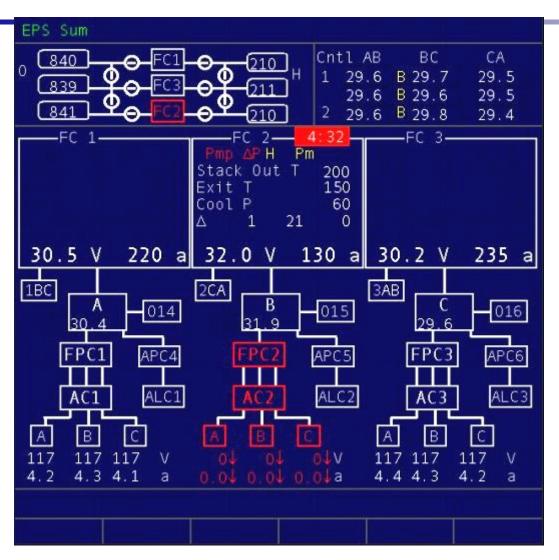

# CAU Electrical System Summary Display

# **Legacy Ascent Horizontal Situation Display**

| 1011/050/<br>PTI INH 1 ALTM<br>INDEX 0 9 2                                    | HORIZ SIT<br>9_92                            | 1 217/06:22:56<br>000/00:01:33<br>NAV DELTA<br>ΔX 10    |

|-------------------------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------|

| 40 TAL SITE _4<br>41 RTLS SITE _1<br>PRI KSC15 3<br>SEC KSC33 4*<br>TAC- 59 5 |                                              | ΔΛ 10<br>ΔΥ 11<br>[] 0<br>ΔΖ 12<br>[] 0                 |

| GPS FOM RA<br><u>1 46</u><br>TAEM TGT<br>G&N OVHD 6<br>HSI                    |                                              | ∆X 13<br>[10<br>∆Y 14<br>[] 0<br>∆Z 15                  |

| NEP 7<br>AIM NOM 8<br>S/B NOM 39<br>NAV RESID RATIO                           | AUTINHFOR TACI                               | [] 0<br>LOAD 16<br><u>18 AT [10.00</u><br>0TAC2 0TAC3 0 |

| TAC AZ<br>RNG<br>GPS<br>DRAG H                                                | 19 20*21<br>42 43*44 DES 3<br>22*23 24 ABS 3 | 1 DES 32 DES 33                                         |

| ADTA H<br>ADTA TO G&C                                                         | <u>25 26*27 G</u> PS R<br>28 29*30 AIF_G     | AZ<br>47 48 <del>*</del> 49 H                           |

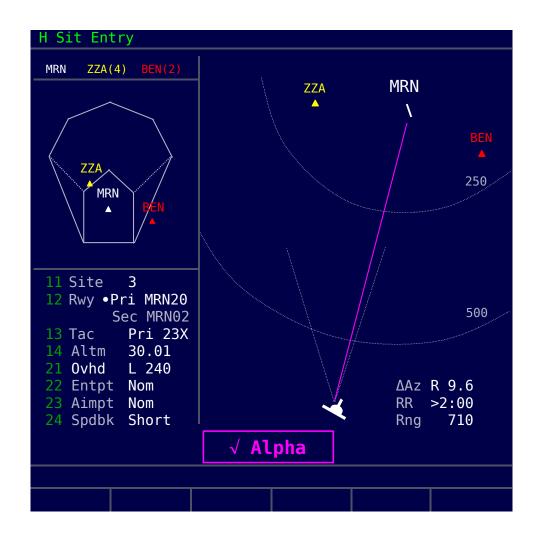

## **CAU Ascent Horizontal Situation with SAFM**

AT 0 H Sit Asc 2 Cur: ATO 104 Negative Return 1 Out TAL ZZA Out Cont 2nd Green Un Out Cont 2nd Yellow Site 1 Rwy •Pri KSC15 Sec KSC33 Pri 59Y Tac Altm 29.92 4 ZZA TAL Yaw Str Ena 17 SERC 22. LAJ 1845 23 85 Abort Mode -3 MRN Cont RTLS 2 BEN TAL 34•AT0  $\sigma_{o}$ 99 Abort

Ascent Horizontal Situation Display 2 with 1 Engine Out, and ATO Abort Executed.

# **Legacy Entry Horizontal Situation Display**

#### **CAU Entry Horizontal Situation Display with SAFM**

# **Summary – The CAU Safety Payback**

- Decisions and actions are more timely and more accurate

- CAU provides improved crew interface for display navigation and vehicle command and control

- Execute commands from any display via the existing keyboards

- Consolidate information from / commanding to multiple subsystems on single display

- Fewer keystrokes, less rote memorization, and better encoding of display parameters

- New mobile scratchpad and improved keyboard

- Generate multi-color graphics and logical information & command groupings on any display format

- CAU provides task-oriented displays

- Tailored to the phase of operation

- Utilize data from multiple sources and embedded logic in critical system and flight displays (data becomes information)

- Provide root cause analysis for the Data Processing subsystem and Electrical subsystem

- CAU provides trajectory information, now available at all times

- CAU expands the avionics processing power and capacity for future implementation of display applications and logic

- CAU separates display generation software and new applications from the GPCs

- Enabling Requirements drove the CAU Architecture & Design