DOW DFCL GUIDANCE AND NAVIGATION Date Approved MILTON B. TRAGESER. DIRECTOR APOLLO NAVIGATION AND GUIDANCE PROGRAM ROGER B. WOODBURY, ASSOCIATE DIRECTOR Approved INSTRUMENTATION LABORATORY CLASSIFIED by NA59-..... Subject to General Declassification Schedule of Executive Order 11652 Automatically Downgraded at Two Year Intervals. DECLASSIFIED on 3/ Dec 73

(Unclassified Title)

R-393

LOGICAL DESCRIPTION FOR THE APOLLO GUIDANCE COMPUTER (AGC 4)

> by Albert Hopkins Ramon Alonso Hugh Blair-Smith

COPY # 14 OF 1 ROPIES THIS DOCUMENT CONTAINS PAGES

(Unchessified Title) R-393 LOCICAL DESCRIPTION FOR THE AFOLLO GUIDANCE COMPUTER (AGC 4)

by Albert Hopkins Ramon Alonso Hugh Blair-Smith

## INSTRUMENTATION LABORATORY

**CAMBRIDGE 39, MASSACHUSETTS**

$\frac{\text{COPY} \# 29/1 \text{ of } 423 \text{ copies}}{\text{THIS DOCUMENT CONTAINS } 16 P$ PAGES

UNCLASSIFIED

#### ACKNOWLEDGMENT

This report was prepared under the auspices of DSR Project 55-191, sponsored by the Manned Spacecraft Center of the National Aeronautics and Space Administration through contract NAS9-153.

> This document contains information affecting the atio defen Unite within States the n aning )f Espior 18. T S U. ns 793 the ssion Sect rans and of w or the re ch in' latic any m nner to an unauthorize person is p ohibi aw.

The publication of this report does not constitute approval by the National Aeronautics and Space Administration of the findings or the conclusions contained therein. It is published only for the exchange and stimulation of ideas.

## UNCLASSIFIED

#### CONTENTS

| Chapter |  |

|---------|--|

|---------|--|

1

$\mathbf{2}$

3

4

| INTRODUCTION to AGC 4                        | 1        |

|----------------------------------------------|----------|

| AGC 4 SYSTEM                                 | 1        |

| General Organization                         | 1        |

| Clock and Scaler                             | <b>2</b> |

| Sequence Generator                           | 2        |

| Central Processing Section                   | 9        |

|                                              | 11       |

|                                              | 11       |

| Counter Incrementing                         | 12       |

| Program Interruption                         |          |

| WAITLIST and EXECUTIVE Programs              |          |

| -                                            | 19       |

|                                              | 19       |

|                                              |          |

| AGC 4 INSTRUCTIONS                           | 1        |

| General Remarks                              | 1        |

| Basic Instructions                           | 4        |

| Extracode Instructions                       | 6        |

| Special Cases; Implied Address Codes         |          |

|                                              | 13       |

|                                              | 14       |

|                                              | 20       |

|                                              | 21       |

| Exercises on the Examples                    |          |

|                                              |          |

| MEMORY • • • • • • • • • • • • • • • • • • • | 1        |

|                                              |          |

| General Characteristics                      | 1        |

| Fixed Memory Organization                    | 2        |

| Erasable Memory Organization                 | 13       |

|                                              |          |

# UNUL ... FIED .

### R-393 LOGICAL DESCRIPTION FOR APOLLO GUIDANCE COMPUTER 4

#### CUMPBENTIAL

| Chapter                  |         |     |   |     |   |   |   |   |   |       |   |   |   |   |   |   | Page |

|--------------------------|---------|-----|---|-----|---|---|---|---|---|-------|---|---|---|---|---|---|------|

| 5 IN-OUT                 | • • •   | • • | • | ••• | • | • | • | • | • | <br>• | • | • | • | • | • | • | 5-1  |

| General                  |         |     | • |     |   |   |   |   |   | <br>• | • | • |   |   | • |   | 5-1  |

| Types of Inputs and Ou   | tputs . |     | • |     |   |   |   | • |   |       |   |   |   |   |   | • | 5-1  |

| Method for Generating    |         |     |   |     |   |   |   |   |   |       |   |   |   |   |   |   |      |

| Conversion of Pulses in  |         |     |   |     |   |   |   |   |   |       |   |   |   |   |   |   |      |

| UPLINK $\ldots$ $\ldots$ |         |     |   |     |   |   |   |   |   |       |   |   |   |   |   |   | 5-5  |

| DOWNLINK                 |         |     |   |     |   |   |   |   |   |       |   |   |   |   |   |   | 5-5  |

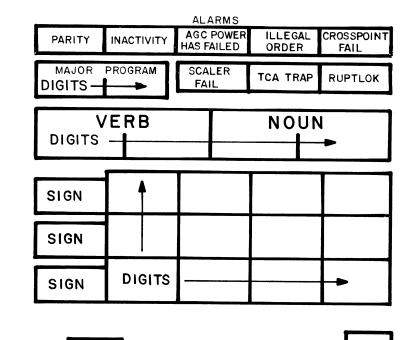

| Display and Keyboard (   |         |     |   |     |   |   |   |   |   |       |   |   |   |   |   |   | 5-11 |

| Standby Operation        |         |     |   |     |   |   |   |   |   |       |   |   |   |   |   |   | 5-13 |

| Alarms and Checks .      |         |     |   |     |   |   |   |   |   |       |   |   |   |   |   |   | 5-21 |

# UNCLASSIFIED

#### TONTESTIN

#### **ILLUSTRATIONS**

| Figure |                                                                  | Page   |

|--------|------------------------------------------------------------------|--------|

| 2-1    | General Block Diagram                                            | 2-3    |

| 2-2    | Clock and Scaler Block Diagram                                   | 2-5    |

| 2-3    | Sequence Generator Block Diagram                                 | 2-7    |

| 2-4    | Parity Test and Generation Block Diagram • • • • • • • • • • • • | 2-13   |

| 2-5    | Priority System for Counters                                     | 2 - 15 |

| 3-1    | Memory Cycle Timing                                              | 3-15   |

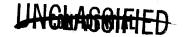

| 4-1    | Rope Suborganization Diagram                                     | 4-3    |

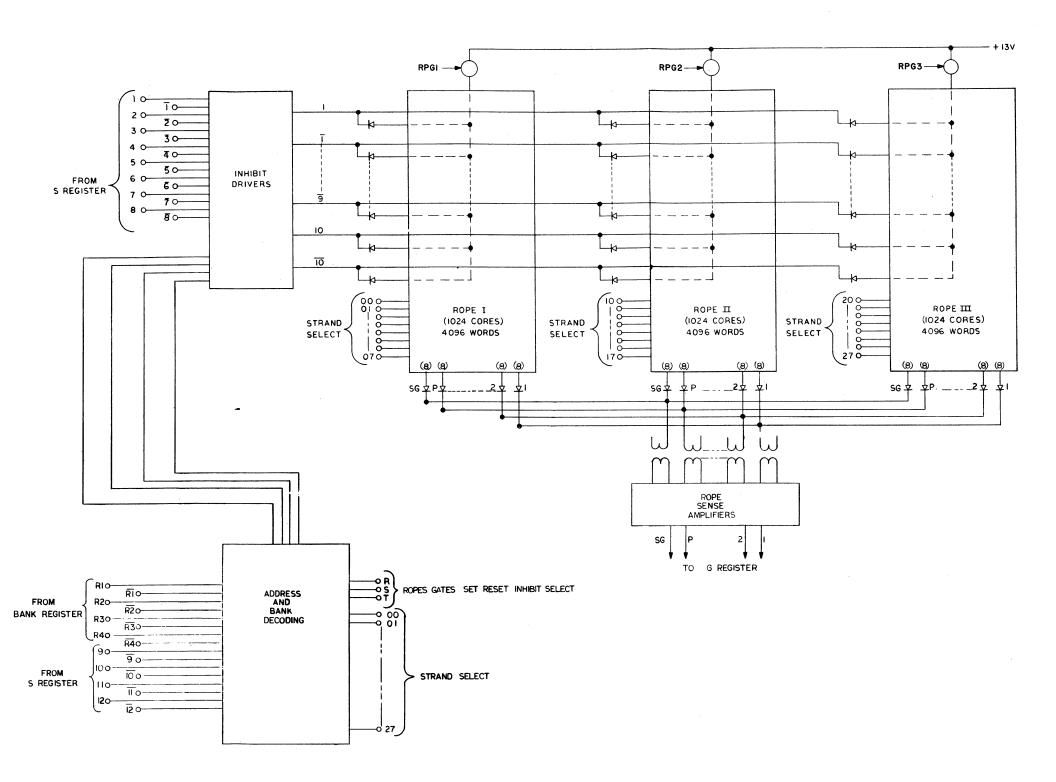

| 4-2    | Rope Selection System                                            | 4-5    |

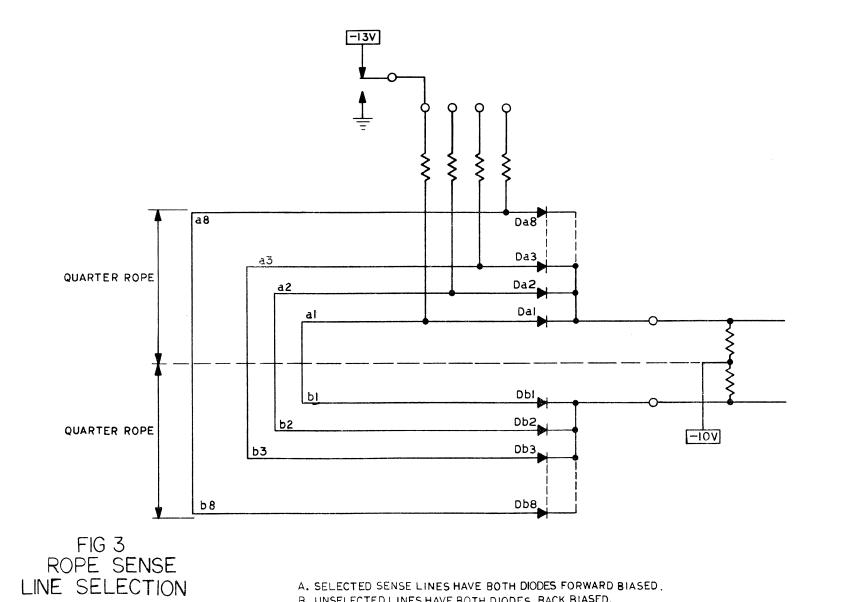

| 4-3    | Rope Sense-Line Selection                                        | 4-8    |

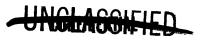

| 4-4    | Fixed Memory Timing • • • • • • • • • • • • • • • • • • •        | 4-12   |

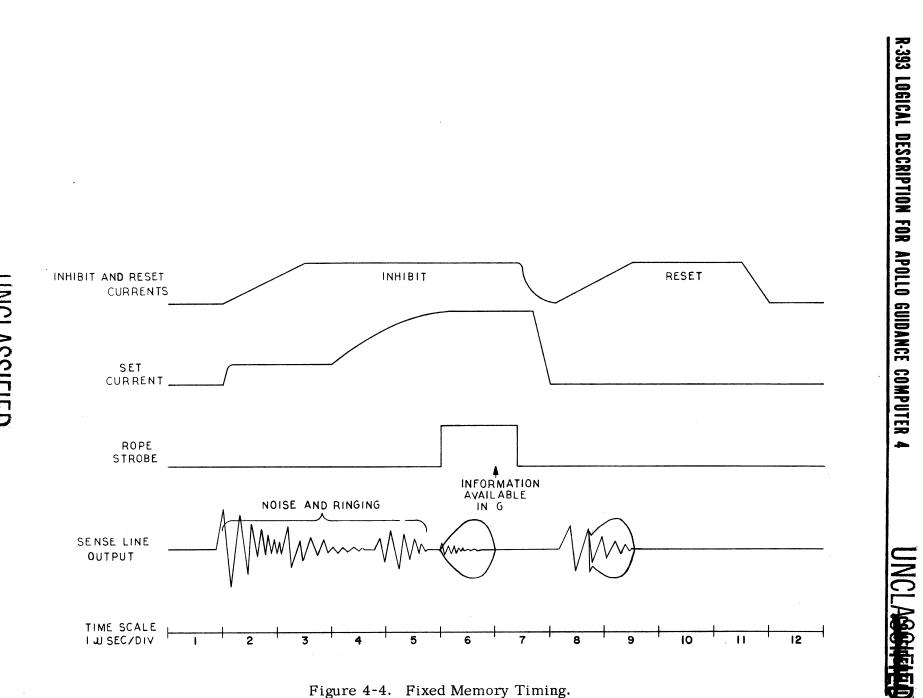

| 4-5    | Erasable Memory Timing                                           | 4-14   |

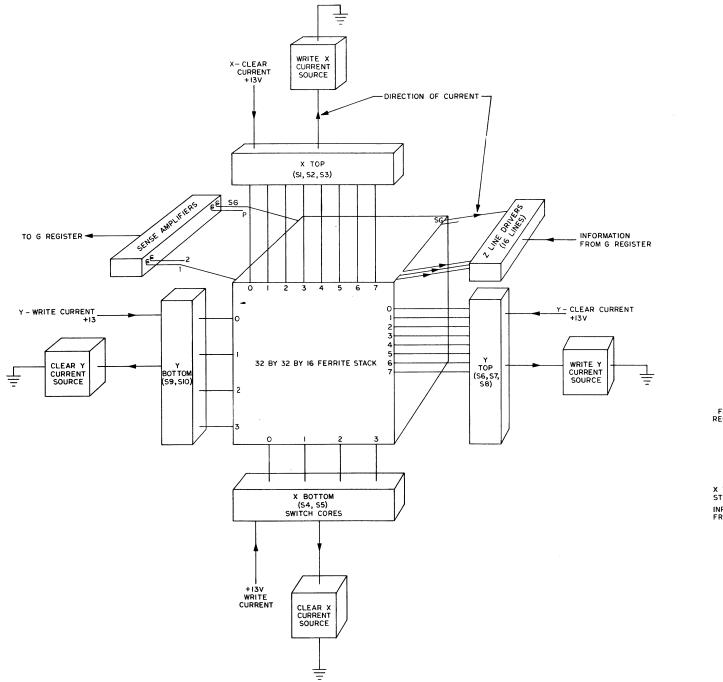

| 4-6    | Erasable Memory System                                           | 4-15   |

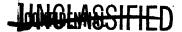

| 5-1    | In-Out Functional Breakdown                                      | 5-2    |

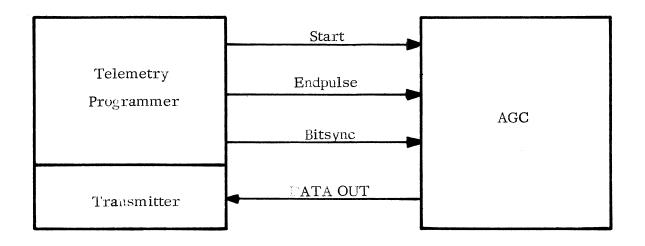

| 5-2    | Timing for D-A Converter                                         | 5-6    |

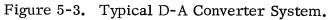

| 5-3    | Typical D-A Converter System                                     | 5-6    |

| 5-4    | Telemetry Interface                                              | 5-8    |

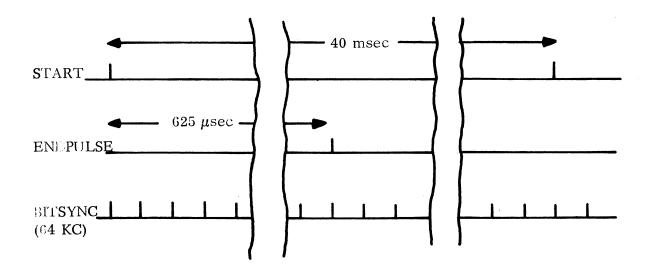

| 5-5    | Telemetry Timing                                                 | 5-8    |

| 5-6    | Telemetry System                                                 | 5-9    |

| 5-7    | Keyboard and Display                                             | 5 - 12 |

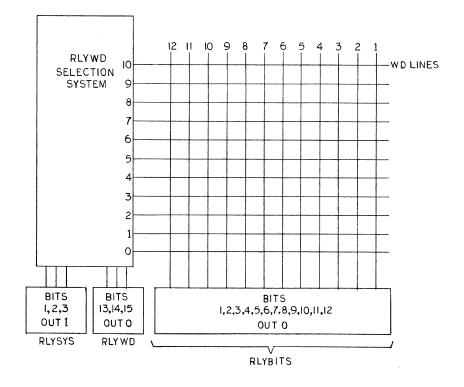

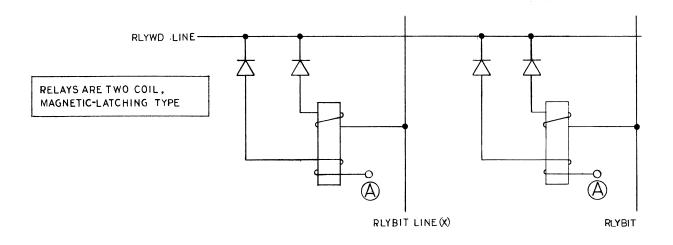

| 5-8    | Relay Crosspoint System                                          | 5-14   |

| 5-9    | Detail of a Relay Crosspoint                                     | 5-14   |

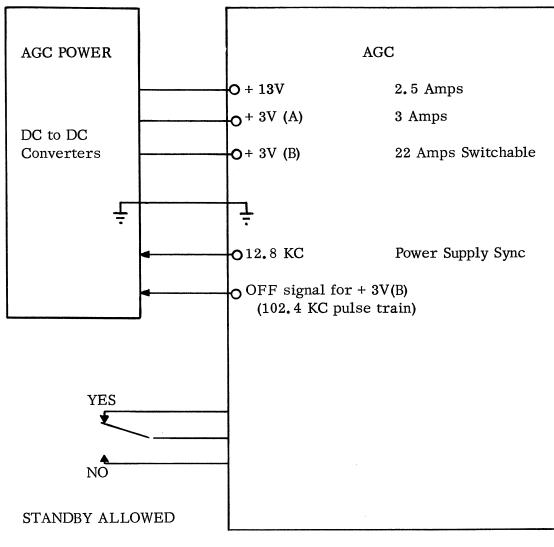

| 5-10   | Power System                                                     | 5-15   |

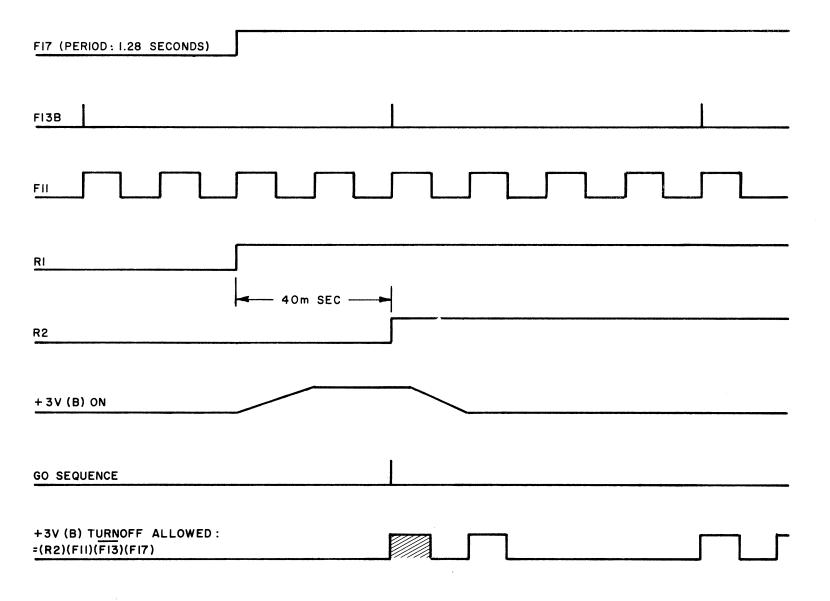

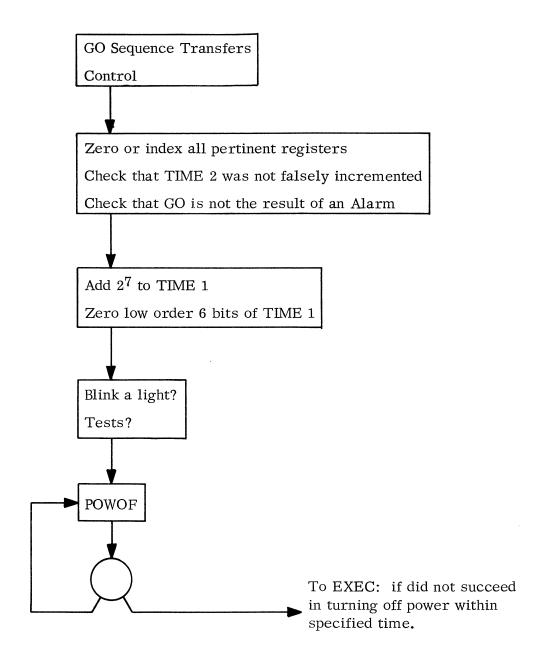

| 5 - 11 | Timing for Power Switching, Detailed View                        | 5-16   |

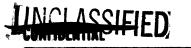

| 5-12   | Logic for POWOF                                                  | 5-17   |

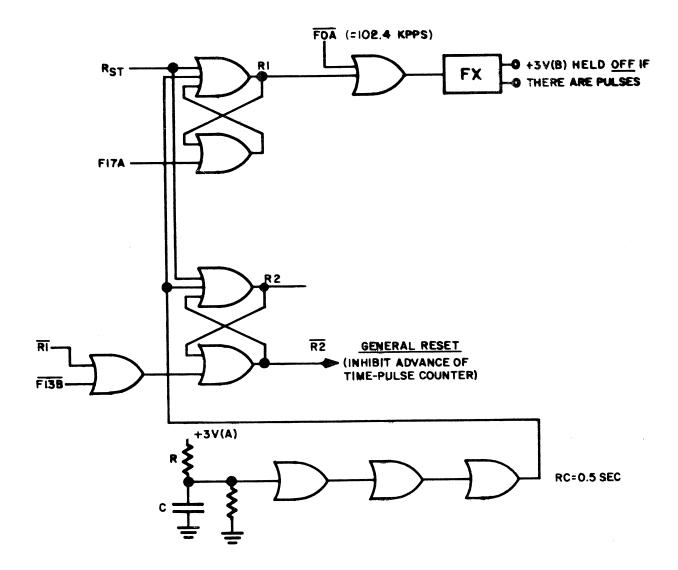

| 5-13   | Power Off Program                                                | 5-19   |

|        |                                                                  |        |

Page

#### TABLES

| 1-1   | Comparison of AGC 3 and AGC 4 Characteristics 1-3   |   |

|-------|-----------------------------------------------------|---|

| 2-1   | AGC 4 Special Registers                             | ) |

| 3 - 1 | AGC 4 Special Registers                             |   |

| 3-2   | How Registers are Written Into in AGC 4             |   |

| 3-3   | Comparison of Running Times of AGC 4 Sequences with |   |

|       | AGC 3 Sequences                                     | ) |

| 3-4   | Control Pulses in AGC 4                             | _ |

| 3-5   | Control Pulse Sequences in AGC 4                    | ; |

| 3 -6  | Flow Charts of Pulse Sequences in AGC 4 Part 1 3-51 | L |

| 4-1   | AGC 4, Bank Substitution                            |   |

| 4-2   | AGC 4, Rope Switching Functions                     |   |

| 5-1   | AGC 4, Complete Signals                             | ł |

|       |                                                     |   |

|       | A. Input Signal List                                | ; |

|       | B. Input Summary                                    | 1 |

|       | C. Inbit Assignments                                | ) |

|       | D. Counter Assignments                              | Ĺ |

|       | E. Interrupt (RUPT) Assignments                     | 3 |

|       | F. Output Signal List                               | Ŧ |

|       | G. Output Summary                                   | 7 |

|       | H. Outbit Assignments                               | ) |

|       | I. Scaler Nomenclature                              | L |

|       | J. Timing Specifications                            | 1 |

|       | K. In-Out System Scaling                            | 3 |

|       |                                                     |   |

Table

#### PREFACE

This report discribes the logical structure of the APOLLO guidance and navigation computer. A previous computer, AGC 3, designed for the APOLLO mission, was predominately composed of core-transistor logic. The computer design described here employs miniature integrated NOR logic, whose use will result in the next APOLLO computer (AGC 4) being just over half the size of AGC 3.

The decision to change over to integrated circuitry was made in October, 1962. About a year ago, it was deemed inadvisable to commit the APOLLO Guidance Computer (AGC) to integrated circuitry. Its desirable attributes of small size, high speed, and universality were then offset by its high cost, the difficulty in regulating power consumption as a function of speed of computation, and the absence of operational experience in large scale systems. Because of its potential, however, a computer-design investigation was conducted with integrated circuits at the Instrumentation Laboratory during the development of AGC 3.

Now, a year later, the price of integrated circuit elements has changed from high to moderate; and enough experience has been gained in their use, by MIT and by others, to permit extrapolation of their reliability data with substantial confidence. The adoption of the new technology, with the consequent redesign of the computer, is being undertaken at a time when it is felt that it can still be effected without causing undue delays in the program.

Since the first design of AGC 3 of about a year ago, much has been learned about the capabilities demanded of the APOLLO computer; enough programming experience has been gained to warrant the inclusion of programming features not present in AGC 3 and the exclusion of others that were. Consequently, AGC 4 is sufficiently different from AGC 3 to make existing AGC documents inadequate for use in further developing the guidance system and its production and support facilities. The prime purpose of this report is to furnish necessary information to members of the Laboratory and its contract and industrial support associates. Fine detail and internal consistency have been underemphasized for the sake of promptness so that this report could be written within a few weeks of the inception of the design.

#### GENERAL REFERENCES

MIT/IL Report E-1077

Preliminary Mod 3C Programmers Manual by R. Alonso, J. H. Laning, Jr., and Hugh Blair-Smith

MIT/IL Report E-1126

AGC Mod 3C Computer Circuits - General by A. Hopkins

UNU\_ASSI<u>FIED</u>

The design described here came about through the efforts of many people. The work was done under the general direction of Eldon C. Hall, who is in charge of the Digital Development group.

The electrical design of AGC 4 has been greatly aided by David Shansky, who has produced several circuits, including the Erasable Memory, and who has engaged in extensive negotiations with component manufacturers.

L. David Hanley carried out the unified evaluation of integrated components by redesigning sections of AGC 3 with them. Many of the present AGC 4 circuits are based on his earlier designs; the decision to change to integrated circuits was influenced by his work in a major way.

Robert Oleksiak, Robert Scott, Samuel Scott, and Edwin Smally have helped in developing memory circuits and test equipment and in formulating the AGC 4 memory cycle. Alan Green, Charles Muntz, Joseph Rocchio, and Richard Warren programmed simulations and generated display and test routines for AGC 3, which have influenced the design of AGC 4. John Deyst and Thomas Lawton first proposed the present output pulse rate generation method. Dr. J. H. Laning, Jr., who was a partner in earlier computer design efforts, devised the original key WAITLIST and EXECUTIVE routines for AGC 3.

Finally, the authors want to acknowledge the substantial contribution made to this work by Herbert Thaler of the Raytheon Missiles and Space Division. His collaboration in all of the areas of this report has made its rapid preparation possible and has stimulated the progress of the entire computer design. William Lund, also of Raytheon, has aided in later phases of the design.

#### Chapter 1

#### INTRODUCTION TO AGC 4

Because of the many similarities between AGC 3 and AGC 4, and because most of the people for whom this report is primarily intended are familiar with the characteristics of AGC 3, the essential features of AGC 4 can be discussed by comparing them with those of AGC 3.

The principal difference between the two computers is in the difference between core-transistor logic and NOR logic. In the former, a binary ONE is represented by a current path established by a transistor switch in a conductive state. Complemented variables are not generally available, and variables stored in cores are available one time only, at the time the cores are reset. In NOR logic, a binary ONE has a voltage representation. Each stage performs inversion so that complements are readily available; variables are available on a DC basis. Central registers consist of flip-flops instead of cores, and are more expensive in terms of cost, size, and power. They are faster, though, and will be operated at a  $1-\mu$ sec word rate as compared to the  $5-\mu$ sec rate of the core registers. Moreover, they may be read nondestructively and cleared without putting their contents onto the Read Bus.

The Fixed and Erasable Memories of AGC 3 are used in AGC 4. To take advantage of the faster word-transfer rate in central registers, the cycle times are reduced from an average of 19.5  $\mu$ sec to a fixed 11.7  $\mu$ sec. By fixing the memory cycle, the timing of the various control functions may be set for maximum reliability and speed.

The memory cycle is broken down into twelve steps, or time pulses, each approximately one microsecond long. Within each step, a number may be transferred from one flip-flop register to another. AGC 4 instructions consist of an integral number of memory cycle times (generally two) instead of an integral multiple of eight 5- $\mu$ sec pulse times (generally one) as in AGC 3. Because of the high cost of flip-flop registers, the number of central registers in AGC 4 is less than in AGC 3; and all of the editing registers which are not central are relocated into the Erasable Memory.

The timing of the memory cycle does not permit reading directly from memory to the Write Buses without reserving the buses for several time pulses which could otherwise be used for data transfer. For this reason, a memory-buffer register, called the "G register," is incorporated into AGC 4. The G register is loaded from Erasable or Fixed Memory before the seventh time pulse and must be prepared for writing into the Erasable Memory before the tenth.

#### **R-393 LOGICAL DESCRIPTION FOR APOLLO GUIDANCE COMPUTER 4**

UNCLASSIE

The Write Buses in AGC 4 communicate among the G, Central, input, and output registers, and the arithmetic unit. Since all of these have flip-flop storage, there is no need for a storage medium in the Write Buses such as the Write Latches of AGC 3. The Write Buses are simply multi-input amplifiers.

In AGC 3, the add time and parity-generation time were smaller than a number transfer time. In AGC 4, they are greater; consequently, the adder and parity circuits need input storage, whereas output storage was used in AGC 3. Three microseconds are allowed for additions and two for parity detection, including the time for writing in and reading out.

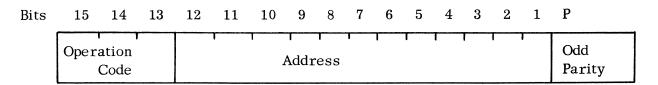

Three new instructions have been added to AGC 4: Mask, Divide, and Subtract. An extra bit is added to the three-bit operation code by causing a negative overflow to take place within an Index instruction and using the uncorrected sign bit in conjunction with the sign bit in selecting operations. Multiply, Divide, and Subtract are the three instructions which require negative overflow on Index for selection.

Table 1-1 lists some of the principal logical attributes of AGC 4 and compares these with equivalent properties of AGC 3. Certain numbers in the table, such as the numbers of counters, interrupts, and inputs and outputs, are descriptive of the guidance system interface rather than of logical limitations of the computers.

| Table 1-1. | Comparison o | of AGC 3 and | AGC 4 | Characteristics |

|------------|--------------|--------------|-------|-----------------|

|------------|--------------|--------------|-------|-----------------|

| Characteristic                                                                                  | AGC 4           | AGC 3                  |

|-------------------------------------------------------------------------------------------------|-----------------|------------------------|

| Word Length: 16 bits (15 bits + parity)                                                         |                 |                        |

| Number System: "1's" complement,<br>with overflow correction                                    |                 |                        |

| Memory Cycle Time                                                                               | 11.7 μsec       | Av. 19.5 μsec          |

| Wired-in memory (Core Rope)                                                                     | 12, 288 words   | 12, 288 words          |

| Erasable memory (Coincident current<br>Ferrite)                                                 | 1008 words      | 992 words              |

| Normal order code                                                                               | 11 instructions | 8 instructions         |

| Involuntary instructions (Interrupt,<br>Increment, Load, Start)                                 | 8 instructions  | 6 instructions         |

| Add instruction time                                                                            | 23.4 µsec       | 39 µsec                |

| $\frac{\text{Double precision Add subroutine}}{(X + x) + (Y + y) = (Z + z)}$                    | 234 µsec        | ≈ 1 msec               |

| Multiply                                                                                        | 98 µsec         | $634 \ \mu \text{sec}$ |

| Double precision multiply subroutine                                                            | 780 µsec        | ≈ 4 msec               |

| Counter incrementing                                                                            | 11.7 µsec       | 19.5 µsec              |

| Aggregate input rate at which instructions are executed at half speed                           | 43 Kpps         | 25.6 Kpps              |

| Number of counters                                                                              | 20 counters     | 20 counters            |

| Interrupt options                                                                               | 5 options       | 5 options              |

| Discrete input lines (one input bit per line)                                                   | 60 lines        | 60 lines               |

| Discrete outputs (for displays)                                                                 | 18 lines        | 18 lines               |

| Pulsed outputs under program control                                                            | 25 lines        | 25 lines               |

| Pulsed outputs not under program control                                                        | 16 lines        | 16 lines               |

| <u>Telemetry:</u> Single error correcting<br>pulse train. Output asynchronous to<br>AGC timing. |                 |                        |

| Up Link: Serial input to one register,<br>rates up to 5 words per second,<br>asynchronous.      |                 |                        |

This page intentionally left blank.

Chapter 2

#### AGC 4 SYSTEM

#### GENERAL ORGANIZATION

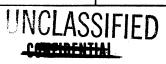

The principal structure of AGC 4 is shown in figure 2-1. The various Central registers are shown at the left of the drawing and are denoted A, Q, Z, etc. All of these are flip-flop registers, and all except B, X, Y, and P are addressable. The Central registers communicate with one another and with the rest of the computer via the Write Buses. Gating pulses for reading out of, and writing in to, the Central registers are formed in the control pulse amplifiers. For addressable registers, the gating pulses are in part dependent upon the memory selection logic.

Memory addressing is effected via the S register and the Bank register, which is used for memory bank selection. The bank register is addressable; the S register is not. Bank selection is used to choose one of ten groups of 1024 words of Fixed Memory to be the fourth of four addressable 1024 word segments of memory. This means that octal addresses 6000 to 7777 refer to one of ten groups of 1024 words, depending on the state of the Bank bits. All addresses below octal 6000 have the same meaning regardless of the state of the Bank bits. The first segment of 1024 words comprises the Central and Erasable Memories. The second and third segments are always the same two groups of fixed storage.

Whenever the Erasable or Fixed portion of memory is addressed, the information is read to the G register prior to time pulse seven. The G register (not addressable) communicates with the Write Buses in normal fashion for reading out and in one of five modes for writing in. The choice of mode depends upon the address stored in the S register. When a cycling or shifting register address is stored in S (these registers are CYR, SR, CYL, and SL), the appropriate mode is used to effect the desired editing transformation on the word being written into G for storage in the Erasable Memory; otherwise, the normal mode is used.

The S and SQ registers together add up to sixteen bits: the SQ register uses four bits, and the S register the remaining twelve bits.

Output signals are formed by logical functions of output register bits and time signals from the scaler. Input signals belong to one or both of two classes: those which appear as bits in input registers and those which request counter increments or program interrupts. Those signals belonging to the latter class operate a priority network which causes the instruction selection logic to interject an increment or interrupt sequence as

2 - 1

soon as permissible. The priority network also supplies to the Write Buses the counter address or the interrupt sequence address.

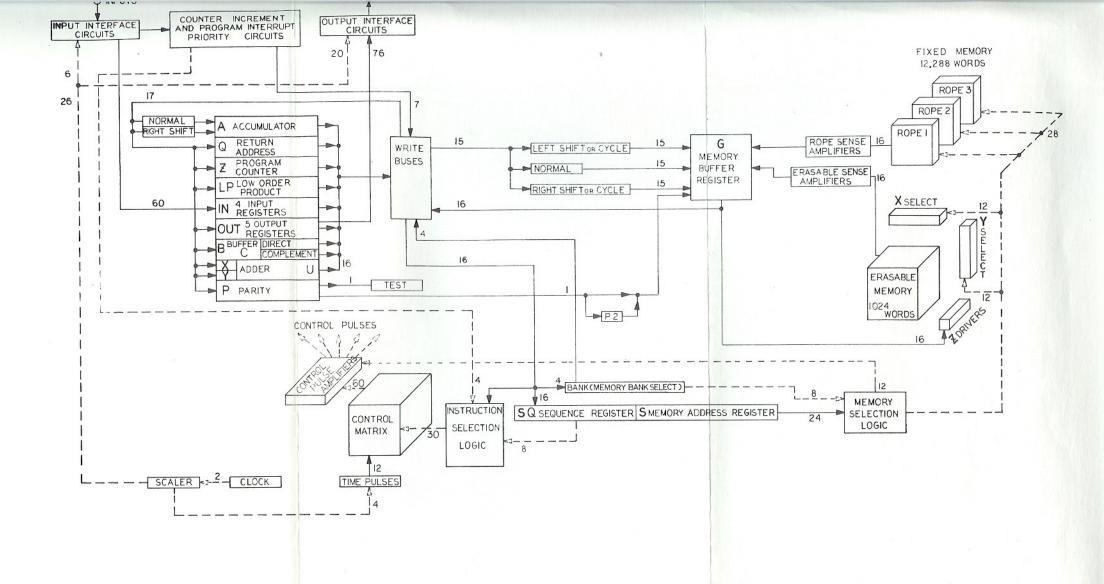

#### CLOCK AND SCALER

The oscillator for the AGC is the frequency standard for all of the APOLLO guidance and spacecraft systems. It is a 2.048 megacycle, crystal-controlled, transistor oscillator with an oven for thermal regulation. The computer uses as its clock signals four phases of the 1.024 MC square wave obtained from a binary division of the oscillator output. One more binary division produces the 512 KC signal, which serves as a synchronizing signal to the spacecraft systems clock.

The Scaler provides timing signals for the operation and synchronization of the electromechanical parts of the guidance system and for other sequential control processes with which the computer is concerned.

Figure 2-2 illustrates the organization of the clock and scaler. The 512 KC square wave is gated to the Scaler by the start-stop logic and is scaled by a factor of five to a frequency of 102.4 KC. All of its subharmonics are generated by powers of two down to 0.390625 cps, this last frequency being used to control the computer in the standby (low power) mode. Chapter 5 of this volume contains detailed information concerning the uses of the various intermediate frequencies and the method of standby operation.

Under control of the Monitor, an external ground support device, the start-stop logic can cause the scaler to halt. This permits certain aspects of real time operation to be studied at slow speed or with manual interventions.\*

The twelve time pulses are generated by means of a four-stage, gray-coded counter advanced by gated phases of the computer clock. Like the scaler, the time-pulse generator can be halted by the Monitor.

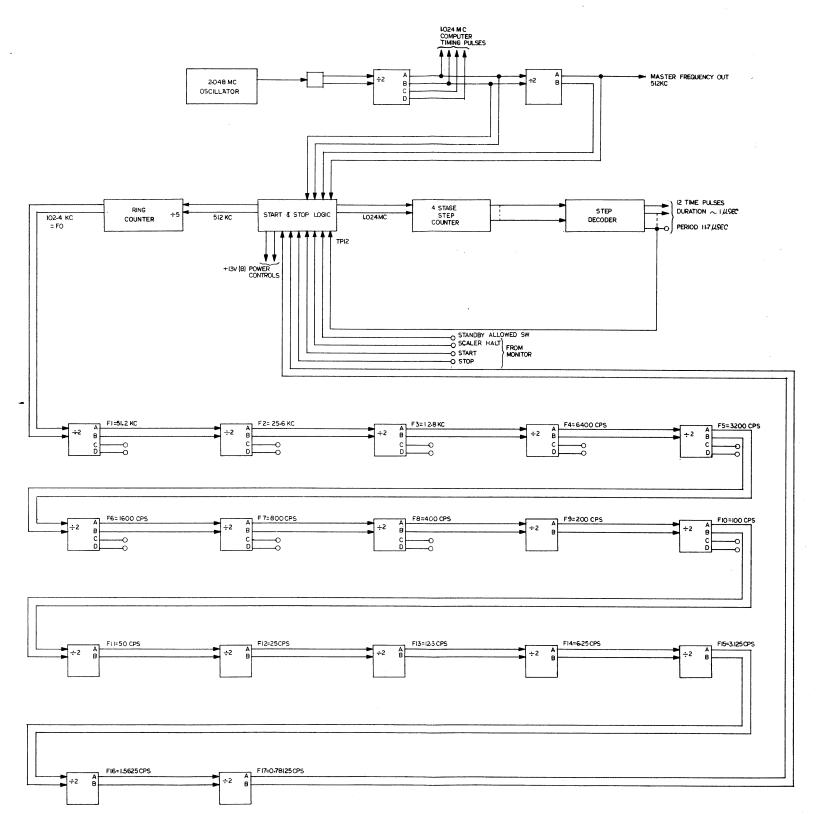

#### SEQUENCE GENERATOR

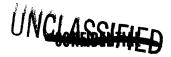

The operation of the sequence generator is functionally depicted in figure 2-3. Time Pulse 12 is reserved for instruction selection. If a new instruction is to be initiated, "read B" (RB) and "write SQ" (WSQ) control pulses are generated at Time 12. The operation code in the upper four bits of B is transferred into the SQ register, where it remains throughout the execution of the instruction. The stage counter is cleared by the coincidence of Time 12 and the absence of inputs to its first section. The contents of SQ and the stage counter uniquely select a subinstruction memory cycle, which will be executed in eleven steps unless a counter increment has been requested. In that case, the selected subinstruction is inhibited during any increment cycle servicing the counter.

\*When the Monitor is not connected to the **co**mputer, the computer is always operating in real time, either at full speed or in the standby mode.

#### NOTES:

1: SOLID ARROWS DENOTE FLOW OF NUMERICAL DATA OR OF INSTRUCTION AND ADDRESS INFORMATION, DASHED ARROWS DENOTE CONTROL SIGNALS. 2: A NUMBER WRITTEN BY AN ARROW INDICATES THE NUMBER OF SIGNAL LINES REPRESENTED BY THE ARROW.

Figure 2-1. General Block Diagram.

D R-393 LOGICAL DESCRIPTION FOR APOLLO GUIDANCE COMPUTER 4

Figure 2-2. Clock and Scaler Block Diagram.

UNCLASSIFIED

2-5/2-6

Figure 2-3. Sequence Generator Block Diagram.

Figure 2-3. Sequence Generator Block Diagram.

2-7/2-8

The following Time 12 does not disturb SQ or the stage counter in order that the selected instruction be executed after all counter requests are fulfilled.

If an instruction consists of more than one memory cycle, as is true of all but TC and the three counter incrementing sequences, the stage counter is advanced by control pulses (ST1, ST2, TRSM, CTR) at some time during the first 11 time pulses; and a transfer to the "B" section of the stage counter occurs at Time 12.

A Control pulse is generated as the logical sum of a subset of the matrix crosspoints. A crosspoint, in turn, is the logical product of a subinstruction variable and a time pulse, and may produce as many as five control pulses by driving five different logical sum circuits.

Branching is effected by storing the result of a test in a flip-flop and using the flipflop outputs to inhibit certain crosspoints. In some instances, two branch conditions are stored simultaneously, thereby permitting a selection from among four crosspoints at one time of one subinstruction. In figure 2-3, the four branch tests are indicated setting BR1 or BR2 for their various conditions.

#### CENTRAL PROCESSING SECTION

The circuits which constitute the Central registers, input and output registers, the G and S registers, and the Write Buses, are physically organized into sixteen identical, interchangeable units called "bit sticks." Each bit stick contains one bit of each register and its connections to and from the Write Buses. The sixteen bit sticks, together with a few others, constitute the Central Processing Section, about half of the micrologic part of the computer.

The AGC adder is a 16-bit parallel adder with end around carry. It operates in a modified "1's" complement system in which the sign bit is processed in two adjacent columns. The two sign columns of the sum are identical unless overflow occurs on the addition. If overflow does occur, the leftmost sign bit is the same as the original sign of the operands; and it is adopted as the sign (SG) of the sum. Thus it can be said that sign is preserved on overflow.

Some of the arithmetic and logical machine processes require preservation of the rightmost sign bit, the uncorrected sign (US). For this reason, the A, Q, Z, LP, and B registers contain columns for storage of the uncorrected sign. These registers have no parity bit position; hence, the bit stick which contains the parity positions of the G and Output registers also contains the US positions of the other Central registers and of the Write Buses.

Since words coming from Erasable or Fixed Memory contain no overflow information, all transfers from G to the Central registers duplicate the sign of G into the US position of the Write Buses.

The functions of the various Central registers are given in detail in chapter 3 of this volume. Briefly, the arithmetic is all done in the adder, which has flip-flop storage for two operand words X and Y. The correct sum of X and Y is present at the output of the sum circuit U within three microseconds of the time at which the read-in of the second operand (always X) occurs. It is also possible to add one to a positive number in X or Y by means of a "Carry In" (CI) control pulse. Three microseconds are sufficient for generating the correct sum in this case, too.

The B register is primarily for temporary storage. The C register is fictitious; C is the complement side of the B register. The A register is also used for temporary storage. It is called the accumulator and retains data from one instruction to the next. The LP register, together with the A register via right shift gates, forms a doublelength shifting accumulator for multiplication.

The input and output registers are flip-flop registers whose assignments and functions are described in chapter 5.

Table 2-1 is a list of Special registers, including addressable Central registers, their octal addresses, and their physical locations.

| OCTAL<br>ADDRESS | REGISTER<br>NAME  | LOCATION                 | OCTAL<br>ADDRESS | REGISTER<br>NAME | LOCATION   |

|------------------|-------------------|--------------------------|------------------|------------------|------------|

| 0000             | A                 |                          | 15               | Bank             | Located in |

| 1                | Q                 |                          | 16               | Relint >         | Service    |

| 2                | Z                 |                          | 17               | Inhint           | Sticks     |

| 3                | LP                |                          | 0020             | CYR              |            |

| 4                | IN0               |                          | 21               | SR               |            |

| 5                | IN1               |                          | 22               | CYL              | Located in |

| 6                | IN2               | Located in<br>Bit Sticks | 23               | SL               | Erasable   |

| 7                | IN3               |                          | 24               | ZRUPT            | Memory     |

| 0010             | OUT0              |                          | 25               | BRUPT            |            |

| 11               | OUT1              |                          |                  | (RIP)            |            |

| 12               | OUT2              |                          | 26               | ARUPT            |            |

| 13               | OUT3              |                          | 27               | QRUPT            |            |

| 14               | OUT4<br>(DOWNTEL) |                          |                  |                  |            |

Table 2-1. AGC 4 Special Registers

UNCLASSIFIED

## UMEROSIFIED

#### MEMORY OPERATION

The signals which operate the Erasable and Fixed Memories are generated during every subinstruction (with two exceptions) as functions of the time-pulse generator, the clock, and the contents of the S and Bank select registers. If the S register contains the address of a flip-flop register, neither memory is operated; if not, then only the appropriate memory is operated. The memory is not operated during the Multiply and Divide repetitive loops, MP1 and DV1.

Chapter 4 contains further details of memory selection and timing.

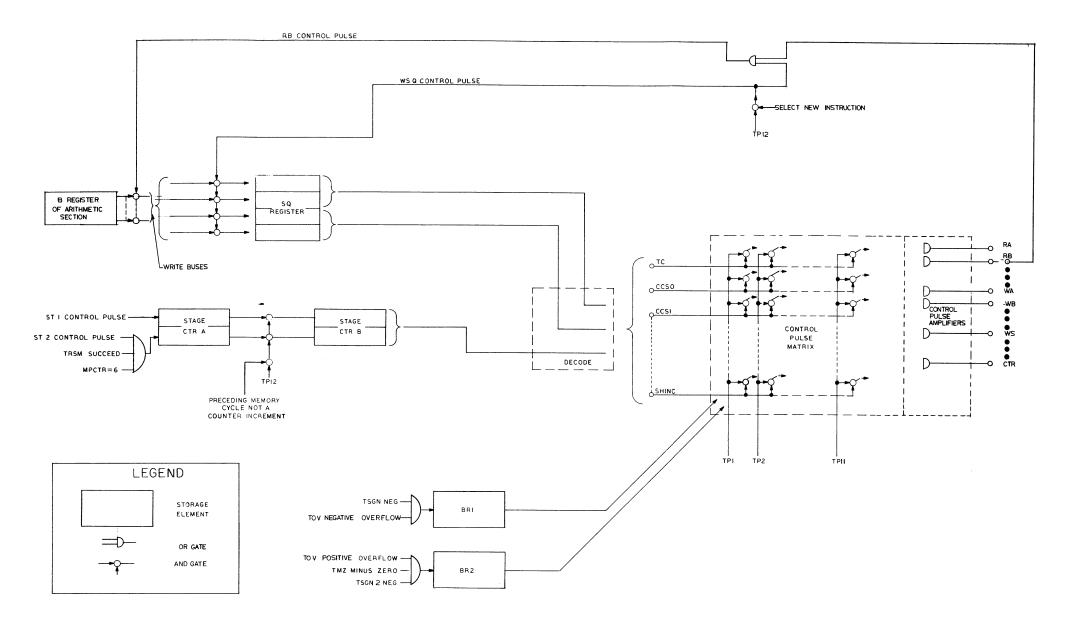

#### PARITY TEST AND GENERATION

The purpose of the parity circuit is to ensure that the numbers stored in Erasable and Fixed Memory are read correctly. Single errors and all other odd multiple errors cause an alarm to be signalled to the computer and the display panel. The parity bit is chosen so that the number of "1's" in a word is odd. In Fixed Memory, this bit is wired in along with the rest of the information. In Erasable Memory, it must be generated each time a new word is stored. It is convenient, in fact, to generate a new parity bit each time a word is read so that any wrong parity indication will not persist. In the Special registers, no parity test is made because of the difficulty of generating the parity bit for words produced by arithmetic, logical, and editing operations.

Figure 2-4 illustrates the flow of parity information. A single circuit, called a "pyramid," is sufficient to generate and test a parity bit. If "read G" (RG) and "write P" (WP) gates are on at the same time, the pyramid produces even number indications of the incoming word, both with and without the parity bit. These two indications are called the P-15 and 1-15 indications, respectively. If the source of the word is not G, then both outputs produce a 1-15 indication.

The parity output of G has only a single destination, which is the write gate of the P register. The position in the Write Buses corresponding to the parity bit is used for the uncorrected sign, as mentioned in the Central Processing Section of this chapter, and receives the SG bit from G.

During memory cycles in which information is brought from memory, the process of parity testing is initiated by RG and WP control pulses. A later Test Parity (TP) pulse generates an alarm if an even number of "1's" was written into P.

When no new information is being written into Erasable Memory, the word just read is regenerated except for the parity bit. The latter is generated by the 1-15 indication of the pyramid and gated into the G register by a Generate Parity (GP) control pulse.

When a new word is stored, the same method is used except in the Exchange instruction. There, it is necessary to store the generated parity bit while the pyramid is used to test another incoming word. The P2 register serves that purpose. A Read P2 (RP2) control pulse produces the same result from P2 as does GP from the 1-15 indication.

Finally, for Down telemetry, it is required to store a parity bit in the OUT4 register; there is a special gate which is enabled only when OUT4 is addressed. This gate transmits the parity bit as required.

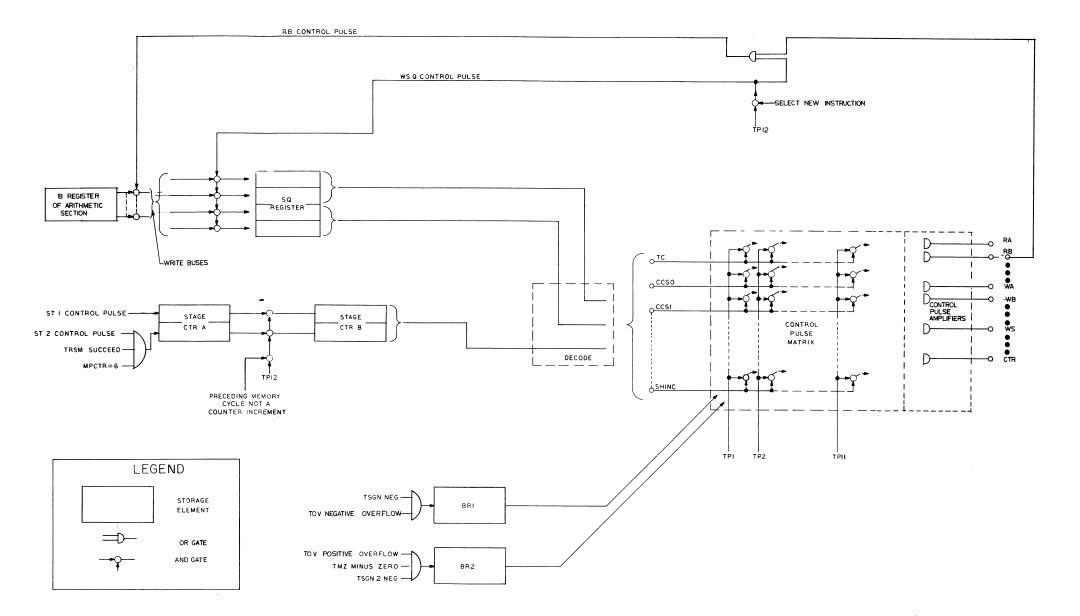

#### COUNTER INCREMENTING

Counters in AGC 4 are addressable registers in the Erasable Memory. The inputs to these counters are trains of pulses which are first stored in a special set of circuits called a Priority Chain. The Priority Chain is shown symbolically in figure 2-5. The cells labeled  $P_1$ ,  $P_2$ ,  $P_3$ , ...,  $P_{20}$ , each represents a pair of flip-flops and some extra gates; each flip-flop stores one of the two possible incoming pulses (e.g., a pulse for increment or a pulse for decrement). If either flip-flop of  $P_i$  is set to "1", which means that the counter i is to be serviced, then a "1" is transmitted through gate  $G_i$  into the Counter Address Generation Network; and all other gates  $G_j$ , where J > i, are blocked. Gate  $G_i$  will transmit a "1" into the Counter Address Generation Network only if no other earlier counter  $G_k$ , where k < i, requires processing.

Should simultaneous requests be made, the counters are serviced in preassigned order, hence, the name "Priority Chain."

The cells  $P_i$  each have two outputs, such as  $C_i +$ ,  $C_i -$ , or  $C_i +$ ,  $C_iS$ . These outputs are "1" if the corresponding storage flip-flops are <u>on</u>, and if the corresponding gages  $G_i$  are not blocked.

The signals  $C_i +$ ,  $C_i -$ , and  $C_iS$  are grouped into three OR gates; the outputs from these OR gates go to the Sequence Generator, where they are used in the selection of a PINC, MINC, or SHINC sequence.

When an increment is received, the address of the appropriate Erasable register is supplied through the Address Generation Network; information for the selection of the appropriate sequence is provided to the Sequence Generator; and activity relating to all counters of lower priority is inhibited temporarily. Inputs to lower priority counters are not lost, however, since they are stored in the P cells.

**MARKANSSIFIED** R-393 LOGICAL DESCRIPTION FOR APOLLO GUIDANCE COMPUTER 4 2 3 3 4 4 4 5 5 5 6 6 6 7 7 7 8 8 8 9 9 ALARM -9 à 10 10 ю 11 H П 12 12 12 13 13 13 14 14 14 SG Р US ≁ Ρ SG SG P REGISTER G WRITE BUSES REGISTER RG w'n POSITION P OF OUT 4 Р C (S)=0014 P2 REGISTER WP2 RP2 GP

Figure 2-4. Parity Test and Generation Block Diagram.

UNCOMBOTTED

2-13/2-14

CONTRACTASSIFIED

#### **R-393 LOGICAL DESCRIPTION FOR APOLLO GUIDANCE COMPUTER 4**

Figure 2-5. Priority System for Counters.

2-15/2-16

2 - 17

When the Sequence Generator reaches the end of a memory cycle, a test is made to see if any of PINC, MINC, or SHINC are requested. If so, the outputs of all P cells are temporarily (3  $\mu$ sec) prevented from changing state; and the counter address and proper sequence are recorded in the address register S and in the Sequence Generator, respectively. Blocking the changes of state of outputs of all P cells is necessary in order to prevent an ill-timed input pulse from changing a counter address in the middle of the sampling period. Such an incoming pulse is not lost, however, since there are holding flip-flops before the blocking gate inside the P cells.

The counter to be serviced is then incremented after the end of a memory cycle, essentially by inserting an incrementing memory cycle before proceeding with the next 'normal' cycle called for by the instruction being executed.

If more than one counter input is to be serviced, the counters are incremented in order of descending priority until there are no further increments to be made. The same test made at the end of "normal" memory cycles is made at the end of an incrementing cycle. The only thing not "normal" about an incrementing cycle is that it was not called for by an instruction.

A detailed description of the steps of PINC, MINC, and SHINC are found in chapter 3.

While normal computations proceed at half speed, AGC 4 is capable of an aggregate counting rate of about 42 Kpps. The relationship between counting rate and computing speed is an inverse one; if the aggregate input rate is about 21 Kpps, the computing speed is 75% of maximum.

It is difficult to speak of maximum counting rate for counters in an absolute sense. If there are no other counters receiving inputs, then a given counter will lose no counts if its inputs are below 80 Kpps. It is also true that no pulses will be lost if <u>all</u> counters receive simultaneous inputs which are at least 240  $\mu$ sec apart (about 4 Kpps). In both of the above cases, however, no computing other than counting would be done, since the end of every memory cycle would find a new request for servicing a counter.

If a counter input circuit P receives simultaneous plus and minus inputs, a single incrementing cycle occurs which increments the counter by zero; i.e., there is no net change in the contents of that counter.

A 20-counter system requires about 250 NOR gates, including those necessary for generating the address of the counter.

**UNGLASSIE**

#### PROGRAM INTERRUPTION

The normal sequence of instructions can be interrupted by a certain kind of signals called RUPT's (for interrupts). These signals are derived from certain other signals, which go to INBITS, or by the overflow of some counters. (See chapter 5.) The Priority Chain associated with RUPT's is much the same as that of the counters, but the resulting actions are more complicated for RUPT's than for increments.

A RUPT causes a transfer of control to some prespecified program. At the end of that program, a RSM (for resume) sequence takes place, which sets the AGC arithmetic and control units back to the exact state they were in at the time of interruption. To do this, the RUPT sequence must preserve, and store in a safe place, the contents of B and Z; the interrupting program further preserves A and Q.

Interrupts themselves cannot be interrupted. If an interrupting program is in progress, and a RUPT signal comes in at this time, the new request is preserved and acted upon only after the original interrupting program has ended and the RSM sequence has taken place.

It is sometimes desirable to inhibit interruptions for a brief period. This can be done by the instruction INDEX INHINT. The address INHINT (octal 0017) is interpreted as meaning that RUPT signals should not be processed until further notice. "Further notice" is defined as the instruction INDEX RELINT (for Release Interrupt). Address RELINT is octal 0016. The inhibition of interrupts is used sometimes when dealing with input and output registers.

#### WAITLIST AND EXECUTIVE PROGRAMS\*

One of the most important problems in general purpose control computers is that of starting and stopping programs for which real time is a variable. The WAITLIST and EXECUTIVE programs should, for this reason, be considered to be an integral part of AGC 4. These programs do not presently exist for AGC 4, but they do exist for AGC 3; the differences between the two versions are expected to be minor.

The descriptions given below, although superficial, are included in order to give some idea as to the nature of such programs.

<sup>\*</sup>Both WAITLIST and EXECUTIVE programs were first written by J. H. Laning, Jr., for the Mod 3C Computer, later AGC 3.

#### WAITLIST

This program allows a desired subroutine, called "task," to be entered at a specified future time. The format for such requests is as follows:

| L     | ХСН         | $\Delta T$ |

|-------|-------------|------------|

| L + 1 | ТС          | WAITLIST   |

| L + 2 | TASKADDRESS |            |

The contents of register  $\Delta T$  is a time interval  $\Delta t$ , the time from "now" at which the desired task is to be executed by means of an interrupt. The contents of L + 2, "TASKADDRESS," is the fourteen-bit address of the desired task. As a matter of convention, "tasks" refer to programs executed by WAITLIST, while "jobs" refer to programs under control of the EXECUTIVE, described in the next section. After making the request, the program continues at L + 3.

There may be up to seven different task requests waiting to be processed at one time. If two of these tasks should happen to request the same time of execution, then the first one requested is executed first; and the second one as soon as the first task is completed. The end of a task is signalled by the instruction TC TASKOVER. The program TASKOVER sees to it that any additional tasks requested for that time are executed before resuming the interrupted program.

The WAITLIST routine makes use of the Time 3 counter, which is incremented at the rate of 100 pps. A task request essentially results in presetting Time 3 so that it will overflow at the proper time. When Time 3 overflows, it triggers the T3RUPT interrupt. The interrupt program then determines which task is called for at this time and takes appropriate action, after which it resumes the original at the point of interruption. A common type of action is to enter a job request into the executive system of routines (of which EXECUTIVE and WAITLIST are a part). This last is done to avoid lengthy interrupting programs which, in turn, prevent other interrupting signals from being serviced.

A task request may be self-perpetuating. After a task is done, but before transferring to TASKOVER, a new request is made for the same task to be executed  $\Delta t$  seconds ahead.

#### EXECUTIVE

This program will arrange the order of processing of up to seven independent programs, each of which has a preassigned priority ranking. The AGC 4 programs will have certain points at which the EXECUTIVE can suspend that program's computations and initiate processing of a program of higher priority. When the higher priority job is

done, the interrupted job is resumed. Unlike the "hardware" priority circuits, the EXECUTIVE will allow for the interruption of interrupted programs. To initiate a job, programs FINDVAC or NOVAC are used in the interrupt mode or with interrupt inhibited. FINDVAC is used if the job desired is written in interpretive language or uses a vector accumulator; NOVAC is used if the job requested does not use a vector accumulator and is in basic language.

Entry into the EXECUTIVE is via the sequence:

| L            | XCH     | PRIO    |

|--------------|---------|---------|

| $\int L + 1$ | TC      | FINDVAC |

| L + 1        | TC      | NOVAC   |

| L + 2        | JOBADDR | RESS    |

c(PRIO) is a priority designation for the job, and c(L + 2) = JOBADDRESS is the fourteen-bit address of the requested job. After making the request, the program continues at L + 3.

To terminate a job, it should end with the instruction TC ENDOFJOB if the job written in was basic AGC language, or with the interpretive instruction RTB ENDJOB1 if the job was written in interpretive. "RTB" stands for "Return to Basic."

All AGC programs which qualify as jobs have, at suitable points, the instructions:

| L            | CCS | NEWJOB |                                  |

|--------------|-----|--------|----------------------------------|

| $\int L + 1$ | TC  | CHANG1 | (if present job is basic)        |

| L + 1        | TC  | CHANG2 | (if present job is interpretive) |

This pair of instructions allows the EXECUTIVE to replace the present job with one of higher priority, if one exists.

The time required for the EXECUTIVE for AGC 4 is not known exactly at this time. Assuming, however, that the AGC 4 program is like that for AGC 3, then the speeds are approximately as follows:

|         | AGC 3        | AGC 4           |

|---------|--------------|-----------------|

| NOVAC   | (27 + 7P) I  | 2(27 + 7P) MCT  |

| FINDVAC | (40 + 7P) I  | 2(40 + 7P) MCT  |

| CHANG2  | 50 I         | 100 MCT         |

| ENDJOB1 | (91 + 11P) I | 2(91 + 11P) MCT |

where: P is the number of jobs outstanding. I is the AGC 3 instruction time (40  $\mu$ sec). MCT is the AGC 4 Memory cycle time (12  $\mu$ sec).

#### Chapter 3

#### AGC 4 INSTRUCTIONS

#### GENERAL REMARKS

There are eighteen sequences in the repertoire of AGC 4: eight basic instructions, three extracode instructions, four unprogrammed sequences, a special case of one of the basic instructions (resume), and two sequences that operate under control of the system test equipment. The last two are of no concern to programmers and are mentioned here only for completeness.

Each sequence consists of one or more subsequences lasting one memory cycle time (MCT). 1 MCT is nominally 12  $\mu$ sec; actually it is a little less.

The format of an instruction word is:

In the notation of this memo, L is the address of the location from which the instruction is taken. For any register or location K, c(K) denotes the contents of K; b(K) denotes initial ("b" is for "before") contents of K wherever the distinction clarifies the discussion. The results of addressing special registers referenced explicitly by instructions are given in the "Special Cases: Implied Address Codes" section of this chapter.

Table 3-1 shows the special registers, excluding unaddressable central registers. A, Q, Z, and LP figure prominently as arithmetic or control registers. It should be noted that an initial condition for an instruction in L is bits 12 - 1 of C(Z) = L + 1. Normally bits 16-13 of C(Z) are zero. Table 3-2 shows how the registers are written into. Note particularly that A has two independent sign bits. When a word is brought into A from Fixed or Erasable Memory, its sign bit goes into both positions. When C(A) is stored in Erasable Memory, bit 16 is stored as the sign. The quantity stored is said to be overflow-corrected because, if bits 16 and 15 of C(A) had become different due to an arithmetic overflow, the stored sign is that of the operands of the overflow-ing addition. One implication of these facts is that overflow is not so much an event as it is a class of quantity retainable in a special register; the descriptions in the next section treat it accordingly.

| OCTAL<br>ADDRESS | REGISTER<br>NAME |                        | OCTAL<br>ADDRESS | REGISTER<br>NAME    |

|------------------|------------------|------------------------|------------------|---------------------|

| 0000             | A                |                        | 0020             | CYR                 |

| 1                | Q                |                        | 21               | SR                  |

| 2                | Z                |                        | 22               | CYL                 |

| 3                | LP               |                        | 23               | SL                  |

| 4                | INO              |                        | 24               | ZRUPT (In Erasable) |

| 5                | IN1              | Flip-Flop<br>Registers | 25               | BRUPT (RIP)         |

| 6                | IN2              |                        | 26               | ARUPT               |

| 7                | IN3              |                        | 27               | QRUPT               |

| 0010             | OUT0             |                        | 0030-56          | COUNTERS            |

| 11               | OUT1             |                        |                  |                     |

| 12               | OUT2             |                        |                  |                     |

| 13               | OUT3             |                        |                  |                     |

| 14               | OUT4             |                        |                  |                     |

| 15               | Bank J           |                        |                  |                     |

| 16               | Relint           | No bits in             |                  |                     |

| 17               | Inhint           | these registers        |                  |                     |

Table 3-1. AGC 4 Special Registers

UNCLASSIE

#### Table 3-2. How Registers are Written Into in AGC 4

#### REGISTER BIT POSITION

| UNCLASSIFIED | Write<br>Pulses     | REG.           | 16   | 15   | 14   | 13     | 12     | 11    | 10     | 9    | 8     | 7     | 6     | 5     | 4     | 3        | 2        | 1        | Comments                |

|--------------|---------------------|----------------|------|------|------|--------|--------|-------|--------|------|-------|-------|-------|-------|-------|----------|----------|----------|-------------------------|

|              | WA<br>W0            | A              | SG   | US   | 14   | 13     | 12     | 11    | 10     | 9    | 8     | 7     | 6     | 5     | 4     | 3        | 2        | 1        |                         |

|              | WALP                | А              | SG   | SG   | US   | 14     | 13     | 12    | 11     | 10   | 9     | 8     | 7     | 6     | 5     | 4        | 3        | <b>2</b> |                         |

|              | WQ W1               | Q              | SG   | US   | 14   | 13     | 12     | 11    | 10     | 9    | 8     | 7     | 6     | 5     | 4     | 3        | <b>2</b> | 1        |                         |

|              | WZ $W\overline{2}$  | Z              | SG   | US   | 14   | 13     | 12     | 11    | 10     | 9    | · 8   | 7     | 6     | 5     | 4     | 3        | <b>2</b> | 1        |                         |

|              | WLP $\overline{W3}$ | LP             | 1    | 1    | -    | 14     | 13     | 12    | 11     | 10   | 9     | 8     | 7     | 6     | 5     | 4        | 3        | 2        |                         |

|              | WALP -              | LP             | -    | -    | 1    | -      |        | -     | -      | -    | -     | -     | -     | -     | -     | -        | -        | -        |                         |

|              | WB                  | В              | SG   | US   | 14   | 13     | 12     | 11    | 10     | 9    | 8     | 7     | 6     | 5     | 4     | 3        | 2        | 1        |                         |

|              | W10-<br>W14         | OUT0 -<br>OUT4 | SG   | Р    | 14   | 13     | 12     | 11    | 10     | 9    | 8     | 7     | 6     | 5     | 4     | 3        | 2        | 1        |                         |

|              | SBE WG<br>SBF       | G              | SG   | Р    | 14   | 13     | 12     | 11    | 10     | 9    | 8     | 7     | 6     | 5     | 4     | 3        | 2        | 1        | Memory into G           |

|              | W20                 | G              | 1    | -    | SG   | 14     | 13     | 12    | 11     | 10   | 9     | 8     | 7     | 6     | 5     | 4        | 3        | 2        | Information into CYR    |

|              | $W\overline{21}$    | G              | SG   | -    | SG   | 14     | 13     | 12    | 11     | 10   | 9     | 8     | 7     | 6     | 5     | 4        | 3        | 2        | Information into SR     |

|              | W22<br>W23          | G              | 14   | -    | 13   | 12     | 11     | 10    | 9      | 8    | 7     | 6     | 5     | 4     | 3     | <b>2</b> | 1        | SG       | Information into CYL    |

| G            | W23                 | G              | SG   | -    | 13   | 12     | 11     | 10    | 9      | 8    | 7     | 6     | 5     | 4     | 3     | <b>2</b> | 1        | SG       | Information into SL     |

|              | WS                  | S              |      |      |      |        | 12     | 11    | 10     | 9    | 8     | 7     | 6     | 5     | 4     | 3        | <b>2</b> | 1        |                         |

|              | WX                  | Х              | SG   | US   | 14   | 13     | 12     | 11    | 10     | 9    | 8     | 7     | 6     | 5     | 4     | 3        | <b>2</b> | 1        |                         |

|              | WY                  | Υ              | SG   | US   | 14   | 13     | 12     | 11    | 10     | 9    | 8     | 7     | 6     | 5     | 4     | 3        | 2        | 1        |                         |

|              | WP1                 | P1             | SG   | Р    | 14   | 13     | 12     | 11    | 10     | 9    | 8     | 7     | 6     | 5     | 4     | 3        | <b>2</b> | 1        | For Test Parity         |

|              | WP2                 | P2             | SG   | -    | 14   | 13     | 12     | 11    | 10     | 9    | 8     | 7     | 6     | 5     | 4     | 3        | <b>2</b> | 1        | For Generate Parity     |

|              | WBK                 | BNK            | -    | -    | 14   | 13     | 12     | 11    | -      | -    | -     | -     | -     | -     | -     | -        | -        | -        |                         |

|              | WSQ                 | SQ             | SG   | US   | 14   | 13     | -      | -     | -      | -    | -     | -     | -     | -     | -     | -        | -        | -        |                         |

| -            | Tabl                | e entries      | show | whic | h Wr | ite La | atch c | onneo | ets to | that | : Reg | giste | er Bi | t Pos | sitio | n        |          |          | P = Parity<br>SG = Sign |

SG = SignUS = Uncorrected Sign

3-3

2 g \$

#### BASIC INSTRUCTIONS

These eight instructions are called basic because, unlike the extracodes, they are completely specified by an instruction word. The code number accompanying each description is the octal digit in bits 15-13 of the instruction word.

Code 0. L: TC K Transfer Control 1 MCT Set C(Q) = TC L + 1; Take next instruction from K, and proceed from there.

Code 1. L: CCS K Count, Compare, and Skip 2 MCT Set C(A) = DABS [C(K)], where the DABS function (Diminished Absolute Value) of an integer α is defined as =

DABS(

$$\alpha$$

) =  $|\alpha|$  - 1, if  $|\alpha|$  > 1

+ 0, if  $|\alpha| \leq 1$ ;

Set C(K) = b(K);

Take next instruction from L + n, and proceed from there, where

n = 1 if C(K) > 0 n = 2 if C(K) = +0 n = 3 if C(K) < 0n = 4 if C(K) = -0.

Remarks: K may not be in Fixed Memory; a parity error and wrong answer would result. This is no restriction because nothing is gained by testing the contents of Fixed Memory.

> If K is a flip-flop register, the sign bit (position 16) is tested. Note that for any quantity  $\alpha$ ,  $\alpha - \alpha = -0$  in "1's" complement notation.

Code 2. L: INDEX K (K  $\neq$  0025) Index 2 MCT

Use the sum of C(L + 1) + C(K) as the next instruction just as if that sum had been taken from L + 1; set C(K) = b(K). Final C(L + 1) = b(L + 1).

UNCLASSIFIED

Remarks: One of eight operation codes distinct from the basic set results if the sum contains an overflow. Three of these (the extracodes) are used; interrupt cannot occur at the end of an INDEX that overflows.

Code 2. L: RESUME ( = INDEX 25 ) Resume 2 MCT Set C(Z) = C(24);

Enable further interrupts.

Use C(25) as the next instruction.

Remarks: This brings about resumption of an interrupted program because the interrupt sequence stores in 24 (ZRUPT) the contents of Z at the time of interruption and in 25 (BRUPT) the contents of B at that time. Interrupt occurs between instructions, at which time C(B) is the upcoming instruction and C (Z) is L' + 1, where L' is the address of the source of C(B). Notice that RESUME is INDEX 25 and not TC 25.

Code 3. L: XCH K Exchange 2 MCT Set C(A) = b(K); Set C(K) = b(A) unless K is in fixed memory; Take next instruction from L + 1.

Code 4. L: CS K Clear and Subtract 2 MCT Set C(A) = -C(K); Set C(K) = b(K); Take next instruction from L + 1. Remarks: The minus sign, here and elsewhere, indicates "1's" complement.

Code 5. L: TS K Transfer to Storage 2 MCT

Set C(K) = b(A);

If b(A) contains no overflow, C(A) = b(A);

Take next instruction from L + 1;

If b(A) contains overflow, take next instruction from L + 2 and set

UNC ACCOUNT OF THE HAL

C(A) = 000001 for positive overflow, or

C(A) = 177776 for negative overflow

(The leftmost digit is binary, representing the sign bit. The uncorrected sign bit is accounted for in the digit second from left.

Remarks: The "skip on overflow" feature of TS is used chiefly in double precision arithmetic.

#### Code 6. L: AD K Add 2 or 3 MCT

Set C(A) = b(A) + C(K);

Set C(K) = b(K);

Take the next instruction from L + 1.

Remarks: If C(A) contains positive (negative) overflow after the addition, the overflow counter OVCTR (octal address 0034) is incremented (decremented) by one, which accounts for the third MCT. Also, an interrupt can never occur while C(A) contains an overflow. The effect on OVCTR is an explicit property of the AD and SU instructions and not of overflows in general.

Code 7. L: MASK K Mask 2 MCT Set C(A) = b(A)  $\bigwedge$  C(K); C(K) = b(K) Remarks: " $\bigwedge$ " is the Boolean operator AND applied in each bit position.

#### EXTRACODE INSTRUCTIONS

These three instructions are formed by overflow of the addition in INDEX. They cannot be completely stored in memory, but conventional octal codes are stipulated, assuming a conventional way of causing the overflow. If no address modification is desired, this will be done by an EXTEND instruction which is simply INDEX 5777. The programmer is responsible for supplying in 5777 the octal constant 47777. If address modification of an extracode instruction is desired, the technique is to index by the sum of octal 47777 and the modifying quantity. This implies that, if an argument address is used several times to modify extracode instruction addresses, indexing of extracodes is virtually free. (See the examples of double-precision multiplication.)

In the following descriptions, the conventional octal code is shown as the code number; but it is understood that the code does not have the meaning shown unless it is preceded by the proper INDEX 5777 instruction.

Code 4. L: MP K Multiply 10 MCT Set  $C(A, LP) = b'(A) \times C(K)$ ; Take next instruction from L + 1. Remarks: b'(A) is the overflow-corrected form of b(A); that is, overflow in b(A) is ignored. The high-order product in A and the low-order product in LP (address 0003) agree in sign, which is determined strictly by the sign bits of the operands, even if one or both operands is zero. C(K) = b(K) except when K = A or K = LP.

Code 5. L: DV K Divide 18 MCT

Set C(A) = b(A) / C(K);

Set C(Q) = - Remainder ;

Set C(LP) > 0 if quotient is positive,

< 0 if quotient is negative;

Take next instruction from L + 1.

Remarks: |b(A)| should be less than |C(K)|, although equal magnitudes are permissible if used very carefully -|C(A)| = 37777 and C(Q) = -|C(K)| in this case. If |b(A)| > |C(K)|, |C(A)|= 37777 and C(Q) is meaningless. Therefore, b(A) must not contain an overflow. C(K) = b(K) except when K = A, Q, or LP.

Code 6. L: SU K Subtract 4 or 5 MCTSet C(A) = b(A) - C(K);

Set C(K) = b(K);

Take next instruction from L + 1.

Remarks: This instruction is identical to AD in all other respects.

## SPECIAL CASES; IMPLIED ADDRESS CODES

The descriptions in the foregoing "Basic Instructions" and "Extracode Instructions" sections assume that the address K is in nonediting Erasable or in Fixed Memory, except as noted. The phrase "Set C(K) = b(K)" appears in most of the descriptions as a shorthand indication that C(K) remains unchanged unless:

- 1. K = LP, CYR, SR, CYL, or SL, in which case b(K) is edited by one of the editing functions shown in table 3-2 to produce the final C(K).

- 2. K is the address of one of the central registers always used by the instruction. It is not obvious in this case how the instruction behaves.

There is an exception to Rule 1 in MASK, MP, and DV, as stated in their descriptions. Also, in the very unlikely case that an instruction is taken from an editing register, Rule 1 holds for the instruction except for the instruction executed after a CCS. The function of this section is to state the implications of Rule 2 for each instruction.

The following can also be considered as a list of special instructions. The mnemonic of the instruction is on the left, and the means for getting it executed is explained on the right-hand text.

- RESUME, which is done by INDEX 25; this is a unique combination because it actually performs a special pulse sequence during the second MCT; and

- EXTEND, done by INDEX 5777.

Three more are defined which do not have to do with the consequences of Rule 2:

- INHINT, done by INDEX 17, which inhibits interrupt until further notice;

- RELINT, done by INDEX 16, which enables or "releases" interrupt (no storage is associated with addresses 16 and 17, which behave as if they always contained +0, so that neither INHINT nor RELINT affects the next instruction); and

- XAQ, done by TC A, the mnemonic being "Execute C(A) using Q." The action is straightforward, but it appears to do an out-of-line execution of C(A) because Q follows A in the address pattern. In nearly all cases, it is better to write

an important exception being the case that the instruction in A is a TC.

# UNCLACOUFIED

The remaining special actions are introduced as they come up in the following paragraphs, which discuss the consequences of Rule 2.

TC uses Z and Q. TC Z is not useful. TC Q is useful and is represented by the mnemonic code RETURN. Let b(Q) = TC K, then the action of TC Q is, in 2 MCT:

Set C(Q) = TC 2;

Take next instruction from K, and proceed from there.

Remarks: Not useful if b(Q) is not a TC; see cautionary note under TCAA (TS Z).

CCS uses Z and A. CCS Z might be useful; its action is, in 2 MCT:

Set C(A) = TC L;

Take next instruction from L + 1.

CCS A is definitely useful; its action is, in 2 MCT:

Set C(A) = DABS [b(A)];

Take next instruction from L + n, and proceed from there,

where

n = 1 if b(A) > 0,

n = 2 if b(A) = +0,

n = 3 if b(A) < 0,

n = 4 if b(A) = -0.

Remarks: Bit 16 is regarded as the sign. The DABS function is computed on the full 15 bits and sign of b(A), so that C(A) contains an overflow if  $|b(A)| \ge 40001$ .

INDEX uses Z. INDEX Z might be useful for a small program to operate anywhere in Erasable Memory; its action is, in 2 MCT:

Use the sum of C(L + 1) + L + 1 as the next instruction just as if that sum had been taken from L + 1.

XCH uses Z and A. XCH Z might be useful. Let b(A) = TC K; then the action of XCH Z is, in 2 MCT:

Set C(A) = TC L + 1;

Take next instruction from K, and proceed from there.

OTIOLADOIT

Remarks: The effect is the same if b(A) is not a TC; but see cautionary note under TCAA (TS Z).

XCH A (mnemonic NOOP) is useful and its action is, in 2 MCT:

Take next instruction from L + 1.

Remarks: This is used for no operation whenever it is desired to save C(Q). Otherwise TC L + 1 is faster.

CS uses Z and A. CS Z might be useful; its action is, in 2 MCT:

Set C(A) = -(TC L + 1);

Take next instruction from L + 1.

CS A (Mnemonic COM) is definitely useful and its action is, in 2 MCT:

Set C(A) = -b(A);

Take next instruction from L + 1.

Remarks: The full 15 bits and sign are complemented.

TS uses Z and A. TS Z is useful and is represented by the mnchonic code TCAA (transfer control to address in A). Let b(A) = OP K, where OP is any four bits; then the action is, in 2 MCT:

If b(A) contains no overflow, C(A) = b(A);

If b(A) contains positive overflow, C(A) = 000001;

If b(A) contains negative overflow, C(A) = 177776;

Take next instruction from K and proceed from there.

Remarks: Assuming that no explicit manipulation of C(Z) intervenes, the

next TC executed (from, say, location L') will set C(Q) = OP

L + 1, which in general is not a proper return address (see TC Q).

CAUTION: The first TC following a TCAA must not be a subroutine call. There is no problem if OP = 0000 (binary), but in this case XAQ is as fast and is preferred unless it is desired to save C(Q). TS A is also useful and is represented by the mnemonic code OVSK (overflow skip). Its action is, in 2 MCT:

If C(A) contains no overflow, take next instruction from L + 1;

If C(A) contains positive or negative overflow, take next instruction from

L + 2, and proceed from there.

AD uses Z and A. AD Z might be useful; its action is, in 2 or 3 MCT:

Set C(A) = b(A) + L + 1;

Take next instruction from L + 1.

Remarks: (Same as those under AD in the previous "Basic Instructions" section.)

AD A is definitely useful; its mnemonic is DOUBLE; its action is, in 2 or 3 MCT:

Set C(A) = b(A) + b(A);

Take next instruction from L + 1.

Remarks: (Same as those under AD in the previous "Basic Instructions." section.)

MASK uses Z and A. MASK Z is not useful. MASK A is equivalent to XCH A.

MP uses Z, A, and LP. MP Z is not useful. MP A is useful; its mnemonic is SQUARE, and its action is, in 10 MCT (including 2 MCT for the EXTEND instruction):

Set C(A, LP) =  $b'(A) \times b'(A)$ ;

Take next instruction from L + 1.

Remarks: b'(A) is the overflow-corrected form of b(A); that is, overflow in b(A) is ignored.

MP LP might be useful; its action is, in 10 MCT:

Set  $C(A, LP) = b'(A) \times b(LP);$

Take next instruction from L + 1.

DV uses Z, A, Q, and LP. DV Z and DV A are not useful. DV Q might be useful; its action is, in 18 MCT:

Take next instruction from L + 1.

SU uses Z and A. SU Z might be useful, its action is, in 4 or 5 MCT:

Set C(A) = b(A) - L - 1;

Take next instruction from L + 1.

Remarks: (Same as those under AD in previous "Basic Instructions" section.)

SU A is not useful.

Summary of Consequences of Rule 2:

- 1. With the exception of MP, addressing of a flip-flop register causes the full 15 bits and sign to be used as the operand.

- 2. Addressing registers, whether or not they are centrals used by the instruction, usually results in straightforward operation, except as follows:

TCAA (TS Z) yields the  $\pm 1$  overflow indicator in A but always transfers control to the location whose address is in bits 12-1 of C(A); that is, the skipping function is lacking.

OVSK (TS A) skips if C(A) contains an overflow but leaves C(A) as it was.

The complete set of mnemonic codes for which the address is implied is:

| RESUME | = | INDEX | 25   | NOOP   | = | XCH | А |

|--------|---|-------|------|--------|---|-----|---|

| EXTEND | = | INDEX | 5777 | COM    | = | CS  | Α |

| INHINT | = | INDEX | 17   | TCAA   | = | TS  | Z |

| RELINT | = | INDEX | 16   | OVSK   | = | TS  | А |

| XAQ    | = | TC    | А    | DOUBLE | = | AD  | А |

| RETURN | = | TC    | Q    | SQUARE | = | MP  | Α |

There are three mnemonic operation codes (not implied address) that may be used for clarity in place of the standard codes:

TCR = TC, indicating a subroutine call (Transfer Control, intending to Return);

CAF = XCH, indicating that an XCH addressed to Fixed acts like a Clear and Add;

OVIND = TS, indicating that a TS addressed to Fixed skips and sets C(A) = ±1 on overflow but changes no memory location.

UNCLASSIFIED

### SEQUENCES NOT UNDER PROGRAM CONTROL

There are four sequences whose execution is specified not by program but by the state of the priority chain, which is altered by events external to the computer and some internal events, such as overflow of a counter.

### INTERRUPT

3 MCT

Set C(ZRUPT) = b(Z);

Set C(BRUPT) = b(B);

Reset priority signal, and inhibit interrupt until further notice;

Take next instruction from 2000 + 4n (n = 0, 1, 2, ---), where n is the

interrupt type number; and proceed from there.

- Remarks: At the end of each instruction, C(B) is the next instruction. An interrupt may occur at the end of any instruction except in the following circumstances:

- 1. An interrupting program is in progress;

- 2. An INHINT instruction has occurred, but no subsequent RELINT;

- 3. C(B) contains overflow (as from INDEX);

- 4. C(A) contains overflow.

The standard coding at 2000 + 4n is:

TS ARUPT XCH Q XCH QRUPT TC RUPTPRGN

By convention, ARUPT = 26 and QRUPT = 27.

Note that an interrupt causes any overflow in C(Q) to be lost.

COUNTER INCREMENT

Set C(J) = b(J) + 1.

COUNTER DECREMENT

1 MCT

1 MCT

Set C(J) = b(J) - 1.

COUNTER SHIFT

1 MCT

Set C(J) = b(J) + b(J).

Remarks: J is the address of the counter corresponding to the priority signal,  $30 \leq J \leq 56$ . For some counters, an overflow sets up an interrupt priority signal. Any memory cycle time may be preempted by the priority chain for a counter operation.

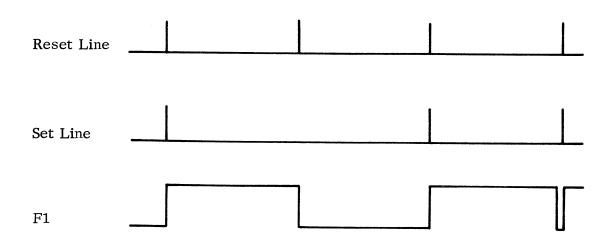

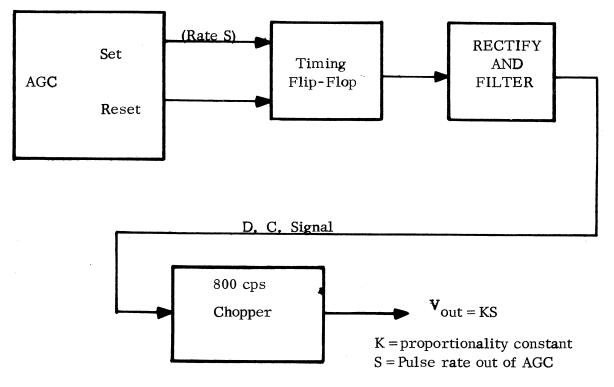

#### PULSE SEQUENCES

The skeleton upon which the AGC 4 sequences are built is the memory cycle, which occurs every MCT except in the Multiply and Divide loops and whenever a flip-flop register is addressed. The events of two different types of memory cycles are shown in figure 3-1, with the division into 1- $\mu$ sec time periods called Time 1 through Time 12. The address selection register is written into at Time 1; if the address is 2000 or greater, the Rope manipulations shown at the left begin. If the address is in the range 20 to 1777, the Erasable Memory manipulations shown at the right begin. A strobe writes data from the sense lines of its memory into the memory buffer register G, which is cleared beforehand. It can be seen that information from Fixed Memory becomes available early in Time 7, and from Erasable early in Time 6. G accepts information to be stored in Erasable before Time 10 or by special early pulses in Time 10, and supplies it to the Z Inhibit Drive (ZID) during Times 10-12.

The control pulses that form the micro-operations of the sequences are listed in table 3-4 at the end of this chapter.

As many as five pulses can occur simultaneously. Table 3-5 (at the end of this chapter) shows the subsequences of twelve times (1 MCT) each. The subsequences that make up a sequence are selected in turn by changes in a 2-bit stage counter, which starts at 00 for instructions and 01 for interrupt, and is stepped explicitly by the pulses ST1 and ST2 as they occur in subsequences. Each subsequence has a name consisting of a mnemonic abbrevia-tion and a suffix (0, 1, 2, or 3) showing the state of the stage counter when it is selected. Where no suffix is given, 0 is understood.

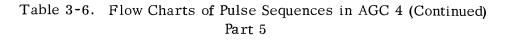

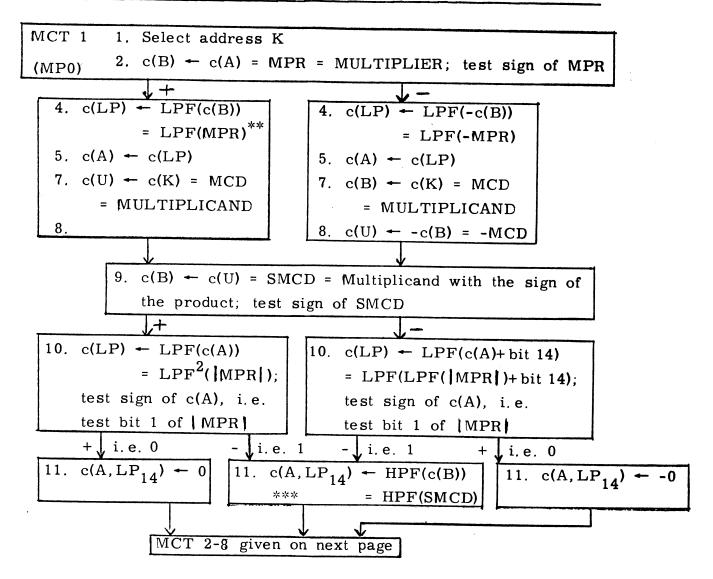

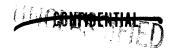

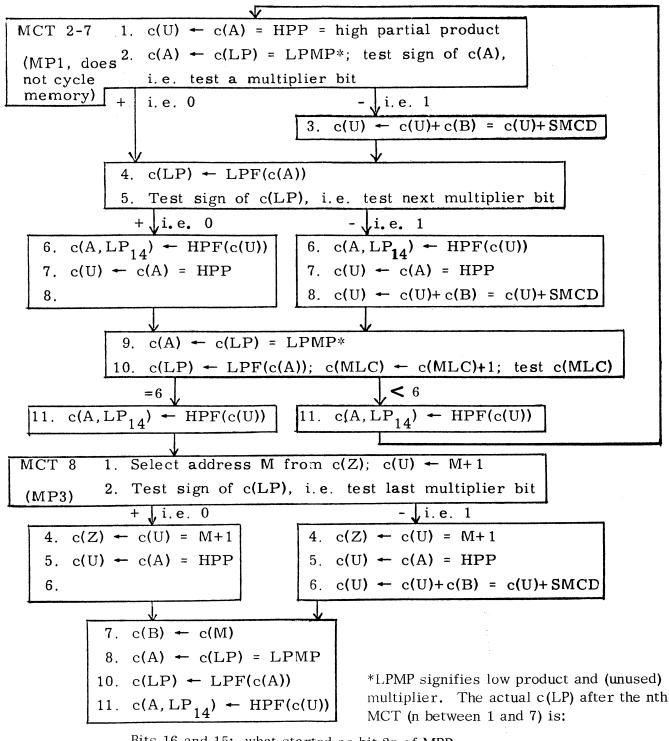

Flowcharts of the sequences are given in table 3-6 (at the end of this chapter), Parts 1 through 13. These are simplified to show activities of central importance to the results of each sequence, omitting parity procedures and the application or not of Rule 1 in the "Special Cases: Implied Address Codes" section. Explanatory remarks on the flowcharts comprise the bulk of this discussion.

INSTRUCTIONS

MEMORY CYCLE TIMING AGC 4

| TIME |                                   |                                        |                      |

|------|-----------------------------------|----------------------------------------|----------------------|

| 1    | ١                                 | /                                      |                      |

| 2    | Rope Inhibit<br>and<br>Rope Set 1 |                                        |                      |

| 3    |                                   |                                        |                      |

| 4    | A<br>Rope Set 2                   | Λ                                      |                      |

| 5    |                                   | Set A<br>Erasable Read<br>Selection XY | ^                    |

| 6    | A<br>Rope<br>Strobe               | Switch<br>Cores V                      | Erasable<br>V Strobe |

| 7    |                                   | V                                      |                      |

| 8    | Rope<br>Reset                     |                                        |                      |

| 9    |                                   |                                        |                      |

| 10   | /                                 | Reset<br>Erasable<br>Selection         | ZID                  |

| 11   |                                   | Switch A<br>Cores Write<br>XY          |                      |

| 12   |                                   | V                                      | V                    |

Figure 3-1. APOLLO Guidance Computer 4, Memory Cycle Timing.

Notation: INHINT 1 denotes that interrupt is prevented from occurring at the end of the current instruction; "V" denotes superposition (Boolean inclusive OR); INHINT denotes the inhibition of interrupt until further notice; other notation is that of the "Basic Instructions" and "Extracode Instructions" sections, except that "C(n)  $\leftarrow$ " is used instead of "set C(n) =."

Boundary conditions: At the beginning of the instruction in L, C(Z) = L + 1. After Time 11 of the last subsequence in each sequence, C(B) is the next instruction. If no unprogrammed sequences are commanded, Time 12 selects the next instruction by writing C(B) into the sequence selection register SQ.

Table 3-6, Part 1: TC requires only 1 MCT because its only operation on memory is to fetch the instruction to which control is being transferred. Time 7 sets up that instruction, Time 8 the return address, and Time 10 the initial condition in Z for C(K).