# Modular Electronics Learning (ModEL) PROJECT

### COMBINATIONAL LOGIC

© 2019-2025 by Tony R. Kuphaldt – under the terms and conditions of the Creative Commons Attribution 4.0 International Public License

#### Last update = 6 May 2025

This is a copyrighted work, but licensed under the Creative Commons Attribution 4.0 International Public License. A copy of this license is found in the last Appendix of this document. Alternatively, you may visit http://creativecommons.org/licenses/by/4.0/ or send a letter to Creative Commons: 171 Second Street, Suite 300, San Francisco, California, 94105, USA. The terms and conditions of this license allow for free copying, distribution, and/or modification of all licensed works by the general public.

# Contents

| 1 | Inti | roduction                                                | 3          |

|---|------|----------------------------------------------------------|------------|

|   | 1.1  | Recommendations for students                             | 3          |

|   | 1.2  | Challenging concepts related to combinational logic      | 5          |

|   | 1.3  | Recommendations for instructors                          | 6          |

| 2 | Cas  | se Tutorial                                              | 7          |

|   | 2.1  | Example: gate circuits from 4-input truth tables         | 8          |

|   | 2.2  | Example: ladder logic circuits from 4-input truth tables | 11         |

|   | 2.3  |                                                          | 15         |

|   | 2.4  |                                                          | 19         |

|   |      | 2.4.1 Power circuit fault detector                       | 19         |

|   |      | 2.4.2 H-bridge driver circuit                            | 20         |

|   |      | 2.4.3 Two-out-of-three voting circuit                    | 22         |

|   |      |                                                          | 23         |

|   |      | 2.4.5 Binary decoder circuits                            | 24         |

|   |      |                                                          | 26         |

| 3 | Tut  | sorial                                                   | <b>2</b> 9 |

|   | 3.1  | Logic functions                                          | 29         |

|   | 3.2  |                                                          | 32         |

|   | 3.3  | Combinational relay logic                                | 36         |

|   | 3.4  | · · ·                                                    | 38         |

|   | 3.5  | •                                                        | 41         |

|   |      |                                                          | 42         |

|   |      |                                                          | 44         |

|   |      |                                                          | 47         |

| 4 | His  | torical References                                       | 51         |

|   | 4.1  | Claude Shannon makes the connection                      | 52         |

|   |      |                                                          | 54         |

|   | 4.2  | NASA'S Apono Guidance Computer                           | 07         |

| 5 |      |                                                          |            |

| 5 |      | rivations and Technical References                       | <b>59</b>  |

CONTENTS

| 6 | $\mathbf{Pro}$ | gramming References 69                                               |

|---|----------------|----------------------------------------------------------------------|

|   | 6.1            | Programming in C++                                                   |

|   | 6.2            | Programming in Python                                                |

|   | 6.3            | Modeling combinational logic using C++                               |

| 7 | Que            | estions 83                                                           |

|   | 7.1            | Conceptual reasoning                                                 |

|   |                | 7.1.1 Reading outline and reflections                                |

|   |                | 7.1.2 Foundational concepts                                          |

|   |                | 7.1.3 Use of spare NAND gates                                        |

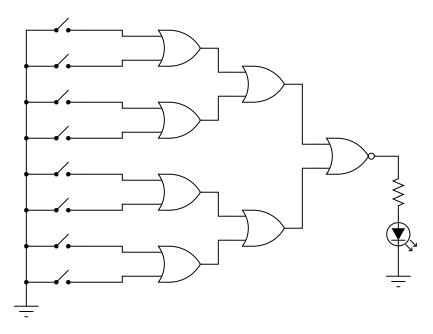

|   |                | 7.1.4 Unanimous vote detector circuit                                |

|   |                | 7.1.5 Combination lock circuit                                       |

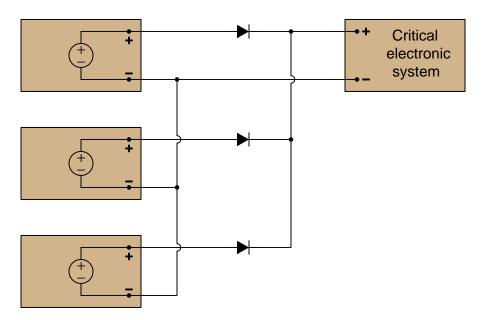

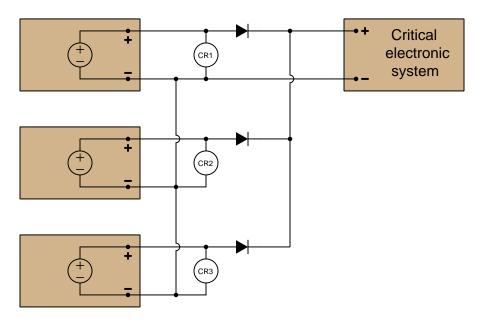

|   |                | 7.1.6 Triple-redundant power supply                                  |

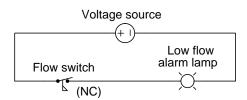

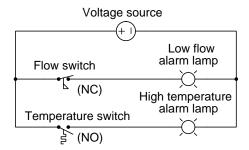

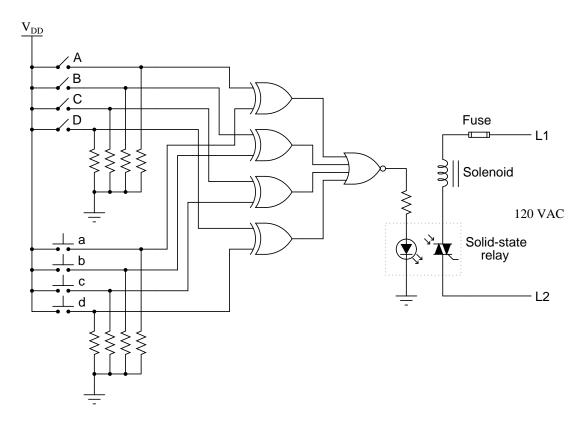

|   |                | 7.1.7 Chemical weapons incinerator                                   |

|   | 7.2            | Quantitative reasoning                                               |

|   |                | 7.2.1 Miscellaneous physical constants                               |

|   |                | 7.2.2 Introduction to spreadsheets                                   |

|   |                | 7.2.3 Using Python to evaluate combinational logic expressions       |

|   |                | 7.2.4 Using Python to evaluate a combinational function diagram 106  |

|   |                | 7.2.5 Boolean expressions from gate circuits                         |

|   |                | 7.2.6 Boolean expressions from relay circuits                        |

|   |                | 7.2.7 Truth tables from Boolean expressions                          |

|   |                | 7.2.8 Gate circuits from Boolean expressions                         |

|   |                | 7.2.9 Relay circuits from Boolean expressions                        |

|   |                | 7.2.10 Circuits from two-input truth tables                          |

|   |                | 7.2.11 SOP and POS expressions from the same truth table             |

|   |                | 7.2.12 Circuits from three-input truth tables                        |

|   |                | 7.2.13 Boolean expression for an undocumented logic circuit          |

|   |                | 7.2.14 SOP expression and ladder logic from a truth table            |

|   |                | 7.2.15 Gate circuit from a truth table                               |

|   |                | 7.2.16 Relay circuit from a truth table                              |

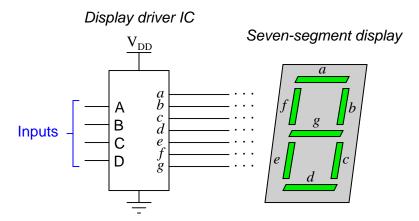

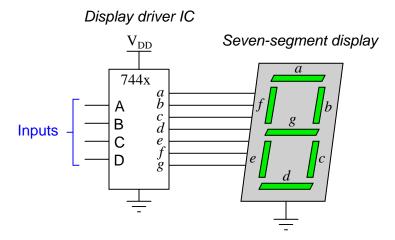

|   |                | 7.2.17 Seven-segment decoder                                         |

|   |                | 7.2.18 Timing diagrams for gate circuits                             |

|   | 7.3            | Diagnostic reasoning                                                 |

|   |                | 7.3.1 Effect of gate fault on Boolean expression                     |

|   |                | 7.3.2 Seven-segment decoder/driver problem                           |

| 8 | Pro            | jects and Experiments 125                                            |

| Ü | 8.1            | Recommended practices                                                |

|   | 0.1            | 8.1.1 Safety first!                                                  |

|   |                | 8.1.2 Other helpful tips                                             |

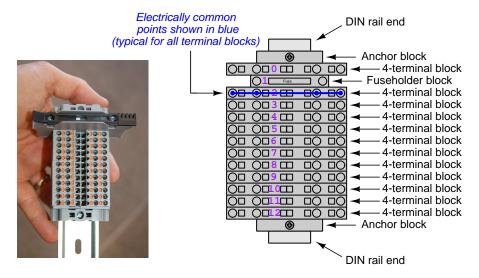

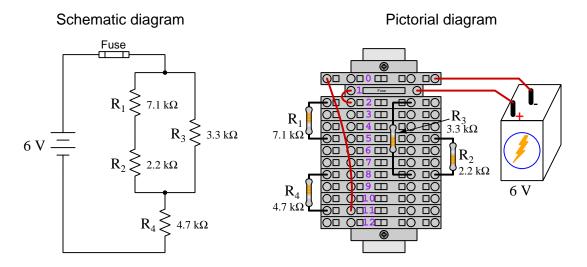

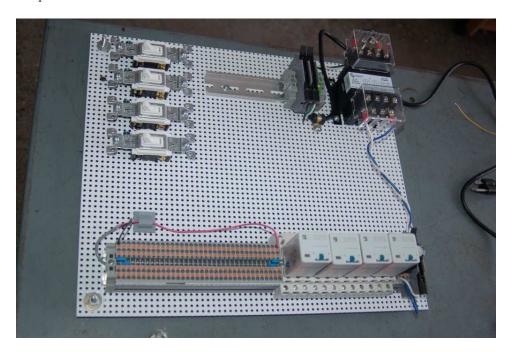

|   |                | 8.1.3 Terminal blocks for circuit construction                       |

|   |                | 8.1.4 Conducting experiments                                         |

|   |                | 8.1.5 Constructing projects                                          |

|   | 8.2            | Experiment: Relay circuit implementation of an arbitrary truth table |

|   | 8.3            | Project: Combinational gate circuit driving 120 VAC load             |

|   | 0.0            | 100                                                                  |

| CONTENTS | 1 |

|----------|---|

|          |   |

| A Problem-Solving Strategies | 141 |

|------------------------------|-----|

| B Instructional philosophy   | 143 |

| C Tools used                 | 149 |

| D Creative Commons License   | 153 |

| E References                 | 161 |

| F Version history            | 163 |

| Index                        | 166 |

|                              |     |

2 CONTENTS

# Chapter 1

# Introduction

### 1.1 Recommendations for students

Logic functions such as AND, OR, and NOT form the basis of nearly all digital systems. However, each one of these functions by itself is of limited use. Practical applications usually demand logic functions of additional complexity, and when multiple AND/OR/NOT functions are connected together to form a more advanced logical function the result is called *combinational logic*.

A defining characteristic of any combinational logic system is that the output state(s) are entirely defined by the input states. That is to say, it is possible to write a *truth table* for any combinational logic function exactly describing which input states immediately lead to which output states. This stands in contrast to other digital functions such as *timing functions* and *latching functions*, the output states of which depend on input states as well as past history for that function (e.g. elapsed time for timing functions, and previous output states for latching functions).

Important concepts related to combinational logic include **logic states**, **logic levels**, **high** and **low** logic states, **logic functions**, **truth tables**, **Boolean algebra**, **logic gates**, electromechanical **relays**, logic function **universality**, **DeMorgan's Theorem**, the **normal state** of a switch, algebraic **order of operations**, **sum-of-products**, **product-of-sums**, and logic circuit **minimization**.

Here are some good questions to ask of yourself while studying this subject:

- How might an experiment be designed and conducted to explore DeMorgan's Theorem? What hypothesis (i.e. prediction) might you pose for that experiment, and what result(s) would either support or disprove that hypothesis?

- What are some practical applications of SOP and POS Boolean expressions?

- What does a *truth table* represent?

- What is a *logic function*?

- What are some basic forms of logic functions?

- How may we use lettered variables to represent logic states and logic functions?

- How are digital logic states represented as electrical voltage signals?

- How may logical functions be implemented using electromechanical relays?

- Which logic functions may be configured to emulate other logic functions?

- How do series and parallel switch networks relate to logical functions?

- What is a practical application for "universal" logic functions?

- What is DeMorgan's Theorem and where might we apply it?

- How does a Boolean product relate to logic gate functions, and also to relay contact networks?

- How does a Boolean sum relate to logic gate functions, and also to relay contact networks?

- Why is the *order of operations* important when translating a Boolean expression into a logic circuit?

- Describe how a "Sum of Products" (SOP) Boolean expression may be derived from a truth table

- Describe how a "Negative Sum of Products" (NSOP) Boolean expression may be derived from a truth table.

- Describe how a "Product of Sums" (POS) Boolean expression may be derived from a truth table.

- Why is it useful to have multiple techniques for translating a truth table into a Boolean expression?

- Why might it be beneficial to reduce or minimize logic circuits?

### 1.2 Challenging concepts related to combinational logic

The following list cites concepts related to this module's topic that are easily misunderstood, along with suggestions for properly understanding them:

- Sourcing versus Sinking output currents a common misconception is that since the output of a logic gate is called "output" it must mean that current only ever *exits* that terminal. This is untrue. All that "output" actually signifies is the fact that the gate is outputting *information* consisting of voltage values measured between that terminal and ground. Sometimes the assertion of a "low" (zero-voltage) logical state requires that the gate actually draw current *in* through its "output" terminal!

- Gates require DC power since logic gates are really just transistor amplifier circuits, those treansistors require constant DC voltage applied between their power terminals to function properly. Gates are *not* powered through their input terminals these terminals only receive information in the form of "high" and "low" logic states, and ideally pass negligible current.

- Pullup and pulldown resistors in digital circuits, resistors are often used to provide a secure logic state when an input device (such as a switch) goes to a high-impedance (open) mode. Students often have difficulty figuring out exactly where these resistors should go in a circuit. The most common mistake I've seen is to place one of these "pullup" or "pulldown" resistors in *series* with a gate input, which will accomplish absolutely nothing. The "trick" to getting this placement right, if you can call it a trick at all, is to literally follow the word "pullup" or "pulldown". A *pullup* resistor pulls the logic state of a wire up to the positive supply rail, and so must connect between the gate input and +V. A *pulldown* resistor pulls the logic state of a wire down to ground potential, and so must connect between the gate input and ground. In either case, the resistor provides a sure path to the opposite power rail that the input device connects to when active (closed).

- **DeMorgan's Theorem** a common tendency for students is to attempt to memorize new mathematical formulae and techniques, and DeMorgan's Theorem is no exception. However, a more insightful approach is to see how DeMorgan's Theorem works in practical applications such as logic function universality, where we use just one type of logic function to emulate other logic functions.

### 1.3 Recommendations for instructors

This section lists realistic student learning outcomes supported by the content of the module as well as suggested means of assessing (measuring) student learning. The outcomes state what learners should be able to do, and the assessments are specific challenges to prove students have learned.

• Outcome – Demonstrate effective technical reading and writing

<u>Assessment</u> – Students present their outlines of this module's instructional chapters (e.g. Case Tutorial, Tutorial, Historical References, etc.) ideally as an entry to a larger Journal document chronicling their learning. These outlines should exhibit good-faith effort at summarizing major concepts explained in the text.

<u>Assessment</u> – Students explain how gate universality is proven in the Tutorial chapter's examples.

<u>Assessment</u> – Students explain how logic circuits were derived from Boolean expressions in the Tutorial chapter's examples.

<u>Assessment</u> – Students explain how logic circuits were derived from truth tables in the Tutorial chapter's examples.

• Outcome – Design logic circuits to implement given truth tables

<u>Assessment</u> – Given a truth table with desired output states, design a semiconductor logic gate circuit to implement that function.

<u>Assessment</u> – Given a truth table with desired output states, design an electromechanical relay "ladder logic" circuit to implement that function.

#### • Outcome – Independent research

<u>Assessment</u> – Locate logic gate datasheets and properly interpret some of the information contained in those documents including supply voltage range, input logic voltage levels, output logic voltage levels, maximum switching speed, maximum output current, internal schematic diagrams (not available in all datasheets), etc.

<u>Assessment</u> – Read and summarize in your own words reliable source documents on the subject of NASA'a Apollo Guidance Computer (AGC) which was built entirely of NOR gates.

# Chapter 2

# Case Tutorial

The idea behind a *Case Tutorial* is to explore new concepts by way of example. In this chapter you will read less presentation of theory compared to other Tutorial chapters, but by close observation and comparison of the given examples be able to discern patterns and principles much the same way as a scientific experimenter. Hopefully you will find these cases illuminating, and a good supplement to text-based tutorials.

These examples also serve well as challenges following your reading of the other Tutorial(s) in this module – can you explain why the circuits behave as they do?

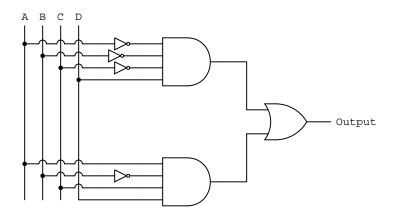

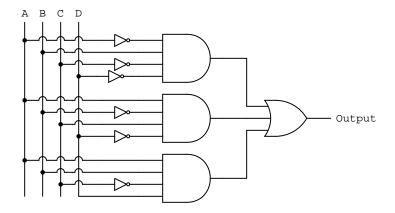

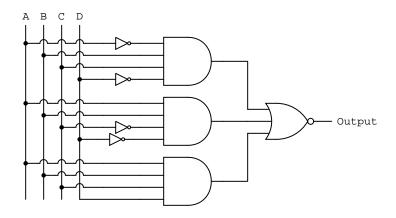

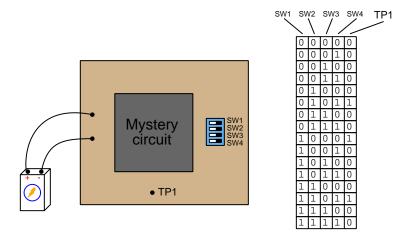

## 2.1 Example: gate circuits from 4-input truth tables

| A | В | $\mathbf{C}$ | D | Output |

|---|---|--------------|---|--------|

| 0 | 0 | 0            | 0 | 0      |

| 0 | 0 | 0            | 1 | 1      |

| 0 | 0 | 1            | 0 | 0      |

| 0 | 0 | 1            | 1 | 0      |

| 0 | 1 | 0            | 0 | 0      |

| 0 | 1 | 0            | 1 | 0      |

| 0 | 1 | 1            | 0 | 0      |

| 0 | 1 | 1            | 1 | 0      |

| 1 | 0 | 0            | 0 | 0      |

| 1 | 0 | 0            | 1 | 0      |

| 1 | 0 | 1            | 0 | 0      |

| 1 | 0 | 1            | 1 | 1      |

| 1 | 1 | 0            | 0 | 0      |

| 1 | 1 | 0            | 1 | 0      |

| 1 | 1 | 1            | 0 | 0      |

| 1 | 1 | 1            | 1 | 0      |

**Boolean SOP expression:**  $\overline{A} \ \overline{B} \ \overline{C}D + A \overline{B}CD$

| A | В | $\mathbf{C}$ | D | Output |

|---|---|--------------|---|--------|

| 0 | 0 | 0            | 0 | 0      |

| 0 | 0 | 0            | 1 | 0      |

| 0 | 0 | 1            | 0 | 0      |

| 0 | 0 | 1            | 1 | 0      |

| 0 | 1 | 0            | 0 | 1      |

| 0 | 1 | 0            | 1 | 0      |

| 0 | 1 | 1            | 0 | 0      |

| 0 | 1 | 1            | 1 | 0      |

| 1 | 0 | 0            | 0 | 0      |

| 1 | 0 | 0            | 1 | 0      |

| 1 | 0 | 1            | 0 | 1      |

| 1 | 0 | 1            | 1 | 0      |

| 1 | 1 | 0            | 0 | 0      |

| 1 | 1 | 0            | 1 | 1      |

| 1 | 1 | 1            | 0 | 0      |

| 1 | 1 | 1            | 1 | 0      |

**Boolean SOP expression:**  $\overline{A}B\overline{C}\overline{D} + A\overline{B}C\overline{D} + AB\overline{C}D$

| A | В | $\mathbf{C}$ | D | Output |

|---|---|--------------|---|--------|

| 0 | 0 | 0            | 0 | 1      |

| 0 | 0 | 0            | 1 | 1      |

| 0 | 0 | 1            | 0 | 1      |

| 0 | 0 | 1            | 1 | 1      |

| 0 | 1 | 0            | 0 | 1      |

| 0 | 1 | 0            | 1 | 1      |

| 0 | 1 | 1            | 0 | 0      |

| 0 | 1 | 1            | 1 | 1      |

| 1 | 0 | 0            | 0 | 1      |

| 1 | 0 | 0            | 1 | 1      |

| 1 | 0 | 1            | 0 | 1      |

| 1 | 0 | 1            | 1 | 1      |

| 1 | 1 | 0            | 0 | 0      |

| 1 | 1 | 0            | 1 | 1      |

| 1 | 1 | 1            | 0 | 1      |

| 1 | 1 | 1            | 1 | 0      |

Boolean Negative-SOP expression:  $\overline{\overline{A}BC\overline{D}} + AB\overline{C}\overline{D} + ABCD$

## 2.2 Example: ladder logic circuits from 4-input truth tables

| A | В | $\mathbf{C}$ | D | Output |

|---|---|--------------|---|--------|

| 0 | 0 | 0            | 0 | 0      |

| 0 | 0 | 0            | 1 | 0      |

| 0 | 0 | 1            | 0 | 0      |

| 0 | 0 | 1            | 1 | 1      |

| 0 | 1 | 0            | 0 | 0      |

| 0 | 1 | 0            | 1 | 0      |

| 0 | 1 | 1            | 0 | 0      |

| 0 | 1 | 1            | 1 | 1      |

| 1 | 0 | 0            | 0 | 0      |

| 1 | 0 | 0            | 1 | 0      |

| 1 | 0 | 1            | 0 | 0      |

| 1 | 0 | 1            | 1 | 0      |

| 1 | 1 | 0            | 0 | 0      |

| 1 | 1 | 0            | 1 | 0      |

| 1 | 1 | 1            | 0 | 1      |

| 1 | 1 | 1            | 1 | 0      |

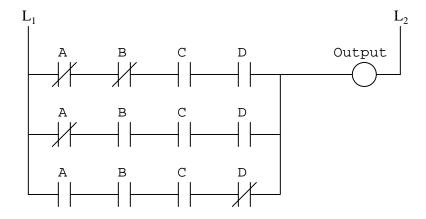

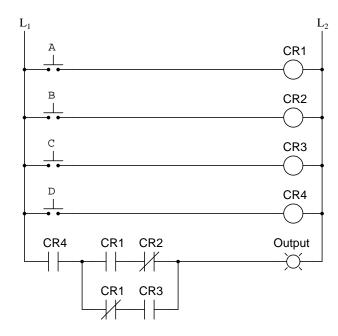

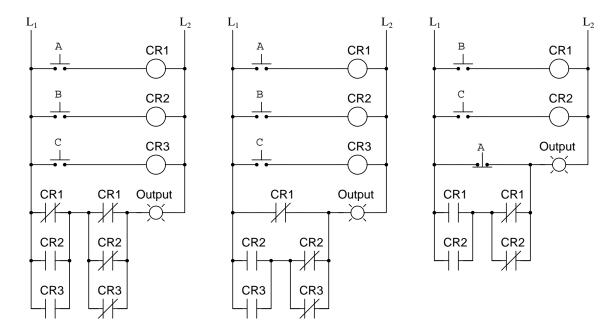

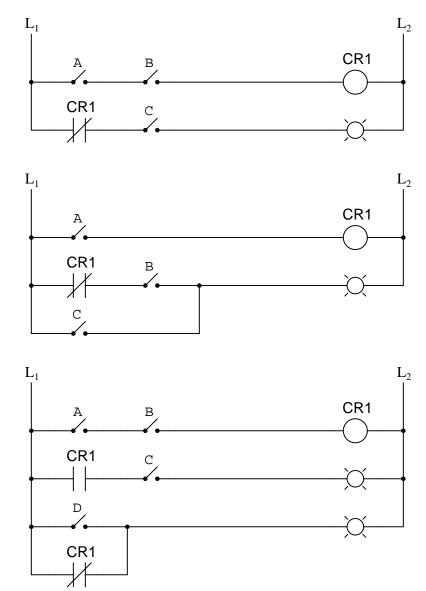

**Boolean SOP expression:**  $\overline{A} \, \overline{B} CD + \overline{A} BCD + ABC\overline{D}$

And of course it should be evident from the ladder-logic circuit that certain simplifications may be made while still retaining the same logical functionality:

The process of simplifying the original ladder-logic circuit to what you see above is a matter of identifying identical contacts (e.g. the normally-open C contact) present in multiple rungs which may be consolidated into a single rung in series with the non-common contact rungs. Note also how the normally-closed B and normally-open B contacts were eliminated as the upper and middle rungs were consolidated into one rung, because having NO and NC contacts in parallel driven by the same input is pointless – there would *always* be a path through one or the other of them regardless of B's state, therefore B need not have a presence in the consolidated rung.

A good simplification strategy is to consolidate contacts shared amongst the greatest number of rungs first. This is why the first consolidation was the normally-open C contact, because it was found in all three of the original rungs. This is also why the second consolidation was the upper and middle rungs: with C removed they still they had A (normally-closed) and D (normally-open) in common with each other.

| A | В | C | D | Output |

|---|---|---|---|--------|

| 0 | 0 | 0 | 0 | 1      |

| 0 | 0 | 0 | 1 | 1      |

| 0 | 0 | 1 | 0 | 1      |

| 0 | 0 | 1 | 1 | 1      |

| 0 | 1 | 0 | 0 | 1      |

| 0 | 1 | 0 | 1 | 1      |

| 0 | 1 | 1 | 0 | 1      |

| 0 | 1 | 1 | 1 | 1      |

| 1 | 0 | 0 | 0 | 0      |

| 1 | 0 | 0 | 1 | 1      |

| 1 | 0 | 1 | 0 | 1      |

| 1 | 0 | 1 | 1 | 0      |

| 1 | 1 | 0 | 0 | 1      |

| 1 | 1 | 0 | 1 | 0      |

| 1 | 1 | 1 | 0 | 1      |

| 1 | 1 | 1 | 1 | 1      |

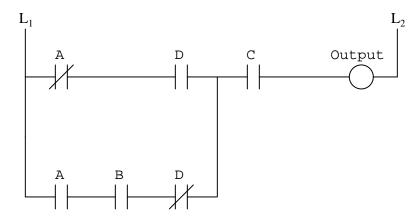

Boolean Negative-SOP expression:

$\overline{A\overline{B}\;\overline{C}\;\overline{D} + A\overline{B}CD + AB\overline{C}D}$

Certain simplifications are possible for this circuit while still retaining the same logical functionality:

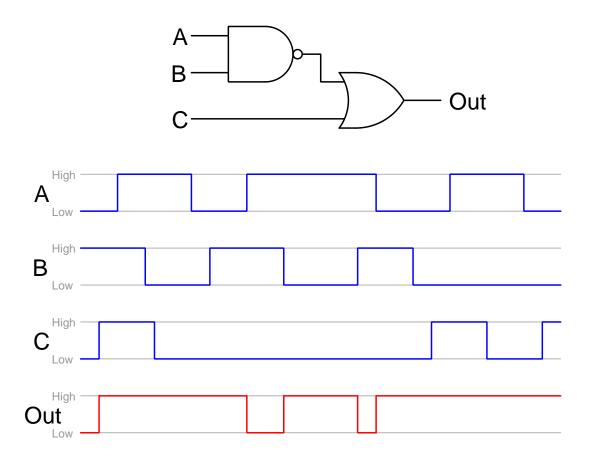

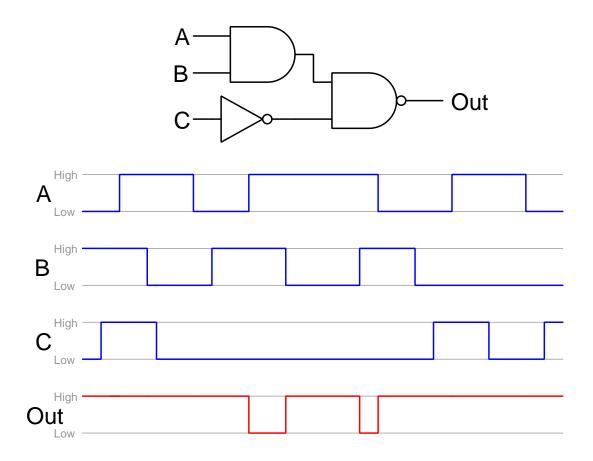

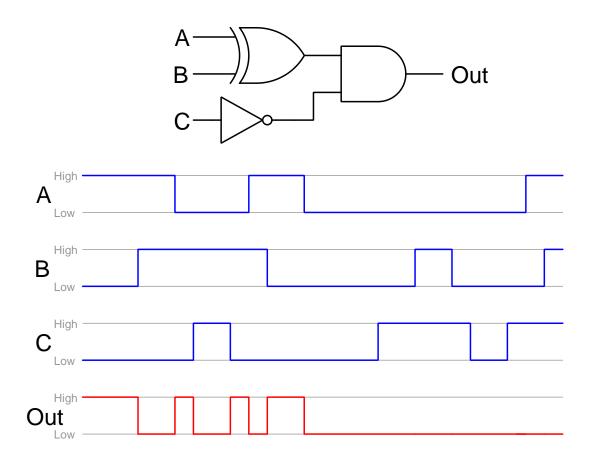

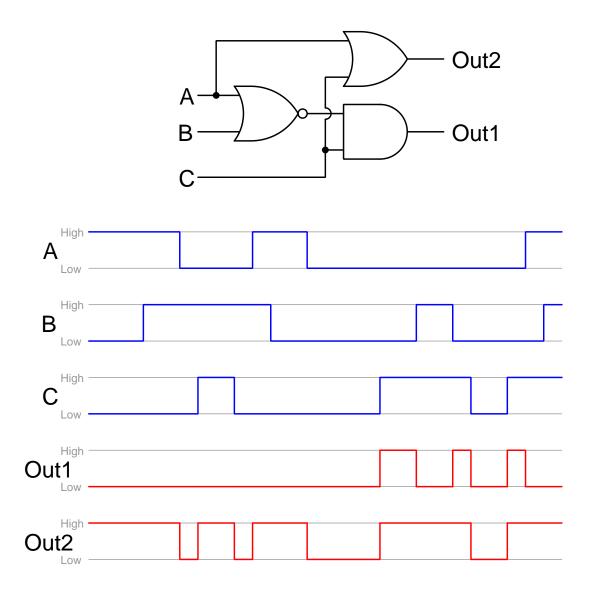

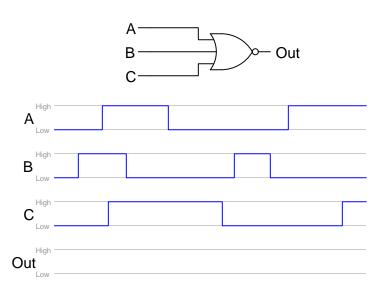

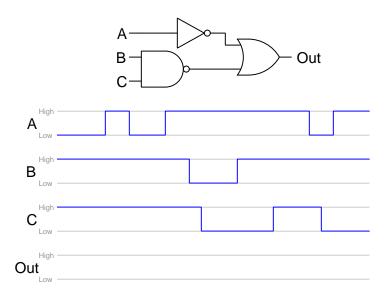

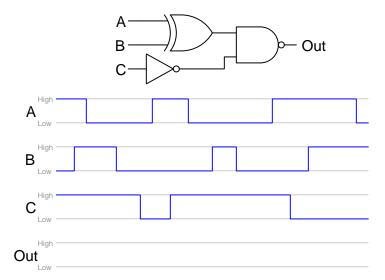

# 2.3 Example: timing diagrams for combinational gate circuits

A timing diagram shows the "high" and "low" states of logic signals as waveforms in the time domain (i.e. with time being the horizontal axis). These diagrams are essential for analyzing logic circuits with *latching* (memory) capability, but they may also be used to document the behavior of non-latching logic circuits too. The following examples show this for different configurations of logic networks.

Note: a good way to approach the analysis of this and other circuits where conditions change over time is to make multiple copies of the schematic diagram – one for each different moment in time shown on the timing diagram where there is a unique set of input conditions – and then annotate each of those diagrams with all the logic conditions at that particular moment in time. Essentially, we perform several "thought experiments" on the logic circuit, each one representing a different moment with a unique set of input conditions. This breaks a complex problem down into simpler, more manageable parts.

## 2.4 Gallery of logic gate applications

Semiconductor logic gates have many, many practical applications. The following subsections show just a few!

As is customary with most logic gate schematic diagrams, DC power terminals for the logic gates themselves have been omitted in order to reduce clutter on the diagrams. Know, however, that logic gates are transistor circuits which require DC power to function!!

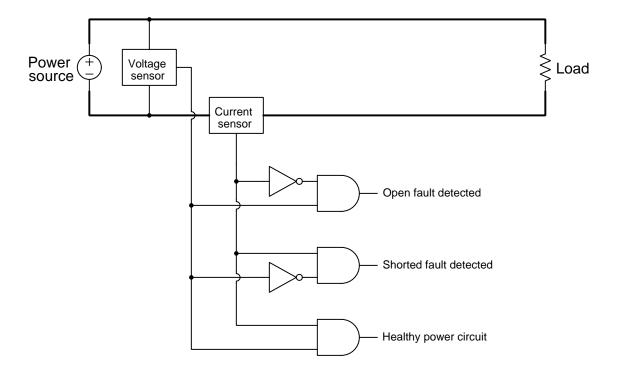

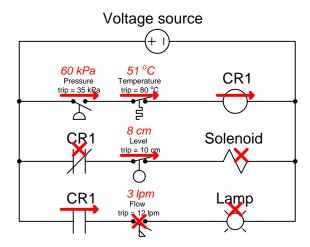

#### 2.4.1 Power circuit fault detector

A power circuit equipped with voltage and current sensors providing boolean ("true" or "false") indications of voltage and current may be equipped with a logic circuit to take those sensor signals and from their values determine if there is any fault in the power circuit:

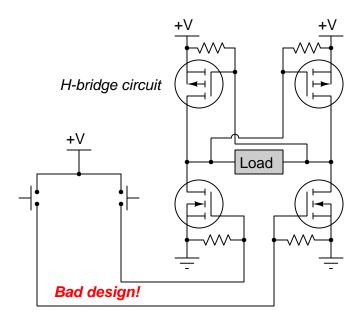

### 2.4.2 H-bridge driver circuit

H-bridge circuits are networks of four power transistors useful for controlling power to a load. By activating either one of the lower transistors in the bridge, the appropriate upper transistor becomes activated as well, passing current through the load in one direction or the other. However, the simplistic H-bridge circuit shown below is a bad design because all four transistors will activate (and short-circuit the +V source) if anyone happens to press both pushbuttons happen at the same time:

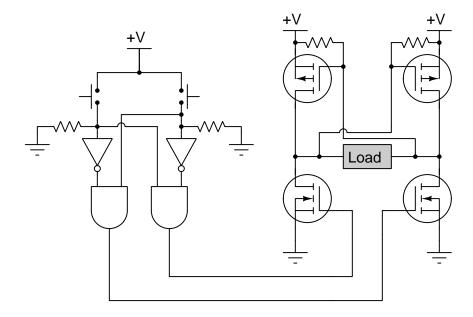

The addition of some logic gates will safeguard against this improper mode of operation, by activating the H-bridge only if one of the two pushbuttons is pressed but not if both are simultaneously pressed:

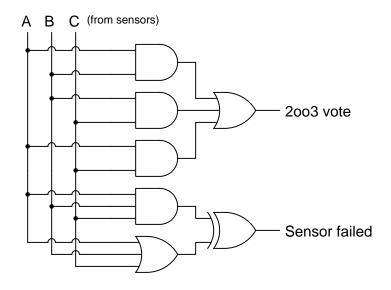

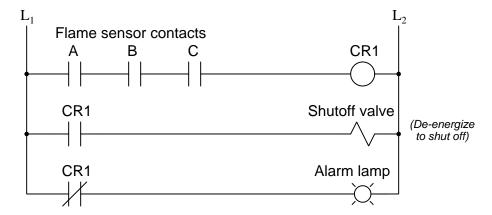

### 2.4.3 Two-out-of-three voting circuit

High-reliability systems often use redundant components to achieve fault tolerance. For example a system may use three identical sensors (A, B, and C) all detecting the same physical stimulus, all three sensors reporting their statuses to an electronic "voting" logic circuit providing a reliable output signal based on a two-out-of-three ("2003") vote:

| A | В | $\mathbf{C}$ | 2003 vote | Sensor failed |

|---|---|--------------|-----------|---------------|

| 0 | 0 | 0            | 0         | 0             |

| 0 | 0 | 1            | 0         | 1             |

| 0 | 1 | 0            | 0         | 1             |

| 0 | 1 | 1            | 1         | 1             |

| 1 | 0 | 0            | 0         | 1             |

| 1 | 0 | 1            | 1         | 1             |

| 1 | 1 | 0            | 1         | 1             |

| 1 | 1 | 1            | 1         | 0             |

All it takes is for at least two of the three redundant sensors to agree with each other to generate a reliable "high" or "low" output from the voting circuit, and if there is any disagreement at all between the three sensors we will know by the "sensor failed" output going high. This provides a fault tolerance of one, which means any one of the three sensors could fail in any state and the voting circuit would still reliably indicate the true status of the measured stimulus.

### 2.4.4 Binary word comparator

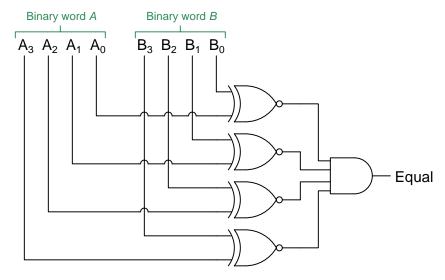

A binary word is a collection of bits representing a numerical quantity or a symbolic code<sup>1</sup>. This circuit compares two 4-bit binary words to check for equality:

Each Exclusive-NOR gate compares a pair of respective bits in words A and B, outputting a "high" signal if those two bits are equal in state. The AND gate outputs a "high" signal only if every one of its input lines is also "high", which can only happen when the two 4-bit words are identical.

$<sup>^{1}</sup>$ For example, the American Standard Code for Information Interchange (ASCII) uses 7-bit words to represent all numerical and alphabetical characters on a standard English computer keyboard.

### 2.4.5 Binary decoder circuits

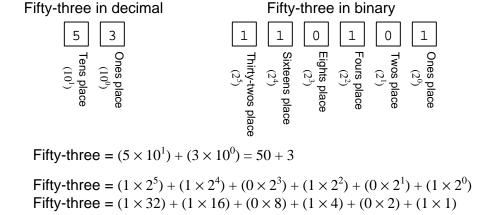

Binary numeration represents numerical quantities using multiple bits, each bit capable of being either "high" (1) or "low" (0). Basic whole-number representation in binary is simple – each bit has a place-weight that is some power of two, as opposed to decimal numeration where each place-weight is a power of ten. For example, compare the decimal versus binary representations of the number fifty-three:

Modern digital computers use binary as the means of representing numbers because each bit of a binary number may be unambiguously symbolized using Boolean-state (true/false, on/off, 1/0) logic circuits.

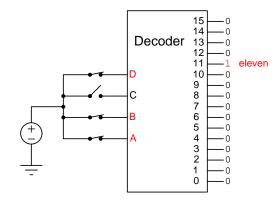

Any circuit designed to input a binary number and activate one or more outputs selected by the value of that binary number is generally referred to as a *decoder*. For example, in the illustration below we see a 4-line to 16-line binary decoder decoding the number eleven:

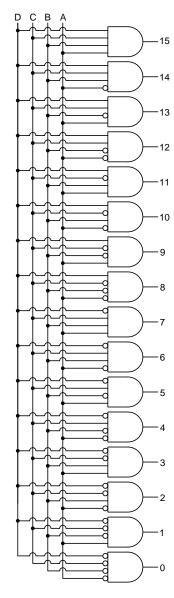

Binary decoders are really nothing more than a collection of AND and inverter (NOT) gates. In the example circuit below, inverters placed on the input of each AND gate appear as "bubbles" for the sake of compactness:

Only one of these AND gates will have its input conditions satisfied to generate a "high" output, for any given combination of bit-states in the four-bit binary input.

## 2.4.6 Binary adder circuits

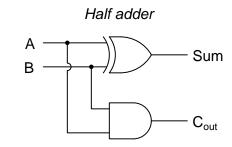

Gate circuits may be built to perform simple arithmetic operations on binary numbers. Shown below is a binary half-adder circuit, able to add two binary bits to produce sum and a carry outputs:

| A | В | Carry out | Sum | Explanation |

|---|---|-----------|-----|-------------|

| 0 | 0 | 0         | 0   | 0 + 0 = 0   |

| 0 | 1 | 0         | 1   | 0 + 1 = 1   |

| 1 | 0 | 0         | 1   | 1 + 0 = 1   |

| 1 | 1 | 1         | 0   | 1 + 1 = 2   |

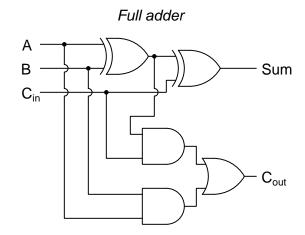

Next is a binary full-adder circuit, able to add two binary bits as well as a carry-in signal to produce sum and a carry outputs:

| Carry in | A | В | Carry out | Sum | Explanation   |

|----------|---|---|-----------|-----|---------------|

| 0        | 0 | 0 | 0         | 0   | 0 + 0 + 0 = 0 |

| 0        | 0 | 1 | 0         | 1   | 0 + 0 + 1 = 1 |

| 0        | 1 | 0 | 0         | 1   | 0 + 1 + 0 = 1 |

| 0        | 1 | 1 | 1         | 0   | 0+1+1=2       |

| 1        | 0 | 0 | 0         | 1   | 1 + 0 + 0 = 1 |

| 1        | 0 | 1 | 1         | 0   | 1 + 0 + 1 = 2 |

| 1        | 1 | 0 | 1         | 0   | 1 + 1 + 0 = 2 |

| 1        | 1 | 1 | 1         | 1   | 1 + 1 + 1 = 3 |

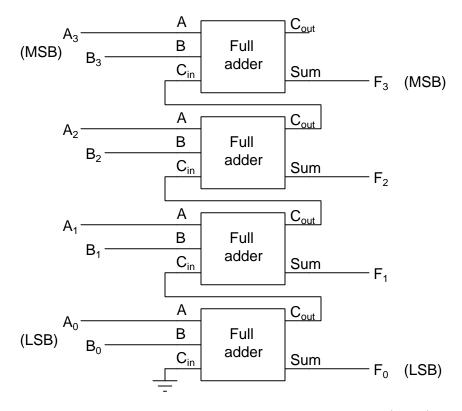

Neither a half-adder nor a full-adder circuit is very useful on its own. In order to actually add two binary numbers of any significant magnitude together we must cascade multiple full-adder networks together. Below we see a full adder network for two 4-bit binary numbers (A + B = F):

Binary adders are a fundamental building-block of Arithmetic Logic Units (ALUs), which perform numerical operations on binary numbers within microprocessor systems. Most readers of this document will do so using some digital electronic device, and rest assured each and every one of those devices will contain at least one ALU!

# Chapter 3

# **Tutorial**

## 3.1 Logic functions

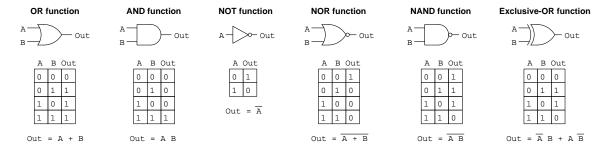

Digital logic is the realm of "discrete" quantities having only two possible values, or "states": 1 and 0. From this simple idea springs forth the concept of logical functions where specific combinations of input signal states result in pre-defined output states. Several fundamental logic functions are shown in the following illustration, each function accompanied by a truth table declaring the output state for each possible combination of input states, as well as a Boolean algebra expression describing the function mathematically:

Although the use of arithmetic (e.g. A+B for the OR function, AB for the AND function) may seem strange, it makes sense when you consider the limited values each discrete variable has. If each variable may only be a 0 or a 1, it makes sense, for example, that an AND function whose output is 1 only if all inputs are 1 is equivalent to multiplication, where the product is 1 only if all multiplied values are 1. Likewise, addition makes sense for the OR function up until 1+1=1, and even that makes sense once you realize there is no such thing as a value of "two" in the Boolean numbering system. An overhead bar symbol represents logical inversion or complementation, which flips the value to its opposite. Thus,  $\overline{A}$  means the opposite logical state of A, and  $\overline{A+B}$  (NOR) represents a function with output states exactly opposite of A+B (OR).

$<sup>^1</sup>$ When spoken, one generally says "A-bar" or "not-A" to represent the complement of A.

All of the two-input logic functions previously shown, with the exception of the Exclusive-OR (also called XOR), are available in versions having more than two inputs. A four-input OR function, for example, would have an expanded truth table with sixteen  $(2^4)$  rows, only the first of which has a 0 output state (with all four inputs in their 0 states); and a Boolean equivalent expression of Out = A + B + C + D.

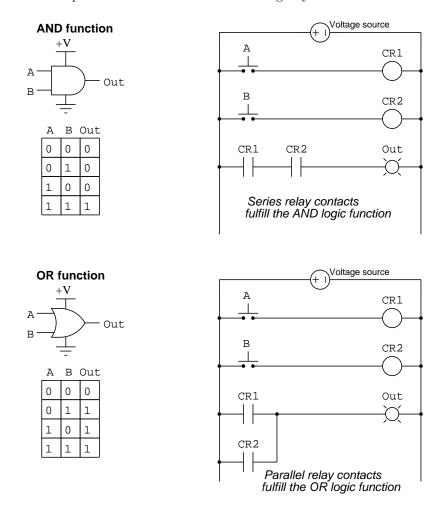

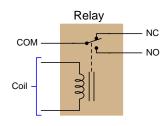

Electrical logic circuits use discrete voltage signals to represent 0 and 1 logical states. Typically, a "high" voltage value (at or near the positive power supply rail voltage with respect to ground) represents 1 and a "low" voltage value (at or near ground potential) represents 0. Logical functions take the form of transistor or relay networks in digital circuits, transistor-based logic circuit elements being called *gates* and relay-based logic being called *relay ladder logic*.

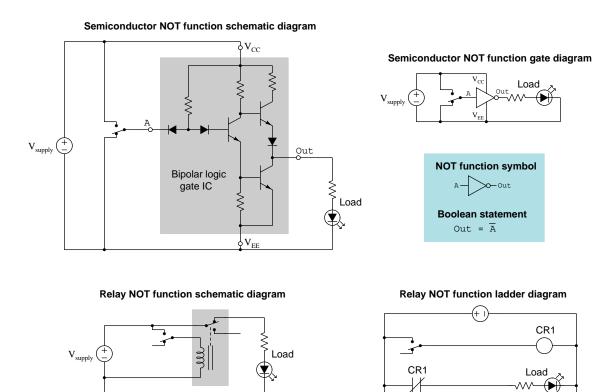

The NOT function, for example, may be constructed using bipolar junction transistors and packaged in an integrated circuit (IC), or alternatively it could manifest as an interconnection of electromechanical relays. Four diagrams below show how the NOT function may be implemented using either solid-state or relay technology, two of these diagrams use standard electronic schematic diagram symbols, while the other two use special symbols made for the purpose of simplifying digital diagrams:

Semiconductor technologies other than bipolar junction transistors (BJTs) may alternatively be used. A type of logic gate called CMOS using complementary N-channel and P-channel MOSFETs is also quite popular.

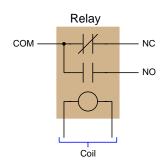

Basic logical functions such as AND and OR may be implemented using electromechanical relays just as they can using transistors. AND and OR functions in particular have direct relation to *series* and *parallel* contact connections, respectively. Please note that electrical power supply connections are typically omitted from these diagrams for simplicity, but are shown here in order to present a complete view of all required connections to make these logic systems functional:

It is important to closely study the conventions of each diagram style, where we find similar or even identical symbols used to represent different things. A small circle, for example, refers to a terminal on an integrated circuit (IC) package, whereas on a gate diagram an identical circle represents logical negation (inversion, or complementation). A larger circle drawn as a component in a ladder diagram represents the coil of an electromechanical relay.

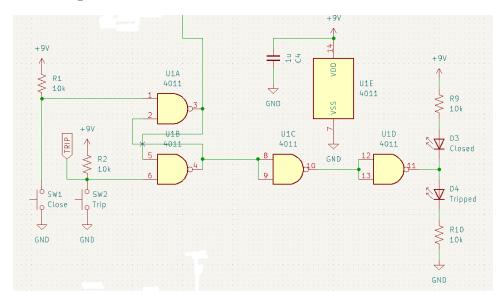

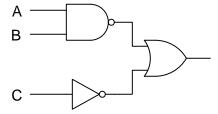

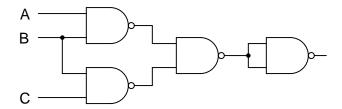

## 3.2 Universal logic functions

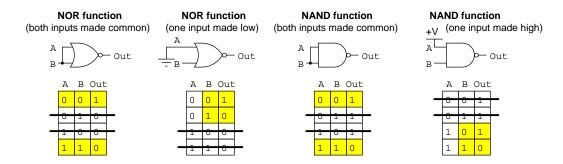

When we combine basic logical functions to make other (usually more complex) logical functions, it is called *combinational logic*. A simple and practical application of combinational logic is the use of one basic function to create another basic function. Two logical functions are classified as *universal* because any other logical function may be made from combinations of either type. Both NAND and NOR functions share this property of universality, meaning we may build up any logic function at all simply by connecting a sufficient number of NAND functions together, or a sufficient number of NOR functions together. The key to this universality is the ability of both NAND and NOR functions to operate as inverters (i.e. as NOT functions), and from this property we may combine multiple instances of each gate type to form any other.

First, demonstrating how NAND and NOR gates may function as inverters, either by connecting both input terminals together to function as a single input, or by connecting the unused input terminal to a particular power supply rail to force its logical state all the time<sup>2</sup>:

An excellent active reading exercise is to take the time to annotate the logic diagrams presented in this (and future) Tutorials with various combinations of "1" and "0" input states, then reference truth tables for the respective functions to determine what the output states must be. For example, if we annotate the upper-left NOR diagram with a "0" state at its input we see that both NOR inputs must be "0" which according to the NOR truth table must yield a "1" output; annotating the same diagram with a "1" state at its input means both of the NOR inputs must be "1" as well which according to the NOR truth table yields a "0" output.

<sup>&</sup>lt;sup>2</sup>Although from a strictly logical perspective it makes no difference whether a NAND or NOR gate is turned into an inverter (NOT gate) by connecting its input terminals together or by forcing the state of one of those inputs with a direct connection to a power supply rail, usually the latter method is preferred in actual circuit design. The reason for the latter preference has to do with the current sourcing or sinking demands of logic gate inputs: tying input terminals together means the driving device must service the current requirements of two inputs rather than just one, and additional loading degrades high-speed performance.

The following illustration demonstrates<sup>3</sup> how it is possible to use nothing but combinations of NOR gates to construct the other three basic logic functions (OR, AND, and NAND). As an aid to understanding, every signal line bears a Boolean expression describing its state:

Upon first inspection it may not be clear why some of these NOR gate networks are logically equivalent to their basic equivalents shown on the right. The first example, turning a NOR into an  $\overline{OR}$  by inverting its output, is simple enough because any double-negation cancels itself, and so  $\overline{A+B}$  is equivalent to A+B. The next example, turning a NOR gate into an AND gate by inverting its input signals, is not so obvious. They key to understanding this conversion is a theorem in Boolean algebra known as DeMorgan's Theorem, which states any negation bar spanning an arithmetic operation may be divided ("broken") and that arithmetic operation exchanged for the other type. Following DeMorgan's Theorem, we may break the long bar over  $\overline{A+B}$  and convert the addition into multiplication, resulting in  $\overline{A}\overline{B}$ , which then becomes AB according to the principle of double-negations canceling. Likewise, the next example where NOR gates become a NAND gate, involves first canceling double-bars to turn  $\overline{A}\overline{+B}$  into  $\overline{A}\overline{+B}$ , at which point DeMorgan's Theorem shows us the equivalence between this statement and  $\overline{AB}$ .

<sup>&</sup>lt;sup>3</sup>This illustration itself, of course, does not actually demonstrate the universality of NOR gates. In order for a true demonstration to be complete, one must observe the system operating as intended. For this, it is left as an exercise to the reader to perform "thought experiments" on these three logic circuits, imagining the input terminals in their various possible states and following through to the consequent output states based on the truth table of a NOR function.

$<sup>^4</sup>$ In standard Boolean algebra, the only two arithmetic operations are addition and multiplication.

This next illustration shows the same principle of universality with combinations of NAND gates rather than combinations of NOR gates:

Once again we see DeMorgan's Theorem in action, where a long complementation bar may be "broken" into shorter pieces with a corresponding change of arithmetic operation below the break (e.g.  $\overline{A} \, \overline{B}$  becomes  $\overline{A} + \overline{B}$  which becomes A + B after canceling the double-bars). This example, like the others, shows the power of Boolean algebra as a means of expressing logical functions: it may not be apparent by inspection of the diagram how combining three NAND gates results in an OR function, but a rule such as DeMorgan's Theorem lets us manipulate these symbols to prove that equivalence. In other words, Boolean algebra is a *tool* for understanding combinational logic.

Combinational gate circuits may be created to implement any conceivable digital function. The examples shown so far merely illustrate one application, and that is the creation of basic logic functions using just one type of "universal" gate.

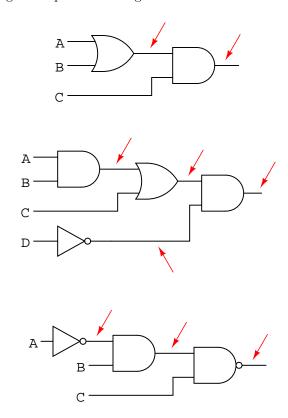

The practical procedure for deriving a Boolean expression from any combinational gate circuit diagram is apparent in both the NOR and NAND combinational logic examples: begin by labeling the inputs with unique letters (variables), then label the output terminals of each logic gate based on those inputs and the Boolean mathematical operation for each logic function (e.g. addition for OR, multiplication for AND, complementation for NOT), repeating this procedure through to the final output(s) of the circuit. Similarly, the procedure for determining the logic states within any combinational gate circuit diagram is to label all the given input states, then reference truth tables to determine the output state of each gate those inputs feed into; then repeat this procedure as

the output states of those gates feed into the input terminals of other gates. A truth table may be generated for any combinational function the same way: analyze all logic states within the circuit for every possible combination of input states, the number of rows in this truth table being equal to 2 raised to the power of the number of discrete inputs.

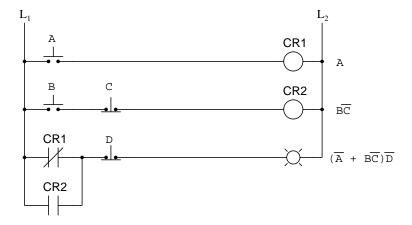

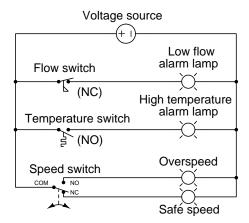

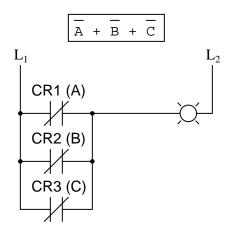

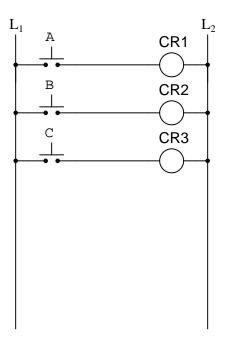

# 3.3 Combinational relay logic

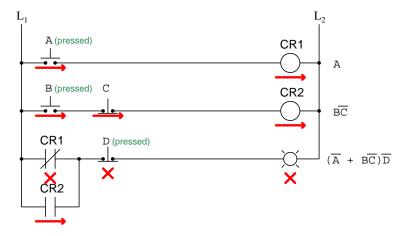

Logic functions and Boolean algebra are abstractions, and as such are independent of physical form. This means the same principles apply to digital circuits built using different technology, for example electromechanical relays rather than semiconductor gates. Consider the following "ladder logic" relay circuit shown below, using pushbutton switches for inputs and a lamp for the single output. We will define a 1 state as electrically conductive (for a switch contact) or energized (for a load), and write a Boolean expression to the right of each "rung" in the "ladder" circuit. With these definitions, series-connected contacts implement the AND function, parallel-connected contacts implement the OR function, and normally-closed contacts represent the NOT function:

The state of relay coil CR1 is identical to the state of switch A's actuation (i.e. 1 = pressed switch = closed contact = energized coil), and so that coil's Boolean expression is simply A. In the next rung we have a normally-open B switch in series with a normally-closed C switch, and so coil CR2's expression is  $B\overline{C}$ . Relay contact CR2 is normally-open and so carries with it the same state as coil CR2  $(B\overline{C})$ , but contact CR1 is normally-closed and so it inverts or complements its coil's state  $(\overline{A})$ . Those two relay contacts are connected together in parallel, and so their combined expression is the Boolean  $sum \overline{A} + B\overline{C}$ . Connected in series with those paralleled relay contacts is a normally-closed pushbutton switch  $\overline{D}$ , and so the expression of the lamp in the last rung is the Boolean  $product (\overline{A} + B\overline{C})\overline{D}$ .

Similar to gate circuits, the procedure for deriving a Boolean expression from any combinational relay circuit diagram begins by labeling the inputs with unique letters (variables), then labeling each relay coil based on the Boolean mathematical operation for each connection type (e.g. addition for parallel, multiplication for series, complementation for normally-closed), repeating this procedure through to the final load(s) of the circuit.

$<sup>^5</sup>$ The term "ladder logic" refers to the ladder-like orientation of the components and connecting wires in the diagram. Each horizontal row is called a *rung*, while the two vertical lines (representing the poles of a voltage source) are called *rails*. The voltage source symbol is usually omitted for simplicity, with the labels L1 and L2 representing these "line voltage" rails not unlike  $V_{CC}$  and  $V_{EE}$  in a bipolar logic gate circuit.

$<sup>^6</sup>$ This would be *positive logic* as applied to a relay circuit, analogous to defining 1 as a "high" voltage state and 0 as a "low" voltage state for a semiconductor gate circuit.

Logic states within a relay ladder logic circuit are easy to track using simple annotations to represent the electrical status of each contact and each load. I recommend a line or arrow drawn near the component to represent *continuity* (switch) or *energization* (load), and an "X" symbol to represent *non-continuity* (switch) or *de-energization* (load). For example, the previous ladder logic circuit is shown here annotated for a condition where switches A, B, and D are pressed but C is released:

Switch contacts A and B are both closed (lines drawn) because they are normally-open switches and are both being pressed. Switch C is closed (line drawn) because it is normally-closed and is not being pressed. Switch D is open (X drawn) because it is normally-closed and is being pressed.

Relay coils CR1 and CR2 are both energized (lines drawn) because there is electrical continuity through their rungs. Relay contact CR1 is open (X drawn) because it is normally-closed and actuated by its energized coil. Relay contact CR2 is closed (line drawn) because it is normally-open and actuated by its energized coil.

Whether the contact in question is a pushbutton switch or a relay contact, its electrical status is a function of its *normal* type and its actuation state. Always remember that the "normal" condition for any electrical switch is its state when at rest (i.e. no actuating stimulus applied), and that electrical contact symbols are always drawn<sup>7</sup> in their "normal" (resting) states.

<sup>&</sup>lt;sup>7</sup>This is why one should never draw a slash mark through a relay contact symbol as a means to annotate closure, because this unnecessarily confuses the disparate concepts of a switch's *current* status with its *normal* status. Sadly, this is an all-too-common habit both of students and of (some) working professionals, and it represents a temptation to conflate two different concepts in a misguided attempt to simplify the task of relay circuit analysis. A relay contact drawn with a diagonal slash through it is a *normally*-closed contact, and not necessarily in its closed state at the time of analysis.

# 3.4 Boolean expressions into circuits

At times it is necessary to design a digital circuit to implement a given Boolean expression. In such cases the procedure is simply to step through the Boolean expression using proper algebraic order-of-operations<sup>8</sup>, applying the following equivalent circuit structures to the Boolean operations:

- Boolean addition is equivalent to the OR function, also equivalent to parallel switch contacts

- Boolean multiplication is equivalent to the AND function, also equivalent to series switch contacts

- ullet Boolean **inversion** is equivalent to the NOT function, also equivalent to normally-closed switch contacts

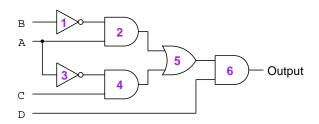

For example, suppose the Boolean expression we needed to implement is as follows:

Output =

$$D(A\overline{B} + \overline{A}C)$$

The proper order of operations for evaluating this expression is shown here:

- 1. Invert the value of B

- 2. Multiply  $\overline{B}$  by A

- 3. Invert the value of A

- 4. Multiply  $\overline{A}$  by C

- 5. Add  $A\overline{B}$  and  $\overline{A}C$

- 6. Multiply  $A\overline{B} + \overline{A}C$  by D

<sup>&</sup>lt;sup>8</sup>Beginning algebra students typically learn a mnemonic such as PEMDAS to remember which operations take precedence over others. In the case of PEMDAS, it is first any operation enclosed within  $\underline{P}$  arentheses, followed by  $\underline{E}$ xponents, then by  $\underline{M}$ ultiplication and  $\underline{D}$ ivision, and finally by  $\underline{A}$ ddition and  $\underline{S}$ ubtraction. Boolean order-of-operations is simpler because there is no such thing as an exponent, division, or subtraction. A comparable mnemonic for Boolean expressions is PIMA:  $\underline{P}$  arentheses followed by  $\underline{M}$  ultiplication, followed by  $\underline{M}$  ultiplication, followed by  $\underline{A}$ ddition.

Building a gate circuit to implement  $D(A\overline{B} + \overline{A}C)$  is as simple as following this ordered list, using a NOT gate for inversion, an AND gate for multiplication, and an OR gate for addition. Note the number labels for each of the logic gates in the schematic diagram, showing which logic gate implements which step we followed with mathematical order-of-operations.

- 1. Invert the value of B Connect input B to a NOT gate

- 2. Multiply  $\overline{B}$  by A Connect the NOT gate's output to one input of an AND gate, with the other AND gate input connected to input A

- 3. Invert the value of A Connect input A to a second NOT gate

- 4. Multiply  $\overline{A}$  by C Connect the second NOT gate's output to one input of a second AND gate, with the other AND gate input connected to input C

- 5. Add  $A\overline{B}$  and  $\overline{A}C$  Connect the two AND gate outputs to the inputs of an OR gate

- 6. Multiply  $A\overline{B} + \overline{A}C$  by D Connect the OR gate's output to one input of a third AND gate, and input D to the other input of this AND gate

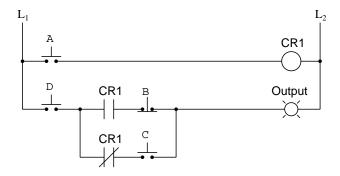

Much the same is true for creating a relay logic circuit from a Boolean expression: we use normally-closed contacts to invert, series-connected contacts for multiplication, and parallel-connected contacts for addition. Again, implementing the Boolean expression  $D(A\overline{B} + \overline{A}C)$ , but this time in relay ladder logic form:

A useful strategy for logic circuits with mechanical switch inputs to minimize the number of electromechanical relays required is to only include a relay when a variable appears more than once in the Boolean expression. For the expression  $D(A\overline{B} + \overline{A}C)$  only A requires a relay. All other inputs are simply switches wired NO or NC as needed:

If the given Boolean expression contains no repeated variables, the circuit may be constructed entirely of switches with no relays necessary!

# 3.5 Truth tables into circuits

When designing a digital logic circuit to perform some practical function, we usually begin the design process by sketching a truth table describing exactly what we wish this circuit to do. The truth table is where we declare which input state combinations will cause the output to achieve a certain state. Once we've defined our truth table, we need to find some way to translate this abstract representation into a real working circuit diagram.

Fortunately, Boolean expressions make this process relatively straightforward. The following subsections describe slightly different methods of developing a Boolean expression from any arbitrary truth table, and then from that Boolean expression we may create a logic gate or relay "ladder logic" circuit to fulfill the function (as described in earlier sections).

The first technique utilizes a Boolean form called sum-of-products (SOP), consisting of a Boolean expression that is a sum of terms comprised of multiple variables multiplied together. For example, ABC + DEF is a sum-of-products where ABC and DEF are both products that are being added (summed) together. The basic circuit form used to implement any SOP expression is a set of AND gates (or series-connected switch contacts) for each product and an OR gate (or parallel connection) for the sum. The basic SOP technique works very well when a minority of the truth table's output values are true (1).

The second technique is a variation of sum-of-products method optimized to work best when a minority of the truth table's output values are false (0).

The third technique uses a Boolean form called product-of-sums (POS), consisting of a Boolean expression that is the product of several sums contained in parentheses. For example, (A + B + C)(D + E + F) is a product-of-sums where (A + B + C) and (D + E + F) are both sums that are being multiplied together. The basic circuit format for a POS expression is a set of OR gates (or parallel-connected switch contacts) for each sum and an AND gate (or series connection) for the product. The POS technique works well for truth tables where a minority of the output values are false (0).

In full disclosure, any of these techniques may be used to translate a given truth table into a correct circuit. What makes one of them better than another for any specific problem is really the balance of true (1) versus false (0) states in the truth table's output column. That is to say, some techniques generate Boolean expressions with fewer terms than others for a given truth table, and therefore translate that truth table into equivalent circuits with fewer components than others.

For students new to this topic I recommend mastering the first two techniques, both based on sum-of-products (SOP) Boolean expressions. The product-of-sums (POS) technique works well, but can be confusing because nearly everything about it seems "backwards" compared to the basic SOP technique. If you master the SOP-based techniques – which I call "Sum of Products" and "Negative Sum of Products" respectively – you will be able to translate any arbitrary truth table into a reasonably efficient circuit with a minimum of confusion.

# 3.5.1 Sum of Products

The number of products in any *sum-of-products* Boolean expression is equal to the number of "1" output states listed in the truth table. Take the following truth table as an example:

| A | В | $\mathbf{C}$ | Output |

|---|---|--------------|--------|

| 0 | 0 | 0            | 0      |

| 0 | 0 | 1            | 1      |

| 0 | 1 | 0            | 0      |

| 0 | 1 | 1            | 0      |

| 1 | 0 | 0            | 0      |

| 1 | 0 | 1            | 0      |

| 1 | 1 | 0            | 0      |

| 1 | 1 | 1            | 1      |

Only two rows in this table contain "1" output states, and so our sum-of-products expression may be described in the following terms:

The Output will be 1 when

$$A=0$$

and  $B=0$  and  $C=1$  . . . or . . . when  $A=1$  and  $B=1$  and  $C=1$

The italicized words and and or are intentionally emphasized for the purpose of associating with Boolean operations of multiplication and addition, respectively. Writing this same statement in mathematical form:

$$Output = \overline{A} \, \overline{B}C + ABC$$

The product  $\overline{ABC}$  expresses the "truth" of the second row, where A=0 and B=0 and C=1, the individual variables complemented or uncomplemented as necessary to make the product equal 1 for those conditions. The product ABC expresses the "truth" of the eighth row, where A=1 and B=1 and C=1. The overall function is the sum of these two products; i.e. the function will output a 1 if either of these products are "true". Each of the two products represents a three-input AND function, while the sum of those two products represents a two-input OR function.

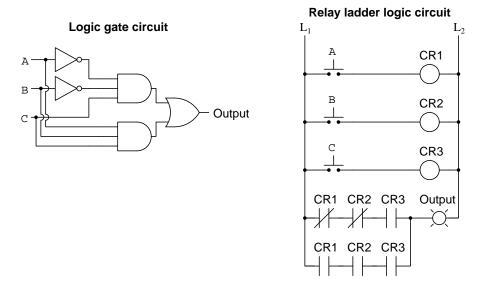

Taking this sum-of-products expression (Output =  $\overline{A}\overline{B}C + ABC$ ) and converting into both logic gate and relay ladder logic circuits as previously described:

The structure of these two circuits reflects the structure of the sum-of-products Boolean expression. Note how the product  $\overline{A}\,\overline{B}C$  is evident in the upper AND gate of the logic gate circuit, as well as in the second rung from the bottom of the ladder logic diagram; also how the product ABC is represented by the lower AND gate and also by the lowest rung. The OR gate (and the paralleled network of the lowest two rungs) embodies the sum between the two products.

If we consider the fact that the number of products in a sum-of-products Boolean expression is equal to the number of truth table rows with a "1" output state, it becomes apparent that both the sum-of-products expression and the equivalent circuit(s) becomes larger as the number of "1" output states in the truth table increases. In other words, the more "1" output states in a truth table, the larger the sum-of-products solution will be. For truth tables containing more "1" output states than "0" output states, this fact can be problematic.

In answer to this challenge, multiple techniques exist to derive Boolean expressions from truth tables. The best technique for any application depends on the nature of the truth table, in particular whether the function has a super-majority of "1" or "0" output states.

# 3.5.2 Negative Sum of Products

One such alternative approach designed to work best for truth tables containing a minority of "0" output states, is to write a sum-of-products expression while thinking in "negative" terms, identifying Boolean products describing truth table rows with "0" output states rather than "1" output states. The intrinsic problem-solving technique here is to simplify the problem, imagining the truth table's majority-1 output states to be majority-0 instead and then writing an SOP expression for that inverted table using the previously-described technique. To make the SOP expression correct for the original table, one must place a long inversion (complement) bar covering all terms. Take the following truth table as an example:

| A | В | $\mathbf{C}$ | Output |

|---|---|--------------|--------|

| 0 | 0 | 0            | 1      |

| 0 | 0 | 1            | 1      |

| 0 | 1 | 0            | 1      |

| 0 | 1 | 1            | 0      |

| 1 | 0 | 0            | 1      |

| 1 | 0 | 1            | 0      |

| 1 | 1 | 0            | 1      |

| 1 | 1 | 1            | 1      |

Only two rows in this table contain "0" output states, and so our sum-of-product expression may be described in the following terms:

The Output will be 0 when

$$A=0$$

and  $B=1$  and  $C=1$  . . . or . . . when  $A=1$  and  $B=0$  and  $C=1$

Once again the italicized words and and or intentionally emphasize the Boolean operations of multiplication and addition, respectively. Writing this same statement in mathematical form:

$$Output = \overline{\overline{A}BC + A\overline{B}C}$$

The product  $\overline{ABC}$  expresses the "negative truth" of the fourth row, where A=0 and B=1 and C=1. The product  $A\overline{B}C$  expresses the "negative truth" of the sixth row, where A=1 and B=0 and C=1. By "negative truth" we mean that the overall function is the *inverted* sum of these two products; i.e. the output is 0 if either of these products equal 1. In other words, if either  $\overline{ABC}$  or  $A\overline{B}C$  is true, the output will be false. Each of the two products represents an AND function, while the final sum and negation represents a NOR function.

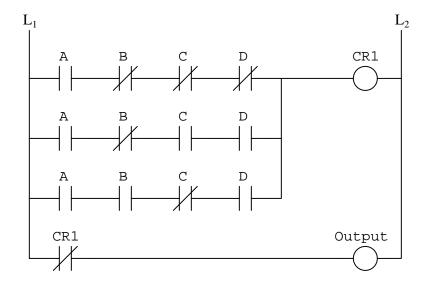

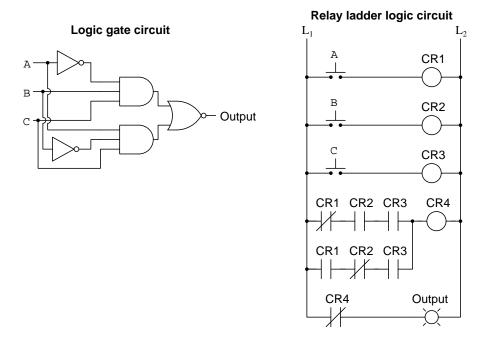

Taking this sum-of-products expression (Output =  $\overline{A}BC + A\overline{B}C$ ) and converting into both logic gate and relay ladder logic circuits as previously described:

Once again we see how the circuits' topologies reflect the structure of the sum-of-products Boolean expression. Note how the product  $\overline{A}BC$  is evident in the upper AND gate of the logic gate circuit, as well as in the third rung from the bottom of the ladder logic diagram; also how the product  $A\overline{B}C$  is represented by the lower AND gate and also by the second rung from the bottom. The NOR gate implements the inverted sum of the two products in the gate circuit. In the relay circuit, this final inversion requires a fourth relay with a normally-closed contact, its coil powered by the positive sum (parallel network) of two rungs.

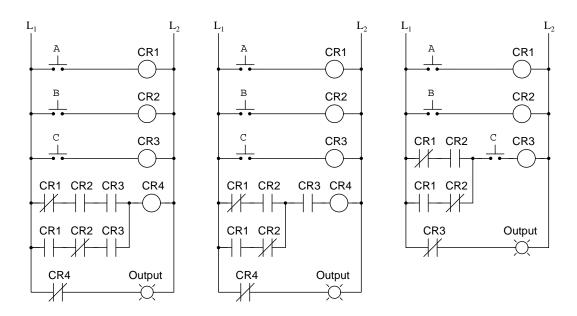

Close inspection of the relay ladder logic circuit for the Boolean expression  $\overline{A}BC + A\overline{B}C$  reveals potential for simplification. Notice how the two normally-open CR3 contacts are redundant to each other, and how we may implement the exact same logical function by eliminating one of those CR3 contacts. Going further, we may eliminate one relay altogether, since C now appears only once in the Boolean expression and therefore relay CR3 contributes nothing to the circuit. The following set of diagrams show the original circuit (left) and two levels of simplification (middle and right):

The first simplification – eliminating one of the CR3 relay contacts – could have been done (first) to the Boolean expression prior to drawing any circuit diagram. If we examine the two products underneath the long complement bar, we see both of them have a common C variable. This means we may  $factor\ C$  out of the two products as demonstrated here:

$$\overline{\overline{A}BC + A\overline{B}C} = \overline{C(\overline{A}B + A\overline{B})}$$

The simplified expression is directly implemented in the middle relay ladder logic diagram shown above. The far-right diagram simplification comes not from Boolean algebra, but rather from the realization that relay CR3 just wasn't necessary.

Boolean algebra offers several identities and properties useful<sup>9</sup> for simplifying long expressions. A full exploration of these techniques will be left to another learning module.

<sup>&</sup>lt;sup>9</sup>Interestingly, while simplified Boolean expressions require fewer circuit components to implement, which typically decreases construction cost and increases operational reliability, Boolean simplifications lend little benefit to programmed logic functions, whether in a microcontroller or in a PLC (Programmable Logic Controller). AND, OR, and NOT functions programmed in code cost nothing either in capital investment or in non-reliability, and so a large expression programmed into a digital controller works just as well as an equivalent reduced expression. In fact, there are circumstances where the simplified version of a Boolean logic function actually makes less sense to anyone examining the code than the raw expression generated directly from the truth table, in which case Boolean reduction does more harm than good!

### 3.5.3 Product of Sums

Another alternative approach well-suited to truth tables having more "1" output states than "0" is to write a product-of-sums Boolean expression (e.g. (A+B+C)(D+E+F)) rather than a sum-of-products (e.g. ABC+DEF). Here, the strategy is to identify those "0" input conditions leading to an output value of 0. As before, we will begin with an example truth table, our goal being to derive both logic gate and relay ladder logic circuit implementations of the arbitrary function represented by the truth table:

| A | В | $\mathbf{C}$ | Output |

|---|---|--------------|--------|

| 0 | 0 | 0            | 1      |

| 0 | 0 | 1            | 1      |

| 0 | 1 | 0            | 1      |

| 0 | 1 | 1            | 1      |

| 1 | 0 | 0            | 0      |

| 1 | 0 | 1            | 1      |

| 1 | 1 | 0            | 1      |

| 1 | 1 | 1            | 0      |

The "0 truth" sum representing the fifth row is  $\overline{A}+B+C$ , the individual variables complemented or uncomplemented as necessary to yield a sum of 0 when A=1 and B=0 and C=0. The "0 truth" sum representing the eighth row is  $\overline{A}+\overline{B}+\overline{C}$ . Multiplying 11 these two sums to arrive at a product-of-sums expression for the truth table:

$$(\overline{A} + B + C)(\overline{A} + \overline{B} + \overline{C})$$

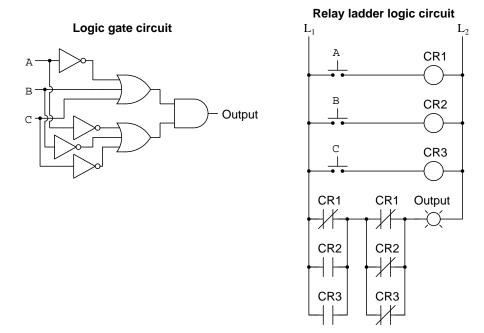

Implementing this Boolean product-of-sums expression in circuit form requires either OR gates or parallel relay contacts for the sums (addition), and AND gates or series relay contacts for the product (multiplication).

$<sup>^{10}</sup>$ At first it may seem incorrect to use Boolean addition (which is normally equivalent to an OR function) to associate particular states of A, B, and C, but this is actually legitimate because we are thinking in "negative" terms. Recall that a three-input OR function outputs a 1 if A=1 or B=1 or C=1; but it is also true to say that an OR function outputs a 0 if A=0 and B=0 and C=0. Therefore, when thinking in terms of a "0" result, it is fair to use Boolean addition (i.e. an "OR" function) to identify some simultaneous set of "0" input states. This is actually an example of DeMorgan's Theorem in action: inverting both the inputs and output of a fundamental logic function changes its type from OR to AND or vice-versa.

<sup>&</sup>lt;sup>11</sup>The reason we choose Boolean *multiplication* to piece these two sums together is because we want the output to be 0 if either sum is equal to 0. Again, this may seem wrong to use multiplication to represent an "or" condition, but it works because we are thinking in "negative" terms, and an AND function (multiplication) always has a 0 output if *any* of its inputs are 0.

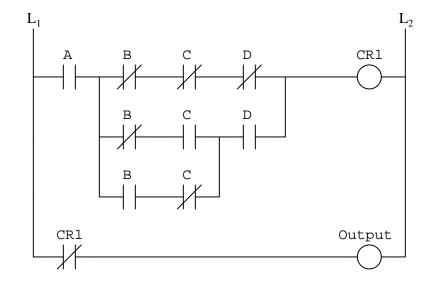

Both equivalent logic gate and relay ladder logic circuits for the product-of-sums expression  $(\overline{A} + B + C)(\overline{A} + \overline{B} + \overline{C})$  are shown in the following diagrams:

As with the previous example, a close inspection of the relay ladder logic circuit reveals potential for simplification. Note how the two normally-closed CR1 relay contacts are redundant to each other, and may be replaced by a single normally-closed CR1 contact passing power to the Output lamp: any time pushbutton A is unpressed, both CR1 contacts will be in their closed (resting) states, guaranteeing energization of the load. From an electrical perspective, it makes no sense to have two series-connected relay contacts with the exact same state doing what one contact could do by itself. That simplification leads to the next, where we realize with only one CR1 contact in the circuit we may simply replace it with a normally-closed "A" pushbutton switch and dispense with one relay.

The following diagrams show these three versions of the circuit, the original (left), the first simplification (center), and the simplest version (right):

Mathematically demonstrating why these three circuits are functionally equivalent is much more difficult to do with a product-of-sums expression than for a sum-of-products expression, which is a strong argument against the product-of-sums approach of converting a truth table into an equivalent circuit and simplifying through Boolean algebraic techniques.

# Chapter 4

# Historical References

This chapter is where you will find references to historical texts and technologies related to the module's topic.

Readers may wonder why historical references might be included in any modern lesson on a subject. Why dwell on old ideas and obsolete technologies? One answer to this question is that the initial discoveries and early applications of scientific principles typically present those principles in forms that are unusually easy to grasp. Anyone who first discovers a new principle must necessarily do so from a perspective of ignorance (i.e. if you truly discover something yourself, it means you must have come to that discovery with no prior knowledge of it and no hints from others knowledgeable in it), and in so doing the discoverer lacks any hindsight or advantage that might have otherwise come from a more advanced perspective. Thus, discoverers are forced to think and express themselves in less-advanced terms, and this often makes their explanations more readily accessible to others who, like the discoverer, comes to this idea with no prior knowledge. Furthermore, early discoverers often faced the daunting challenge of explaining their new and complex ideas to a naturally skeptical scientific community, and this pressure incentivized clear and compelling communication. As James Clerk Maxwell eloquently stated in the Preface to his book A Treatise on Electricity and Magnetism written in 1873,

It is of great advantage to the student of any subject to read the original memoirs on that subject, for science is always most completely assimilated when it is in its nascent state . . . [page xi]

Furthermore, grasping the historical context of technological discoveries is important for understanding how science intersects with culture and civilization, which is ever important because new discoveries and new applications of existing discoveries will always continue to impact our lives. One will often find themselves impressed by the ingenuity of previous generations, and by the high degree of refinement to which now-obsolete technologies were once raised. There is much to learn and much inspiration to be drawn from the technological past, and to the inquisitive mind these historical references are treasures waiting to be (re)-discovered.

# 4.1 Claude Shannon makes the connection

One of the great minds of electrical engineering, Claude Shannon, recognized the application of Boolean logic to relay switching circuits while studying for his Master's degree at Massachusetts Institute of Technology (MIT) in 1940. His thesis paper submitted as part of the graduation requirements for this degree has been widely hailed as a breakthrough for the analysis of digital circuits.

On pages 2 and 3 of Shannon's paper, we read the following paragraph where he states an equivalence between propositional logic and electrical switching:

The method of solution of these problems which will be developed here may be described briefly as follows: Any circuit is represented by a set of equations, the terms of the equations representing the various relays and switches of the circuit. A calculus is developed for manipulating these equations by simple mathematical processes, most of which are similar to ordinary algebraic [sic] algorithms. This calculus is shown to be exactly analogous to the Calculus of Propositions used in the symbolic study of logic. For the synthesis problem the desired characteristics are first written as a system of equations, and the equations are then manipulated into the form representing the simplest circuit. The circuit may then be immediately drawn from the equations. By this method it is always possible to find the simplest circuit containing only series and parallel connections, [page 2]

and for certain types of functions it is possible to find the simplest circuit containing any type of connection. In the analysis problem the equations representing the given circuit are written and may then be interpreted in terms of the operating characteristics of the circuit. It is also possible with the calculus to obtain any number of circuits equivalent to a given circuit. [page 3]

Note his express intent of using Boolean algebra as a tool for circuit minimization. In his era, when logical functions required electromechanical relays to implement, the minimization of relay coils and contacts meant a logic circuit with fewer components, translating into lower cost of manufacture and greater reliability. When solid-state (semiconductor) transistor-based logic circuits appeared, this same Boolean algebra proved useful as a tool for determining the simplest (and therefore most compact) circuit that could be etched into a silicon chip.

Shannon's mathematical approach to switching circuits was to consider an open circuit to have a value of 1, and a closed circuit to have a value of 0. He referred to this as the hinderance of the switching network, similar in concept to resistance but discrete in nature rather than continuous. This is inverse of how we now consider most switching circuits in Boolean form, energized (closed) being 1 and de-energized (open) being 0. Based on his definition of 0 and 1 for switching circuits, Shannon then reasoned that series switch networks would be represented by the Boolean addition of their hinderance values and that parallel switch networks would be represented by the multiplication of their hinderances. Again, this seems backwards from our modern perspective where we relate series-connected switch contacts to the logical AND function (Boolean multiplication) and parallel contacts to the OR function (addition), but it is important to realize that either approach is mathematically valid. As with any other application of axiomatic reasoning, the outcomes depend greatly upon one's initial definitions.

Shannon then proceeds in his paper to present a set of postulates relating 0 and 1 values to open and closed switching networks (pages 5 and 6):

| Boolean expression          | Electrical interpretation                                                             |

|-----------------------------|---------------------------------------------------------------------------------------|

| $0 \cdot 0 = 0$             | A closed circuit in parallel with a closed circuit is a closed circuit                |

| 1 + 1 = 1                   | An open circuit in series with an open circuit is an open circuit                     |

| 1 + 0 = 0 + 1 = 1           | An open circuit in series with a closed circuit in either order is an open circuit    |

| $0 \cdot 1 = 1 \cdot 0 = 0$ | A closed circuit in parallel with an open circuit in either order is a closed circuit |

| 0 + 0 = 0                   | A closed circuit in series with a closed circuit is a closed circuit                  |

| $1 \cdot 1 = 1$             | An open circuit in parallel with an open circuit is an open circuit                   |

Rather than use bar-lines over Boolean variables to denote inversion or negation, Shannon opted to use apostrophe ("prime") characters. So, rather than print the inversion of X as  $\overline{X}$ , Shannon writes X'. If groups of variables are inverted (e.g.  $\overline{A+B}$ ), one must use parentheses to group the variables together and then follow the closing parentheses symbol with an apostrophe, for example (A+B)'. This choice of symbols may very well have been a result of the crude typesetting available in Shannon's time, apostrophes being much easier to properly typeset on a page than bar-lines.

On page 11 of his paper, Shannon neatly summarizes and compares relay switching logic with Propositional Logic:

| Symbol | Relay interpretation                                                      | Propositional interpretation                               |

|--------|---------------------------------------------------------------------------|------------------------------------------------------------|

| X      | The circuit $X$                                                           | The proposition $X$                                        |

| 0      | The circuit is closed                                                     | The proposition is false                                   |

| 1      | The circuit is open                                                       | The proposition is true                                    |

| X + Y  | The series connection of circuits $X$ and $Y$                             | The proposition which is true if either $X$ or $Y$ is true |

| XY     | The parallel connection of circuits $X$ and $Y$                           | The proposition which is true if both $X$ and $Y$ are true |

| X'     | The circuit which is open when $X$ is closed, and closed when $X$ is open | The contradictory proposition $X$                          |

| =      | The circuits open and close simultaneously                                | Each proposition implies the other                         |

Again, recall that Shannon assumed an electrical open to be a 1 and a short to be a 0, which is why series is equivalent to addition and parallel to multiplication in his application of Boolean algebra. This is opposite of how modern relay logic circuits are typically interpreted, with an energized load (i.e. a closed switch allowing current) being 1 and a de-energized load (i.e. an open switch preventing current) being 0.

# 4.2 NASA's Apollo Guidance Computer

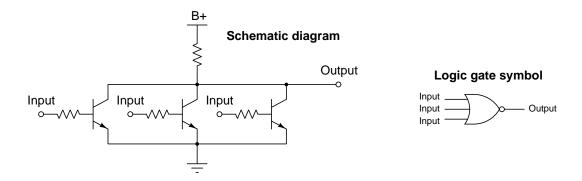

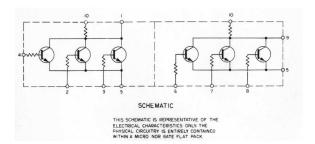

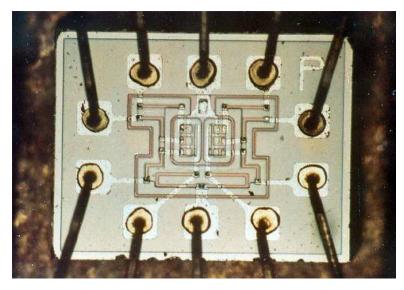

The digital computer used for guidance functions in the 1960's era Apollo spacecraft (the one used to transport the first humans to Earth's Moon) built by NASA used bipolar transistor logic, consisting almost entirely of NOR logic gates. The schematic diagram for each three-input NOR gate was as follows, along with its corresponding logic gate symbol:

Note how the positive power supply terminal is labeled B+, an anachronistic reference to the positive terminal of a high-voltage battery (hence the letter "B") used to power vacuum tube circuits. Based on the knowledge that bipolar transistors are normally "off" devices, and require the base-emitter junction to be forward-biased in order to turn "on", we can tell if any input goes to a high state (i.e. connected to the positive rail of the DC power source), that respective NPN transistor will turn on and bring the output terminal's potential down (nearly) to ground. In other words, any high input forces the output to be low: the very definition of a NOR function.

The three transistors can only sink current, and therefore this NOR gate's sourcing capability is limited by the resistor between the three collectors and the B+ power supply terminal. In other words, this NOR gate had a significantly greater current-sinking rating than its current-sourcing rating.

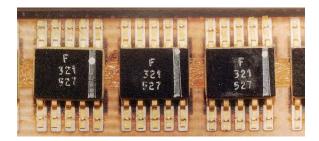

A rather short technical document entitled "A Case History Of The AGC Integrated Logic Circuits" describes how nearly the entire computer consisted of these three-input NOR logic gates:

The standardization approach, which is particularly adaptable to digital computers, has been demonstrated with the Polaris flight computer and extended with integrated circuits to the Apollo Guidance Computer. Both computers were designed to use a three input NOR Gate as the only logic element. All logic functions are generated by interconnecting the three input NOR Gate with no additional logic blocks, resistors, or capacitors. At first glance, it appears that using only one type of logic block greatly increases the number of blocks required for the computer. But, by judiciously selecting and organizing the logic functions it is quickly apparent that few additional blocks are necessary. The few additional units required are greatly counterbalanced by the increased reliability gained during both the manufacturing of components and fabrication of the components into modules. [page 3]