# Modular Electronics Learning (ModEL) PROJECT

#### DIGITAL MEMORY

© 2020-2025 by Tony R. Kuphaldt – under the terms and conditions of the Creative Commons Attribution 4.0 International Public License

#### Last update = 16 January 2025

This is a copyrighted work, but licensed under the Creative Commons Attribution 4.0 International Public License. A copy of this license is found in the last Appendix of this document. Alternatively, you may visit http://creativecommons.org/licenses/by/4.0/ or send a letter to Creative Commons: 171 Second Street, Suite 300, San Francisco, California, 94105, USA. The terms and conditions of this license allow for free copying, distribution, and/or modification of all licensed works by the general public.

# Contents

| 1 | Introduction                           |                                                  |    |  |  |  |

|---|----------------------------------------|--------------------------------------------------|----|--|--|--|

|   | 1.1                                    | Recommendations for students                     | 3  |  |  |  |

|   | 1.2                                    | Challenging concepts related to digital memory   | 5  |  |  |  |

|   | 1.3                                    | Recommendations for instructors                  | 6  |  |  |  |

| 2 | Case Tutorial                          |                                                  |    |  |  |  |

|   | 2.1                                    | Example: 16x8 array from 16x4 memory ICs         | 8  |  |  |  |

|   | 2.2                                    | Example: 16x16 array from 16x4 memory ICs        | 10 |  |  |  |

|   | 2.3                                    | Example: 32x4 array from 16x4 memory ICs         | 12 |  |  |  |

|   | 2.4                                    | Example: 64x4 array from 16x4 memory ICs         | 14 |  |  |  |

|   | 2.5                                    | Example: AWG circuit using nonvolatile memory IC | 16 |  |  |  |

| 3 | Tutorial                               |                                                  |    |  |  |  |

|   | 3.1                                    | Punched paper tape                               | 20 |  |  |  |

|   | 3.2                                    | Digital memory principles                        | 22 |  |  |  |

|   | 3.3                                    | Electronic memory                                | 26 |  |  |  |

|   | 3.4                                    | Signal timing                                    | 28 |  |  |  |

|   | 3.5                                    | Combining memory elements                        | 30 |  |  |  |

|   | 3.6                                    | Types of memory elements                         | 35 |  |  |  |

| 4 | Historical References 3                |                                                  |    |  |  |  |

|   | 4.1                                    | Magnetic core memory                             | 40 |  |  |  |

|   | 4.2                                    | Early magnetic hard disk drives                  | 45 |  |  |  |

|   | 4.3                                    | Floating-gate FET transistor patent              | 47 |  |  |  |

| 5 | Derivations and Technical References 5 |                                                  |    |  |  |  |

|   | 5.1                                    | Tri-state logic gate outputs                     | 56 |  |  |  |

|   | 5.2                                    | Digital pulse criteria                           | 58 |  |  |  |

| 6 | Animations 63                          |                                                  |    |  |  |  |

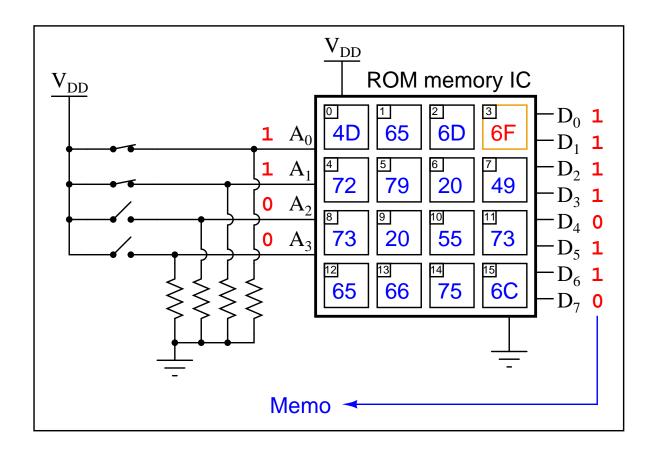

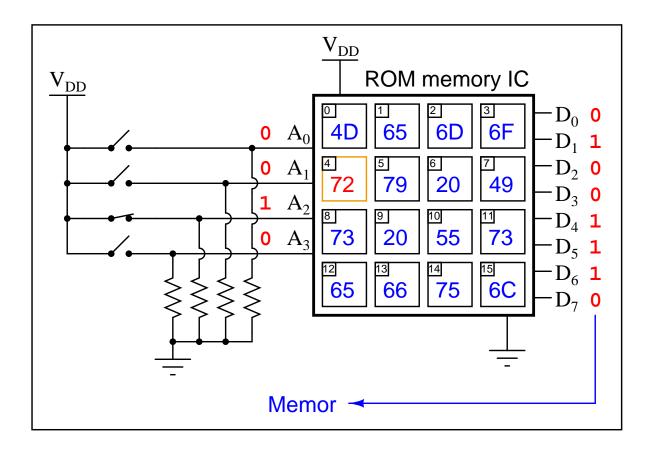

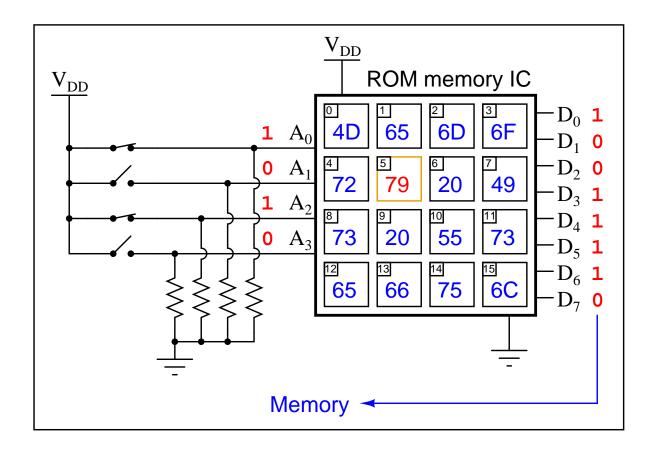

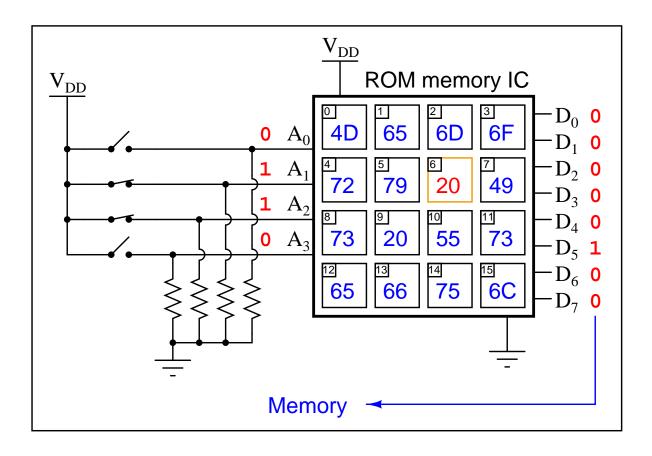

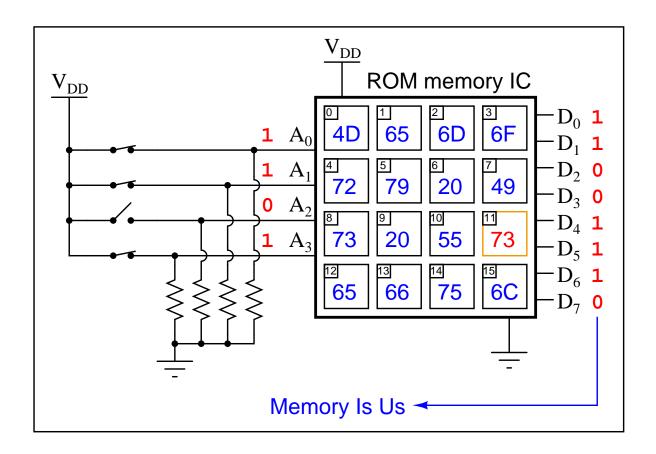

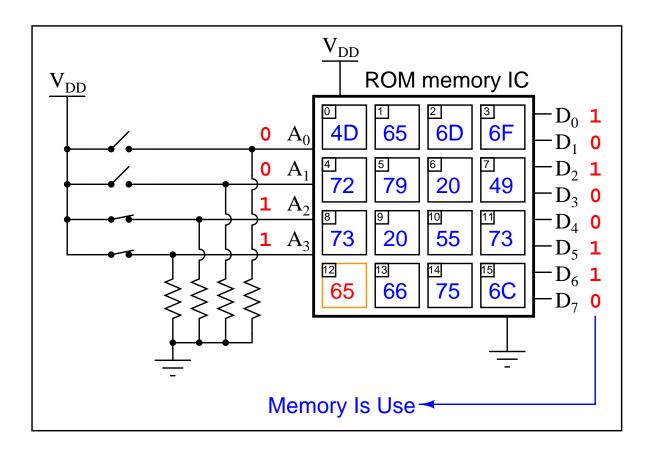

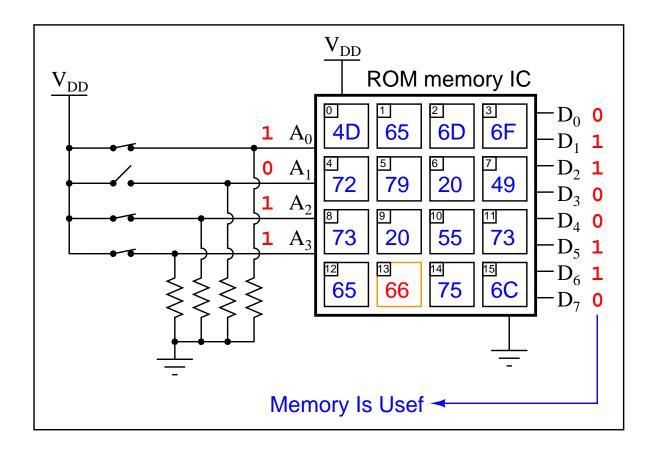

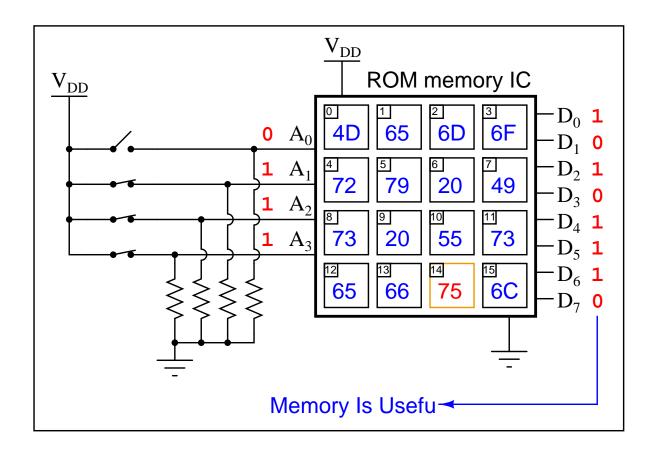

|   | 6.1                                    | Animation of $16 \times 8 \text{ ROM}$           | 64 |  |  |  |

CONTENTS 1

| 7            | Que                                  | tions                                      |  | 81  |  |

|--------------|--------------------------------------|--------------------------------------------|--|-----|--|

|              | 7.1                                  | Conceptual reasoning                       |  | 85  |  |

|              |                                      | 7.1.1 Reading outline and reflections      |  | 86  |  |

|              |                                      | 7.1.2 Foundational concepts                |  | 87  |  |

|              |                                      | 7.1.3 Digital Audio Tape                   |  | 88  |  |

|              |                                      | 7.1.4 Random versus sequential access      |  | 89  |  |

|              |                                      | 7.1.5 Static versus dynamic RAM            |  | 89  |  |

|              |                                      | 7.1.6 Flash versus RAM                     |  | 90  |  |

|              |                                      | 7.1.7 Binary-BCD conversion by memory      |  | 90  |  |

|              | 7.2                                  | Quantitative reasoning                     |  | 91  |  |

|              |                                      | 7.2.1 Miscellaneous physical constants     |  | 92  |  |

|              |                                      | 7.2.2 Introduction to spreadsheets         |  | 93  |  |

|              |                                      | $7.2.3$ 4k $\times$ 8 ROM                  |  | 96  |  |

|              |                                      | 7.2.4 Memory organization                  |  | 96  |  |

|              |                                      | 7.2.5 Storing ASCII text characters        |  | 97  |  |

|              |                                      | 7.2.6 Addressing an expanded memory module |  | 98  |  |

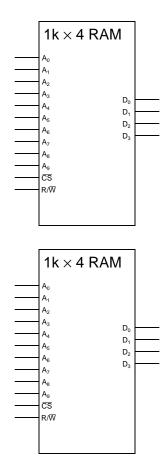

|              |                                      | 7.2.7 Doubling data width                  |  | 99  |  |

|              |                                      | 7.2.8 Doubling address width               |  | 100 |  |

|              |                                      | 7.2.9 Quadrupling address width            |  | 101 |  |

|              |                                      | 7.2.10 Quadrupling data width              |  | 101 |  |

|              | 7.3                                  | Diagnostic reasoning                       |  | 102 |  |

|              |                                      | 7.3.1 Checksums                            |  | 102 |  |

| $\mathbf{A}$ | Pro                                  | em-Solving Strategies                      |  | 103 |  |

| D            | T4                                   |                                            |  | 105 |  |

| D            | mst                                  | actional philosophy                        |  | 109 |  |

| $\mathbf{C}$ | Tools used  Creative Commons License |                                            |  |     |  |

| D            |                                      |                                            |  |     |  |

| $\mathbf{E}$ | Ref                                  | ences                                      |  | 123 |  |

| 123          | <b>1</b> 7                           | on history                                 |  | 105 |  |

| F            | ver                                  | on history                                 |  | 125 |  |

| Index        |                                      |                                            |  |     |  |

2 CONTENTS

# Chapter 1

# Introduction

#### 1.1 Recommendations for students

One of the principal advantages of digital data is its relative ease of storage. Unlike analog data which must find expression in some physical form capable of the same infinitesimal resolution, digital data may be stored in any medium capable of retaining discrete states. The storage of digital data allows for the existence of computer files, digital audio recordings, digital movie recordings, with all the intrinsic advantages (and disadvantages!) of digital. The advantages of digital data storage vastly outweigh the advantages of analog for most applications. The general term we use for any form of digital data storage is memory, although this term is most often applied to integrated circuits intended to store digital data.

Important concepts related to digital memory include the representation of data in **discrete** form, digital **codes**, binary **counting**, data **volatility**, modes of data **access** (e.g. sequential), **latch** and **multivibrator** circuits, **addressing**, **tri-state** logic, **timing diagrams**, propagation **delay**, **set-up** and **hold** times, **decoding**, memory **expansion**, different memory **technologies**, and **electroscopes**.

Here are some good questions to ask of yourself while studying this subject:

- How might an experiment be designed and conducted to demontrate how to read and write solid-state RAM memory? What hypotheses (i.e. predictions) might you pose for that experiment, and what result(s) would either support or disprove those hypotheses?

- How might an experiment be designed and conducted to measure the minimum necessary setup time for a flip-flop? What hypothesis (i.e. prediction) might you pose for that experiment, and what result(s) would either support or disprove that hypothesis?

- How might an experiment be designed and conducted to measure the minimum necessary hold time for a flip-flop? What hypothesis (i.e. prediction) might you pose for that experiment, and what result(s) would either support or disprove that hypothesis?

- What property(ies) of a device or system is/are necessary for it to function as a memory element?

- What is the distinction between reading from memory versus writing to it?

- What is the distinction between address versus data for any particular memory device?

- How may we tell if a memory device is volatile or non-volatile?

- How may we tell if a memory device is sequential- or random-access?

- Why are tri-state logic gates necessary within certain types of memory circuits?

- What timing requirements may be necessary for reliably reading and writing memory data?

- Why do memory timing diagrams sometimes show data states that are both high and low at the same time?

- Why is the duration of the address enable (AE) line for a memory circuit different from the duration of the stable data on the I/O line(s)?

- How do we "expand" a memory array from smaller memory elements?

- What is the purpose of the various "enable" lines on a memory IC?

- What are some of the various sub-types of "read-only" (ROM) memory technologies?

- Where might we use specific types of digital memory technologies (e.g. PROM versus EEPROM, RAM versus magnetic disk, etc.)?

### 1.2 Challenging concepts related to digital memory

The following list cites concepts related to this module's topic that are easily misunderstood, along with suggestions for properly understanding them:

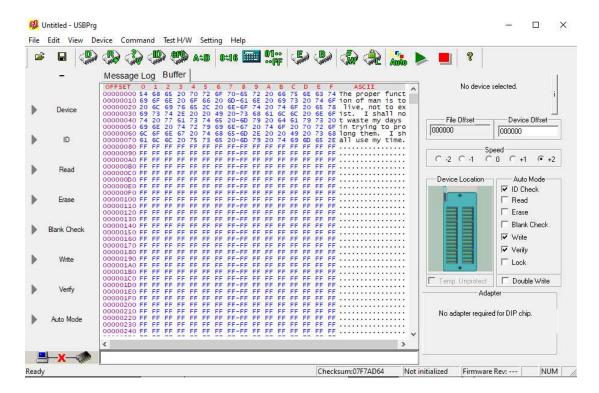

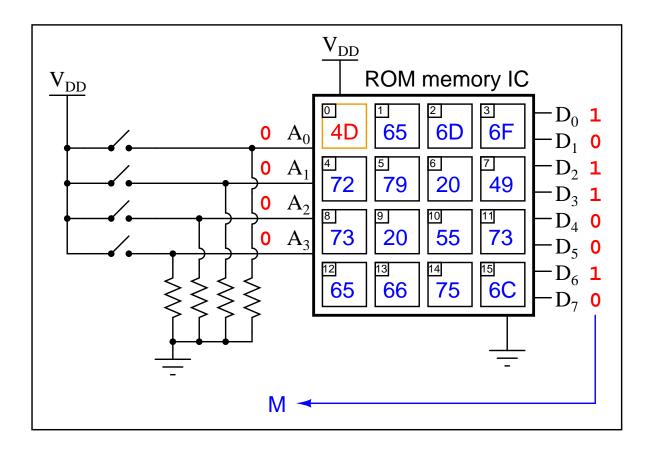

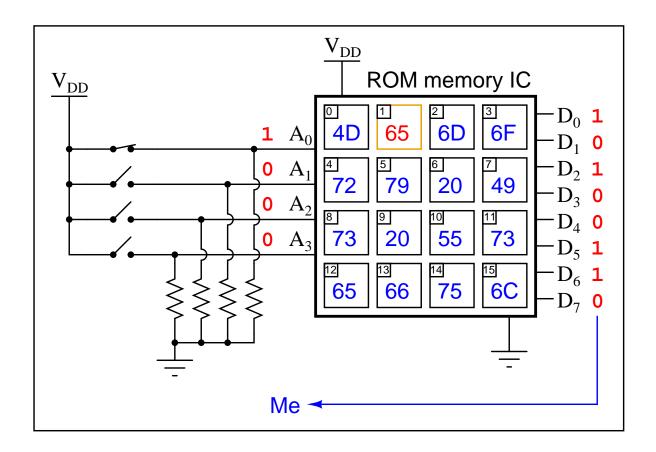

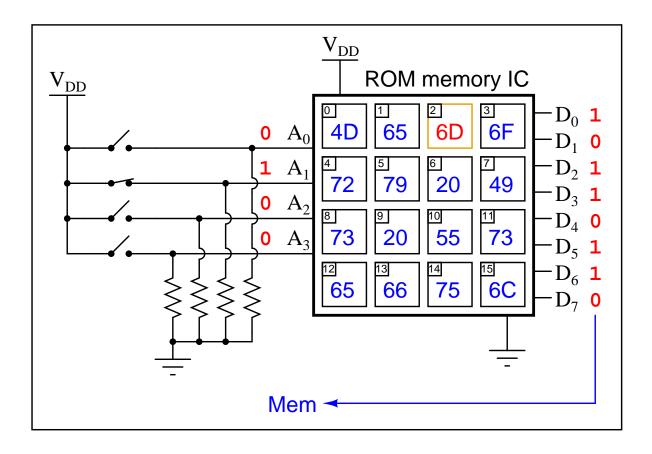

- Reading hex dumps arrays of hexadecimal values showing the contents of a memory module are often referred to as *hex dumps*, and properly interpreting their contents is a skill in itself. Just know that the addresses go in incrementing order as the hex dump is read from left to right, top to bottom, just like reading an English-written document. The "offset" address given in the left-most column simply shows the beginning address value for that row of hex data, each successive column in the hex dump array moving toward the right reflecting an increment in address value from that starting "offset value".

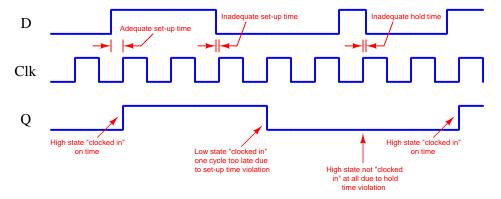

- Set-up and Hold times any digital circuit using timing pulses will have set-up and hold-time requirements, which are *minimum-time specifications* that all input pulse signals must meet in order for the circuit to reliably work. Always remember that these specified times are *minimum*, which means it's perfectly okay to exceed them but not safe to time the signals for less.

- Memory expansion combining multiple memory ICs together to form larger, more practical memory arrays is an important concept in digital systems. Data-word expansion is easy enough to grasp, but address expansion requires more components to implement and tends to cause confusion for students new to the topic.

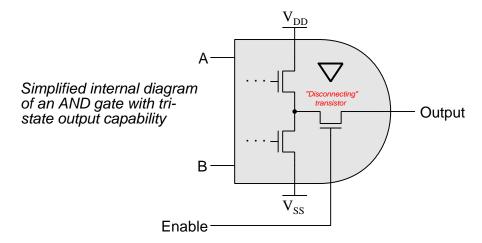

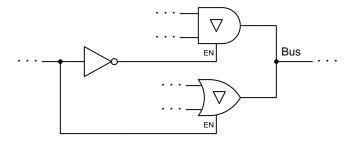

- Tri-state gate outputs logic gates with tri-state output capability are commonly used to allow multiple digital devices to output data to common "bus" lines, only one of those devices being enabled at any given time. Tri-state outputs essentially disconnect the output of the logic gate from its external output terminal when in "Hi-Z" or high-impedance mode. When enabled, a tri-state output acts like the output of any regular logic gate, able to sink or source current.

The *Historical References* chapter contains multiple sections describing memory technologies, some legacy and some still popular. These are useful for applying concepts taught in the Tutorial, as well as for historical context. The *Case Tutorial* chapter also contains sections showing realistic examples of how multiple memory ICs may be interconnected to form memory arrays with wider data words, or with larger address spaces.

#### 1.3 Recommendations for instructors

This section lists realistic student learning outcomes supported by the content of the module as well as suggested means of assessing (measuring) student learning. The outcomes state what learners should be able to do, and the assessments are specific challenges to prove students have learned.

• Outcome – Demonstrate effective technical reading and writing

<u>Assessment</u> – Students present their outlines of this module's instructional chapters (e.g. Case Tutorial, Tutorial, Historical References, etc.) ideally as an entry to a larger Journal document chronicling their learning. These outlines should exhibit good-faith effort at summarizing major concepts explained in the text.

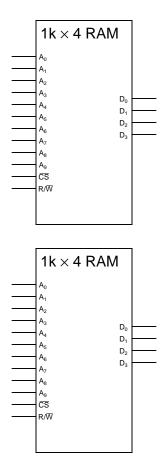

• Outcome – Apply the concept of memory expansion to practical memory circuits

<u>Assessment</u> – Predict logical states on address lines necessary to select a given address in an expanded memory array; e.g. pose problems in the form of the "Addressing an expanded memory module" Quantitative Reasoning question.

• Outcome – Design an expanded memory array circuit

<u>Assessment</u> – Sketch a schematic diagram of a circuit employing multiple static RAM or ROM ICs to form a memory array with more data bits; e.g. pose problems in the form of the "Doubling data width" Quantitative Reasoning question.

<u>Assessment</u> – Sketch a schematic diagram of a circuit employing multiple static RAM or ROM ICs to form a memory array with more addresses; e.g. pose problems in the form of the "Doubling address width" Quantitative Reasoning question.

• Outcome - Apply the concept of checksums to digital data

<u>Assessment</u> – Use hash algorithms to validate the integrity of data files provided by the instructor or by other students, comparing hashes from files claimed to be identical.

• Outcome - Program an EPROM or NVRAM memory device with a specified data set

<u>Assessment</u> – Use a PROM programming tool to load a hex dump style table into the memory IC.

<u>Assessment</u> – Connect switches to the address and data inputs of a static memory IC to program its contents manually.

<u>Assessment</u> – Locate static RAM datasheets and properly interpret some of the information contained in those documents including bus width, number of addresses, total memory capacity, timing diagrams showing set-up and hold time minimums, etc.

<u>Assessment</u> – Locate dynamic RAM datasheets and properly interpret some of the information contained in those documents including bus width, number of addresses, total memory capacity, timing diagrams showing set-up and hold time minimums, etc.

# Chapter 2

# Case Tutorial

The idea behind a *Case Tutorial* is to explore new concepts by way of example. In this chapter you will read less presentation of theory compared to other Tutorial chapters, but by close observation and comparison of the given examples be able to discern patterns and principles much the same way as a scientific experimenter. Hopefully you will find these cases illuminating, and a good supplement to text-based tutorials.

These examples also serve well as challenges following your reading of the other Tutorial(s) in this module – can you explain why the circuits behave as they do?

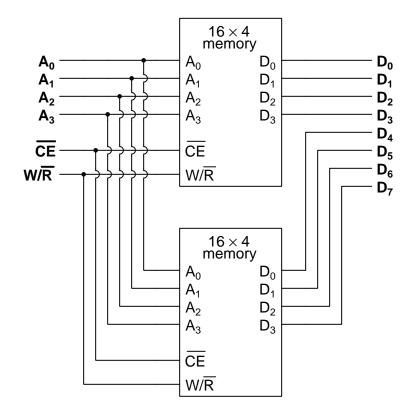

# 2.1 Example: 16x8 array from 16x4 memory ICs

- Each memory ICs contains sixteen addressable memory cells, each cell storing a four-bit word

- The entire array contains sixteen addressable memory cells, each cell storing an eight-bit word

- Both memory ICs access their respective memory cells simultaneously

- Both memory ICs enable and disable simultaneously by command of the  $\overline{CE}$  input signal

- Both memory ICs write or read simultaneously by command of the  $W\overline{R}$  input signal

# 2.2 Example: 16x16 array from 16x4 memory ICs

- Each memory ICs contains sixteen addressable memory cells, each cell storing a four-bit word

- The entire array contains sixteen addressable memory cells, each cell storing a sixteen-bit word

- Both memory ICs access their respective memory cells simultaneously

- ullet Both memory ICs enable and disable simultaneously by command of the  $\overline{CE}$  input signal

- Both memory ICs write or read simultaneously by command of the  $W\overline{R}$  input signal

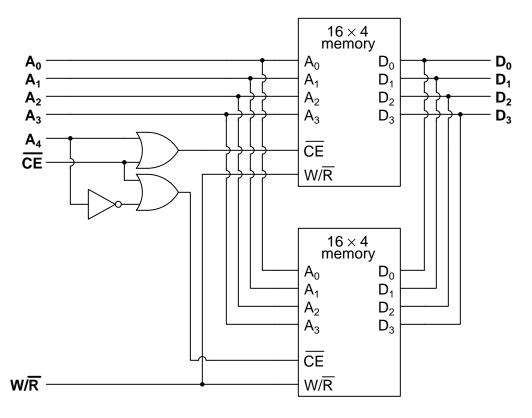

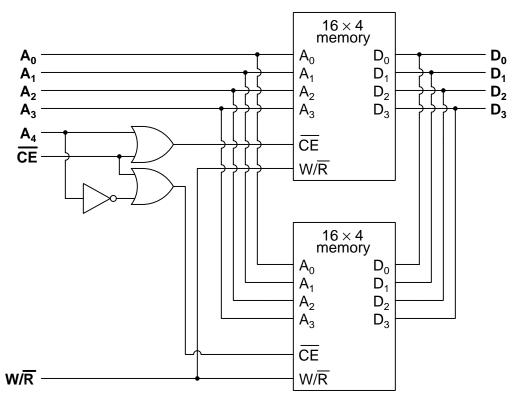

# 2.3 Example: 32x4 array from 16x4 memory ICs

- Each memory ICs contains sixteen addressable memory cells, each cell storing a four-bit word

- The entire array contains thirty-two addressable memory cells, each cell storing a four-bit word

- The upper IC accesses its memory cells for the first 16 addresses 0b00000 through 0b01111

- The lower IC accesses its memory cells for the second 16 addresses 0b10000 through 0b11111

- Both memory ICs enable and disable simultaneously by command of the  $\overline{CE}$  input signal

- Both memory ICs write or read simultaneously by command of the  $W/\overline{R}$  input signal

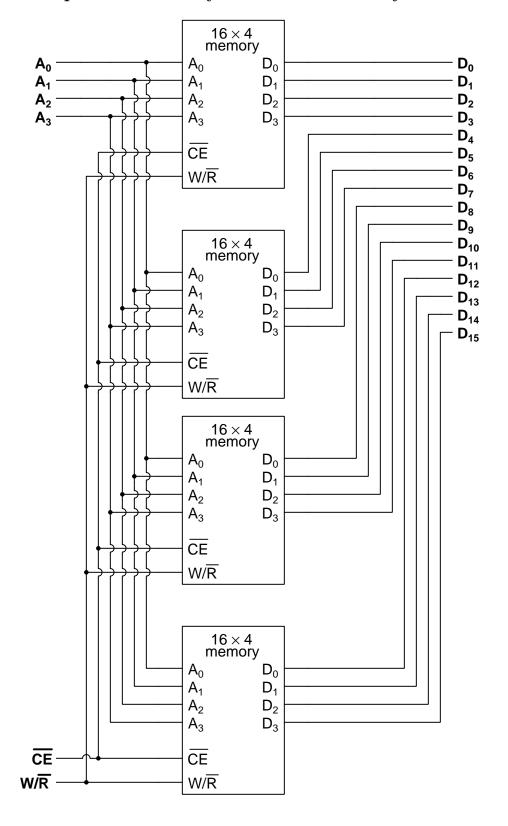

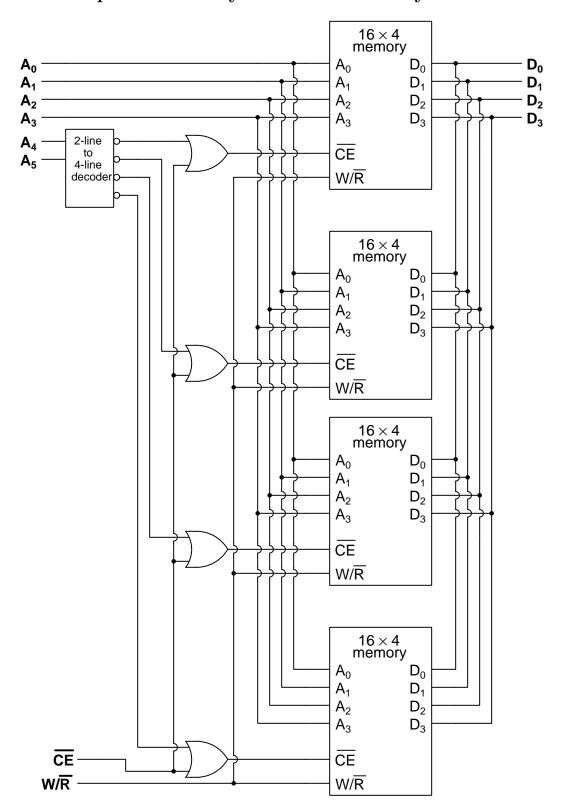

# 2.4 Example: 64x4 array from 16x4 memory ICs

- Each memory ICs contains sixteen addressable memory cells, each cell storing a four-bit word

- The entire array contains sixty-four addressable memory cells, each cell storing a four-bit word

- Each IC accesses its memory cells for one-quarter of the address space, i.e.:

One IC for the first 16 addresses 0b000000 through 0b001111 Another for the next 16 addresses 0b010000 through 0b011111 Another for the next 16 addresses 0b100000 through 0b101111 The last for last 16 addresses 0b110000 through 0b111111

- Both memory ICs enable and disable simultaneously by command of the  $\overline{CE}$  input signal

- Both memory ICs write or read simultaneously by command of the  $W/\overline{R}$  input signal

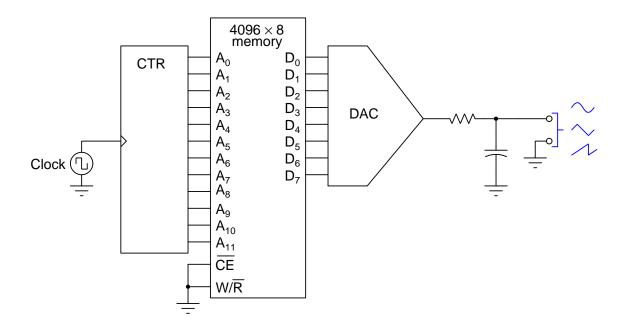

### 2.5 Example: AWG circuit using nonvolatile memory IC

A very useful piece of test equipment for electronics work is an  $arbitrary\ waveform\ generator$ , or AWG, designed to produce an AC or pulsing DC voltage signal with adjustable frequency. A parallel memory IC may be used as the basis for such a circuit, by programming the memory with numerical values corresponding to different levels of voltage in the desired waveform over time, and then using a clock-driven counter circuit to address the memory IC. The memory IC's output data then drives a digital-to-analog converter:

In the example shown here where we use a 12-bit counter to drive a  $4096 \times 8$  memory IC, the arbitrary waveform is stored as a series of 4096 ( $2^{12}$ ) numerical values in the memory IC which means the output waveform will have a frequency that is  $\frac{1}{4096}$  that of the clock signal. The clock may be as simple as a 555 timer circuit, and should be adjustable-frequency. With 8 bits of data driving the DAC, the waveform's amplitude may be divided up into 256 ( $2^8$ ) increments which establishes its voltage resolution. The result is a waveform that actually has a stair-step profile, but may be easily "smoothed" with some low-pass filtering.

If we do not require a very "smooth" wave-shape, we may use fewer address lines and therefore fewer addresses within the memory (this makes fewer horizontal steps in the stair-step output waveform, and also makes the output waveform's frequency greater for the same clock pulse frequency) and/or use fewer data lines (this makes fewer vertical steps in the stair-step output waveform).

Configuring the wave-shape for this AWG is simply a matter of programming different numerical values into the memory IC. A *sawtooth* waveform, for example, consists simply of steadily-incrementing data values written to consecutive addresses, so the 8-bit output begins at 0x00 and

proceeds linearly to 0xFF over as many time-steps as there are addresses. Such a sawtooth wave example would be a great application for truncating the memory space to the same number of bits as the data, so that each consecutive address will contain the identical value as data (e.g. address 0x00 is data 0x00, address 0x01 is data 0x02, etc. A *sine* wave would require the data values to be scaled linearly from the minimum and maximum values of a sine wave (e.g. the data values span 0 through 255 for an 8-bit DAC, corresponding to a sine wave oscillating between -1 and +1).

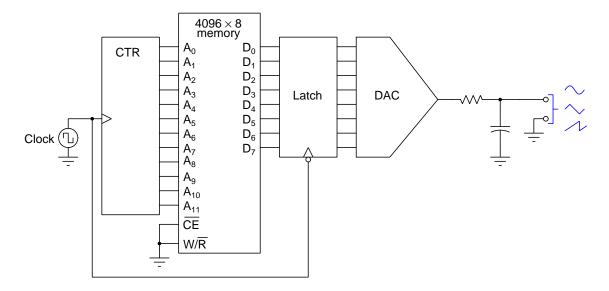

High-frequency AWG applications may require the addition of a data latch between the memory IC and the DAC, to avoid spurious results if the memory IC's data lines do not all settle at their next values simultaneously:

The latch's function is to "hold" the data value constant to the input of the DAC while the memory IC's data lines are transitioning states, and "pass" that new data to the DAC during a period when the counter's output is not changing and therefore not driving any new address values to the memory.

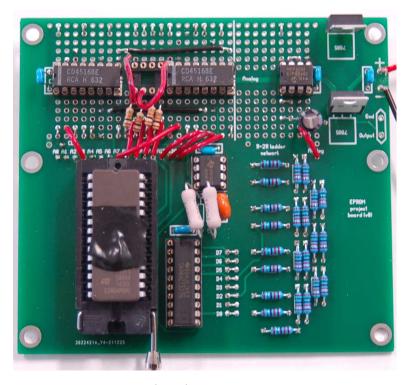

A photograph of a complete AWG built using a 27C256 UVEPROM appears below:

This particular printed circuit board (PCB) has etched traces for all the EPROM terminals, 555 timer circuit, 74HCT377 data latch, and R/2R "ladder" network as the digital-to-analog converter, but a generic "prototyping" area where a student could design and build their own digital counter and analog amplifier circuits.

# Chapter 3

# **Tutorial**

The most elementary form of signal is called discrete: a signal with only two possible states: true and false, or 1 and 0, respectively. Such signals may be expressed as electrical voltage levels, optical light intensities, magnetic polarities, physical component positions, subatomic particle "spin" states, and/or any other medium capable of two definite states. Alone, a discrete signal cannot represent anything but a single bit of information, but when grouped together a collection of bits may represent many things, for example  $binary\ numbers$  or  $alphanumeric\ characters$ . This is what we mean by the word digital: information represented by means of discrete bit states in any medium<sup>1</sup>.

Furthermore, any medium capable of retaining a discrete status over some length of time may be employed as a means for the storage of digital information. So long as those discrete states are not easily disturbed, the medium will be able to "remember" the digital data even in the face of corrupting influences such as external noise.

Digital data storage is incredibly useful, and has revolutionized our modern world. We have the ability today to archive and retrieve information in digital form that were unthinkable just a few decades ago, with the most evident form of progress being the ever-shrinking physical volume occupied by this storage.

A general term we use to describe any circuit, mechanism, or other device designed to "remember" information in digital form is *memory*. Many different types of memory technologies exist, and the purpose of this Simplified Tutorial is to introduce you to common principles as some of the more popular forms. We will begin with a form of memory that is considered obsolete but is very easy to understand: *punched paper tape*.

<sup>&</sup>lt;sup>1</sup>In fact, DNA with its chemical bonds formed between adenine and thymine molecules, and also between guanine and cytosine molecules, is itself a form of digital information storage. These four types of molecules comprise four possible states for each "bit" of a DNA data "word", making DNA coding *quaternary* rather than *binary*.

### 3.1 Punched paper tape

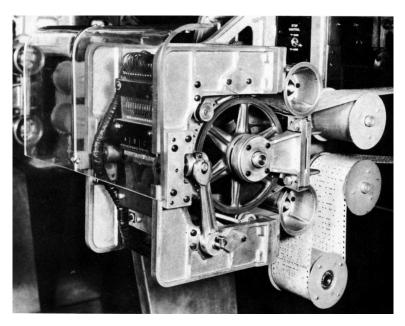

The earliest digital electrical computers stored data both electrically and mechanically, electrical memory consisting of relay-based latching circuits and mechanical memory consisting of paper tape with small holes punched through. A hole (versus an un-punched area of tape) constituted the discrete states of each section of tape. A photograph of a mechanism designed to translate these holes and non-holes into discrete electrical states appears in the following photograph taken of the *Automatic Sequence Controlled Calculator* built by IBM in the 1940's. The tape with its patterns of punched holes is clearly visible, threaded through the mechanism:

As this tape passed through the mechanism, metal contacts placed on either side of the paper tape would make contact through a hole in the tape and be insulated from each other in the absence of a hole, thus translating the paper's discrete states (hole versus non-hole) into discrete electrical states (continuity versus non-continuity).

A mechanism such as the one pictured is said to *read* the tape: translating the paper holes/non-holes into electrical bits, akin to a human being translating ink markings on paper into word-based thoughts when reading a text. The complement to reading is *writing*, which took the form of a special hole-punching machine in the case of paper tape.

*Reading* and *writing* are fundamental concepts applicable to any form of memory or data storage system, and are easy to understand in the context of paper tape.

Another general concept associated with digital memory is *access*: the ability to locate data on the medium. In the case of tape, the access is *sequential* in nature because the tape can only move longitudinally. If the computer needed to read (or write) data at some location on the tape far from its present location, its only recourse was to fast-forward or rewind the tape until that location reached the mechanism, meanwhile passing over all the other locations on the tape in sequence.

Some digital memory technologies, by contrast, offer *random access* which means the ability to "jump" to any arbitrary data location on demand without having to pass through all the other data locations in sequential fashion.

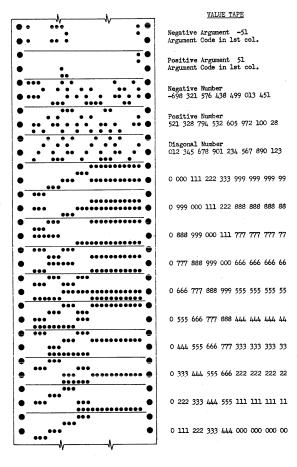

An illustration of a punched tape section for the Automatic Sequence Controlled Calculator shows a set of "drive holes" at either edge designed to engage with sprocket pegs within the mechanisms. The smaller holes in the middle section of the tape encode the digital data. Text written beside the tape illustration comment on the meaning of the hole patterns. Thin horizontal lines drawn on the tape serve only as marks to help human readers separate sets of holes from each other, dividing the tape's data into distinct sections<sup>2</sup>, each representing a single numerical quantity:

Figure 13

<sup>&</sup>lt;sup>2</sup>The computer itself had no need for these lines, and in fact was blind to all but the holes. A careful examination of this illustration reveals a consistent placement of the drive holes with each section of tape, so that the computer needed only to align the drive sprocket to these intervals in order to properly orient the rows of holes for reading.

### 3.2 Digital memory principles

Punched paper tape, of course, is an obsolete technology. However, it serves as a simple example of concepts common to most memory technologies, as we saw with *reading* versus *writing* and *sequential*- versus *random-access*.

Another important concept of digital memory evident in punched paper tape is the distinction between address and data<sup>3</sup>. "Data" is the information encoded at any particular location in the memory, in the case of this paper tape from the 1940's data being the numerical value represented by any four-row pattern of punched holes. "Address" is the particular location of data along the length of the tape. We could imagine the first set of four data rows at one end of a tape being address number zero, with each successive data group having sequentially-numbered addresses.

Every digital memory is limited by addresses and also by the amount of data resident at each address. In the case of the paper tape example previously shown, the number of addresses is limited only by the length of the tape, while the amount of data per address is fixed at 96 bits<sup>4</sup>, equivalent to (a maximum of) 24 decimal digits by the encoding scheme used within the Automatic Sequence Controlled Calculator. A magnetic hard disk (another form of digital memory) is limited in addresses by the maximum number of areas on the disk surface which may be magnetized to represent binary 1 and 0 states.

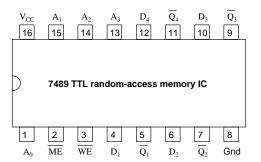

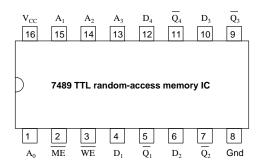

When we examine semiconductor memory ICs we generally find some pins<sup>5</sup> dedicated as address lines and other pins dedicated as data lines. The legacy model 7489 memory IC pin assignments are as follows, with four address lines labeled  $A_0$  through  $A_3$  and four data lines labeled  $D_1$  through  $D_4$ :

The model 7489 memory IC thus had a total capacity of 64 bits, organized as  $16 \times 4$  bits – sixteen addresses containing four bits of data each. To select the address of interest we set the logic states of the address lines to the binary number desired (e.g. address number five would be selected by making  $A_3 = 0$  and  $A_2 = 1$  and  $A_1 = 0$  and  $A_0 = 1$ ) while the four-bit data word could either be applied to the data pins (with pin 3 set low to enable the IC's write mode) or measured on those same pins (with pin 3 set high to disable write mode and enter read mode, making the data pins outputs rather than inputs).

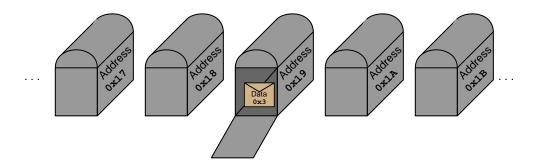

<sup>&</sup>lt;sup>3</sup>Non-computer analogies exist to help understand these two terms. In a postal service, the *address* for any particular mailbox is usually a combination of numbers and words (e.g. 1234 Main Street) while the *data* is the information contained within each mailbox in the forms of letters, photographs, and other items residing inside.

<sup>&</sup>lt;sup>4</sup>A close examination of the tape reveals that each row contains 24 places for holes, and there are four of these rows per section.  $24 \times 4 = 96$ .

<sup>&</sup>lt;sup>5</sup>This is true of so-called *parallel-addressed* memory ICs.

A helpful analogy for digital memory addresses versus data is to consider the function of a postal service mailbox, where the box bears a label called the address and is ready to contain letters inside of it (data). Here we see a row of mailboxes with sequential address labels, one of those mailboxes opened up to reveal data inside of it:

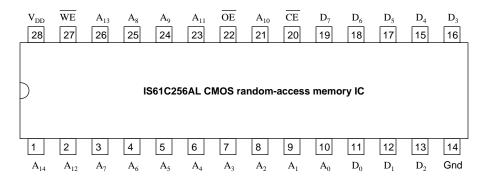

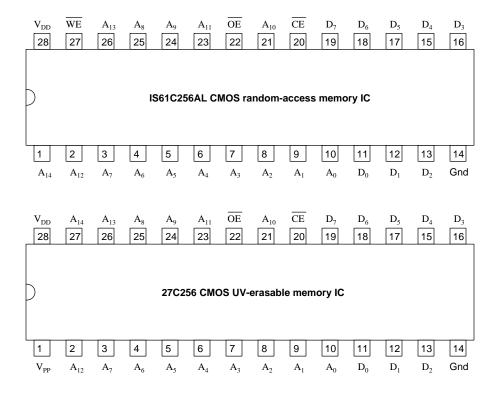

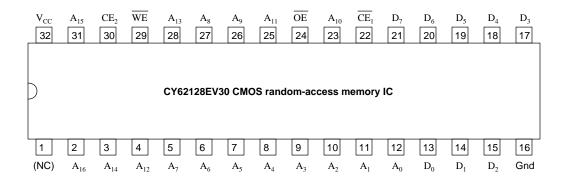

Modern digital memory devices have enormous capacity compared to the legacy 7489 IC. Consider the following IC with an organization of  $32k \times 8$ :

Despite its much larger capacity, this IC functions much the same as the legacy model 7489 with its lowly  $16 \times 4$  organization. We still select the intended address within the IC by asserting "high" and "low" logical states on the address pins  $(A_0$  through  $A_{14})$  while either reading data from or writing data to the data pins  $(D_0$  through  $D_7)$ . Fifteen address lines represents  $2^{15} = 32768$  unique addresses, each of those addresses storing one byte of data accessible via the eight data lines.

The fact that any address within this IC may be accessed simply and immediately by applying the desired "high" and "low" logical states to its address pins makes this device an example of random-access memory, because different addresses may be accessed in any (random) order. Nearly all solid-state memory devices are random-access in nature.

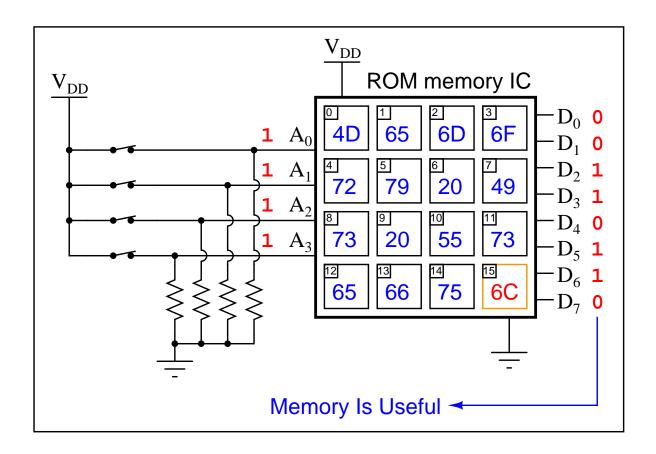

A common form of visual map for addresses and the data stored within a memory device is something called a *hex dump*. This is a listing of digital word values (in hexadecimal) printed left-to-right and top-to-bottom, with a listing of starting addresses on the left-hand side. For example, here is a hex dump shown on the software screen for a memory IC programming device, for a string of text written by the American author Jack London:

The proper function of man is to live, not to exist. I shall not waste my days in trying to prolong them. I shall use my time.

The column of numbers on the left-hand edge of the display labeled "OFFSET" (00000000 through 00000240) are the starting addresse values for each row. Each row contains sixteen bytes of data (each byte shown as a two-character hex value), which is why the starting addresses increment by "1" in the sixteen's place<sup>6</sup>. In this example, the data value 0x54 resides in memory address 0x00000000, the data value 0x68 in address 0x00000001, the data value 0x65 in address 0x00000003, the data value 0x74 in address 0x0000000F, etc. On the far-right side of this display we see the ASCII interpretation of these byte values, which for the digitization of the Jack London quote is perfectly appropriate. Often you will find hex dumps where the ASCII characters are gibberish because the data stored in the device's memory is intended for some purpose other than text.

<sup>&</sup>lt;sup>6</sup>Remember that the address labels themselves are in hexadecimal as well! Thus, 0x00000000 is zero, 0x00000010 is sixteen, 0x00000020 is thirty-two, etc.

Yet another general concept associated with memory is *volatility*: the degree to which the bits are able to retain their proper states in the absence of any supporting energy or manipulation. Punched paper tape is considered *nonvolatile* memory because it "remembers" its data indefinitely without any external assistance. By contrast, many of the electrical relays used within the IBM Automatic Sequence Controlled Calculator for temporarily storing data would "forget" that data if de-energized, and would therefore be categorized as *volatile* memory.

For example, the model IS61C256AL memory IC shown previously happens to be volatile. However, the model 27C256 memory IC has the same organization ( $32k \times 8$ ) and nearly the same pin assignments but is nonvolatile<sup>7</sup>:

Let us recap these general concepts before continuing:

- Reading versus Writing retrieving data from versus placing data to memory

- Random-access versus Sequential-access being able to arbitrarily jump to a location in memory versus being forced to pass through all locations in sequence

- Address versus Data the location at which information is stored versus the information being stored at a given location in memory

- Volatile versus Nonvolatile requiring power to retain data versus not

<sup>&</sup>lt;sup>7</sup>The 27C256 IC may be electrically written, but erased only by exposing the silicon die to ultraviolet light.

## 3.3 Electronic memory

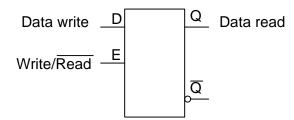

A primitive example of volatile electronic memory is the *D latch* logic circuit, capable of storing a single bit of information so long as DC power is maintained to the D-type latch:

A single bit may be written to the latch through the D input terminal, as a discrete ground-referenced voltage signal<sup>8</sup>. The stored data may be read at the Q terminal at all times. The "Enable" (E) terminal serves to control when external data is written to the latch or ignored: when high the latch is in write mode with any data presented to the latch at terminal D transparently passed on to terminal Q; when low the latch is in read mode and it ignores any data input to its D terminal, simply "holding" (i.e. remembering) the previously-written data at its Q output terminal.

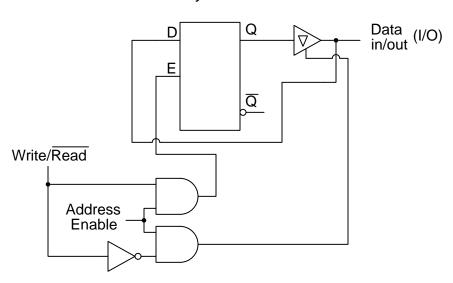

Most semiconductor-based memory circuits re-use the same terminals for alternately reading and writing data. In other words, a single-bit memory circuit will have a solitary "data in/out" terminal serving as an input during write mode and an output during read mode. This functionality is easy to add to our D-type latch using tri-state buffer and inverter gates:

# Memory cell circuit D Q Data in/out (I/O) Write/Read

This simple memory circuit has a storage capacity of one bit, and a single address for that bit.

$<sup>^8</sup>$ As usual, power supply terminals are omitted from this diagram for simplicity, but are absolutely essential to the proper operation of the circuit.

While this simple circuit works well as a one-bit "memory cell", we will need to find a way to link many of these "cells" together to form memory arrays if we are to ever have memory with significant data-storage capacity. In order to provide multiple addresses for single bits of data, we will need to have multiple memory cells and be able to selectively access one at a time. To do this, we must augment our memory cell design with a master enable/disable input useful for selecting which cell will be read from or written to. Since the purpose of this additional input is for addressing, we will call it the address enable line:

#### Memory cell circuit

When high, the address enable line allows data to be read from or written to the memory cell. When low, the address enable line forces the outputs of both AND gates to go low, placing the tri-state buffer into its high-impedance modes to effectively "disconnect" the Q terminal from the data I/O line, so that the D-type latch cannot assert a logical state onto the I/O line.

Not only does the tri-state buffer allow this memory cell to take data in through the I/O line from some other source when in the Read mode (also with the address enabled, of course) while not sensing its own last-stored state from the latch's Q output, but it also prevents multiple memory cells sharing a common I/O line from accidently asserting opposing logic states on that same line when only one of those memory cells is being addressed.

## 3.4 Signal timing

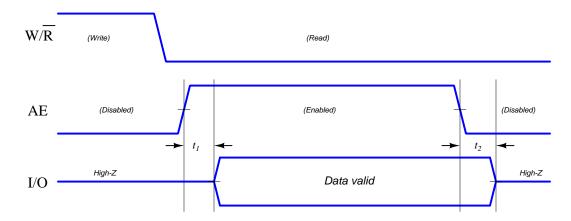

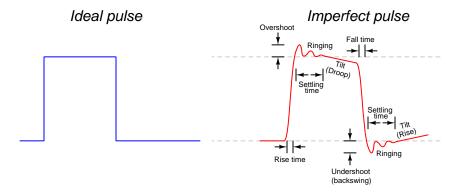

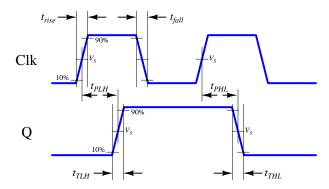

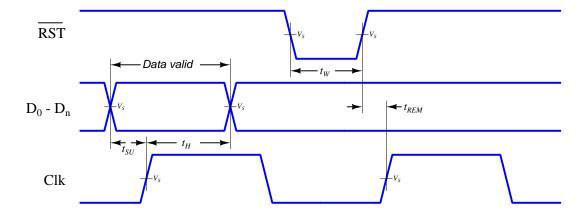

Timing diagrams help illustrate the proper use of memory circuits, showing all the set-up and hold times necessary for reliable operation. Below we see a timing diagram for a *read* cycle where we give the memory cell circuit the read command (by making the Write/Read input line *low*) and "address" the memory cell (by making the Address Enable input high):

So long as the Address Enable line is disabled (i.e. low) the memory cell's data I/O line will be in its high-impedance mode, as shown in the timing diagram by the line being in the middle rather than firmly high or low<sup>9</sup>. Once the memory cell is enabled by the high Address Enable signal and the buffer's propagation delay time elapses, the D latch's Q output state appears on the I/O line ready to be "read" by any other digital device. Propagation delays  $(t_1 \text{ and } t_2)$  associated with the AND gate and the tri-state buffers make the data's appearance "lag" the Address Enable signal.

The read data's appearance on this timing diagram may look very strange to anyone familiar with combinational logic circuits, as the "Data valid" time period appears to show this signal as being simultaneously high and low. This, of course, is an impossibility, and so the timing diagram must be communicating some other idea to us. Indeed it is, as this "high-and-low" notation simply means the memory cell will output whatever state is held in the D latch, be it high or low. Since this depends on data previously "written" to the D latch, and we have not been informed of this circuit's history prior to this read cycle, we have no way of knowing whether the I/O line will assume a high or a low state, and so we draw both states.

An important lesson we need to draw from this timing diagram about memory circuits in general is that certain input states are necessary to permit us to read their contents, and also that certain time delays must be anticipated between the assertion of those necessary states and the presentation of the stored data.

$<sup>^9</sup>$ This is not to imply that the actual voltage will be mid-way between the +V power supply rail and ground, but rather this is just a way to distinguish the high-impedance mode from a definite low or high state. In reality the data I/O signal's voltage level could be any value during that time. All we can say during the "disabled" time is that the memory cell circuit will not *assert* any logic state to its I/O line, either high or low.

3.4. SIGNAL TIMING 29

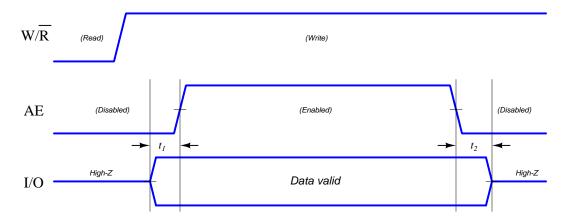

Likewise, when writing data to a memory cell circuit we must be sure to abide by the sequence and timing requirements of the circuit as shown by a timing diagram. Below we see such a diagram showing a *write* cycle where we give the memory cell circuit the write command (by making the Write/Read input line high) and "address" the memory cell (by making the Address Enable input high):

Since this is a write cycle and not a read cycle, data on the I/O line comes from some other digital device sending a signal to the memory cell. Note how this data must be stable ("valid") prior to the enabling of the circuit and remain stable after we disable the circuit for certain amounts of time  $(t_1 \text{ set-up time and } t_2 \text{ hold time, respectively})$ .

An important lesson we need to draw from this timing diagram about memory circuits in general is that data sent to a memory circuit must be stabilized at the I/O pin(s) both before and after the circuit is enabled for a write cycle. Failure to heed these set-up and hold times will result in unreliable operation.

These basic timing principles are true for multi-bit memory arrays as they are for single-bit memory cell circuits. Next, we will explore just how we may combine multiple memory cells together to form these larger arrays.

### 3.5 Combining memory elements

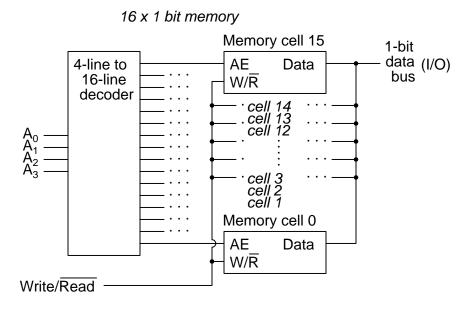

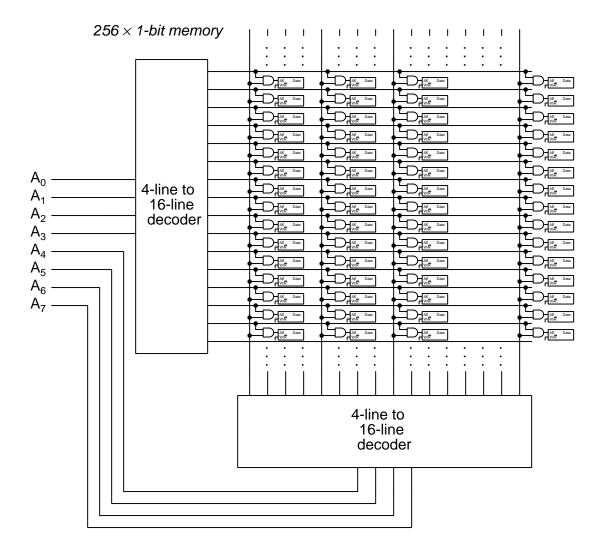

The following schematic diagram shows how sixteen such memory cells may be interconnected along with a 4-line to 16-line decoder to form a  $16 \times 1$  bit memory array (i.e. sixteen addresses, each one storing one bit of data):

Four address lines  $(A_0$  through  $A_3)$  accept a binary-numbered value into the decoder, which in turn selects (enables) which of the sixteen memory cells connects to the data bus for either reading or writing. Note how every one of the memory cells'  $W/\overline{R}$  lines connect in common to a single  $W/\overline{R}$  line for the  $16 \times 1$  memory array, but with the individually-activated Address Enable (AE) lines only one memory cell may input or output its data at any given moment.

Expanding this memory array to possess a greater number of addresses simply consists of adding address lines and using a larger decoder to select a larger number of memory cells. For example, five address lines would yield  $2^5$  (thirty-two) memory addresses; eight address lines would yield  $2^8$  (two hundred and fifty-six) memory addresses; sixteen address lines would give us  $2^{16}$  (65536) addresses.

In order to avoid the complexity of extremely large decoders (e.g. a 16-line to 65536-line decoder!) it is more practical to use pairs of smaller decoders to select memory cells arranged in a two-dimensional grid. For our hypothetical  $65536 \times 1$  memory array, imagine an 8-line to 256-line decoder connected to the first eight address lines ( $A_0$  through  $A_7$ ) selecting which row of memory cells, plus another 8-line to 256-line decoder connected to the last eight address lines ( $A_8$  through  $A_{15}$ ) selecting which column of memory cells to access. Thus, we would have a "grid" of memory cells with 256 rows and 256 columns and a total of 65535 memory cells, each memory cell located at an intersection of one row and one column line. The address enable (AE) input of each memory cell would connect to the output of an AND gate, the AND gate's inputs connecting to the respective row and column lines such that only the cell located at the active row line and the active column line would become connected to the data bus for reading or writing.

A simplified schematic diagram showing a  $16 \times 16$  "grid" addressing just 256 memory cells appears below<sup>10</sup>. Each memory cell has an AND gate driving its AE input, with the two inputs of each AND gate connected to a unique combination of row and column lines:

Thus, the "grid" circuit design allows relatively large memory arrays to be constructed using decoders of modest line count.

$<sup>^{10}</sup>$  Many wires and memory cells have been omitted from this diagram to avoid clutter, and unconnected wires crossing paths are simply overlaid on top of one another rather than shown with the semi-circular "jump" symbols as I typically use, simply because the schematic would become overwhelmingly complicated if shown in full detail. In fact, the number of memory cells shown here is only one-quarter of the 256 you would find in a real 16  $\times$  16 grid memory!

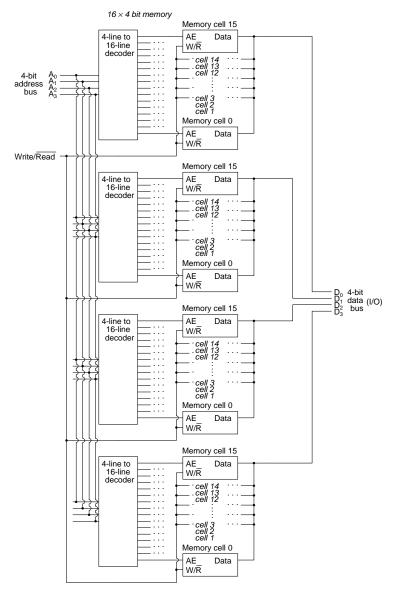

However, no amount of address expansion will make this array store more than one bit per address. In order to expand the number of data bits stored within each address of the array, we must combine the circuits in a different manner. Examine the following  $16 \times 4$  memory array, constructed from four  $16 \times 1$  arrays:

As you can see here, each of the  $16 \times 1$  arrays shares the same address and  $R/\overline{W}$  lines, but their respective data lines separately form a 4-bit data I/O bus. Thus, each array stores just one bit of the four-bit data word for the larger memory array.

The legacy model 7489 memory IC used a very similar form of  $16 \times 4$  organization scheme:

Notable differences between the 7489 and our 16  $\times$  4 memory circuit design include separate input and output data busses ( $D_0$  through  $D_4$  are inputs accepting data to be written, while  $\overline{Q_0}$  through  $\overline{Q_3}$  are outputs where data could be read from the memory) as well as a master memory enable ( $\overline{ME}$ , alternatively known as a chip enable, or  $\overline{CE}$ ) line designed to enable or disable the entire integrated circuit by placing the data pins in high-impedance (tri-state) mode.

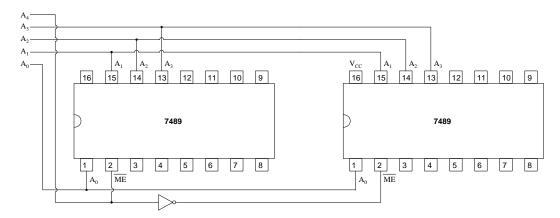

The "master enable" line is especially useful for combining multiple memory ICs to form even larger memory arrays. Consider the following example, where two 7489 ICs are combined to form a single  $32 \times 4$  memory (showing only the address line connections for simplicity – the other terminals are all respectively paralleled):

A fifth address bit  $(A_4)$  selects which of the two 7489 memory ICs to enable: when low, the left-hand 7489 enables for reading and writing; when high, the right-hand 7489 enables. Thus, one memory IC handles the first sixteen addresses (00000 through 01111) while the second IC handles the next sixteen addresses (10000 through 11111).

This same strategy could be expanded as far as one likes, combining memory arrays to form even larger arrays, with each new address line doubling the number of memory addresses. We may even incorporate decoder ICs to simplify this expansion: all additional address lines become inputs to the decoder, while the decoder's output lines selectively enable one memory IC at a time. A 3-line to 8-line decoder, for example, would permit us to combine eight memory ICs together for an eight-fold expansion of the address space.

Before proceeding further, let us review our list of general memory concepts and see how they apply to these latch-based forms of digital memory:

- Reading versus Writing controlled by the discrete state of a single  $R/\overline{W}$  input terminal, which in turn controls which of the internal tri-state buffers pass data and which are in high-impedance mode

- Address versus Data addressing is controlled by the digital states of a four-bit bus, while data is read and written by a separate four-bit bus

- Random-access versus Sequential-access since addressing is entirely controlled by the binary value represented by the four-bit address bus, it is possible to "jump" to any arbitrary address desired without having to pass sequentially through all the others lying in between

- Volatile versus Nonvolatile since latch circuits are based on interconnected semiconductor logic gates, and logic gates require the DC power to function, this memory is entirely volatile

### 3.6 Types of memory elements

Many digital applications require electronic forms of memory that are nonvolatile. An example of this is the *BIOS* of a personal computer, retaining important information the microprocessor needs to know immediately upon start-up in order to properly utilize the resources available to it (e.g. magnetic hard drives, communication ports, etc.). *Microcontrollers*, which are essentially single-chip computers, need some on-board nonvolatile memory in order to retain the programming which will instruct them what to do upon power-up as well.

If we were to replace the latch circuit at the heart of every memory cell of the previous examples with a hard-wired connection to  $+{\rm V}$  or to Ground (a logical 1 or 0, respectively), maintaining most of the other circuitry required for addressing and multiplexing those hard-written cells, we would have a read-only memory useful for the aforementioned purposes. If the memory IC is designed in such a way that it may only be written (programmed) at the place of manufacture, we simply refer to it as a ROM (Read-Only Memory). If it is manufactured as a "blank slate" ready to be indelibly programmed once by the end-user, it is known as a PROM (Programmable Read-Only Memory). Some PROMs may be bulk-erased, either by an electrical signal or by exposure to ultraviolet light, in which case they are called EEPROM (Electrically Erasable) or UVPROM (UltraViolet erasable) memories, respectively. Such EPROM (Erasable Programmable Read-Only) memories are the basis of digital system firmware, where instructions for some digital device may be deliberately altered by the user, but are otherwise only read by that device and not written to.

Unfortunately, read-write electronic memory systems such as those based on latch circuits are typically called RAM which of course stands for Random-Access Memory. While this type of memory is certainly random-access, so is every semiconductor-based read-only memory (ROM). So, the label of "RAM" in fact has more to do with the circuits being volatile than with being randomly-accessible.

Multiple technologies exist for RAM. Latch-based memory cells such as those we previously explored create what is known as *static RAM*. One disadvantage of static RAM is the number of transistors necessary to implement each cell. Since most practical RAM ICs contain *thousands* of these memory cells, even modest reductions in transistor count for each cell yield substantial savings in silicon overall. Fewer transistors per cell mean more cells that may be placed on the same area of silicon. Another disadvantage of static RAM, especially when based on TTL logic circuitry, is high power dissipation: thousands of latch circuits drawing current from the power source will dissipate significant quantities of heat and pose an operating limit on battery-powered digital circuits.

An alternative to a transistor-based latch-type memory cells is RAM memory using capacitively-triggered transistors, the logical memory state maintained as an electric charge (or lack of charge) on each capacitor. With a microscopic capacitance serving as the memory element instead of a latch circuit, the number of transistors per cell may be dramatically reduced, and the amount of memory available on a given chip dramatically increased. Also, power dissipation is less than a static RAM memory cell. However, a disadvantage of this form of memory is that the microscopic capacitors dissipate their stored energy rather rapidly due to parasitic loading, and must be periodically "refreshed" to retain their data. It is this transitory nature which earns them the label of dynamic

<sup>&</sup>lt;sup>11</sup>Some PROMs use fusible links in the integrated circuit which may be intentionally "blown" by careful connections to an external power source. When one of these microscopic fuses blows, the memory cell assumes the complement of its factory-default state. Of course, this procedure is non-reversible: once blown, a fuse cannot be "healed" to restore the original logic state.

*RAM.* Modern dynamic RAM chips have on-board refresh circuitry to handle this for the user, while older dynamic RAMs required the user's application to periodically address certain regions of memory space in order to keep those cells' states refreshed<sup>12</sup>.

A more modern semiconductor memory technology blurring the distinction between RAM and ROM is flash memory. It is similar in principle to dynamic RAM – storing single bit-states as electrostatic charges – but the physical construction and operating behavior is different. Flash memory cells utilize a special type of MOSFET transistor with a metal "floating gate" electrode suspended within layers of electrically-insulating material adjacent to the channel of the transistor. This floating electrode becomes electrostatically charged or discharged by means of quantum tunneling, a process whereby electrons "leap" from one nearby conductive surface to another without ever passing through the insulating material separating those conductive surfaces. This tunneling behavior is possible only under certain energy-level conditions, and if those conditions are not met the electrical charges remain isolated on either side of the insulating barrier as one would expect in "classical" physics. Thus, quantum tunneling becomes the sole method of writing data to a cell, which means the stored data is nonvolatile. Reading the stored charge (or lack of charge) on the floating gate is as simple as testing the conductivity of the MOSFET's channel, that channel acting as an electroscope (i.e. electric-charge detector) for the floating gate.

Flash memory cells basically consist of single MOSFETs which makes them extremely compact, and due to the strict conditions necessary for quantum tunneling the stored electrostatic charges do not bleed off in the same manner as conventional dynamic RAM. This gives flash memory reliable retention times in the span of *decades* as opposed to *milliseconds* for dynamic RAM cells.

The speed at which flash memory cells may be written and read exceeds current state-of-the-art mechanical memory technologies (e.g. magnetic disks) which is why this technology finds use in *solid-state hard drives* for computers. It is still not as fast as either dynamic or static RAM, though, which is why these latter technologies are still popular.

Another modern nonvolatile memory technology is  $ferroelectric^{13}$ , based on substances exhibiting a natural electric polarization (i.e. a permanent electric field), the polarity of that field being reversible by the application of sufficient external voltage. Like flash memory, ferroelectric memory elements are based on MOSFETs activated by this stored electric field. However, ferroelectric memory offers faster data access times and greater durability (more read/write cycles before failure) at the expense of lower physical density (fewer bits stored in a given volume).

$<sup>^{12}</sup>$ A datasheet for the Texas Instruments model TMS 4062 JL/NL 1024  $\times$  1 dynamic RAM says the following about refreshing the cells: "Each cell must be refreshed at least once in every 2-millisecond period by cycling through the lower order row addresses (A0-A4) or by addressing each row at least once in that period. Addressing any row refreshes all 32 cells in that row. The chip-select clock need not be activated during refresh; however, the clock input must be cycled from high to low to high."

<sup>&</sup>lt;sup>13</sup>Interestingly, the "ferro" root refers to the hysteretic behavior of these substances (i.e. they may be electrically polarized in a manner similar to how ferromagnetic substances may be magnetically polarized), not their chemical composition. That is to say, a "ferroelectric" need not contain any iron.

Reviewing the many (and confusing) labels used to describe semiconductor memory, all of which happen to be randomly-accessible:

- RAM Random-Access Memory, technically a misnomer because all semiconductor memory is random-access. What this acronym really distinguishes is the memory's volatility, as data is lost or corrupted when de-energized. Typically very fast read/write times.

- ROM Read-Only Memory. In its purest form, this is a mask ROM (MROM) where the data must be programmed into the IC at the time of manufacture, that data completely unalterable by the user.

- **PROM** *Programmable Read-Only Memory*. Literally interpreted, this is an oxymoron (a contradiction in terms). It refers to a memory IC that may be programmed by the user, but afterwards either cannot be altered or requires substantial effort to alter. One-Time-Programmable (OTP) PROM ICs often use "fuse" or "anti-fuse" <sup>14</sup> elements to store the data, where blowing the fuse (or alternatively, shorting the anti-fuse) constitutes writing one of the two states. Such writing cannot be un-done, hence the term "one-time programmable".

- **EPROM** *Erasable Programmable Read-Only Memory*. Literally interpreted, this is another oxymoron, referring to a PROM that may be erased by the user. EPROM re-writing times are much longer than RAM writing times, which is the major distinguishing feature.

- UVEPROM Electrically Erasable Programmable Read-Only Memory. An EPROM that may be programmed multiple times via electrical signals.

- **EEPROM** *Electrically Erasable Programmable Read-Only Memory*. An EPROM that may be erased by exposure to ultraviolet light.

- NVRAM Non-Volatile RAM. A RAM IC with a built-in means to retain information when powered down. Some NVRAMs use an internal long-life battery to maintain energization when external power is lost. Others use a slower EPROM technology to copy the RAM's contents at power-down<sup>15</sup>, and restore the RAM's contents at power-up. NVRAm provides all the benefits of non-volatility while enjoying the fast access times of standard RAM.

<sup>&</sup>lt;sup>14</sup>Zener diodes may function as anti-fuses, because overpowering a Zener diode's PN junction will cause it to fail in a shorted state.

<sup>&</sup>lt;sup>15</sup>An external capacitor is often required for this type of NVRAM, providing just enough energy for the internal data-archiving action in the absence of regular external power.

### Chapter 4

### Historical References

This chapter is where you will find references to historical texts and technologies related to the module's topic.

Readers may wonder why historical references might be included in any modern lesson on a subject. Why dwell on old ideas and obsolete technologies? One answer to this question is that the initial discoveries and early applications of scientific principles typically present those principles in forms that are unusually easy to grasp. Anyone who first discovers a new principle must necessarily do so from a perspective of ignorance (i.e. if you truly discover something yourself, it means you must have come to that discovery with no prior knowledge of it and no hints from others knowledgeable in it), and in so doing the discoverer lacks any hindsight or advantage that might have otherwise come from a more advanced perspective. Thus, discoverers are forced to think and express themselves in less-advanced terms, and this often makes their explanations more readily accessible to others who, like the discoverer, comes to this idea with no prior knowledge. Furthermore, early discoverers often faced the daunting challenge of explaining their new and complex ideas to a naturally skeptical scientific community, and this pressure incentivized clear and compelling communication. As James Clerk Maxwell eloquently stated in the Preface to his book A Treatise on Electricity and Magnetism written in 1873,

It is of great advantage to the student of any subject to read the original memoirs on that subject, for science is always most completely assimilated when it is in its nascent state . . . [page xi]

Furthermore, grasping the historical context of technological discoveries is important for understanding how science intersects with culture and civilization, which is ever important because new discoveries and new applications of existing discoveries will always continue to impact our lives. One will often find themselves impressed by the ingenuity of previous generations, and by the high degree of refinement to which now-obsolete technologies were once raised. There is much to learn and much inspiration to be drawn from the technological past, and to the inquisitive mind these historical references are treasures waiting to be (re)-discovered.

### 4.1 Magnetic core memory

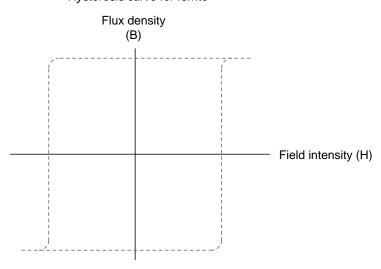

One of the earliest forms of solid-state memory for digital computers was magnetic core memory, often referred to simply as core. The fundamental principle of operation is the hysteresis curve for ferrite, a compound of iron and oxygen. Unlike most ferromagnetic materials, ferrite exhibits an extremely pronounced hysteresis curve which means once magnetized in a particular direction it tends very strongly to retain that magnetic flux. This property of ferrite makes it well-suited for all kinds of magnetic-based digital storage technologies including magnetic disks, magnetic tape, etc.

#### Hysteresis curve for ferrite

The field intensity (H) is the "magneto-motive force" (MMF) applied to the ferrite by an external magnetic source such as a current-carrying wire. Flux density (B) represents the number of magnetic domains within the ferrite that have aligned themselves in a common direction with the externally-applied field (H).

When ferrite magnetizes, it tends to do so until saturation which makes it ideal for storing discrete (1 versus 0) states – magnetization in one polarity represents a 1 state, and in the other polarity a 0 state. This single datum bit may be written to the ferrite specimen by a suitably strong H from a nearby current-carrying wire, with the direction of current determining the magnetic polarity and therefore the logical state written to the ferrite.

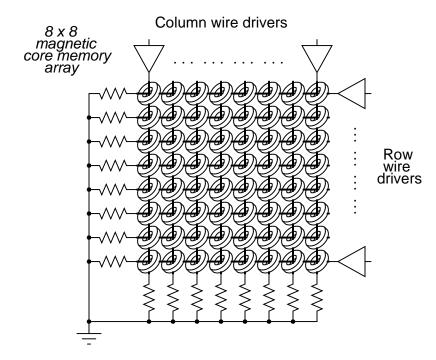

Core memory differs from disks and tape principally in the fact that the magnetic material does not need to physically move. Instead, tiny rings ("cores") of ferrite are arranged in grids with wires threaded through their centers as shown in the following illustration:

Each core has a "row" wire passing through its center, and also a "column" wire doing the same. Each wire's energized-state current is less than what would be required to saturate the ferrite, and so any ferrite current experiencing the magnetic field intensity (H) from just one wire's current will remain in its present magnetic flux condition (B). However, each wire's current is also regulated to be greater than one-half of the saturation threshold for ferrite, which means if one column wire and one row wire are simultaneously energized with current, the ferrite ring at the intersection of those two wires will experience saturation. Thus, we are able to address individual ferrite cores by column and row coordinates, just like individual RAM or ROM memory cells within large memory arrays are selectively enabled by row/column intersections.

Writing to individual cores is simple, but reading from them is not. The solution developed for reading core states consisted of a single "read" wire threaded through *every* core in the grid. Unlike the row and column wires, the read wire was not energized by any source, but instead connected to the input of an amplifier built to sense a voltage pulse resulting from the sudden change<sup>1</sup> in magnetic flux at a core. So, to read a core, what we do is try *writing* to it and monitor the sense wire to see if anything changed. If we try to write a 1 state and nothing changed, then that bit must have already been a 1; if we try to write a 1 state and sense a change-of-state by means of a voltage pulse across the length of the read wire, then that bit must have been a 0. The memory array's peripheral

This is an application of Faraday's Law of Electromagnetic Induction,  $V = N \frac{d\Phi}{dt}$ , where  $\phi$  is magnetic flux, related to flux density (B) by cross-sectional area.

circuitry would then have to go back and re-write the original state following a change-of-state, lest the data become corrupted. This process is known as a *destructive read*, and it was an interesting idiosyncrasy of magnetic core memory.

Despite this unique behavior, core memory was once extremely popular for computers. It had no moving parts, it was much faster than any tape or disk-based memory, and most favorably was non-volatile<sup>2</sup>.

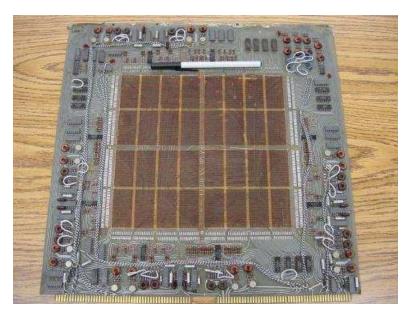

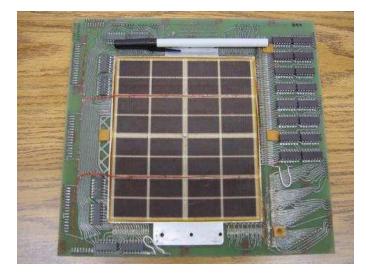

The following photograph shows a core memory board taken from a 1970's era Data General "Nova" minicomputer. A white ball-point pen with a black cap is placed near the top of the board for size reference. The magnetic cores themselves comprise the rust-colored rectangular areas on the board, with column and row drive circuitry as well as sense circuitry occupying the periphery of the board:

This large printed circuit board represented only 4 kilobytes of memory, a paltry amount of digital storage by modern standards.

$<sup>^{2}</sup>$ This meant that any computer using core memory in lieu of static or dynamic RAM would enjoy the power of resuming exactly where it left off following a momentary interruption in power!

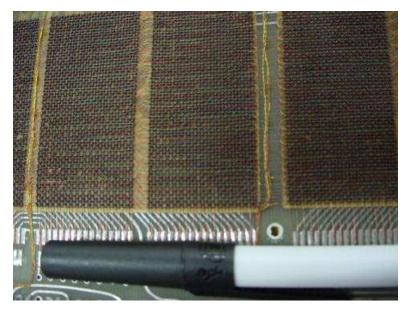

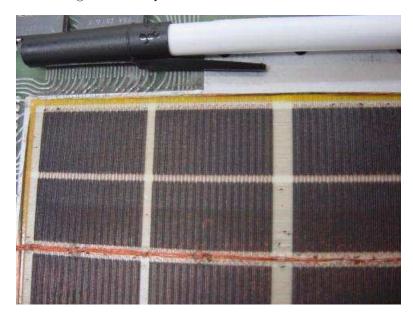

In this next photograph we see a close-up photograph of the same core memory board. The same ball-point pen remains in the photograph as a size reference. If you look closely, you can see the individual magnetic cores with fine-gauge wires threaded through their centers, the cores themselves tilted diagonally to the vertical column wires and horizontal row wires:

A more "modern" version of core memory appears in this next photograph, using much smaller ferrite rings to achieve greater packaging density and therefore greater memory capacity per unit board area:

This board sports double the memory of the previous core memory board: 8 kilobytes instead of 4 kbytes, and it does so using a smaller board size as evidenced by the same ball-point pen.

Next we have a close-up photograph of this denser core memory array. My camera's resolution is insufficient to show a single core's shape or orientation as a result of their much smaller size:

### 4.2 Early magnetic hard disk drives

Any flat surface consisting of ferrite pieces has the ability to be selectively magnetized (i.e. some areas magnetized in one polarity and other areas in the opposite polarity), and such a magnetized surface when passed by a wire coil will induce voltage pulses in that coil with the passing of alternately-polarized areas. This is the basis of both magnetic tape and magnetic disk storage.

Modern magnetic disks use such fine-grained ferrite on their surface, that the wire coils reading and writing data must hover extremely close to the spinning disk's surface, usually closer than the diameter of a grain of dust! For this reason, modern magnetic disk drives are completely sealed units assembled in clean-room manufacturing facilities to prevent the inclusion of dust within the housing containing these moving parts. However, legacy hard disk drives were crude by comparison, and their disks could be removed for service or even archival in any reasonably clean room.

The following photograph shows such a magnetic disk removed from its drive mechanism, a ball-point pen situated at one edge for size reference. The rust-colored disk is the magnetic surface, while the blue plastic around the periphery is the rim of the protective cover permitting the disk to be taken out of the mechanical drive unit and held in safe keeping:

A complementary blue plastic cover (not shown) fit over the disk, enclosing the entire assembly. This allowed the disk to be safely placed on a shelf, as one might shelve a book, for later re-use.

A common storage capacity for a hard disk of this size was 30 megabytes per side, since the disk had two sides which could be used as media. Some referred to these disks as *Winchester* hard disks, since their 30/30 capacity ratings (30 Mbytes on one side and 30 Mbytes on the other) was reminiscent of the legendary 30/30 Winchester-brand rifle cartridge.

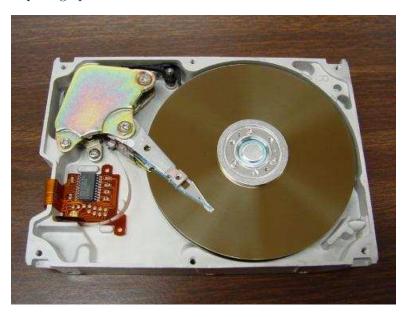

By contrast, a more modern hard disk drive (340 megabytes, still small by modern standards) is shown in this next photograph:

The read/write coil is located at the tip of the lever projecting out over the disk's surface, and is moved in an arc across that spinning surface by means of a small servo motor. In the legacy "Winchester" disk shown previously, the read/write coil and servomechanism was part of a separate unit from the movable disk. Here, the disk is not removable, and all appear as part of a single unit.

Incidentally, the removal of the cover from this hard disk unit necessary for photographing the disk *ruined* it. Unlike the "Winchester" disk shown earlier, modern hard drives must remain sealed throughout their operating lives due to the necessity of a dust-free environment.

#### 4.3 Floating-gate FET transistor patent

A Korean-born researcher working for Bell Laboratories named Dawon Kahng applied for a patent in June of 1967 entitled "Field Effect Semiconductor Apparatus With Memory Involving Entrapment Of Charge Carriers", the patent (number 3,500,142) being granted in March three years later. In Kahng's patent we find a clear description of a special type of MOSFET intended as a digital memory cell. This special MOSFET revolutionized digital memory storage technology, paving the way for "flash" memory, microcontrollers with extensive nonvolatile memory banks, FPGAs, and other modern digital devices.

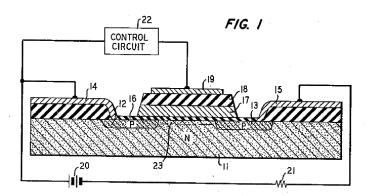

Figure 1A in Kahng's patent shows a cross-section of the FET:

What makes this MOSFET unique is a "floating" gate consisting of an electrically isolated metal layer (17) sandwiched in between two layers of insulating oxide (16 and 18). Kahng's invention became the foundation of EPROM memory technology, including later "flash" memory technologies. The first paragraph of Kahng's patent tersely describes his invention:

ABSTRACT OF THE DISCLOSURE – A field effect transistor is provided with a gate electrode assembly comprising a sandwich of a metallic layer between two insulating films of appropriate characteristics for the entrapment of charge carriers in the metallic layer. Such entrapment provides memory whereby an induced electric field can be maintained in the semiconductive element even after the field inducing force is removed. [page 3]

Kahng begins with a brief explanation of digital memory technology including a review of a magnetic-based memory element which his invention supersedes:

This invention relates to semiconductive apparatus which is characterized by relatively long memory, i.e., apparatus which will persist in a certain induced state for a useful period of time even after the inducing force is removed whereby there is provided for such period a record of the characteristics of the inducing force.

In computers and related apparatus there exists a need for memory elements in which information can be stored temporarily, while remaining accessible for reading, and then readily erased or modified.

Hitherto there have been suggested semiconductive devices having memory in which the memory was achieved by the provision of a ferroelectric element in contact with the semiconductive wafer such that the direction of the remanent polarization of the ferroelectric element controlled the state of the device. Typical of such devices are those described in U.S. Patent 2,791,760. An advantage of these devices is that the memory is independent of any sustaining currents so that even if there is a temporary loss of power the stored information is not lost. A serious difficulty that has hampered the exploitation of devices of this kind is that presently available ferroelectrics tend to suffer mechanical damage with use and after suffering such damage are of limited reliability. Also, the inherent speed capability is limited by the domain motion which is relatively slow, and so it is difficult to realize very fast switching.

To this end, the invention provides a semiconductive device with memory, in which the need for a ferroelectric element is obviated by a novel gate assembly which makes use of trapped charge carriers. In particular, viewed from one aspect, the gate assembly typically will comprise a pair of insulating layers sandwiching a metallic layer in which the charges are trapped. Viewed from another aspect, the gate assembly will include a tunnel sandwich diode formed by two conductive element sandwiching an insulating layer sufficiently thin that electron transport or tunneling therethrough is realized under control of applied signal information. [page 3]

Here Kahng first mentions the principle by which his memory cell functions: tunneling of electric charge carriers through a thin region of insulating material. This is a quantum effect, inexplicable from the perspective of classical physics.

Next, Kahng describes the construction of this special transistor:

In a typical insulated gate field effect transistor embodiment of the invention, the semiconductive element is a silicon wafer the bulk of which is weakly n-type and which includes a pair of spaced p-type surface zones to which are connected the source and drain electrodes, respectively. The surface portion of the element intermediate such p-type zones is covered with a relatively thin layer of silicon oxide which together with a relatively thick outer layer of zirconium oxide sandwiches a layer of zirconium there between which serves as a floating gate.

A metallic layer covers the zirconium oxide to serve as the outer gate electrode. In operation, a positive voltage pulse applied to the outer gate electrode causes the entrapment of electrons in the zirconium layer for a relatively long time, which results in a p-type skin persisting underneath the silicon oxide and a low resistance path between the source and drain electrodes. The application of a negative pulse instead results in leaving the portion of the element underlying the silicon oxide n-type whereby the resistance between the source and drain electrodes is high.

A variety of embodiments will be described hereinafter including ones in which light may be employed for releasing charges trapped in the floating gate and thereby affecting the resistance between the source and drain electrodes. [page 3]

Features evident in Figure 1 (shown at the beginning of this section) are explained in the following paragraphs:

With reference now to the drawing, in the memory cell shown in Fig. 1, a monocrystalline semiconductive element, the bulk 11 of which is weakly n-type, also includes spaced, localized, p-type surface zones, 12, 13. Electrodes 14 and 15 make low resistance connections to zones 12 and 13 and serve as the source and drain electrodes, respectively. Overlying the surface between zones 12 and 13 is the gate assembly comprising a relatively thin insulating layer 16 contiguous to the surface, an inner metallic layer 17, a relatively thick outer insulating layer 18, and an outer metallic layer 19. Layer 18 is also chosen to have a higher dielectric constant than layer 16. As seen, the metallic layer 17 is sandwiched between layers 16 and 18, and is insulated from the outer layer 19 and the semiconductive element. It will be convenient to refer to inner layer 17 as the floating gate and outer layer 19 as the terminal gate. It will also be apparent that insulating layer 16 is sandwiched between the semiconductive element 11 and the metal layer 17 to form a "tunnel sandwich diode" because as will be explained hereinafter the operation depends on electron tunneling through layer 16 under control of signal information.

In one embodiment constructed, the element 11 was primarily n-type silicon with a resistivity of about 1 ohm-centimeter. The layer 16 was about 50 angstroms thick and of silicon dioxide thermally grown, the layer 17 was of zirconium and about 1000 angstroms thick, the layer 18 was of zirconium oxide about 1000 angstroms thick, and the layer 19 and the electrodes 14 and 15 were of aluminum. The p-type zones 12 and 13 were spaced apart about 0.5 mil.

A voltage source 20 and load 21 are connected serially between source and drain electrodes 14 and 15. The control voltage source 22 is connected between the source electrode 14 and the terminal gate electrode 19.

For the specific design previously described, a voltage pulse of about fifty volts with a width of 0.5 microsecond was used to store  $5 \times 10^{12}$  electrons per square centimeter on the floating gate, which was adequate to cause the desired silicon surface layer inversion.

In operation, depending on the polarity of the most [page 3]

recent control voltage pulse provided by source 22, the surface portion 23 of the element extending between zones 12 and 13 and underlying the insulating layer 16 is either effectively n- or p-type. In the former case, a high resistance is presented, due to the presence of the reverse-biased p-n junction, to the flow of current in the load and little current flows. In the latter case, a low resistance is presented and a relatively large current flows. Accordingly, bistable operation is permitted. [page 4]

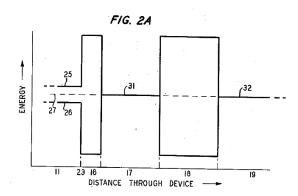

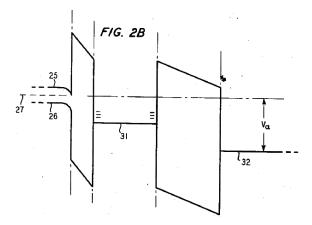

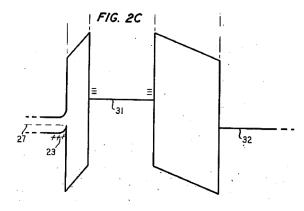

Following this physical description of the transistor, Kahng proceeds to describe its operation from a more theoretical perspective. For this he makes use of energy diagrams, also provided in the patent as figures 2A, 2B, and 2C.